# scientific reports

# **OPEN** Ternary logic decoder using independently controlled double-gate Si-NW MOSFETs

Seong-Joo Han, Joon-Kyu Han, Myung-Su Kim, Gyeong-Jun Yun, Ji-Man Yu, Il-Woong Tcho, Myungsoo Seo, Geon-Beom Lee & Yang-Kyu Choi<sup>™</sup>

A ternary logic decoder (TLD) is demonstrated with independently controlled double-gate (ICDG) silicon-nanowire (Si-NW) MOSFETs to confirm a feasibility of mixed radix system (MRS). The TLD is essential component for realization of the MRS. The ICDG Si-NW MOSFET resolves the limitations of the conventional multi-threshold voltage (multi- $V_{\rm th}$ ) schemes required for the TLD. The ICDG Si-NW MOSFETs were fabricated and characterized. Afterwards, their electrical characteristics were modeled and fitted semi-empirically with the aid of SILVACO ATLAS TCAD simulator. The circuit performance and power consumption of the TLD were analyzed using ATLAS mixed-mode TCAD simulations. The TLD showed a power-delay product of 35 aJ for a gate length ( $L_{\rm G}$ ) of 500 nm and that of 0.16 aJ for  $L_{\rm G}$ of 14 nm. Thanks to its inherent CMOS-compatibility and scalability, the TLD based on the ICDG Si-NW MOSFETs would be a promising candidate for a MRS using ternary and binary logic.

Scalability is one of the most important concerns in complementary metal-oxide-semiconductor (CMOS) device and circuit design1. Over the past several decades, the metal-oxide-semiconductor field-effect transistor (MOSFET) has been continuously scaled down to achieve higher performance and higher packing density with lower cost. An undesirable consequence of this aggressive down-scaling has been the appearance of adverse short-channel effects (SCEs), as well as increasingly challenging fabrication limits. To mitigate the SCEs, and continue further down-scaling, innovative device structures such as FinFETs, gate-all-around (GAA) FETs and a nanosheet (NS) based FET, have been introduced<sup>2-6</sup>. These new device structures have been able to suppress the off-state current ( $I_{\text{off}}$ ), which is fatal to the power consumption of a chip in the stand-by state. However, even with the above structural innovations, there are still limits that require device and process parameters to be continuously optimized.

Another approach to improving on-state current  $(I_{on})$  and chip performance has focused on the use of new materials, such as strained Si/SiGe and III-V compound semiconductors<sup>7-9</sup>. Although the new materials have advantages, silicon is still the most attractive material when CMOS-compatibility with low-cost is considered<sup>10</sup>.

In the meanwhile, multi-valued logic (MVL) has also been considered promising architecture to overcome the MOSFET scaling limitations from a circuit point of views. The MVL system can reduce the burden of circuit complexity inherent to binary-based logic circuits, by converting a multiple-output Boolean function into a single-output multiple-valued function<sup>11,12</sup>. In one particular case, a ternary-based logic circuit reduced the total cost and power consumption by minimizing the number of required inputs, resulting in the simplification of metal interconnection, compared to other MVL systems<sup>13</sup>.

In spite of these potential advantages, the practicality of ternary logic design heavily relies on the availability of the device and circuitry, which must be compatible with present-day binary CMOS technologies<sup>12</sup>. Binary operation has been the mainstay of modern computing system. To take full advantage of ternary logic, a mixed radix system (MRS) using both ternary and binary logic would be more suitable, rather than exclusively using ternary logic. To implement a MRS, conversion from a ternary code to a binary code is essential and vice versa 14-16. This requires a ternary logic decoder (TLD). Logic blocks such as a ternary logic multiplexer (TLM), a TLM-based half adder and comparator can be implemented based on the TLD<sup>17</sup>

To realize a TLD, a logic scheme for multi-threshold voltage (multi- $V_{\rm th}$ ) is necessary 18. There have been two approaches used to implement a multi- $V_{\rm th}$  scheme. One uses physical methods, by tuning the work-function of a metal gate<sup>19</sup> and by modulating the channel or body doping concentration by ion implantation<sup>20</sup>. The other utilizes electrical methods, applying back bias to a body in the MOSFET or potential redistribution in a gate electrode<sup>21</sup>. However, the aforementioned methods have several challenging issues. The gate work-function

School of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), 291 Daehak-ro, Yuseong-gu, Daejeon 34141, Republic of Korea. <sup>™</sup>email: ykchoi@ee.kaist.ac.kr

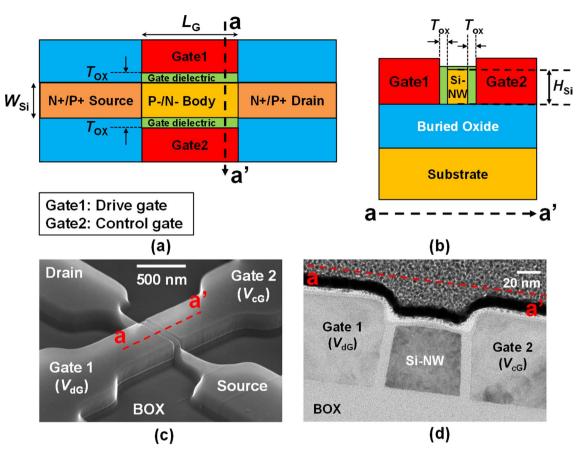

**Figure 1.** Overall structure of the ICDG Si-NW MOSFET. (a) Cross-sectional schematic of the ICDG Si-NW MOSFET along with the channel direction. (b) Cross-sectional schematic of the ICDG Si-NW MOSFET along with the gate direction. (c) SEM image of the fabricated ICDG Si-NW MOSFET. (d) Cross-sectional TEM image of the fabricated ICDG Si-NW MOSFET along with the gate direction.

engineering increases process complexity, and limits the spectrum of potential materials, which can lead to a work function variation (WFV) problem given the variability in grain size<sup>22</sup>. Adjustment of  $V_{\rm th}$  by ion implantation also involves issues with complementary dopants, accurate depth and concentration control, diffusivity, implantation-induced damages, and random dopant fluctuations. Moreover, channel doping concentration has little effect on  $V_{\rm th}$  control for a thin gate dielectric and a fully-depleted thin-body channel<sup>23–25</sup>.

With the electrical approach, additional static back bias in the bulk planar MOSFET increases parasitic capacitance and leakage, which can degrade device performances. In any case, fine tuning the  $V_{\rm th}$  is not an easy task, because  $V_{\rm th}$  modulated by applied static back bias does not follow a linear relationship. In addition, the static back bias can degrade  $I_{\rm off}$  and subthreshold swing (SS). For the gate electrode potential redistribution method, another challenging issue has been observed, an increase in static power consumption  $^{21}$ .

In another approach, a previous study attempted to control  $V_{\rm th}$  dynamically by using the four-terminals of an independently controlled double-gate (ICDG) FinFET<sup>26-31</sup>. Such a novel device could mitigate the abovementioned problems by allowing multi- $V_{\rm th}$ . But, there have been no reports of using ICDG devices for TLD so far. A primary goal of the present work is to demonstrate a TLD composed of ICDG silicon-nanowire (Si-NW) MOSFETs, and to confirm the feasibility of manufacturing a MRS chip. Because of their inherent CMOS-compatibility and simplicity, the proposed TLD would be a promising option for realizing a mixed radix circuit.

# Results and discussion

Supplementary Fig. S1 shows a simplified sequence of the experimental details. N-channel ICDG Si-NW MOS-FETs were fabricated, modeled, and fitted semi-empirically with the aid of SILVACO ATLAS TCAD simulator<sup>32</sup>. Thereafter, a P-channel ICDG Si-NW MOSFET was regenerated as a counter-part of the N-channel by simulations. Following device-level simulations, further analyses of the TLD circuit performance and power consumption were conducted using ATLAS mixed-mode TCAD simulations to predict the TLD behaviors at an elementary circuit level, as an extension. All of the abbreviations and nomenclature of variables are summarized in Supplementary Table S1.

Fabrication process of the ICDG Si-NW MOSFET is summarized in Supplementary Fig. S2. Figure 1 shows a schematic of the ICDG Si-NW MOSFET and scanning electron microscopy (SEM) and transmission electron microscopy (TEM), images of the fabricated ICDG Si-NW MOSFET. The fabricated ICDG Si-NW MOSFET was composed of two gates, a drive gate and a control gate, positioned at each sidewall of the Si-NW to control the current flowing in the Si-NW. The drive gate turns the channel on or off. The control gate modulates threshold

voltage as a body electrode does in a conventional bulk-MOSFET. The fabricated device had a Si-NW width  $(W_{\rm Si})$  of 70 nm, a gate length  $(L_{\rm G})$  of 500 nm, a Si-NW height  $(H_{\rm Si})$  of 50 nm and a gate dielectric thickness  $(T_{\rm ox})$  of 10 nm. The dimensions of the modeled device were the same as the fabricated device. Source, body, and drain doping concentration were set to  $1\times10^{20}$  cm<sup>-3</sup>,  $1\times10^{15}$  cm<sup>-3</sup>,  $1\times10^{20}$  cm<sup>-3</sup>, respectively. Various models such as Schockly-Read-Hall (SRH), bandgap narrowing (BGN), Fermi–Dirac (FERMI), energy balance model (EBM), non-local band-to-band tunneling (BTBT), trap-assisted tunneling (TAT), and quantum effect (QUANTUM for electrons and P.QUANTUM for holes) were utilized for the simulations. The P-channel ICDG Si-NW MOSFET was modeled in the same manner as the N-channel device, except for the doping polarity and  $H_{\rm Si}$ . The dopant of the P-channel device was the opposite that of the N-channel device, and the  $H_{\rm Si}$  was doubled considering the difference in carrier mobility of electrons and holes.

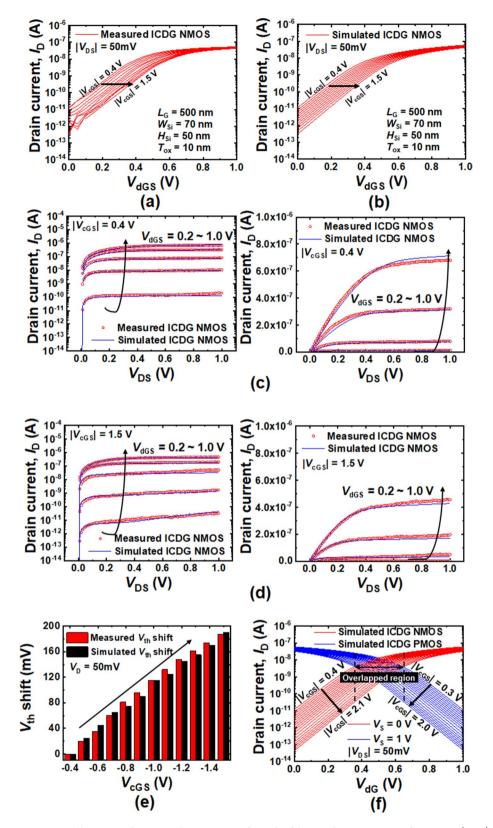

Figure 2(a) and (b) show the  $I_{\rm D}$ – $V_{\rm dGS}$  characteristics of the measured and simulated N-channel ICDG Si-NW MOSFET, respectively. The  $I_{\rm D}$ – $V_{\rm dGS}$  curves are shown for various  $|V_{\rm cGS}|$ . Measured and simulated  $I_{\rm D}$ – $V_{\rm DS}$  characteristics of N-channel ICDG Si-NW MOSFET are superimposed for  $V_{\rm cGS}$  = 0.4 V (Fig. 2c) and  $V_{\rm cGS}$  = −1.5 V (Fig. 2d) on the log-scaled y-axis and linear-scaled y-axis. They (measured and simulated) are very similar to each other. Because individual gate addressing is possible thanks to the use of two local gates, the channel potential of the Si-NW can be controlled independently<sup>33</sup>. One of the two gates is used to sweep the gate voltage of the drive gate while a constant voltage is applied to the other gate, which is the control gate to precisely tune the channel potential of the Si-NW. A shift in  $V_{\rm th}$  and its multiple values by  $V_{\rm cGS}$  are shown in Fig. 2e. The  $V_{\rm th}$  shift by  $V_{\rm cGS}$  has linear relationship. The results are consistent with the previously reported data<sup>26–31</sup>. As the  $|V_{\rm cGS}|$  increased, the  $I_{\rm D}$ – $V_{\rm dGS}$  curve shifted rightward in parallel and the  $V_{\rm th}$  was increased. Herein, leakage current is defined as off-state current at  $V_{\rm dGS}$  of 0 V. The measured leakage current from the fabricated ICDG Si-NW NMOSFET was decreased from 10 pA to 300 fA as the  $|V_{\rm cGS}|$  was increased from 0.4 V to 1.5 V. Figure 2f shows the symmetrically overlaid  $I_{\rm D}$ – $V_{\rm dGS}$  curves of the simulated N-channel and P-channel ICDG Si-NW MOSFET. Here, there is a wide overlapped region between the N-channel device and the P-channel device. This wide overlapped region stably creates a intermidiate output signal (output '1'), which enables the TLD. It becomes wider as the applied  $|V_{\rm cGS}|$  increases.

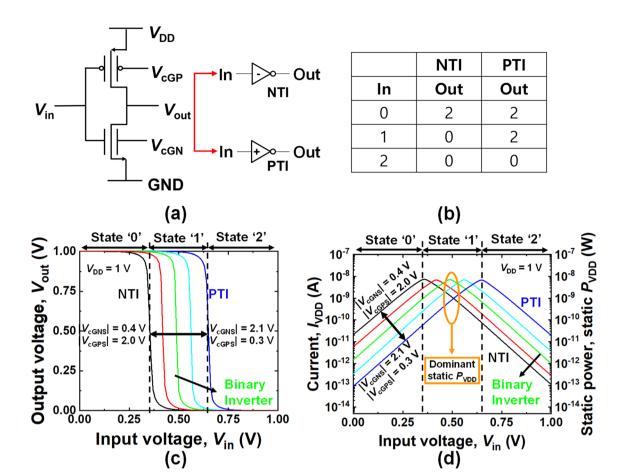

Note that there are negative ternary inverters (NTI) and positive ternary inverters (PTI) in ternary logic. Its output state becomes '0' or '2' when the input state is '1'18 as shown in Fig. 3b. The proposed TLD was composed of NTI, PTI, and negative ternary NOR (NTNOR)18. To implement the TLD, the characteristics of NTI and PTI should be confirmed.

As shown in Fig. 3a, the ternary inverter circuitry is similar to a typical binary inverter except for the use of the control gates. The complementary circuit shown in Fig. 3a can become both the NTI and the PTI by adjusting  $V_{\rm cGN}$  and  $V_{\rm cGP}$ . As shown in Fig. 3c, the voltage transfer curve (VTC) is shifted in parallel as  $|V_{\rm cGNS}|$  increases from 0.4 V to 2.1 V and  $|V_{\rm cGPS}|$  decreases from 2.0 V to 0.3 V. For the NTI, an input voltage ( $V_{\rm in}$ ) of 0.5 V (state '1') is transformed to a  $V_{\rm out}$  of 0 V (state '0') because  $|V_{\rm th}|$  in the P-channel device is higher than that of the N-channel device. In contrast, the  $V_{\rm in}$  of 0.5 V (state '1') is converted to a  $V_{\rm out}$  of 1 V (state '2') in the case of the PTI, due to the higher  $|V_{\rm th}|$  of the N-channel device.

Figure 3d shows the  $I_{\rm VDD}$  and  $P_{\rm VDD}$  characteristics versus the  $V_{\rm in}$ . The  $I_{\rm VDD}$  increased and decreased exponentially as the N-channel and P-channel devices started to turn on and turn off, respectively, at a certain voltage. Peak points of the  $I_{\rm VDD}$  curve at a certain voltage, were shifted as the  $|V_{\rm cGNS}|$  and  $|V_{\rm cGPS}|$  changed.  $P_{\rm VDD}$  can be obtained by multiplying the  $I_{\rm VDD}$  by  $V_{\rm DD}$  for various  $V_{\rm in}$ , as shown in the 2nd y-axis in Fig. 3d. We can average  $P_{\rm VDD}$  for three states with a different weighting factor:  $w_0$  for state '0',  $w_1$  for state '1' and  $w_2$  for state '2'. This is represented by  $\langle P_{\rm VDD} \rangle_{\rm avg} = (w_0 \cdot P_{\rm VDD})_{\rm state-0} + w_1 \cdot P_{\rm VDD}|_{\rm state-1} + w_2 \cdot P_{\rm VDD}|_{\rm state-2})/(w_0 + w_1 + w_2)$ . This averaged  $P_{\rm VDD}$  is approximated to  $(1/3) \cdot w_1 \cdot P_{\rm VDD}|_{\rm state-1}$  under the condition of  $w_0 = w_1 = w_2$ , because the  $P_{\rm VDD}|_{\rm state-2}$  and  $P_{\rm VDD}|_{\rm state-2}$  are much smaller than the  $P_{\rm VDD}|_{\rm state-1}$ . It should be noted that  $I_{\rm VDD}$  for state '1' is much larger than that at the state '0' and '2'. When the curve (green line) of a typical binary inverter in Fig. 3d is shifted to the NTI or the PTI, the  $P_{\rm VDD}|_{\rm state-1}$  decreases. Accordingly, the total  $P_{\rm VDD}$  decreases.

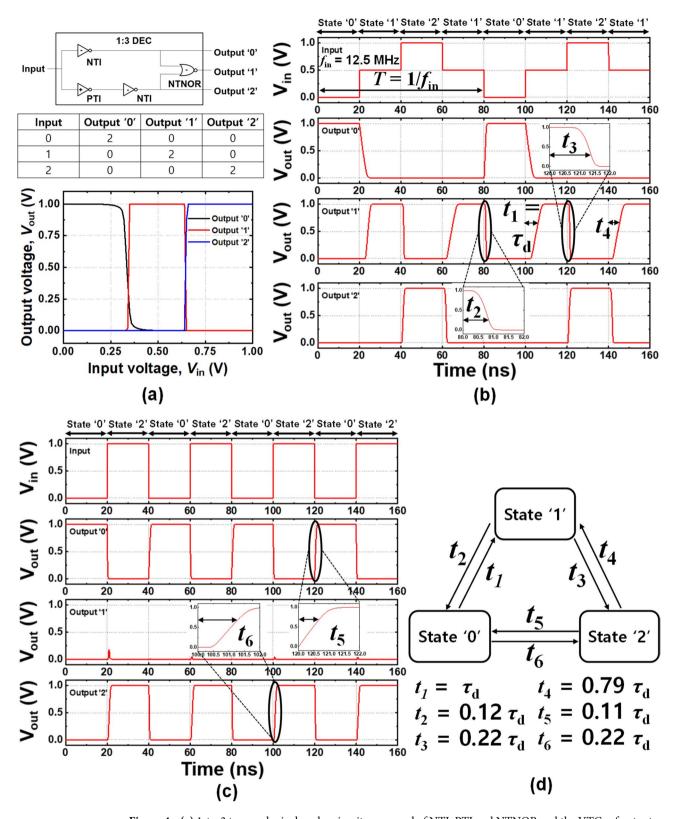

A 1-to-3 TLD circuit was designed to examine the feasibility of the ICDG Si-NW MOSFET for the TLD. The TLD consisted of 10 complementary ICDG Si-NW MOSFETs. Figure 4a shows the TLD logic circuit and its VTCs for an output '0', output '1', and output '2' versus the  $V_{\rm in}$ . The NTNOR CMOS circuitry was the same as the typical binary NOR except for the use of the control gates. The device models for the NTNOR were identical to the device models described in Fig. 2. As shown in the VTC graph in Fig. 4a, the TLD stably accepts voltage near 0.5 V as an input then it produces the third output voltage (output '1'). The behaviors of the TLD were verified using the ATLAS mixed-mode TCAD simulations, as shown in Fig. 4b and c. Voltage levels of 1 V ( $V_{\rm DD}$ ), 0.5 V (half  $V_{DD}$ ), and 0 V ( $V_{SS}$ ) are equivalent to a logic value of '2', '1', and '0', respectively. Figure 4d shows a diagram of the state transition with propagation delay time. Note that the transition time is related to on-current of a MOSFET. According to the result of Fig. 4d,  $t_2$  ('1'  $\rightarrow$  '0') was almost the same as  $t_5$  ('2'  $\rightarrow$  '0') because both the  $t_2$  and  $t_5$  depend on the on-current of an n-channel pull-down transistor ( $I_{\text{on}, 0}$ ). Likewise,  $t_3$  ('1'  $\rightarrow$  '2') was the same as  $t_6$  ('0'  $\rightarrow$  '2') because both the  $t_3$  and  $t_6$  depend on the on-current of a p-channel pull-up transistor  $(I_{\text{on}, '2'})$ .  $t_1$  and  $t_4$  are dominated by on-current  $(I_{\text{on}, '1'})$  at an intermediate state.  $I_{\text{on}, '1'}$  is defined as the drain current at  $V_{\text{dGS}} = V_{\text{DD}}/2$ . As shown in Fig. 2f, the  $I_{\text{on, '1'}}$  was smaller than the  $I_{\text{on, '0'}}$  and  $I_{\text{on, '2'}}$ . Therefore,  $t_1$  and  $t_4$  were longer than the other transition times  $(t_2, t_3, t_5, \text{ and } t_6)$ . Additionally, the difference between  $t_1$  and  $t_4$  was arisen from a slight disparity of  $I_D$  between  $I_{\text{on},'1'}$  of a p-channel MOSFET and an n-channel MOSFET. The delay time  $(\tau_d)$  is dominated by the longest transition time  $(t_1)$ . To reduce the delay time,  $I_{\text{on, '1'}}$  modulated by  $|V_{\text{cGS}}|$  should be maximized as large as possible.

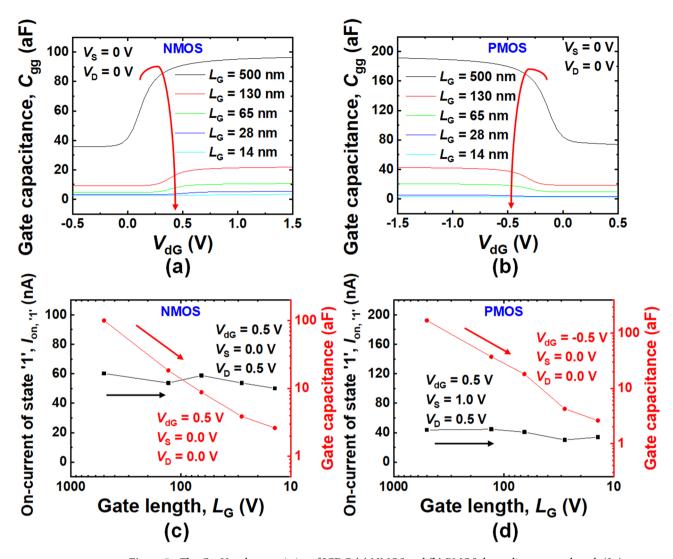

Based on SILVACO ATLAS TCAD simulator, the scaling analysis was implemented by reducing device dimensions ( $L_{\rm G}$ ,  $W_{\rm Si}$ ,  $H_{\rm Si}$ , and  $T_{\rm ox}$ ). The detailed information of those is shown in Supplementary Table S2. Figure 5 shows a quantitative analysis of gate capacitance ( $C_{\rm gg}$ ) and  $I_{\rm on, T}$ . Figures 5a and b show the  $C_{\rm gg}$ - $V_{\rm dG}$  characteristics depending on  $L_{\rm G}$  under certain  $V_{\rm cG}$  conditions which were optimized for  $V_{\rm th}$ -modulation. Optimization of

Figure 2. (a) Measured  $I_{\rm D}$ - $V_{\rm dGS}$  characteristics from the fabricated ICDG NMOS for various  $|V_{\rm cGS}|$ . (b) Semi-empirically simulated  $I_{\rm D}$ - $V_{\rm dGS}$  characteristics according to various  $|V_{\rm cGS}|$ . Superimposition of measured and simulated  $I_{\rm D}$ - $V_{\rm DS}$  characteristics of N-channel for (c)  $|V_{\rm cGS}|$ =0.4 V and (d) 1.5 V on the log-scaled y-axis and linear-scaled y-axis. (e) Linear  $V_{\rm th}$  shift by  $V_{\rm cGS}$ . (f) Simulated  $I_{\rm D}$ - $V_{\rm dGS}$  characteristics of both ICDG NMOS and PMOS for various  $|V_{\rm cGS}|$ .

Figure 3. (a) Complementary inverter circuits composed of ICDG NMOS and PMOS with each control gate. They can serve as the NTI and the PTI by adjusting  $V_{\rm cGN}$  and  $V_{\rm cGP}$  (b) Truth table of the NTI and PTI. (c) Input–output voltage transfer curves (VTCs) of the inverter circuit for various  $|V_{\rm cGNS}|$  and  $|V_{\rm cGPS}|$ . (d) Current  $(I_{\rm VDD})$  from the  $V_{\rm DD}$  node to the ground node versus input voltage  $(V_{\rm in})$  and power consumption  $(P_{\rm VDD})$  versus input voltage  $(V_{\rm in})$ .

$V_{

m th}$ -modulation according to  $V_{

m cG}$  can be performed with consideration of two conflicting demands: maximization of speed and minimization of static power consumption. Increment of  $I_{

m on,\,'I'}$  through the  $V_{

m cG}$  modulation can result in boosting speed of the ternary logic decoder (TLD). But, excessive increment of  $I_{

m on,\,'I'}$  can adversely increase the static power consumption (P) of the TLD owing to a parallel shift of  $V_{

m th}$ , which provokes increment of leakage current. Thus, the optimization of  $V_{

m cG}$  can be done with a well-known figure of merit, power-delay product (PDP) owing to the abovementioned trade-off relationship. The magnitude of  $C_{

m gg}$  for N-channel and P-channel ICDG Si-NW MOSFETs was decreased as  $L_{

m G}$  was decreased. As shown in Fig. 4c and d, as  $L_{

m G}$  was decreased,  $C_{

m gg}$  was continuously decreased, while  $I_{

m on,\,'I'}$  was maintained by  $V_{

m th}$ -modulation. It means that delay time ( $\tau_{

m d}$ ) of the TLD circuit is decreased by down-scaling.

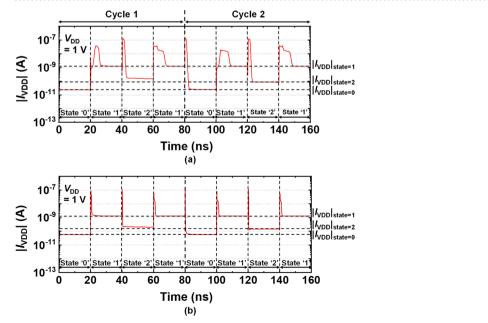

Figure 6a and b show two transient current responses for an  $L_{\rm G}$  of 500 nm and an  $L_{\rm G}$  of 14 nm, respectively at input voltage frequency ( $f_{\rm in}$ ) of 12.5 MHz. The  $f_{\rm in}$  of 12.5 MHz was used from  $T=1/f_{\rm in}=80$  ns as shown in Fig. 4b first graph. When the input voltage signal abruptly switched from one state to another, charges were transferred from the power supply to the gate capacitors or load capacitors. And  $|I_{\rm VDD}|$  rapidly increased and temporarily overshot, thereafter it began to stabilize. As shown in Fig. 6b, the pulse width needed to induce the overshoot was significantly reduced by down-scaling from  $L_{\rm G}=500$  nm to  $L_{\rm G}=14$  nm. The stabilized  $|I_{\rm VDD}|$  depended on the applied  $V_{\rm in}$  (state of input). The magnitude of the stabilized  $|I_{\rm VDD}|$  for the input voltage of 0.5 V (state '1') was much higher than that for the other states, like the  $|I_{\rm VDD}|$  of the NTI and PTI shown in Fig. 3d. For an  $L_{\rm G}=500$  nm, a total  $P_{\rm VDD}$  of 6.37 nW was calculated by integrating  $V_{\rm DD} \times |I_{\rm VDD}(t)|$  with respect to the 2 cycle time (2 T=160 ns) and dividing it by the same time, i.e., (total  $P_{\rm VDD}$ ) =  $[V_{\rm DD} \cdot \int_{0~\rm ns}^{160} |I_{\rm VDD}(t)|dt]/(160$  ns).

The TLD was evaluated in terms of  $\tau_{\rm d}$ ,  $P_{\rm c}$ , and PDP. These values were semi-empirically extracted from the

The TLD was evaluated in terms of  $\tau_{\rm d}$ , P, and PDP. These values were semi-empirically extracted from the simulations, which were based on the fabricated device. Theoretically,  $\tau_{\rm d}$  can be reduced by  $V_{\rm th}$  engineering by biasing the control gate, as well as by device down-scaling. The above three metrics were changed by reducing the gate length ( $L_{\rm G}$ ), as summarized in Table 1. As shown in Fig. 4d, the propagation delay times,  $t_1$  from state '0' to state '1' and  $t_4$  from state '2' to state '1' were longer than the other transition times ( $t_2$ ,  $t_3$ ,  $t_5$ , and  $t_6$ ) because  $I_{\rm on, '1'}$  is smaller than  $I_{\rm on, '0'}$  and  $I_{\rm on, '2'}$ . In this work, the  $\tau_{\rm d}$  of TLD is predominantly governed by the longest transition time,  $t_1$  ( $t_1 > t_4$ ).

**Figure 4.** (a) 1-to-3 ternary logic decoder circuit composed of NTI, PTI and NTNOR and the VTCs of output '0', output '1' and output '2'. (b) Transient ternary responses of output '0', output '1', output '2' versus time ( $f_{\rm in}$  = 12.5 MHz). (c) Transient binary responses for direct alteration between states '2' and '0'. (d) Diagram of state transition with propagation delay time.

**Figure 5.** The  $C_{\rm gg}$ - $V_{\rm dG}$  characteristics of ICDG (a) NMOS and (b) PMOS depending on gate length ( $L_{\rm G}$ ) reduction.  $I_{\rm on,\,'1'}$  and  $C_{\rm gg}$  of ICDG (c) NMOS and (d) PMOS according to gate length reduction.

**Figure 6.** Transient response of  $I_{\rm VDD}$  versus time for (a)  $L_{\rm G}$  = 500 nm and (b)  $L_{\rm G}$  = 14 nm.

| Gate length (L <sub>G</sub> ) [nm] | Delay (τ <sub>d</sub> ) [ns] | Possible operating frequency [GHz] | Power (P) [nW] (at f <sub>in</sub> [MHz]) | PDP [aJ] |

|------------------------------------|------------------------------|------------------------------------|-------------------------------------------|----------|

| 500                                | 5.57                         | 0.045                              | 6.37<br>(12.5)                            | 35.48    |

| 130                                | 0.95                         | 0.263                              | 2.68<br>(48.1)                            | 2.55     |

| 65                                 | 0.44                         | 0.568                              | 2.20<br>(96.2)                            | 0.97     |

| 28                                 | 0.18                         | 1.389                              | 2.14<br>(223.2)                           | 0.39     |

| 14                                 | 0.085                        | 2.941                              | 1.90<br>(446.4)                           | 0.1615   |

**Table 1.** Power and delay time according to gate length scaling.

|           | Type of devices         | $V_{ m th}$ -modulation   | Number of transistors | Power (P) [nW] | Delay (τ <sub>d</sub> ) [ps] | PDP [aJ] |

|-----------|-------------------------|---------------------------|-----------------------|----------------|------------------------------|----------|

| 18        | MOSFETs                 | Body Ion Implantation     | 10                    | 0.444          | >23,000                      | 10.2     |

| 35        | CNTFETs                 | Diameter Engineering      | 16                    | 11,800         | 8.24                         | 97.2     |

| 36        | MOSFETs                 | CMOS Double Pass<br>Logic | 12                    | 13,000         | 140                          | 1820     |

| 37        | CNTFETs                 | Diameter Engineering      | 11                    | 10,400         | 7.06                         | 73.4     |

| 38        | CNTFETs                 | Diameter Engineering      | 10                    | 250,000        | 7.18                         | 1795     |

| 39        | CNTFETs                 | Diameter Engineering      | 9                     | 9100           | 4.18                         | 38.0     |

| This work | ICDG Si-NW MOS-<br>FETs | Electrical Control Bias   | 10                    | 1.90           | 85                           | 0.16     |

**Table 2.** Benchmarking table of ternary logic decoder.

The possible operating frequency was calculated from f = 1 /  $(4\tau_d)^{34}$ . Following a constant field scaling scenario with a scaling factor of K (> 1),  $f_{\rm in}$  is proportional to K for the down-scaling $^1$ . Therefore, the  $f_{\rm in}$  for a short  $L_{\rm G}$  becomes  $f_{\rm in}$ ·long  $L_{\rm G}$ /short  $L_{\rm G}$ . For example, an  $f_{\rm in}$  of 12.5 MHz for an  $L_{\rm G}$  of 500 nm can be increased to 48.1 MHz with an  $L_{\rm G}$  of 130 nm.  $\tau_{\rm d}$  was directly extracted and P was extracted for each  $f_{\rm in}$  predicted by the abovementioned scaling rule for an  $L_{\rm G}$  of 500 nm, 130 nm, 65 nm, 28 nm, and 14 nm, as shown in Table 1. The  $\tau_{\rm d}$  of 5.57 ns for  $L_{\rm G}$  of 500 nm was drastically reduced to 0.085 ns for an  $L_{\rm G}$  of 14 nm. And the P of 6.37 nW for an  $L_{\rm G}$  of 500 nm was also reduced to that of 1.90 nW for  $L_{\rm G}$  of 14 nm. In addition, the PDP of 0.16 aJ was extracted from P of 1.9 nW and  $\tau_{\rm d}$  of 0.085 ns for  $L_{\rm G}$  of 14 nm. The performance metrics of the proposed TLD are compared with the existing implementations, as shown in benchmarking Table  $2^{18,35-39}$ .

The SS of the ICDG Si-NW MOSFET in this experiment was approximately 120 mV/dec, due to the poor interface quality of the TEOS used as the gate oxide. This can be decreased to sub-80 nm/dec replacing the thermally grown oxide or using a high-k dielectric material. Further improvement in the SS will additionally reduce  $\tau_{\rm d}$  and P.

In this study, a ternary logic decoder (TLD) to allow the conversion from a ternary code to a binary code and vice versa has been demonstrated with independently controlled double-gate (ICDG) silicon-nanowire (Si-NW) MOSFETs. Feasibility of the TLD was explored by use of semi-empirical circuit-level simulations based on the measured device-level ICDG Si-NW MOSFET characteristics. Because the ICDG Si-NW MOSFET is not only suitable for a multi- $V_{\rm th}$  scheme but also CMOS-compatible for mass-production, the proposed TLD would be a promising candidate to realize a MRS. Direct demonstration of the TLD with fully fabricated circuits is left as a further work.

### Methods

**Electrical measurements.** A semiconductor parameter analyzer (B1500A) was used to characterize the fabricated ICDG Si-NW MOSFETs. The transfer characteristics of the fabricated N-channel ICDG Si-NW MOSFET were measured at a constant  $V_{\rm DS}$  of 50 mV, whereas the  $V_{\rm dGS}$  was swept from 0 to 1 V.

**Device modeling.** The ICDG Si-NW MOSFETs were modeled and fitted with the SILVACO ATLAS TCAD simulator. A various physical models such as Schockly-Read-Hall (SRH), Bandgap Narrowing (BGN), Fermi-Dirac (FERMI), non-local Band-to-Band Tunneling (BTBT) and Trap-Assisted Tunneling (TAT) were involved.

**Circuit simulation for ternary logic decoder.** Using the experimentally modeled devices, the operation, performance, and power consumption of the TLD were verified using the ATLAS mixed-mode TCAD simulations. To simulate the transient response of the TLD,  $V_{\rm DD}$  and  $V_{\rm SS}$  were set to 1 V and 0 V respectively.

Received: 4 January 2021; Accepted: 8 June 2021

Published online: 21 June 2021

#### References

- Frank, D. J. et al. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89(3), 259–288. https://doi. org/10.1109/5.915374 (2001).

- 2. Taur, Y. et al. CMOS scaling into the nanometer regime. Proc. IEEE 85(4), 486–504. https://doi.org/10.1109/5.573737 (1997).

- 3. Y.-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "Sub-20 nm CMOS FinFET technologies," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, pp. 421–424, Dec. 2001. https://doi.org/10.1109/IEDM.2001.979526.

- 4. Colinge, J.-P. FinFETs and Other Multi-Gate Transistors. Springer-Verlag https://doi.org/10.1007/978-0-387-71752-4 (2008).

- 5. J. P. Colinge, M. H. Gao, A. Romano-Rodriguez, H. Maes, and C. Claeys, "Silicon-on-insulator 'gate-all-around device," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, pp. 595–598, 1990. https://doi.org/10.1109/IEDM.1990.237128.

- N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in Proc. IEEE Symp. VLSI Technol., pp. T230–T231, Jun. 2017. https://doi.org/10.23919/VLSIT.2017.7998183.

- Öberhuber, R., Zandler, G. & Vogl, P. Subband structure and mobility of two-dimensional holes in strained Si/SiGe MOSFETs. Phys. Rev. B Condens. Matter 58(15), 9941–9948. https://doi.org/10.1103/PhysRevB.58.9941 (1998).

- Thompson, S. E. et al. A logic nanotechnology featuring strained-silicon. IEEE Electron Device Lett. 25(4), 191–193. https://doi. org/10.1109/LED.2004.825195 (2004).

- del Alamo, J. A. Nanometre-scale electronics with III-V compound semiconductors. Nature 479(7373), 317–323. https://doi.org/10.1038/nature10677 (2011).

- 10. Iwai, H. Future of nano CMOS technology. Solid-State Electron. 112, 56-67. https://doi.org/10.1016/j.sse.2015.02.005 (2015).

- Smith, K. C. The prospects for multivalued logic: a technology and applications view. IEEE Trans. Comput. C-30(9), 619–634. https://doi.org/10.1109/TC.1981.1675860 (1981).

- 12. E. Dubrova, "Multiple-valued logic in VLSI: Challenges and opportunities," in Proc. NORCHIP Conf., pp. 340-350, 1999.

- 13. Hurst, S. L. Multiple-valued logic—Its status and its future. *IEEE Trans. Comput.* C-33(12), 1160-1179. https://doi.org/10.1109/TC.1984.1676392 (1984).

- Etiemble, D. & Israel, M. Comparison of binary and multivalued ICs according to VLSI criteria. Computer 21, 28–42. https://doi. org/10.1109/2.49 (1988).

- Current, K. W. Current-mode CMOS multiple-valued logic circuits. IEEE J. Solid-State Circuits 29, 95–107. https://doi.org/10. 1109/4.272112 (1994).

- Shahangian, M., Hosseini, S. A. & Pishgar Komleh, S. H. Design of a multi-digit binary to ternary converter based on CNTFETs. Circ. Syst. Signal Process. 38(6), 2544–2563. https://doi.org/10.1007/s00034-018-0977-3 (2018).

- C. Vudadha, S. V, and M.B. Srinivas, "2:1 Multiplexer Based Design for Ternary Logic Circuits", PRIME 2012, Aachen, Germany Session TG1 – Analog and Mixed Signal III, pp 139–142, 2012. https://doi.org/10.1109/PrimeAsia.2013.6731176.

- Balla, P. C. & Antoniou, A. Low power dissipation MOS ternary logic family. IEEE J. Solid-State Circuits 19(5), 739–749. https://doi.org/10.1109/JSSC.1984.1052216 (1984).

- 19. Y.-K. Choi, L. Chang, P. Ranade, J. S. Lee, D. Ha, S. Balasubramanian, A. Agarwal, M. Ameen, T.-J. King, and J. Bokor, "FinFET process refinements for improved mobility and gate work function engineering," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, pp. 259–262, Dec. 2002. https://doi.org/10.1109/IEDM.2002.1175827.

- Pherson, M. R. M. The adjustment of MOS transistor threshold voltage by ion implantation. Appl. Phys. Lett. 18(11), 502–504. https://doi.org/10.1063/1.1653513 (1971).

- 21. Park, J.-Y., Bae, H.-Y., Moon, D.-I., Jeon, C.-H. & Choi, Y.-K. Threshold voltage tuning technique in gate-all-around MOSFET by utilizing gate electrode with potential distribution. *IEEE Electron Device Lett.* **37**(11), 1391–1394. https://doi.org/10.1109/LED. 2016.2612653 (2016).

- 22. Choi, K. M. & Choi, W. Y. Work-function variation effects of tunneling field-effect transistors (TFETs). *IEEE Electron Device Lett.* 34(8), 942–944. https://doi.org/10.1109/LED.2013.2264824 (2013).

- 23. Vitale, S., Wyatt, P., Checka, N., Kedzierski, J. & Keast, C. FDSOI process technology for subthreshold-operation ultralow-power electronics. *Proc. IEEE* **98**(2), 333–342. https://doi.org/10.1109/JPROC.2009.2034476 (2010).

- Park, J.-T. & Colinge, J.-P. Multiple-gate SOI MOSFETs: device design guidelines. IEEE Trans. Electron Devices 49(12), 2222–2229. https://doi.org/10.1109/TED.2002.805634 (2002).

- Lee, J.-H., Lee, J.-W., Jungand, H.A.-R. & Choi, B.-K. Comparison of SOI FinFETs and bulk FinFETs. ECS Trans. 19(4), 101–112. https://doi.org/10.1149/1.3117397 (2009).

- Fried, D. M., Duster, J. S. & Kornegay, K. T. Improved independent gate N-type FinFET fabrication and characterization. *IEEE Electron Device Lett.* 24(9), 592–594. https://doi.org/10.1109/LED.2003.815946 (2003).

- 27. Y. X. Liu, M. Masahara, K. Ishii, T. Tsutsumi, T. Sekigawa, H. Takashima, H. Yamauchi, and E. Suzuki, "Flexible Threshold Voltage FinFETs with Independent Double Gates and an Ideal Rectangular Cross-Section Si-Fin Channel," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, pp. 986–988, Dec. 2003. https://doi.org/10.1109/IEDM.2003.1269445.

- 28. Liu, Y. et al. A highly threshold Voltage-controllable 4T FinFET with an 8.5-nm-thick Si-fin channel. *IEEE Electron Device Lett.* 25(7), 510–512. https://doi.org/10.1109/LED.2004.831205 (2004).

- 29. Endo, K. et al. Independent-double-gate FinFET SRAM for leakage current reduction. IEEE Electron Device Lett. 30(7), 757–759 (2009).

- 30. J.-H. Ahn, J.-Y. Kim, C. Jung, D.-I. Moon, S.-J. Choi, C.-H. Kim, K.-B. Lee, H. G. Park, and Y.-K. Choi, "CMOS-based biosensors with an independent double-gate FinFET," in *Proc. IEEE IEDM*, 2011, pp. 36.2.1–36.2.4.

- 31. K. Endo, S. Oʻuchi, Y. Ishikawa, Y. Liu, T. Matsukawa, K. Sakamoto, J. Tsukada, K. Ishii, H. Yamauchi, E. Suzuki, and M. Masahara, "Enhancing SRAM cell performance by using independent double-gate FinFET," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- 32. Atlas User's Manual, Silvaco, Santa Clara, CA, USA, 2016.

- 33. Chen, Y., Wang, X., Erramilli, S., Mohanty, P. & Kalinowski, A. Silicon-based nanoelectronic field-effect pH sensor with local gate control. Appl. Phys. Lett. 89(22), 223512-1-223512-3. https://doi.org/10.1063/1.2392828 (2006).

- 34. Jeong, J. W. et al. Tunnelling-based ternary metal-oxide-semiconductor technology. Nature Electron. 2(7), 307–312. https://doi.org/10.1038/s41928-019-0272-8 (2019).

- 35. R. Jaber, A. El-hajj, L. Nimri, and A. Haidar, "A Novel implementation of ternary decoder using CMOS DPL binary gates," in *Proc. Int. Arab Conf. Inf. Technol. (ACIT)*, Werdanye, Lebanon, Nov. 2018, pp. 1–3.

- 36. Lin, S., Kim, Y. B. & Lombardi, F. CNTFET-based design of ternary logic gates and arithmetic circuits. *IEEE Trans. Nanotechnol.* 10(2), 217–225. https://doi.org/10.1109/TNANO.2009.2036845 (2011).

- 37. P. Wang, D. Gong, Y. Zhang, and Y. Kang, "Ternary 2–9 line address decoder realized by CNFET," U.S. Patent 20 180 182 450 A1, Jun. 28, 2018.

- 38. Sridharan, K., Gurindagunta, S. & Pudi, V. Efficient multiternary digit adder design in CNTFET technology. *IEEE Trans. Nanotechnol.* 12(3), 283–287. https://doi.org/10.1109/TNANO.2013.2251350 (2013).

- 39. Jaber, R. A., Kassem, A., El-Hajj, A. M., El-Nimri, L. A. & Haidar, A. M. High-performance and energy-efficient CNFETbased designs for ternary logic circuits. *IEEE Access* 7, 93871–93886 (2019).

## **Acknowledgements**

This work was supported by the National Research Foundation (NRF) of Republic of Korea (2018R1A2A3075302, 2019M3F3A1A03079603, and 2020M3F3A2A01082592), and in part by IC Design Education Center (EDA Tool and MPW).

# **Author contributions**

S.-J. Han, J.-K. Han, G.-J. Yun, and Y.-K. Choi conceived the idea and designed the experiment. S.-J. Han and J.-K. Han measured the electrical characteristic of the fabricated devices and conducted the SILVACO ATLAS TCAD simulations. S.-J Han and M. Seo conducted the down-scaling analysis. M.-S. Kim, J.-M. Yu, I.-W. Tcho, and G.-B. Lee analyzed experimental data. S.-J. Han and Y.-K Choi prepared the manuscript.

## Competing interests

The authors declare no competing interests.

### Additional information

**Supplementary Information** The online version contains supplementary material available at https://doi.org/10.1038/s41598-021-92378-7.

**Correspondence** and requests for materials should be addressed to Y.-K.C.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2021, corrected publication 2021