Abstract

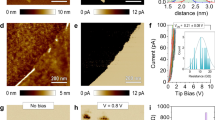

Two-dimensional (2D) semiconductors could potentially be used as channel materials in commercial field-effect transistors. However, the interface between 2D semiconductors and most gate dielectrics contains traps that degrade performance. Layered hexagonal boron nitride (h-BN) can form a defect-free interface with 2D semiconductors, but when prepared by industry-compatible methods—such as chemical vapour deposition (CVD)—the presence of native defects increases leakage current and reduces dielectric strength. Here we show that metal gate electrodes with a high cohesive energy—platinum and tungsten—can allow CVD-grown layered h-BN to be used as a gate dielectric in transistors. The electrodes can reduce the current across CVD-grown h-BN by a factor of around 500 compared to similar devices with gold electrodes and can provide a high dielectric strength of at least 25 MV cm−1. We examine the behaviour statistically across 867 devices, which includes a microchip based on complementary metal–oxide–semiconductor technology.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this article and other findings of this study are available from the corresponding author upon reasonable request.

References

Bakalar, N. Transistors, 1948. The New York Times (31 August, 2009).

Hoerni, J. A. Method of manufacturing semiconductor devices. US patent 3,025,589A (1962).

Kingon, A. I., Maria, J.-P. & Streiffer, S. K. Alternative dielectrics to silicon dioxide for memory and logic devices. Nature 406, 1032–1038 (2000).

Mistry, K. et al. A 45nm logic technology with high-k+metal gate transistors, strained silicon, 9 cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. In Proc. 2007 IEEE International Electron Devices Meeting (ed. Tung, R. T.) 247–250 (IEEE, 2007).

Natarajan, S. et al. A 32nm logic technology featuring 2nd-generation high-k + metal-gate transistors, enhanced channel strain and 0.171μm2 SRAM cell size in a 291Mb array. In Proc. 2008 IEEE International Electron Devices Meeting (ed. King Liu, T.-J.) 1–3 (IEEE, 2008).

International Roadmap for Devices and Systems (IRDS) 2023 Update (ed. Kumar, R.). IEEE IRDS https://irds.ieee.org/editions/2023 (2023).

Cheng, C.-C. et al. First demonstration of 40-nm channel length top-gate WS2 pFET using channel area-selective CVD growth directly on SiOx/Si substrate. In Proc. 2019 Symposium on VLSI Technology T244–T245 (IEEE, 2019).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42nm contact pitch and 250µA/µm drain current. In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) (ed. King Liu, T.-J.) 23.2.1–23.2.4 (IEEE, 2019).

McDonnell, S. et al. HfO2 on MoS2 by atomic layer deposition: adsorption mechanisms and thickness scalability. ACS Nano 7, 10354–10361 (2013).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, 722–726 (2010).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Jiang, L. et al. Dielectric breakdown in chemical vapor deposited hexagonal boron nitride. ACS Appl. Mater. Interfaces 9, 39758–39770 (2017).

Pandey, H. et al. All CVD boron nitride encapsulated graphene FETs with CMOS compatible metal edge contacts. IEEE Trans. Electron Devices 65, 4129–4134 (2018).

Shen, Y. et al. Variability and yield in h‐BN‐based memristive circuits: the role of each type of defect. Adv. Mater. 33, 2103656 (2021).

Wen, C. et al. Advanced data encryption using 2D materials. Adv. Mater. 33, 2100185 (2021).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101–108 (2017).

Yang, Y. et al. Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 3, 732 (2012).

Cabout, T. et al. Role of Ti and Pt electrodes on resistance switching variability of HfO2-based resistive random access memory. Thin Solid Films 533, 19–23 (2013).

Yang, J. J. et al. The mechanism of electroforming of metal oxide memristive switches. Nanotechnology 20, 215201 (2009).

Wu, X. et al. Role of oxygen vacancies in HfO2-based gate stack breakdown. Appl. Phys. Lett. 96, 172901 (2010).

Yoshida, C., Kinoshita, K., Yamasaki, T. & Sugiyama, Y. Direct observation of oxygen movement during resistance switching in NiO/Pt film. Appl. Phys. Lett. 93, 042106 (2008).

Shi, Y. et al. Electronic synapses made of layered two-dimensional materials. Nat. Electron. 1, 458–465 (2018).

Pan, C. et al. Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride. Adv. Funct. Mater. 27, 1604811 (2017).

Arnaud, B., Lebègue, S., Rabiller, P. & Alouani, M. Huge excitonic effects in layered hexagonal boron nitride. Phys. Rev. Lett. 96, 026402 (2006).

Kramer, B. & MacKinnon, A. Localization: theory and experiment. Rep. Prog. Phys. 56, 1469–1564 (1993).

Choi, S.-M. et al. On the universality of drain-induced-barrier-lowering in field-effect transistors. In Proc. 2022 International Electron Devices Meeting (IEDM) (ed. Klimeck, G.) 8.3.1–8.3.4 (IEEE, 2022).

Dorow, C. J. et al. Gate length scaling beyond Si: mono-layer 2D channel FETs robust to short channel effects. In Proc. 2022 International Electron Devices Meeting (IEDM) (ed. Klimeck, G.) 7.5.1–7.5.4 (IEEE, 2022).

Liu, L., Lu, Y. & Guo, J. On monolayer MoS2 field-effect transistors at the scaling limit. IEEE Trans. Electron Devices 60, 4133–4139 (2013).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

The decadal plan for semiconductors. SRC https://www.src.org/about/decadal-plan (2021).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Beck, M. E. et al. Spiking neurons from tunable Gaussian heterojunction transistors. Nat. Commun. 11, 1565 (2020).

Brems, S. et al. Overview of scalable transfer approaches to enable epitaxial 2D material integration. In Proc. 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT) (ed. Chang, S.-C.) 151–152 (IEEE, 2023).

Bae, S. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotechnol. 5, 574–578 (2010).

Zhu, K. et al. The development of integrated circuits based on two-dimensional materials. Nat. Electron. 4, 775–785 (2021).

Zhu, K. et al. Hybrid 2D–CMOS microchips for memristive applications. Nature 618, 57–62 (2023).

Goossens, S. et al. Broadband image sensor array based on graphene–CMOS integration. Nat. Photonics 11, 366–371 (2017).

Han, S.-J., Garcia, A. V., Oida, S., Jenkins, K. A. & Haensch, W. Graphene radio frequency receiver integrated circuit. Nat. Commun. 5, 3086 (2014).

2D-experimental pilot line. Graphene Flagship https://graphene-flagship.eu/industrialisation/pilot-line (2023).

Kühne, T. D. et al. CP2K: an electronic structure and molecular dynamics software package - Quickstep: efficient and accurate electronic structure calculations. J. Chem. Phys. 152, 194103 (2020).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865–3868 (1996).

Grimme, S., Antony, J., Ehrlich, S. & Krieg, H. A consistent and accurate ab initio parametrization of density functional dispersion correction (DFT-D) for the 94 elements H-Pu. J. Chem. Phys. 132, 154104 (2010).

Goedecker, S., Teter, M. & Hutter, J. Separable dual-space Gaussian pseudopotentials. Phys. Rev. B 54, 1703–1710 (1996).

Marian, C. M. & Gastreich, M. A systematic theoretical study of molecular Si/N, B/N, and Si/B/N(H) compounds and parameterisation of a force-field for molecules and solids. J. Mol. Struct. 506, 107–129 (2000).

Guidon, M., Hutter, J. & VandeVondele, J. Robust periodic Hartree–Fock exchange for large-scale simulations using Gaussian basis sets. J. Chem. Theory Comput. 5, 3010–3021 (2009).

Guidon, M., Hutter, J. & VandeVondele, J. Auxiliary density matrix methods for Hartree–Fock exchange calculations. J. Chem. Theory Comput. 6, 2348–2364 (2010).

Henkelman, G., Uberuaga, B. P. & Jónsson, H. A climbing image nudged elastic band method for finding saddle points and minimum energy paths. J. Chem. Phys. 113, 9901–9904 (2000).

Chen, X., Mo, T., Huang, B., Liu, Y. & Yu, P. Capacitance properties in Ba0.3Sr0.7Zr0.18Ti0.82O3 thin films on silicon substrate for thin film capacitor applications. Crystals 10, 318 (2020).

Maissel, L. I. & Reinhard, G. (eds). Handbook of Thin Film Technology (McGraw-Hill, 1970).

Acknowledgements

M.L. acknowledges support from the Ministry of Science and Technology of China (grant nos. 2019YFE0124200, 2018YFE0100800) and the National Natural Science Foundation of China (grant nos. 11661131002, 61874075) and the generous baseline funding scheme of the King Abdullah University of Science and Technology. S.D. acknowledges support from the National Science Foundation through the Career Award under grant no. ECCS-2042154, as well as from the National Science Foundation under cooperative agreement DMR-2039351 for the MOCVD growth of the MoS2 samples in the 2D Crystal Consortium Materials Innovation Platform facility at Penn State. D.W., T.K. and T.G. acknowledge support by the European Research Council under grant no. 101055379. The computational results presented have been achieved in part using the Vienna Scientific Cluster. M.L. acknowledges the platform Web Of Talents (https://weboftalents.com) for support on the recruitment of talented students and postdocs.

Author information

Authors and Affiliations

Contributions

M.L. conceived the idea, designed the experiments and supervised the entire investigation. Y.S. fabricated and characterized most of the devices. K.Z. fabricated and characterized the devices with W electrodes. Y.X. and X.L. fabricated and characterized the devices at high temperature. W.Z. and Y.Y. sporadically helped Y.S., K.Z. and Y.X. with the fabrication and electrical characterization tasks. T.F.S. fabricated the all-CVD devices with supervision from S.D. The MOCVD MoS2 used in these devices was grown by N.T. with supervision from J.M.R. D.W. and A.H.B. performed the atomistic calculations, and T.K., T.G. and U.S. supervised them. J.B.R., H.T. and S.P. gave comments on the strengths and weaknesses of previous versions of the manuscript. H.W. provided the wafers containing CMOS circuitry. M.L. and Y.S. wrote the manuscript. All the authors read the manuscript and provided comments.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Zonghoon Lee and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–18 and Tables 1 and 2.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Shen, Y., Zhu, K., Xiao, Y. et al. Two-dimensional-materials-based transistors using hexagonal boron nitride dielectrics and metal gate electrodes with high cohesive energy. Nat Electron 7, 856–867 (2024). https://doi.org/10.1038/s41928-024-01233-w

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-024-01233-w

This article is cited by

-

Beyond the Silicon Plateau: A Convergence of Novel Materials for Transistor Evolution

Nano-Micro Letters (2026)

-

Mechanisms of resistive switching in two-dimensional monolayer and multilayer materials

Nature Materials (2025)

-

Dielectric strength weakening of hexagonal boron nitride nanosheets under mechanical stress

Nature Communications (2025)