Abstract

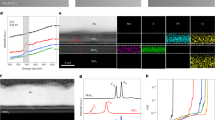

The deposition of a metal oxide layer with good dielectric properties is a critical step in fabricating the gate dielectric of transistors based on two-dimensional semiconductors. However, current techniques for depositing ultrathin metal oxide layers on two-dimensional semiconductors suffer from quality issues that can compromise transistor performance. Here, we show that an ultrathin and uniform native oxide of gallium (Ga2O3) that naturally forms on the surface of liquid metals in an ambient environment can be prepared on the surface of molybdenum disulfide (MoS2) by squeeze-printing and surface-tension-driven methods. The Ga2O3 layer possesses a high dielectric constant of around 30 and equivalent oxide thickness of around 0.4 nm. Due to the good dielectric properties and van der Waals integration, MoS2 transistors with Ga2O3 gate dielectrics exhibit a subthreshold swing down to 60 mV dec−1, an on/off ratio of 108 and a gate leakage down to around 4 × 10−7 A cm−2.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding authors upon reasonable request.

References

Robertson, J. & Wallace, R. M. High-κ materials and metal gates for CMOS applications. Mater. Sci. Eng.: R: Rep. 88, 1–41 (2015).

Helms, C. R. & Deal, B. E. The Physics and Chemistry of SiO2 and the Si-SiO2 Interface (Springer, 1988).

Schuegraf, K. F. & Hu, C. Reliability of thin SiO2. Semicond. Sci. Technol. 9, 989–1004 (1994).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Liu, K. et al. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 4, 906–913 (2021).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Morita, M., Ohmi, T. & Hasegawa, E. Growth of native oxide on a silicon surface. J. Appl. Phys. 68, 1272–1281 (1990).

Ryan, M. P., Williams, D. E., Chater, R. J., Hutton, B. M. & McPhail, D. S. Why stainless steel corrodes. Nature 415, 770–774 (2002).

Zavabeti, A. et al. A liquid metal reaction environment for the room-temperature synthesis of atomically thin metal oxides. Science 358, 332–335 (2017).

Daeneke, T. et al. Liquid metals: fundamentals and applications in chemistry. Chem. Soc. Rev. 47, 4073–4111 (2018).

Syed, N. et al. Printing two-dimensional gallium phosphate out of liquid metal. Nat. Commun. 9, 3618 (2018).

Syed, N. et al. Wafer-sized ultrathin gallium and indium nitride nanosheets through the ammonolysis of liquid metal derived oxides. J. Am. Chem. Soc. 141, 104–108 (2019).

Zavabeti, A. et al. High-mobility p-type semiconducting two-dimensional β-TeO2. Nat. Electron. 4, 277–283 (2021).

Datta, R. S. et al. Flexible two-dimensional indium tin oxide fabricated using a liquid metal printing technique. Nat. Electron. 3, 51–58 (2020).

Messalea, K. A. et al. High-k 2D Sb2O3 made using a substrate-independent and low-temperature liquid-metal-based process. ACS Nano 15, 16067–16075 (2021).

Khan, H. et al. Liquid metal-based synthesis of high performance monolayer SnS piezoelectric nanogenerators. Nat. Commun. 11, 3449 (2020).

Carey, B. J. et al. Wafer-scale two-dimensional semiconductors from printed oxide skin of liquid metals. Nat. Commun. 8, 14482 (2017).

Xing, K. et al. Hydrogen-terminated diamond MOSFETs using ultrathin glassy Ga2O3 dielectric formed by low-temperature liquid metal printing method. ACS Appl. Electron. Mater. 4, 2272–2280 (2022).

Zhang, Y. et al. Liquid-metal-printed ultrathin oxides for atomically smooth 2D material heterostructures. ACS Nano 17, 7929–7939 (2023).

Cabrera, N. Theory of the oxidation of metals. Rep. Prog. Phys. 12, 163 (1949).

Kwon, K. Y. et al. Surface modification of gallium‐based liquid metals: mechanisms and applications in biomedical sensors and soft actuators. Adv. Intell. Syst. 3, 2000159 (2021).

Wurdack, M. et al. Ultrathin Ga2O3 glass: a large‐scale passivation and protection material for monolayer WS2. Adv. Mater. 33, 2005732 (2021).

Zatsepin, D. A. et al. Atomic structure, electronic states, and optical properties of epitaxially grown β-Ga2O3 layers. Superlattices Microstruct. 120, 90–100 (2018).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Jung, Y. et al. Transferred via contacts as a platform for ideal two-dimensional transistors. Nat. Electron. 2, 187–194 (2019).

Yang, X. et al. Highly reproducible van der Waals integration of two-dimensional electronics on the wafer scale. Nat. Nanotechnol. 18, 471–478 (2023).

Kong, L. et al. Wafer-scale and universal van der Waals metal semiconductor contact. Nat. Commun. 14, 1014 (2023).

Dang, W. et al. Ultimate dielectric scaling of 2D transistors via van der Waals metal integration. Nano Res. 15, 1603–1608 (2022).

Bertolazzi, S., Brivio, J. & Kis, A. Stretching and breaking of ultrathin MoS2. ACS Nano 5, 9703–9709 (2011).

Pierret, A. et al. Dielectric permittivity, conductivity and breakdown field of hexagonal boron nitride. Mater. Res. Express 9, 065901 (2022).

McPherson, J., Kim, J., Shanware, A., Mogul, H. & Rodriguez, J. Proposed universal relationship between dielectric breakdown and dielectric constant. In Proc. 2002 International Electron Devices Meeting (IEDM) 633–636 (IEEE, 2002).

Yu, L. et al. Enhancement-mode single-layer CVD MoS2 FET technology for digital electronics. In Proc. 2015 IEEE International Electron Devices Meeting (IEDM) 32.3.1–32.3.4 (IEEE, 2015).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42nm contact pitch and 250 µA/µm drain current. In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) 23.2.1–23.2.4 (IEEE, 2019).

Smets, Q. et al. Sources of variability in scaled MoS2 FETs. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM) 3.1.1–3.1.4 (IEEE, 2020).

Osada, M. & Sasaki, T. The rise of 2D dielectrics/ferroelectrics. APL Mater. 7, 120902 (2019).

Xu, F. et al. Few-layered MnAl2S4 dielectrics for high-performance van der Waals stacked transistors. ACS Appl. Mater. Interfaces 14, 25920–25927 (2022).

Park, J. H. et al. Atomic layer deposition of Al2O3 on WSe2 functionalized by titanyl phthalocyanine. ACS Nano 10, 6888–6896 (2016).

Zou, X. et al. Interface engineering for high-performance top-gated MoS2 field-effect transistors. Adv. Mater. 26, 6255–6261 (2014).

Lin, Y. C. et al. Dielectric material technologies for 2-D semiconductor transistor scaling. IEEE Trans. Electron Devices 70, 1454–1473 (2023).

Moore, M. International Roadmap for Devices and Systems (IEEE, 2022).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Zhang, Y. et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat. Electron. 5, 643–649 (2022).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Chen, T.-A. et al. Wafer-scale single-crystal hexagonal boron nitride monolayers on Cu (111). Nature 579, 219–223 (2020).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Dorow, C. et al. Advancing monolayer 2-D nMOS and pMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. IEEE Trans. Electron Devices 68, 6592–6598 (2021).

Chou, A.-S. et al. High on-current 2D nFET of 390 μA/μm at VDS = 1 V using monolayer CVD MoS2 without intentional doping. In Proc. 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020).

Xiong, X. et al. Demonstration of vertically-stacked CVD monolayer channels: MoS2 nanosheets GAA-FET with Ion > 700 µA/µm and MoS2/WSe2 CFET. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.5.1–7.5.4 (IEEE, 2021).

Wu, X. et al. Dual gate synthetic MoS2 MOSFETs with 4.56µF/cm2 channel capacitance, 320µS/µm Gm and 420 µA/µm Id at 1V Vd/100nm Lg. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.4.1–7.4.4 (IEEE, 2021).

Zhou, C. et al. Low voltage and high on/off ratio field-effect transistors based on CVD MoS2 and ultra high-k gate dielectric PZT. Nanoscale 7, 8695–8700 (2015).

Zheng, X. et al. Patterning metal contacts on monolayer MoS2 with vanishing Schottky barriers using thermal nanolithography. Nat. Electron. 2, 17–25 (2019).

Vu, Q. A. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 031001 (2018).

Lee, G.-H. et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano 9, 7019–7026 (2015).

Kim, S. et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat. Commun. 3, 1011 (2012).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Wang, J. et al. Integration of high-k oxide on MoS2 by using ozone pretreatment for high-performance MoS2 top-gated transistor with thickness-dependent carrier scattering investigation. Small 11, 5932–5938 (2015).

Britnell, L. et al. Electron tunnelling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Gaur, A. et al. Analysis of admittance measurements of MOS capacitors on CVD grown bilayer MoS2. 2D Mater. 6, 035035 (2019).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Liu, H. & Ye, P. D. MoS2 dual-gate MOSFET with atomic-layer-deposited Al2O3 as top-gate dielectric. IEEE Electron Device Lett. 33, 546–548 (2012).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Beckers, A., Jazaeri, F. & Enz, C. Theoretical limit of low temperature subthreshold swing in field-effect transistors. IEEE Electron Device Lett. 41, 276–279 (2020).

Yu, Z. et al. Analyzing the carrier mobility in transition-metal dichalcogenide MoS2 field-effect transistors. Adv. Funct. Mater. 27, 1604093 (2017).

Nourbakhsh, A. et al. 15-nm channel length MoS2 FETs with single- and double-gate structures. In Proc. 2015 Symposium on VLSI Technology (VLSI Technology) T28–T29 (IEEE, 2015).

Yang, Z. et al. Performance limits of the self-aligned nanowire top-gated MoS2 transistors. Adv. Funct. Mater. 27, 1602250 (2017).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Acknowledgements

Z.L. acknowledges support from the National Research Foundation, Singapore, under its Competitive Research Programme (Grant No. NRF-CRP22-2019-0007) and its NRF-ISF joint research program (Grant No. NRF2020-NRF-ISF004-3520). This research is also supported by A*STAR under an AME IRG grant (Project No. A2083c0052) and A*STAR MTC Programmatic Grant (Grant No. M23M2b0056). The microwave microscopy work (S.F. and K.L.) is supported by the Welch Foundation (Grant No. F-1814). The nanoindentation work (Q.F. and J.L) is supported by the Welch Foundation (Grant No. C-1716).

Author information

Authors and Affiliations

Contributions

Z.L. and K.Y. conceived and designed the project. K.Y. performed the OM, AFM, ultraviolet–visible spectroscopy, X-ray photoelectron spectroscopy, device fabrication, electrical measurements and data analysis. Y.H., Y.W., X.C. and Y. Dong contributed to the preparation of focused-ion-beam samples and cross-sectional STEM characterizations. W.Q., Z.H. and Z.Z. performed the DFT calculations. Y.W. performed the STEM, EDS and electron energy loss spectroscopy characterizations. S.F. and K.L. performed the tuning-fork-based microwave impedance microscopy measurements. Q.F. and J.L. performed the indentation measurements. X.Z., T.L. and X.W. provided the wafer-scale MoS2. K.-W.A. helped with the low-temperature measurements. Y. Deng prepared the CVD MoS2 single crystals and performed the Raman measurements. C.Z. commented on the manuscript and helped analyse the data. K.K.-Z. helped revise the manuscript. K.Y. and Z.L. summarized the manuscript. All authors contributed to discussions.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Mohammad Bagher Ghasemian, Yuxuan Cosmi Lin and He Tian for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Table 1 and Figs. 1–40.

Supplementary Video 1

Surface-tension-driven preparation.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Yi, K., Qin, W., Huang, Y. et al. Integration of high-κ native oxides of gallium for two-dimensional transistors. Nat Electron 7, 1126–1136 (2024). https://doi.org/10.1038/s41928-024-01286-x

Received:

Accepted:

Published:

Issue date:

DOI: https://doi.org/10.1038/s41928-024-01286-x

This article is cited by

-

2D computational photodetectors enabling multidimensional optical information perception

Nature Communications (2025)

-

Transferrable, wet-chemistry-derived high-k amorphous metal oxide dielectrics for two-dimensional electronic devices

Nature Communications (2025)

-

2D edge-seeded heteroepitaxy of ultrathin high-κ dielectric CaNb2O6 for 2D field-effect transistors

Nature Communications (2025)

-

Gate stack engineering of two-dimensional transistors

Nature Electronics (2025)

-

A printed gallium oxide dielectric for 2D transistors

Nature Electronics (2024)