Abstract

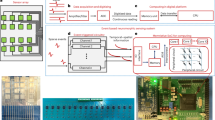

The development of wireless communication technology and the Internet of Things requires radiofrequency communication systems with higher frequencies and faster communication speeds. However, traditional digital processing platforms—which involve high-speed analogue-to-digital converters, intensive data movement and complex digital computation in software-defined radio systems—suffer from high energy consumption and latency. Signal processing in the analogue domain using non-volatile memristive devices can reduce data movement and energy consumption, but the development of system-level designs remains limited. Here we report a radiofrequency signal processing system that is based on analogue in-memory computing within a multicore memristive system-on-a-chip. With the approach, we demonstrate an analogue discrete Fourier transform for spectrum analysis, a mixer-free demodulator for in-phase and quadrature demodulation, and analogue neural networks for radiofrequency transmitter identification and anomaly detection. The memristive system-on-a-chip offers an identification accuracy of over 90% and is up to 6.8 times more energy efficient and up to 6.2 times faster than traditional digital processing platforms.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The datasets for the RF transmitter identification and anomaly detection are available via GitHub at https://github.com/gxhen/LoRa_RFFI/tree/main/Openset_RFFI_TIFS and at https://cores.ee.ucla.edu/downloads/datasets/wisig/. Further data that support other finding of this study are available from the corresponding authors upon reasonable request.

Code availability

The code that supports the operation of the integrated chip for the demonstrated RF application and the plot within this Article is available from the corresponding authors upon reasonable request.

References

He, J., Tian, X., Wei, H., Tian, Y. & He, B. An overview of principles and types of ADC and DAC. J. Phys. Conf. Ser. 2649, 012050 (2023).

Kassri, N., Ennouaary, A., Bah, S. & Baghdadi, H. A review on SDR, spectrum sensing, and CR-based IoT in cognitive radio networks. Int. J. Adv. Comput. Sci. Appl. 12, 6 (2021).

Huang, Y. et al. Memristor-based hardware accelerators for artificial intelligence. Nat. Rev. Electr. Eng. 1, 286–299 (2024).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64 (2015).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Chiu, Y. C. et al. A CMOS-integrated spintronic compute-in-memory macro for secure AI edge devices. Nat. Electron. 6, 534–543 (2023).

Chen, W.-H. et al. CMOS-integrated memristive non-volatile computing-in-memory for AI edge processors. Nat. Electron. 2, 420–428 (2019).

Xue, C.-X. et al. A CMOS-integrated compute-in-memory macro based on resistive random-access memory for AI edge devices. Nat. Electron. 4, 81–90 (2020).

Rao, M. et al. Thousands of conductance levels in memristors integrated on CMOS. Nature 615, 823–829 (2023).

Le Gallo, M. et al. A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference. Nat. Electron. 6, 680–693 (2023).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Wen, T.-H. et al. Fusion of memristor and digital compute-in-memory processing for energy-efficient edge computing. Science 384, 325–332 (2024).

Song, W. et al. Programming memristor arrays with arbitrarily high precision for analog computing. Science 383, 903–910 (2024).

Zhang, W. et al. Edge learning using a fully integrated neuro-inspired memristor chip. Science 381, 1205–1211 (2023).

Wang, C. et al. Scalable massively parallel computing using continuous-time data representation in nanoscale crossbar array. Nat. Nanotechnol. 16, 1079–1085 (2021).

Hung, J.-M. et al. 8-b precision 8-Mb ReRAM compute-in-memory macro using direct-current-free time-domain readout scheme for AI edge devices. IEEE J. Solid-State Circuits 58, 303–315 (2023).

Cai, F. et al. A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. Nat. Electron. 2, 290–299 (2019).

Korkmaz, A., He, C., Katehi, L. P. B., Williams, R. S. & Palermo, S. Design of tunable analog filters using memristive crossbars. In Proc. IEEE International Symposium on Circuits and Systems 1–5 (IEEE, 2021).

He, C., Korkmaz, A., Palermo, S., Williams, R. S. & Katehi, L. P. B. Analog signal processing in high frequency circuits using crossbar configurations. In 2021 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems 116–121 (IEEE, 2021); https://doi.org/10.1109/COMCAS52219.2021.9629041

Mannocci, P., Melacarne, E. & Ielmini, D. An analogue in-memory ridge regression circuit with application to massive MIMO acceleration. IEEE J. Emerg. Sel. Top. Circuits Syst. 12, 952–962 (2022).

Ambrogio, S. et al. Equivalent-accuracy accelerated neural-network training using analogue memory. Nature 558, 60–67 (2018).

Chen, W.-H. et al. A 65nm 1Mb nonvolatile computing-in-memory ReRAM macro with sub-16ns multiply-and-accumulate for binary DNN AI edge processors. In 2018 IEEE International Solid-State Circuits Conference 494–496 (IEEE, 2018); https://doi.org/10.1109/ISSCC.2018.8310400

Xue, C.-X. et al. Embedded 1-Mb ReRAM-based computing-in-memory macro with multibit input and weight for CNN-based AI edge processors. IEEE J. Solid-State Circuits 55, 203–215 (2020).

Zidan, M. A. et al. A general memristor-based partial differential equation solver. Nat. Electron. 1, 411–420 (2018).

Korkmaz, A. et al. Spectral ranking in complex networks using memristor crossbars. IEEE J. Emerg. Sel. Top. Circuits Syst. 13, 357–370 (2023).

Wang, C. et al. Parallel in-memory wireless computing. Nat. Electron. 6, 381–389 (2023).

Zeng, Q. et al. Realizing in-memory baseband processing for ultrafast and energy-efficient 6G. IEEE Internet Things J. 11, 5169–5183 (2024).

Li, C. et al. Analogue signal and image processing with large memristor crossbars. Nat. Electron. 1, 52–59 (2018).

Mohanti, S. et al. AirID: injecting a custom RF fingerprint for enhanced UAV identification using deep learning. In GLOBECOM 2020 – 2020 IEEE Global Communications Conference 1–6 (IEEE, 2020); https://doi.org/10.1109/GLOBECOM42002.2020.9322561

Cai, Z., Wang, Y., Jiang, Q., Gui, G. & Sha, J. Toward intelligent lightweight and efficient UAV identification with RF fingerprinting. IEEE Internet Things J. 11, 26329–26339 (2024).

Sankhe, K. et al. ORACLE: Optimized Radio clAssification through Convolutional neuraL nEtworks. In IEEE INFOCOM 2019 – IEEE Conference on Computer Communications 370–378 (IEEE, 2019); https://doi.org/10.1109/INFOCOM.2019.8737463

Soltanieh, N., Norouzi, Y., Yang, Y. & Karmakar, N. C. A review of radio frequency fingerprinting techniques. IEEE J. Radio Freq. Identif. 4, 222–233 (2020).

Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

Li, C. et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 1, 49–57 (2019).

Kim, H., Mahmoodi, M. R., Nili, H. & Strukov, D. B. 4K-memristor analog-grade passive crossbar circuit. Nat. Commun. 12, 5198 (2021).

Shen, G., Zhang, J., Marshall, A. & Cavallaro, J. R. Towards scalable and channel-robust radio frequency fingerprint identification for LoRa. IEEE Trans. Inf. Forensics Secur. 17, 774–787 (2022).

Hanna, S., Karunaratne, S. & Cabric, D. Open set wireless transmitter authorization: deep learning approaches and dataset considerations. IEEE Trans. Cogn. Commun. Netw. 7, 59–72 (2021).

Ambrogio, S. et al. An analog-AI chip for energy-efficient speech recognition and transcription. Nature 620, 768–775 (2023).

Chabane, L. T., Pham, D.-K. G., Chollet, P. & Desgreys, P. Design method of analog sigmoid function and its approximate derivative. In 2021 XXXVI Conference on Design of Circuits and Integrated Systems 1–5 (IEEE, 2021); https://doi.org/10.1109/DCIS53048.2021.9666181

Kiani, F., Yin, J., Wang, Z., Yang, J. J. & Xia, Q. A fully hardware-based memristive multilayer neural network. Sci. Adv. 7, 4801 (2021).

Geng, C., Sun, Q. & Nakatake, S. An analog CMOS implementation for multi-layer perceptron with ReLU activation. In 2020 9th International Conference on Modern Circuits and Systems Technologies 1–6 (IEEE, 2020); https://doi.org/10.1109/MOCAST49295.2020.9200299

Xie, F. et al. Optimized coherent integration-based radio frequency fingerprinting in Internet of Things. IEEE Internet Things J. 5, 3967–3977 (2018).

Wang, W. & Gan, L. Radio frequency fingerprinting improved by statistical noise reduction. IEEE Trans. Cogn. Commun. Netw. 8, 1444–1452 (2022).

Peng, L., Peng, H., Fu, H. & Liu, M. Channel-robust radio frequency fingerprint identification for cellular uplink LTE devices. IEEE Internet Things J. 11, 17154–17169 (2024).

Xing, Y., Hu, A., Zhang, J., Peng, L. & Wang, X. Design of a channel robust radio frequency fingerprint identification scheme. IEEE Internet Things J. 10, 6946–6959 (2023).

Lu, Q., Yang, Z., Zhang, H., Chen, F. & Xian, H. MRFE: a deep-learning-based multidimensional radio frequency fingerprinting enhancement approach for IoT device identification. IEEE Internet Things J. 11, 30442–30454 (2024).

Swaminathan, R. et al. AMD Instinct TM MI250X accelerator enabled by elevated fanout bridge advanced packaging architecture. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023); https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185224

Jouppi, N. et al. TPU v4: an optically reconfigurable supercomputer for machine learning with hardware support for embeddings. In Proc. 50th Annual International Symposium on Computer Architecture 1–14 (ACM, 2023); https://doi.org/10.1145/3579371.3589350

Choquette, J., Gandhi, W., Giroux, O., Stam, N. & Krashinsky, R. NVIDIA A100 tensor core GPU: performance and innovation. IEEE Micro 41, 29–35 (2021).

Fryza, T. & Mego, R. Power consumption of multicore digital signal processor: theoretical analysis and real applications. In 2014 IEEE 23rd International Symposium on Industrial Electronics 1894–1898 (IEEE, 2014); https://doi.org/10.1109/ISIE.2014.6864904

Agarwal, A. et al. A 320mV-to-1.2V on-die fine-grained reconfigurable fabric for DSP/media accelerators in 32nm CMOS. In 2010 IEEE International Solid-State Circuits Conference 328–329 (IEEE, 2010); https://doi.org/10.1109/ISSCC.2010.5433903

Acknowledgements

Research was sponsored by the Army Research Laboratory and was accomplished under Cooperative Agreement Number W911NF-23–2–0014 (Q.X.), Office of Naval Research (N00014-23-1-2021, Q.X.), and the Texas A&M University System’s Chancellor’s Research Initiative (CRI) (L.K.). The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Army Research Laboratory or the US Government. The US Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein.

Author information

Authors and Affiliations

Contributions

Q.X. and L.K. conceived and led the project. Y.H. and C.H. conducted the experimental and simulation work with help from Y.L. Q.X., N.G., J.J.Y. and M.H. contributed to the evaluation kit (hardware and software). Y.H., C.H., Q.X. and L.K. wrote the article. All authors edited the paper before submission.

Corresponding authors

Ethics declarations

Competing interests

Q.X. and J.J.Y. are co-founders and paid consultants of TetraMem. The other authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Yixiang Li, Zaichen Zhang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Notes 1–9.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Huang, Y., He, C., Ling, Y. et al. Radiofrequency signal processing with a memristive system-on-a-chip. Nat Electron 8, 587–596 (2025). https://doi.org/10.1038/s41928-025-01409-y

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-025-01409-y

This article is cited by

-

Event-based neuromorphic sensing system with flexible haptic sensors and a memristive system on a chip

Nature Sensors (2026)

-

Memristive cellular neural networks for fast in-pixel computing

Nature Electronics (2026)

-

Memristor-based nonlinear neural dynamics with a step-variable edge learning scheme for device non-idealities

Nonlinear Dynamics (2026)