Abstract

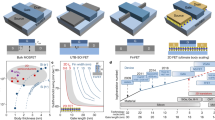

Gate stack engineering has helped enable aggressive device scaling in silicon complementary metal–oxide–semiconductor technology. Two-dimensional (2D) materials are a potential replacement for silicon in next-generation electronics. However, creating gate stacks that are capable of effective and reliable channel control with such materials is inherently challenging owing to the lack of compatible dielectrics and fabrication methods. Here we explore the development of gate stack engineering technologies for two-dimensional transistors. We benchmark key performance metrics for two-dimensional metal–oxide–semiconductor gate stacks against current silicon-based technologies, as well as the targets set by the International Roadmap for Devices and Systems. We also highlight recent advances in ferroelectric-embedded gate stacks, which offer additional functionalities and could be of use in the development of high-speed non-volatile memories and logic-in-memory devices, as well as low-power transistors. Finally, we consider the technical challenges that need to be addressed to develop advanced electronic technologies based on two-dimensional transistors.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Wang, S. et al. Two-dimensional devices and integration towards the silicon lines. Nat. Mater. 21, 1225–1239 (2022).

Kim, K. S. et al. The future of two-dimensional semiconductors beyond Moore’s law. Nat. Nanotechnol. 19, 895–906 (2024).

Ieong, M., Doris, B., Kedzierski, J., Rim, K. & Yang, M. Silicon device scaling to the sub-10-nm regime. Science 306, 2057–2060 (2004).

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat. Electron. 1, 442–450 (2018).

Atalla, M. M., Tannenbaum, E. & Scheibner, E. J. Stabilization of silicon surfaces by thermally grown oxides. Bell Syst. Tech. J. 38, 749–783 (1959).

Mistry, K. et al. A 45 nm logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In Proc. 2007 IEEE International Electron Devices Meeting (IEDM) 247–250 (IEEE, 2007).

Robertson, J. & Wallace, R. M. High-k materials and metal gates for CMOS applications. Mater. Sci. Eng. R 88, 1–41 (2015).

Nowak, E. J. et al. Turning silicon on its edge [double gate CMOS/FinFET technology]. IEEE Circuits Devices Mag. 20, 20–31 (2004).

Yu, B. et al. FinFET scaling to 10 nm gate length. In Proc. 2002 International Electron Devices Meeting (IEDM) 251–254 (IEEE, 2002).

Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proc. 2017 IEEE Symposium on VLSI Technology T230–T231 (IEEE, 2017).

Uchida, K. et al. Experimental study on carrier transport mechanism in ultrathin-body SOI nand p-MOSFETs with SOI thickness less than 5 nm. In Proc. 2002 International Electron Devices Meeting (IEDM) 47–50 (IEEE, 2002).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

The International Roadmap for Devices and Systems (IRDS) 2022 edn (IEEE, 2022).

Lee, C.-H. et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol. 9, 676–681 (2014).

Lee, D. et al. Remote modulation doping in van der Waals heterostructure transistors. Nat. Electron. 4, 664–670 (2021).

Kim, Y. H. et al. Boltzmann switching MoS2 metal–semiconductor field-effect transistors enabled by monolithic-oxide-gapped metal gates at the Schottky–Mott limit. Adv. Mater. 36, 2314274 (2024).

Yan, R.-H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710 (1992).

Frank, D. J., Taur, Y. & Wong, H.-S. P. Generalized scale length for two-dimensional effects in MOSFETs. IEEE Electron Device Lett. 19, 385–387 (1998).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Naylor, C. H. et al. 2D materials in the BEOL. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023).

Thean, A. et al. Low-thermal-budget BEOL-compatible beyond-silicon transistor technologies for future monolithic-3D compute and memory applications. In Proc. 2022 International Electron Devices Meeting (IEDM) 12.2.1-12.2.4 (IEEE, 2022).

Guan, S.-X. et al. Monolithic 3D integration of back-end compatible 2D material FET on Si FinFET. npj 2D Mater. Appl. 7, 9 (2023).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Tong, L. et al. 2D materials–based homogeneous transistor-memory architecture for neuromorphic hardware. Science 373, 1353–1358 (2021).

Hoang, A. T. et al. Low-temperature growth of MoS2 on polymer and thin glass substrates for flexible electronics. Nat. Nanotechnol. 18, 1439–1447 (2023).

Zhu, J. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nat. Nanotechnol. 18, 456–463 (2023).

Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 3, 588–597 (2020).

Yang, F. et al. Emerging opportunities for ferroelectric field-effect transistors: integration of 2D materials. Adv. Funct. Mater. 34, 2310438 (2024).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Neamen, D. A. & Biswas, D. Semiconductor Physics and Devices (McGraw-Hill, 2011).

Cao, W., Kang, J., Liu, W. & Banerjee, K. A compact current–voltage model for 2D semiconductor based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect. IEEE Trans. Electron Devices 61, 4282–4290 (2014).

Kim, H. G. & Lee, H.-B.-R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Vu, Q. A. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 031001 (2018).

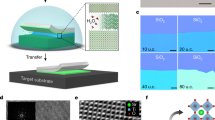

Liu, K. et al. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 4, 906–913 (2021). This article shows high-quality vdW dielectric integration for 2D transistors through the standard evaporation method.

Chen, J. et al. Vertically grown ultrathin Bi2SiO5 as high-κ single-crystalline gate dielectric. Nat. Commun. 14, 4406 (2023).

Yin, L. et al. High-κ monocrystalline dielectrics for low-power two-dimensional electronics. Nat. Mater. 24, 197–204 (2025).

Xu, W. et al. Single-crystalline high-κ GdOCl dielectric for two-dimensional field-effect transistors. Nat. Commun. 15, 9469 (2024).

Söll, A. et al. High-κ wide-gap layered dielectric for two-dimensional van der Waals heterostructures. ACS Nano 18, 10397–10406 (2024).

Mleczko, M. J. et al. HfSe2 and ZrSe2: two-dimensional semiconductors with native high-κ oxides. Sci. Adv. 3, e1700481 (2024).

Jin, Y. et al. Controllable oxidation of ZrS2 to prepare high-κ, single-crystal m-ZrO2 for 2D electronics. Adv. Mater. 35, 2212079 (2023).

Lai, S. et al. HfO2/HfS2 hybrid heterostructure fabricated via controllable chemical conversion of two-dimensional HfS2. Nanoscale 10, 18758–18766 (2018).

Luo, P. et al. Molybdenum disulfide transistors with enlarged van der Waals gaps at their dielectric interface via oxygen accumulation. Nat. Electron. 5, 849–858 (2022).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Zhang, Y. et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat. Electron. 5, 643–649 (2022). This article reports the integration of a single-crystalline vdW-oxidized dielectric with ultrathin equivalent oxide thickness in a monolithic manner.

Kang, T. et al. High-κ dielectric (HfO2)/2D semiconductor (HfSe2) gate stack for low-power steep-switching computing devices. Adv. Mater. 36, 2312747 (2024).

Huang, J.-K. et al. Crystalline complex oxide membrane: sub-1 nm CET dielectrics for 2D transistors. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.6.1–7.6.4 (IEEE, 2022).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022). This article presents the delamination and lamination of high-k perovskite film to form a quasi-vdW gate stack.

Yang, A. J. et al. van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Zeng, D. et al. Single-crystalline metal-oxide dielectrics for top-gate 2D transistors. Nature 632, 788–794 (2024).

Yi, K. et al. Integration of high-κ native oxides of gallium for two-dimensional transistors. Nat. Electron. 7, 1126–1136 (2024).

Wang, L. et al. A general one-step plug-and-probe approach to top-gated transistors for rapidly probing delicate electronic materials. Nat. Nanotechnol. 17, 1206–1213 (2022).

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023).

Zhu, C.-Y. et al. Magnesium niobate as a high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 7, 1137–1146 (2024).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Zhang, L. et al. Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses. Nat. Electron. 7, 662–670 (2024).

Park, J. H. et al. Atomic layer deposition of Al2O3 on WSe2 functionalized by titanyl phthalocyanine. ACS Nano 10, 6888–6896 (2016).

Zou, X. et al. Interface engineering for high-performance top-gated MoS2 field-effect transistors. Adv. Mater. 26, 6255–6261 (2014).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023). This article highlights that a vdW-seeded dielectric can be used to simultaneously accomplish EOT scaling and low Dit.

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Wang, Y. et al. Ultraflat single-crystal hexagonal boron nitride for wafer-scale integration of a 2D-compatible high-κ metal gate. Nat. Mater. 23, 1495–1501 (2024).

Zou, X. et al. Dielectric engineering of a boron nitride/hafnium oxide heterostructure for high-performance 2D field effect transistors. Adv. Mater. 28, 2062–2069 (2016).

Kwak, I. et al. Low interface trap density in scaled bilayer gate oxides on 2D materials via nanofog low temperature atomic layer deposition. Appl. Surf. Sci. 463, 758–766 (2019).

Ko, J.-S. et al. Achieving 1-nm-scale equivalent oxide thickness top gate dielectric on monolayer transition metal dichalcogenide transistors with CMOS-friendly approaches. In Proc. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024). This paper shows that a non-vdW seeding layer with CMOS compatibility facilitates deposition of a high-k dielectric in top-gate geometry.

Lee, T.-E. et al. Nearly ideal subthreshold swing in monolayer MoS2 top-gate nFETs with scaled EOT of 1 nm. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.4.1–7.4.4 (IEEE, 2022).

Lan, H.-Y., Appenzeller, J. & Chen, Z. Dielectric interface engineering for high-performance monolayer MoS2 transistors via hBN interfacial layer and Ta seeding. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.7.1–7.7.4 (IEEE, 2022).

Chung, Y.-Y. et al. First demonstration of GAA monolayer-MoS2 nanosheet nFET with 410 μA/μm Id 1 V Vd at 40 nm gate length. In Proc. 2022 International Electron Devices Meeting (IEDM) 34.5.1–34.5.4 (IEEE, 2022). This article demonstrates that GAA, an advanced 3D gate architecture, is applicable to MoS2 FET.

Wu, X. et al. Dual gate synthetic MoS2 MOSFETs with 4.56µF/cm2 channel capacitance, 320µS/µm Gm and 420 µA/µm Id at 1 V Vd/100 nm Lg. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.4.1–7.4.4 (IEEE, 2021).

Lin, D. et al. Dual gate synthetic WS2 MOSFETs with 120μS/μm Gm 2.7μF/cm2 capacitance and ambipolar channel. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM) 3.6.1–3.6.4 (IEEE, 2020).

Lin, Y.-S., Cheng, P.-H., Huang, K.-W., Lin, H.-C. & Chen, M.-J. Atomic layer deposition of sub-10 nm high-k gate dielectrics on top-gated MoS2 transistors without surface functionalization. Appl. Surf. Sci. 443, 421–428 (2018).

Xu, F. et al. Few-layered MnAl2S4 dielectrics for high-performance van der Waals stacked transistors. ACS Appl. Mater. Interfaces 14, 25920–25927 (2022).

Chamlagain, B. et al. Thermally oxidized 2D TaS2 as a high-κ gate dielectric for MoS2 field-effect transistors. 2D Mater. 4, 031002 (2017).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature 616, 66–72 (2023).

Zhang, Y. et al. Liquid-metal-printed ultrathin oxides for atomically smooth 2D material heterostructures. ACS Nano 17, 7929–7939 (2023).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Tang, J. et al. Low-power 2D gate-all-around logics via epitaxial monolithic 3D integration. Nat. Mater. 24, 519–526 (2025).

Chung, Y.-Y. et al. Stacked channel transistors with 2D materials: an integration perspective. In Proc. 2024 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024).

Xiong, X. et al. Demonstration of vertically-stacked CVD monolayer channels: MoS2 nanosheets GAA-FET with Ion>700 µA/µm and MoS2/WSe2 CFET. In Proc. 2021 International Electron Devices Meeting (IEDM) 7.5.1–7.5.4 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Jiang, J. et al. Yttrium-doping-induced metallization of molybdenum disulfide for ohmic contacts in two-dimensional transistors. Nat. Electron. 7, 545–556 (2024).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Kim, J. et al. Gate structuring on bilayer transition metal dichalcogenides enables ultrahigh current density. Preprint at Research Square https://doi.org/10.21203/rs.3.rs-4632503/v1 (2024).

Cheng, Z. et al. How to report and benchmark emerging field-effect transistors. Nat. Electron. 5, 416–423 (2022).

Zhang, X.-W. et al. MoS2 field-effect transistors with lead zirconate-titanate ferroelectric gating. IEEE Electron Device Lett. 36, 784–786 (2015).

Ko, C. et al. Ferroelectrically gated atomically thin transition-metal dichalcogenides as nonvolatile memory. Adv. Mater. 28, 2923–2930 (2016).

Lipatov, A., Sharma, P., Gruverman, A. & Sinitskii, A. Optoelectrical molybdenum disulfide (MoS2)—ferroelectric memories. ACS Nano 9, 8089–8098 (2015).

Huang, K. et al. Hf0.5Zr0.5O2 ferroelectric embedded dual-gate MoS2 field effect transistors for memory merged logic applications. IEEE Electron Device Lett. 41, 1600–1603 (2020).

Ning, H. et al. An in-memory computing architecture based on a duplex two-dimensional material structure for in situ machine learning. Nat. Nanotechnol. 18, 493–500 (2023).

Zhang, S. et al. Low voltage operating 2D MoS2 ferroelectric memory transistor with Hf1-xZrxO2 gate structure.NNanoscale Res. Lett. 15, 157 (2020).

Gao, J. et al. Multifunctional MoTe2 Fe-FET enabled by ferroelectric polarization-assisted charge trapping. Adv. Funct. Mater. 32, 2110415 (2022).

Xian, J. et al. Experimental demonstration of HfO2-based ferroelectric FET with MoS2 channel for high-density and low-power memory application. In Proc. 2021 Silicon Nanoelectronics Workshop (SNW) 1–2 (IEEE, 2021).

Huo, J. et al. Stacked HZO/α-In2Se3 ferroelectric dielectric/semiconductor FET with ultrahigh speed and large memory window. IEEE Trans. Electron Devices 70, 3071–3075 (2023).

Lee, T.-E. et al. High-endurance MoS2 FeFET with operating voltage less than 1 V for eNVM in scaled CMOS technologies. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023). This article shows a realization of a top-gate MoS2 FE-FET with reliability and low operating voltage using a non-vdW seeding layer.

Lu, T. et al. Two-dimensional fully ferroelectric-gated hybrid computing-in-memory hardware for high-precision and energy-efficient dynamic tracking. Sci. Adv. 10, eadp0174 (2024).

Liu, X. et al. Post-CMOS compatible aluminum scandium nitride/2D channel ferroelectric field-effect-transistor memory. Nano Lett. 21, 3753–3761 (2021).

Kim, K.-H. et al. Scalable CMOS back-end-of-line-compatible AlScN/two-dimensional channel ferroelectric field-effect transistors. Nat. Nanotechnol. 18, 1044–1050 (2023).

Lee, H. S. et al. MoS2 nanosheets for top-gate nonvolatile memory transistor channel. Small 8, 3111–3115 (2012).

Liu, L. et al. Electrical characterization of MoS2 field-effect transistors with different dielectric polymer gate. AIP Adv. 7, 065121 (2017).

Wang, X. et al. Ferroelectric FET for nonvolatile memory application with two-dimensional MoSe2 channels. 2D Mater. 4, 025036 (2017).

Huang, W. et al. Gate-coupling-enabled robust hysteresis for nonvolatile memory and programmable rectifier in van der Waals ferroelectric heterojunctions. Adv. Mater. 32, 1908040 (2020).

Singh, P. et al. Two-dimensional CIPS-InSe van der Waal heterostructure ferroelectric field effect transistor for nonvolatile memory applications. ACS Nano 16, 5418–5426 (2022).

Park, S., Lee, D., Kang, J., Choi, H. & Park, J.-H. Laterally gated ferroelectric field effect transistor (LG-FeFET) using α-In2Se3 for stacked in-memory computing array. Nat. Commun. 14, 6778 (2023).

Wang, X. et al. Van der Waals engineering of ferroelectric heterostructures for long-retention memory. Nat. Commun. 12, 1109 (2021).

Jiang, X. et al. Ferroelectric field-effect transistors based on WSe2/CuInP2S6 heterostructures for memory applications. ACS Appl. Electron Mater. 3, 4711–4717 (2021).

Si, M., Liao, P.-Y., Qiu, G., Duan, Y. & Ye, P. D. Ferroelectric field-effect transistors based on MoS2 and CuInP2S6 two-dimensional van der Waals heterostructure. ACS Nano 12, 6700–6705 (2018).

Kim, K.-H., Karpov, I., Olsson, R. H. & Jariwala, D. Wurtzite and fluorite ferroelectric materials for electronic memory. Nat. Nanotechnol. 18, 422–441 (2023).

Pradhan, D. K. et al. A scalable ferroelectric non-volatile memory operating at 600 °C. Nat. Electron. 7, 348–355 (2024).

Ni, K. et al. Critical role of interlayer in Hf0.5Zr0.5O2 ferroelectric FET nonvolatile memory performance. IEEE Trans. Electron Devices 65, 2461–2469 (2018).

Tian, F. et al. Impact of interlayer and ferroelectric materials on charge trapping during endurance fatigue of FeFET with TiN/HfxZr1−xO2/interlayer/Si (MFIS) gate structure. IEEE Trans. Electron Devices 68, 5872–5878 (2021).

Mittmann, T. et al. Impact of oxygen vacancy content in ferroelectric HZO films on the device performance. In Proc. 2020 International Electron Devices Meeting (IEDM) 18.4.1–18.4.4 (IEEE, 2020).

Luo, Z.-D., Yang, M.-M., Liu, Y. & Alexe, M. Emerging opportunities for 2D semiconductor/ferroelectric transistor-structure devices. Adv. Mater. 33, 2005620 (2021).

Cao, W. & Banerjee, K. Is negative capacitance FET a steep-slope logic switch? Nat. Commun. 11, 196 (2020).

Wang, X. et al. Van der Waals negative capacitance transistors. Nat. Commun. 10, 3037 (2019).

Liu, X. et al. MoS2 negative-capacitance field-effect transistors with subthreshold swing below the physics limit. Adv. Mater. 30, 1800932 (2018).

Cho, H. et al. 5 nm ultrathin crystalline ferroelectric P(VDF-TrFE)-brush tuned for hysteresis-free sub 60 mV dec−1 negative-capacitance transistors. Adv. Mater. 35, 2300478 (2023).

Wang, X. et al. Two-dimensional negative capacitance transistor with polyvinylidene fluoride-based ferroelectric polymer gating. npj 2D Mater. Appl 1, 38 (2017).

Wang, Y. et al. Record-low subthreshold-swing negative-capacitance 2D field-effect transistors. Adv. Mater. 32, 2005353 (2020).

Guo, X. et al. Optimization of subthreshold swing and hysteresis in Hf0.5Zr0.5O2-based MoS2 negative capacitance field-effect transistors by modulating capacitance matching. ACS Appl. Mater. Interfaces 15, 31617–31626 (2023).

Tu, L. et al. Ultrasensitive negative capacitance phototransistors. Nat. Commun. 11, 101 (2020).

Yu, Z. et al. Negative capacitance 2D MoS2 transistors with sub-60mV/dec subthreshold swing over 6 orders, 250 μA/μm current density, and nearly-hysteresis-free. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 23.6.1–23.6.4 (IEEE, 2017).

Song, X., Liu, L. & Xu, J. MoS2 negative-capacitance transistors with steep slope and negligible hysteresis by using monolayer Al1−xZrxOy as gate dielectric plus NH3-plasma treatment. Appl. Surf. Sci. 576, 151882 (2022).

Nourbakhsh, A., Zubair, A., Joglekar, S., Dresselhaus, M. & Palacios, T. Subthreshold swing improvement in MoS2 transistors by the negative-capacitance effect in a ferroelectric Al-doped-HfO2/HfO2 gate dielectric stack. Nanoscale 9, 6122–6127 (2017).

Si, M. et al. Sub-60 mV/dec ferroelectric HZO MoS2 negative capacitance field-effect transistor with internal metal gate: the role of parasitic capacitance. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 23.5.1–23.5.4 (IEEE, 2017).

Lin, C.-Y. et al. Integration of freestanding hafnium zirconium oxide membranes into two-dimensional transistors as a high-κ ferroelectric dielectric. Nat. Electron. 8, 560–570 (2025).

Song, S. et al. Negative capacitance field-effect transistors based on ferroelectric AlScN and 2D MoS2. Appl. Phys. Lett. 123, 183501 (2023).

Quan, H., Meng, D., Ma, X. & Qiu, C. Eliminating ferroelectric hysteresis in all-two-dimensional gate-stack negative-capacitance transistors. ACS Appl. Mater. Interfaces 15, 45076–45082 (2023).

Bao, R. et al. Multiple-Vt solutions in nanosheet technology for high performance and low power applications. In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) 11.2.1–11.2.4 (IEEE, 2019).

Yao, J. et al. Record 7(N) + 7(P) multiple VTs demonstration on GAA Si nanosheet n/pFETs using WFM-less direct interfacial La/Al-dipole technique. In Proc. 2022 International Electron Devices Meeting (IEDM) 34.2.1–34.2.4 (IEEE, 2022).

Bae, G. et al. 3 nm GAA technology featuring multi-bridge-channel FET for low power and high performance applications. In Proc. 2018 International Electron Devices Meeting (IEDM) 28.7.1–28.7.4 (IEEE, 2018).

Park, J. et al. First demonstration of 3-dimensional stacked FET with top/bottom source-drain isolation and stacked n/p metal gate. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Xi, F. et al. High-performance monolayer-2D stacked nanosheet FETs with high ION ~ 451 μA/μm and ION/IOFF > 109. In Proc. 2024 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024).

Demuynck, S. et al. Monolithic complementary field effect transistors (CFET) demonstrated using middle dielectric isolation and stacked contacts. In Proc. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024).

Mertens, H. et al. Nanosheet-based complementary field-effect transistors (CFETs) at 48 nm gate pitch, and middle dielectric isolation to enable CFET inner spacer formation and multi-Vt patterning. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023).

Yu, E., Lyu, X., Si, M., Ye, P. D. & Roy, K. Interfacial layer engineering in sub-5-nm HZO: enabling low-temperature process, low-voltage operation, and high robustness. IEEE Trans. Electron Devices 70, 2962–2969 (2023).

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, 88–94 (2023).

Kwon, J. et al. 200-mm-wafer-scale integration of polycrystalline molybdenum disulfide transistors. Nat. Electron. 7, 356–364 (2024).

Dorow, C. J. et al. Exploring manufacturability of novel 2D channel materials: 300 mm wafer-scale 2D NMOS & PMOS using MoS2, WS2, & WSe2. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In Proc. 2021 International Electron Devices Meeting (IEDM) 7.2.1–7.2.4 (IEEE, 2021).

Wang, Y. et al. p-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61–66 (2022).

Hung, T. Y. T. et al. pMOSFET with CVD-grown 2D semiconductor channel enabled by ultra-thin and fab-compatible spacer doping. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.3.1–7.3.4 (IEEE, 2022).

Li, W. et al. High-performance CVD MoS2 transistors with self-aligned top-gate and Bi contact. In Proc. 2021 International Electron Devices Meeting (IEDM) 37.3.1–37.3.4 (IEEE, 2021).

O’Brien, K. P. et al. Process integration and future outlook of 2D transistors. Nat. Commun. 14, 6400 (2023).

Acknowledgements

This Review was supported by the National Research Foundation of Korea (NRF) (grant nos. 2023R1A2C3005923, RS-2023-00258309 and 2022M3H4A1A01010280). C.-H.L. acknowledges the support from BK21 FOUR programme of the Education and Research Program for Future ICT Pioneers, Seoul National University (SNU) in 2024, Creative-Pioneering Researchers Program, New Faculty Startup Fund from SNU, and SNU Electrical Power Research Institute (SEPRI). J.L. acknowledges support from the Institute of Information & Communications Technology Planning & Evaluation (IITP) under the Artificial Intelligence Semiconductor Support Programme to Nurture the Best Talents (IITP-2023-RS-2023-00256081) grant funded by the Korea government (MSIT).

Author information

Authors and Affiliations

Contributions

C.-H.L. conceptualized and structured the overall paper. C.-H.L. and Y.H.K. wrote the main body of the paper. D.H., J.P. and W.H. provided insights on future technological directions from an industrial perspective. Donghun Lee, G.W. J.L. and Donghyun Lee contributed to analysing previous research, organizing the figures and partially to the writing.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Jing-Kai Huang, Kailang Liu and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, Y.H., Lee, D., Huh, W. et al. Gate stack engineering of two-dimensional transistors. Nat Electron 8, 770–783 (2025). https://doi.org/10.1038/s41928-025-01448-5

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-025-01448-5