# Impact of doping and channel inhomogeneities on the stability of industrially fabricated WS<sub>2</sub> FETs

L. Panarella<sup>1,2</sup>✉, B. Kaczer<sup>2</sup>, Q. Smets<sup>2</sup>, T. Nuytten<sup>2</sup>, B. Van Troeye<sup>2</sup>, S. Tyaginov<sup>2</sup>, P. Saraza-Canflanca<sup>2</sup>, T. Grasser<sup>3</sup>, C. Lockhart de la Rosa<sup>2</sup>, G. S. Kar<sup>2</sup> & V. Afanas'ev<sup>1,2</sup>

We report doping-dependent charge trapping in WS<sub>2</sub> field-effect transistors fabricated on a 300 mm wafer. In particular, higher *n*-type doping—associated with smaller channel areas—correlates with an increased density of active defects. This behavior explains the asymmetric threshold voltage degradation observed in large-area ambipolar devices, where the *n*-branch consistently shifts more than the *p*-branch under gate bias stress (by a factor of ~3). Through electrical characterization and photoluminescence mapping, we attribute this asymmetry to process-induced inhomogeneities in the WS<sub>2</sub> layer and its chemical environment, which lead to enhanced *n*-type doping at the channel center relative to the edges. The non-uniform doping profile and conduction of the 2D channel are then captured using an equivalent circuit model that quantitatively reproduces the observed degradation asymmetry and corroborates our interpretation. These results have important implications for the development of large-scale 2D semiconductor transistors, highlighting the impact of unintentional process-induced doping and channel heterogeneity on device performance and reliability.

Although the performance of as-fabricated two-dimensional field-effect transistors (2D FETs) has advanced considerably in recent years<sup>1–5</sup>, most prototypes still exhibit poor threshold voltage stability and significant long-term degradation<sup>6–11</sup>. This is primarily due to a high density of defects in the gate oxide, which can trap or release charge carriers and electrostatically disturb the current flow along the channel<sup>12,13</sup>. To mitigate these issues, novel dielectric materials are investigated in combination with commonly used 2D semiconductors, aiming to engineer high-quality interfaces despite the challenges of depositing dielectrics on top of 2D van der Waals layers<sup>14–18</sup>.

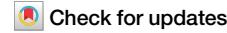

While oxide defects are widely recognized as the main contributors to threshold voltage instability, the critical role of the 2D channel's electrical properties is often overlooked. First, the alignment of the channel Fermi level with the energy states of the oxide defects determines whether these traps are energetically accessible to carriers<sup>12,19,20</sup>. Second, the pronounced electronic inhomogeneities commonly observed in 2D materials (Fig. 1) are expected to force carriers into preferential conduction pathways<sup>21–24</sup>, leading to spatially uneven interactions with trap states and exacerbating variability in device behavior. Finally, unintentional doping of the channel can originate from its dielectric environment. For instance, high concentrations of impurities such as carbon or hydrogen/water, as well as defects like oxygen vacancies, can create an electron-rich environment that facilitates charge transfer to the 2D channel and shifts its Fermi level<sup>25,26</sup>. At the same time, some of these chemical species have also been shown to introduce mid-gap

states, potentially acting as additional charge traps<sup>10,27</sup>. A comprehensive understanding of the intricate interplay between carrier trapping, doping, and non-uniform transport—as well as the resulting degradation mechanisms such as bias temperature instability (BTI), hysteresis, and random telegraph noise (RTN)—is essential for achieving reliable device operation and advancing 2D electronics toward commercial viability.

In this work, we present a detailed analysis of the doping-dependent BTI in back-gated WS<sub>2</sub> FETs (1–2 layers thick) fabricated on a 300 mm wafer<sup>1,28</sup>. First, we use photoluminescence (PL) spectroscopy on as-fabricated devices to correlate the transistor's threshold voltage with the excitonic and trionic peak features of WS<sub>2</sub>, and to map spatial inhomogeneities in the channel's electronic properties. Second, we investigate the BTI-induced threshold voltage shift as a function of stress gate voltage, stress duration, and device dimensions. Third, we compare the threshold voltage shifts in the *n*- and *p*-branches ( $V_{t,n}$  and  $V_{t,p}$ , respectively) of large-area ambipolar devices under identical stress conditions, consistently observing an asymmetry across all examined samples (i.e.,  $|\Delta V_{t,n}| > |\Delta V_{t,p}|$ ). Finally, we employ an equivalent circuit model based on a transistor network to emulate the 2D channel inhomogeneities revealed by PL mapping and to explain the systematically larger  $V_{t,n}$  shifts relative to  $V_{t,p}$ <sup>29</sup>. Our findings indicate that higher *n*-type doping levels are associated with an increased number of active traps. As a result, carriers interact with more defects along the *n*-doped domains that form the electron conduction path, leading to stronger

<sup>1</sup>KU Leuven, Heverlee, Belgium. <sup>2</sup>imec, Heverlee, Belgium. <sup>3</sup>Institute for Microelectronics (TU Wien), Vienna, Austria. ✉e-mail: [luca.panarella@imec.be](mailto:luca.panarella@imec.be)

degradation in the *n*-branch. Overall, these results advance the understanding of how charge trapping, doping, and channel non-uniformities affect the performance and long-term stability of 2D FETs.

## Results

### Dependence of doping level on channel area

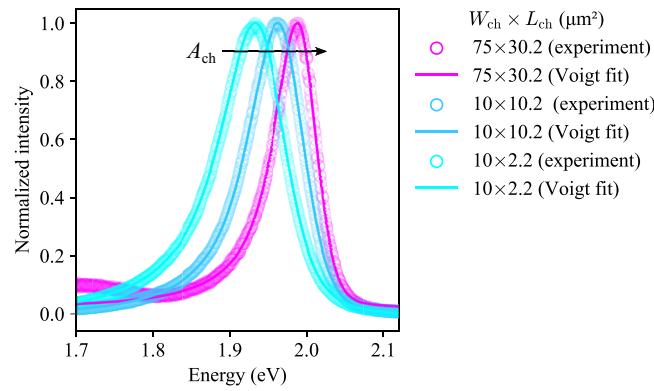

The transfer characteristics of 300-mm-integrated WS<sub>2</sub> FETs (Fig. 2a) with varying channel lengths ( $L_{\text{ch}}$ ) and widths ( $W_{\text{ch}}$ ) exhibit a pronounced dependence of threshold voltage on device dimensions (Fig. 2b). Specifically, smaller channel areas ( $A_{\text{ch}}$ ) yield increasingly negative threshold voltages, indicative of enhanced *n*-type doping. This behavior is unusual and cannot be explained by simple geometrical considerations. In conventional scaling, transistors with narrower  $W_{\text{ch}}$  are expected to exhibit the same width-normalized current density, and devices with shorter  $L_{\text{ch}}$  should display higher current but similar threshold voltage (i.e.,  $I_D \propto W_{\text{ch}}/L_{\text{ch}}$ ), provided that short-channel effects do not occur ( $L_{\text{ch}} \gtrsim 100$  nm). Since this is not the case for our devices, we attribute the threshold voltage dependence on  $A_{\text{ch}}$  to process-induced dopant inhomogeneity across FETs of different sizes<sup>30,31</sup>. Notably, because a uniform WS<sub>2</sub> layer is grown and capped across the wafer prior to any device patterning (see the “Methods” section), the observed doping variability likely does not stem from the growth or capping process, but instead arises during or after active patterning (e.g., due to water intercalation<sup>32</sup>).

**Fig. 1 | 3D Visualization of CBM and VBM fluctuations.** 3D isometric visualization of conduction band minimum (CBM, blue) and valence band maximum (VBM, red) surfaces in a 2D semiconductor, showing spatial inhomogeneities modeled as narrow Gaussian potential fluctuations.

Another key observation emerging from Fig. 2b is that WS<sub>2</sub> FETs with large-area channels ( $L_{\text{ch}}, W_{\text{ch}} \gtrsim 10$   $\mu\text{m}$ ) not only exhibit more positive threshold voltages but also display ambipolar behavior. At negative gate biases, the Fermi level shifts toward the valence band maximum (VBM), resulting in hole accumulation and the emergence of a *p*-type conduction branch. Conversely, positive gate voltages shift the Fermi level toward the conduction band minimum (CBM), leading to electron accumulation and the appearance of the *n*-branch. In the case of small-area devices, the threshold voltage becomes so negative that the *p*-branch falls outside the measurement window.

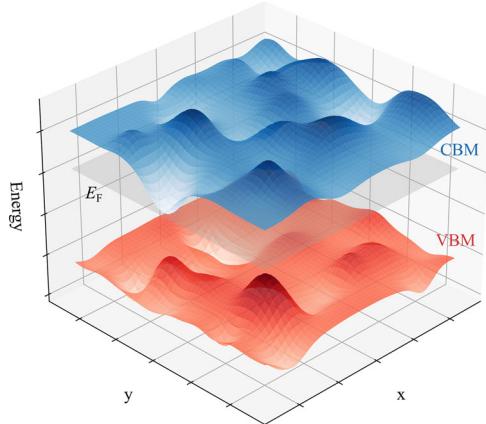

The dependence of channel doping on  $A_{\text{ch}}$  is further supported by PL characterization of the WS<sub>2</sub> channels. PL maps of three devices with different channel areas ( $W_{\text{ch}} \times L_{\text{ch}} = 75 \times 30.2, 10 \times 10.2$ , and  $10 \times 2.2$   $\mu\text{m}^2$ ) are acquired by stepping the laser across the channel (step size = 0.5  $\mu\text{m}$ ) and measuring a PL spectrum at each position. As shown in the representative spectra in Fig. 3, the characteristic PL emission of WS<sub>2</sub> appears just below 2 eV and consists of two convoluted signals arising from the recombination of negatively charged (trion, A<sup>-</sup>) and neutral (A) excitons<sup>33,34</sup>. Since their individual contributions are too closely spaced in energy to be meaningfully deconvoluted, each spectrum is fitted with a single Voigt profile. As the channel area decreases, the PL peak broadens and shifts to lower energies due to the increasing contribution of the A<sup>-</sup> component, indicative of a higher electron density in the channel (i.e., more *n*-doped)<sup>31,35,36</sup>. This

**Fig. 3 | Photoluminescence variation with WS<sub>2</sub> channel area.** Photoluminescence spectra collected at the center of three WS<sub>2</sub> FETs with different channel areas. As the channel area decreases, the WS<sub>2</sub> emission becomes broader and shifts to lower energies due to the enhanced trion contribution, indicative of larger electron concentration and higher *n*-type doping.

**Fig. 2 | Structural and electrical characterization of WS<sub>2</sub> FETs.** **a** TEM images of a WS<sub>2</sub> FET with a channel length of 130 nm and **b** transfer characteristics of devices with varying channel area collected with a single sweep from -40 V to 40 V.

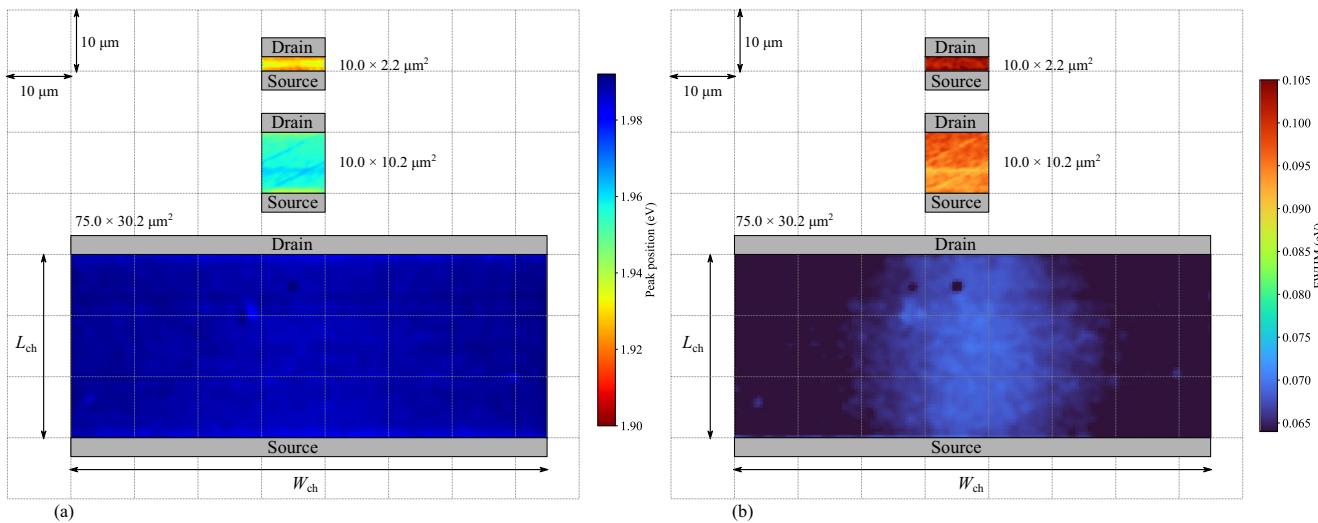

**Fig. 4 | Spatial mapping of PL peak position and FWHM in WS<sub>2</sub> FETs.** **a** PL peak position maps and **b** PL peak FWHM maps collected from three WS<sub>2</sub> FETs with varying channel areas. Again, as the channel area decreases, the PL emission becomes broader and shifts to lower energies, indicating an increased electron

concentration in the channel (i.e., higher *n*-type doping). Additionally, the maps reveal enhanced *n*-type doping near the edge metal contacts in the 10 × 10.2 and 10 × 2.2 μm<sup>2</sup> devices, and a non-uniform doping profile along the channel width in the 75 × 30.2 μm<sup>2</sup> device.

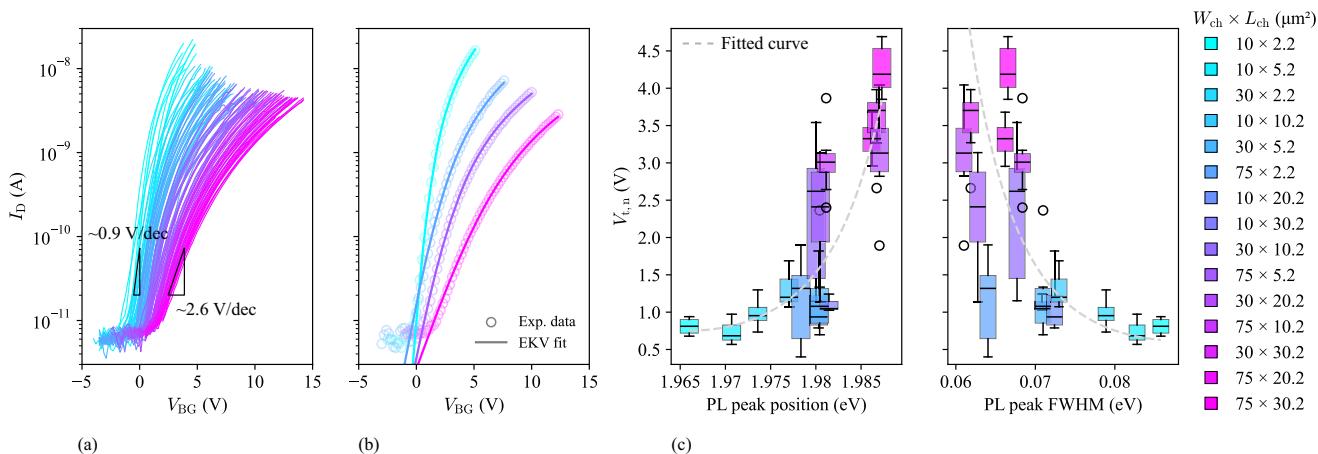

**Fig. 5 | Electrical-optical correlation in WS<sub>2</sub> FETs.** **a**  $I_D$ - $V_{BG}$  curves measured from 120 devices with 15 different channel sizes using an adaptive single sweep from  $\sim -3$  V to  $\sim 5$ –10 V. **b** Representative EKV model fitting for four devices. **c** Correlation between  $V_{t,n}$  and the PL signal from WS<sub>2</sub> (energy position and FWHM). As the

threshold voltage decreases (i.e., *n*-type doping increases), the PL peak broadens and shifts to lower energies, consistent with a higher electron concentration in the channel.

observation confirms the dependence of *n*-type doping on  $A_{ch}$  previously inferred from electrical characterization.

The extracted peak position and full width at half maximum (FWHM) are then mapped as a function of position across the channel (Fig. 4), revealing two distinct patterns of doping inhomogeneities within the individual devices. In the 10 × 10.2 and 10 × 2.2 μm<sup>2</sup> FETs, the PL peak shifts to lower energies near the source and drain edge contacts, indicating localized regions of enhanced electron density in the vicinity of the metal interfaces. In contrast, the 75 × 30.2 μm<sup>2</sup> device exhibits non-uniform electronic properties along the channel width, with significantly broader and slightly lower-energy PL emission at the channel center compared to the edges, indicating higher *n*-type doping in the central region.

To gather more detailed information about the dependence of the exciton/trion peak properties on doping level and  $A_{ch}$  while avoiding time-consuming full PL mapping, we collect single-point PL spectra at the centers of devices with 15 different channel areas (same as in Fig. 2b). For each  $A_{ch}$ , we measure the  $I_D$ - $V_{BG}$  *n*-branch of eight distinct FETs using a narrow  $V_{BG}$  sweep range to minimize trapping effects (Fig. 5a). Interestingly,  $V_{t,n}$  for

large-area devices is minimally affected by the gate bias range, as little to no variation is observed compared to the transfer characteristics in Fig. 2b. In contrast, narrow-range  $I_D$ - $V_{BG}$  curves of small-area devices exhibit significantly more positive  $V_{t,n}$  compared to wide-range sweeps, indicating substantial carrier trapping at negative gate biases. The narrow-range sweeps also reveal a clear difference in subthreshold swing (SS) between small and large devices, with small FETs exhibiting significantly steeper transfer characteristics than large ones ( $\sim 0.9$  V/dec and  $\sim 2.6$  V/dec for the smallest and largest devices, respectively). This observation indicates that large devices have a higher density of fast and active interface traps near the WS<sub>2</sub> CBM compared to small ones.

Due to the markedly different shapes of the  $I_D$ - $V_{BG}$  curves across device sizes—and the electronic inhomogeneities observed in the largest device, which introduce uncertainty in current normalization—we employ a heuristic Enz-Krummenacher-Vittoz (EKV) model fitting to robustly extract  $V_{t,n}$ <sup>37</sup>. An example model fit, along with a box plot of  $V_{t,n}$  versus PL peak position and FWHM, is shown in Fig. 5b, c. For large-area devices with positive threshold voltages, the channel is depleted, the carrier density is

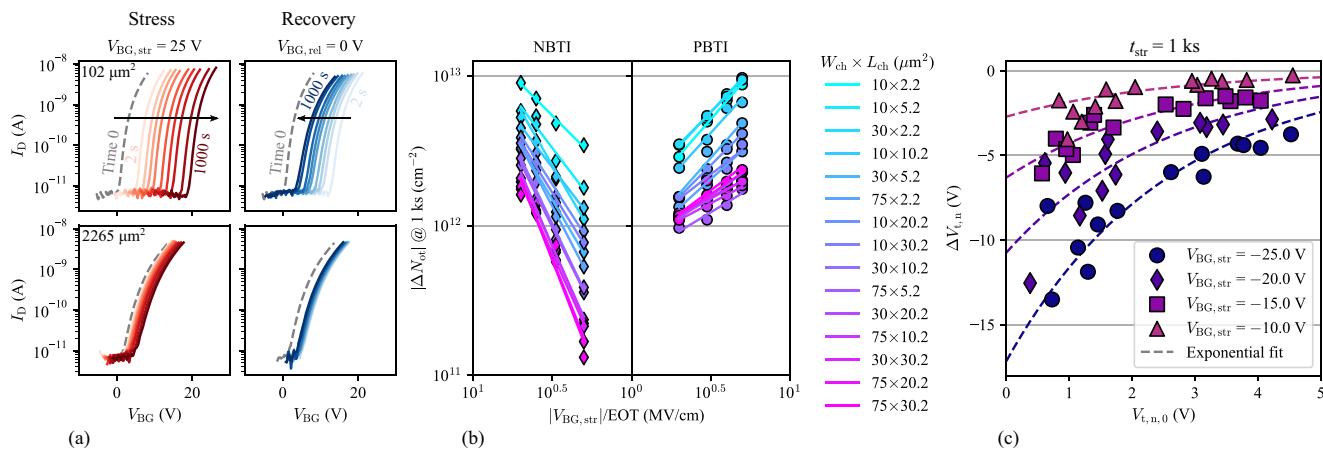

**Fig. 6 | BTI degradation in WS<sub>2</sub> FETs.** **a**  $I_D$ – $V_{BG}$  curves measured during the stress phase ( $V_{BG,str} = 25 \text{ V}$ ) and subsequent recovery phase ( $V_{BG,rel} = 0 \text{ V}$ ) for two devices with different channel areas. **b** Extracted  $\Delta N_{ot}$  plotted as a function of  $|V_{BG,str}|/\text{EOT}$  (MV/cm) at  $t_{str} = 1 \text{ ks}$  for both NBTI and PBTI stress conditions. **c** Experimental negative bias-induced  $\Delta V_{t,n}$  as a function of the initial threshold voltage  $V_{t,n,0}$ . Devices with higher *n*-type doping (i.e., smaller channel area) exhibit more pronounced degradation.

bias-induced  $\Delta V_{t,n}$  as a function of the initial threshold voltage  $V_{t,n,0}$ . Devices with higher *n*-type doping (i.e., smaller channel area) exhibit more pronounced degradation.

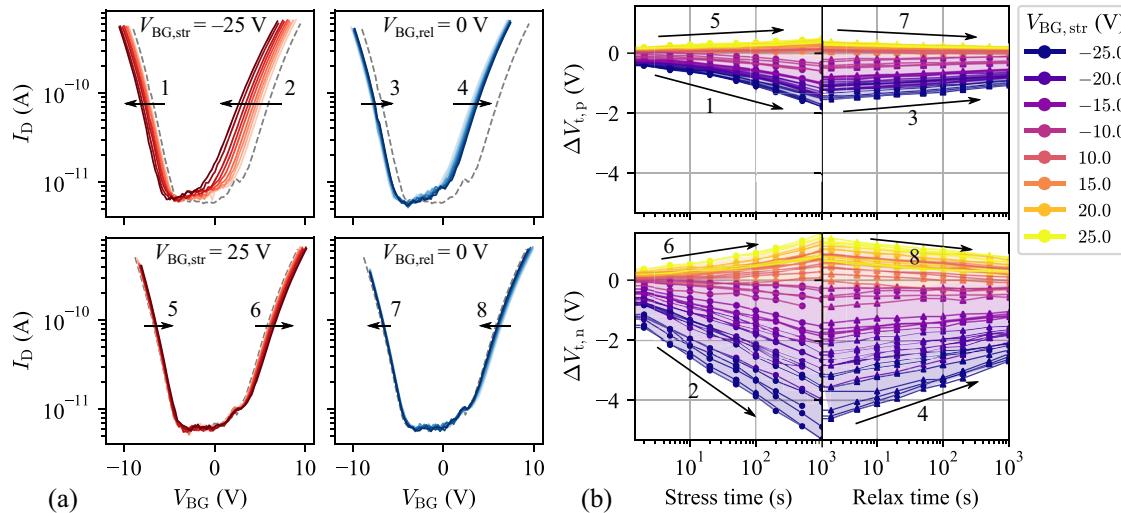

**Fig. 7 | Asymmetric BTI degradation in large-area WS<sub>2</sub> FETs.** **a**  $I_D$ – $V_{BG}$  curves and **b** threshold voltage shifts of the *p*- and *n*-branches under NBTI and PBTI stress, followed by relaxation. The degradation is asymmetric, with the *n*-branch consistently exhibiting a larger shift than the *p*-branch.

near zero, and the exciton/trion peaks (higher energy and narrower FWHM) remain relatively unaffected by  $V_{t,n}$ . However, for small-area devices with lower  $V_{t,n}$  electrons accumulate in the channel, and the exciton/trion peaks (lower energy and wider FWHM) become highly sensitive to small variations in threshold voltage.

#### Analysis of doping-dependent BTI

To investigate size-dependent and doping-dependent trapping effects, we evaluate BTI across 120 FETs with varying channel areas by applying different stress gate biases ( $V_{BG,str}$ ) for various durations ( $t_{str}$ ) and monitoring the resulting shifts in  $V_{t,n}$  (Fig. 6a). To assess degradation recovery, the same approach is used after removing the applied stress ( $V_{BG,rel} = 0 \text{ V}$ ). A small drain bias ( $V_D = 0.1 \text{ V}$ ) is applied throughout the entire experiment, including both stress and recovery phases. The variation of charged defect density projected at the channel interface can be calculated as follows<sup>8</sup>:

$$\Delta N_{ot} = \frac{\epsilon_0 \epsilon_{\text{SiO}_2} \cdot \Delta V_{t,n}}{q \cdot \text{EOT}}, \quad (1)$$

where  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_{\text{SiO}_2}$  is the silica dielectric constant,  $q$  is the elementary charge absolute value, and  $\text{EOT} = t_{\text{SiO}_2} = 50 \text{ nm}$  is the

thickness of the bottom  $\text{SiO}_2$  layer. As shown in Fig. 6b, the extracted  $\Delta N_{ot}$  (eq. (1)) versus  $|V_{BG,str}|/t_{\text{SiO}_2}$  at  $t_{str} = 1 \text{ ks}$  exhibits the expected power-law dependence under all conditions tested. Notably, devices with smaller channel areas show significantly larger  $V_{t,n}$  shifts following both negative and positive gate bias stresses (NBTI and PBTI, respectively). Since equal  $\Delta V_{t,n}$  would be expected if the trap distribution were constant with device dimensions, this finding suggests that higher *n*-type doping is correlated with a larger number of active defects within the Fermi level window scanned under stress, resulting in enhanced degradation. This is further confirmed by the plot of  $\Delta V_{t,n}$  versus the initial threshold voltage of the as-fabricated device ( $V_{t,n,0}$ ) in Fig. 6c, where monotonically increasing degradation is observed with decreasing  $V_{t,n,0}$  across all NBTI stress conditions ( $t_{str} = 1 \text{ ks}$ ). The same trend is also consistent with the substantial threshold voltage differences observed between wide- and narrow-range  $I_D$ – $V_{BG}$  sweeps in small-area devices (Fig. 2b and Fig. 5a, respectively), which arise from strong trapping effects at negative gate biases.

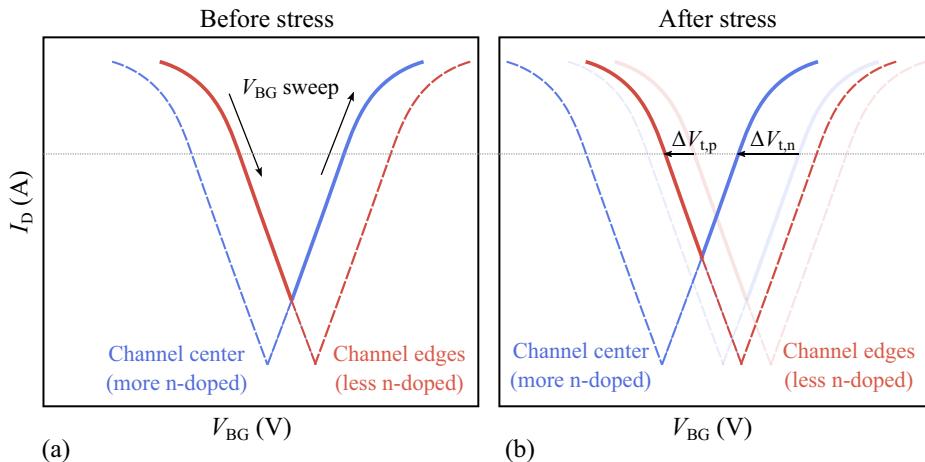

To comprehensively assess bias-induced degradation in ambipolar WS<sub>2</sub> FETs, we extend our BTI investigation to both conduction branches of large-area devices ( $L_{ch} = 30.2 \mu\text{m}$  and  $W_{ch} = 75 \mu\text{m}$ ) by tracking  $\Delta V_{t,n}$  and  $\Delta V_{t,p}$  under NBTI and PBTI stress. As shown in Fig. 7, the resulting threshold voltage shifts exhibit a consistent asymmetry across all devices and

**Fig. 8 | Impact of non-uniform doping on BTI in ambipolar 2D FETs.** **a** Schematic illustration of the ambipolar transfer characteristics of an as-fabricated WS<sub>2</sub> FET with a non-uniform doping profile along the channel width. The channel center, exhibiting higher *n*-type doping, controls the *n*-branch, while the channel edges, exhibiting lower *n*-type doping, control the *p*-branch. **b** Schematic illustration of the degraded transfer characteristics of the same device after negative bias stress. A larger shift of the *n*-branch relative to the *p*-branch arises due to the increasing density of active traps with higher *n*-type doping levels.

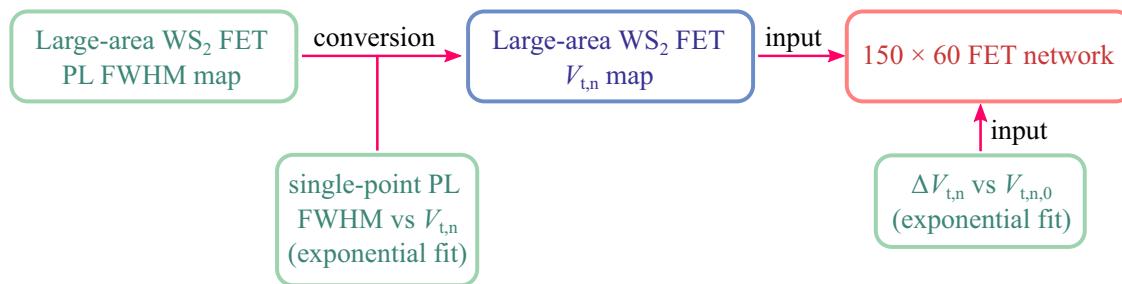

**Fig. 9 | Workflow for FET network modeling.** Workflow for constructing the  $150 \times 60$  FET network model. The PL FWHM map of the large-area WS<sub>2</sub> FET is converted into a spatial  $V_{t,n}$  map using an exponential function derived from single-point PL FWHM vs.  $V_{t,n}$  measurements. This  $V_{t,n}$  distribution serves as input to the network

model, together with an additional exponential relation describing  $\Delta V_{t,n}$  as a function of the initial  $V_{t,n,0}$ , which is required to reproduce the asymmetric degradation resulting from non-uniform charge trapping.

bias conditions, with the *n*-branch systematically shifting more than the *p*-branch. To explain this peculiar behavior, we rule out both uniform charge trapping across the device area—which would be expected to have the same electrostatic impact on both conduction branches, causing a symmetric shift—and the formation of deep, fast defects under stress, which could charge or discharge during the  $V_{BG}$  sweep. If such defects were present, a larger  $\Delta V_{t,n}$  would appear only for positive bias stresses. This is because sweeping  $V_{BG}$  from negative to positive values—corresponding to the Fermi level shift toward the CBM—would result in a net negative variation of the trapped charge, introducing an extra positive  $\Delta V_{t,n}$  contribution after both positive and negative BTI stresses. Consequently, the negative NBTI-induced shifts in the *n*-branch would be smaller than those in the *p*-branch, contrary to our experimental observations.

Instead, we attribute the asymmetric BTI to significant heterogeneity in the electronic properties of the deposited WS<sub>2</sub> channels, as highlighted by the PL map in Fig. 4. If the WS<sub>2</sub> band gap is assumed to be constant across the device area, electrons and holes are expected to preferentially travel through the center and the edges of the channel, respectively, due to the uneven doping profile. In other words, the large-area device is expected to behave as two parallel ambipolar transistors: the more *n*-doped center region, with lower  $|V_{t,n}|$ , controls the *n*-branch, while the less *n*-doped edges, with lower  $|V_{t,p}|$ , control the *p*-branch (Fig. 8a). As a result, each carrier type may interact with a different distribution of defects along its path. In our case, since stronger *n*-type doping is correlated with a higher defect density (Fig. 6), this scenario is consistent with the greater degradation observed in the *n*-branch due to larger charge trapping at the channel center compared to its edges (as schematically shown in Fig. 8b).

### FET network modeling

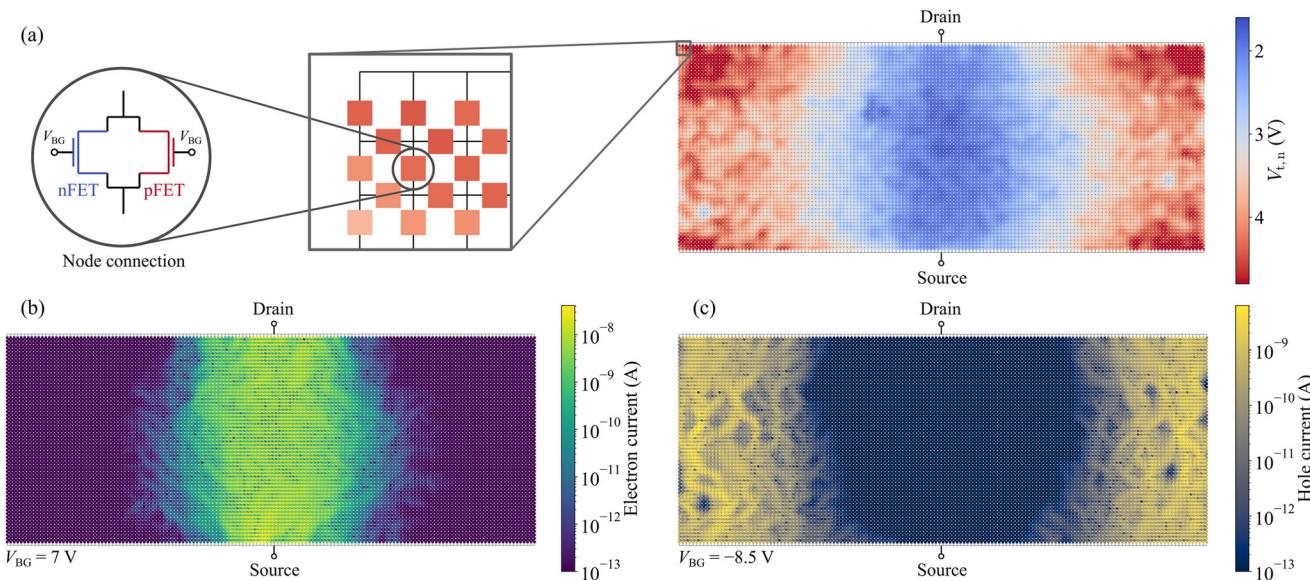

To better quantify the impact of channel inhomogeneities on transport and BTI, we reproduce the degradation asymmetry using an equivalent circuit model based on a  $150 \times 60$  FET-connected network in a SPICE simulator (same aspect ratio as the investigated WS<sub>2</sub>  $75 \times 30.2 \mu\text{m}^2$  channels)<sup>29</sup>. The overall workflow for constructing the FET network model is illustrated in Fig. 9. Each node is connected both vertically and horizontally by a parallel Si-based pFET and nFET with a thick gate dielectric (50 nm SiO<sub>2</sub>), all sharing the same gate voltage to replicate the ambipolar behavior of our WS<sub>2</sub> devices (Fig. 10a). The transport direction is defined by connecting the first and last transistor rows to the source ( $V_S = 0$  V) and drain ( $V_D = 0.1$  V), respectively. To emulate the width-dependent doping profile observed in the PL map in Fig. 4, we convert the PL peak's FWHM into  $V_{t,n}$  by fitting the data in Fig. 5c with an exponential function of a second-order polynomial, which closely follows the experimental trend. The resulting  $V_{t,n}$  distribution is then incorporated into the equivalent circuit model by assigning each value from the converted map to the corresponding node in the FET network (Fig. 10a). For simplicity, the difference between  $V_{t,n}$  and  $V_{t,p}$  in each FET pair is set to 8 V (i.e.,  $V_{t,p} = V_{t,n} - 8$  V, consistent with the experimental data), implying that the channel band gap is assumed constant across the entire device. When a positive gate voltage is applied to the FET network, electrons preferentially flow through nFET paths with lower threshold voltages along the channel center (Fig. 10b). Conversely, under negative gate bias, holes flow through pFET paths with lower threshold voltages along the channel edges (Fig. 10c). This model effectively captures the non-uniform transport mechanism in an ambipolar large-area FET with a spatially varying doping profile.

**Fig. 10 | Non-uniform transport in a 150 × 60 FET-connected network.**

a Schematic of the 150 × 60 FET-connected network implemented in a SPICE simulator to model non-uniform transport and asymmetric degradation in large-area WS<sub>2</sub> FETs. The  $V_{t,n}$  distribution is derived by converting the PL map in Fig. 4 using the exponential fitting function shown in Fig. 5. b Simulated electron current

distribution at  $V_{BG} = 7$  V, illustrating preferential conduction through the channel center, where  $|V_{t,n}|$  is lower (i.e., higher  $n$ -type doping). c Simulated hole current distribution at  $V_{BG} = -8.5$  V, showing that holes flow mainly through the channel edges, where  $|V_{t,p}|$  is lower (i.e., lower  $n$ -type doping).

**Fig. 11 | Modeling asymmetric BTI in a non-uniform FET network.** a Simulated  $I_D$ - $V_{BG}$  curves from the FET network model incorporating the spatially varying doping profile. b Comparison between experimental and simulated  $\Delta V_{t,n}$  vs.  $\Delta V_{t,p}$ , highlighting the model's ability to reproduce the observed degradation asymmetry.

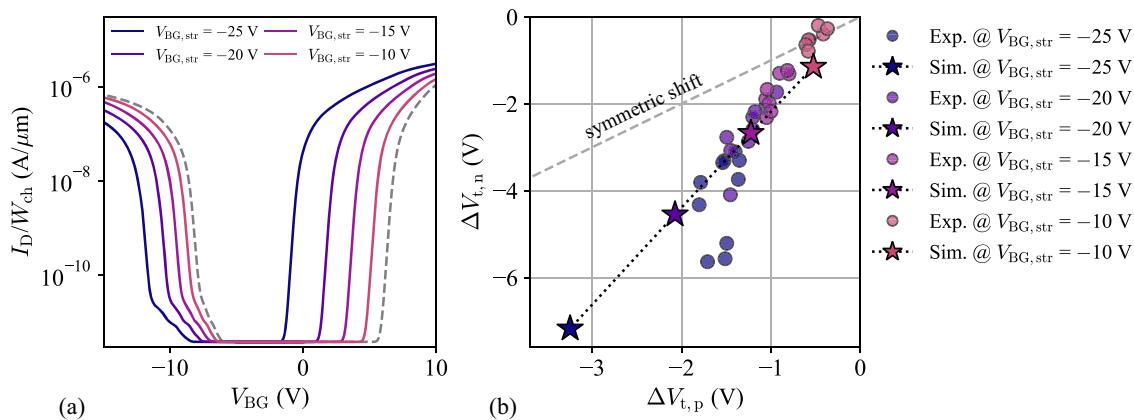

We now evaluate the asymmetric bias-induced degradation caused by non-uniform charging across the device area (Fig. 11). To this end, we consider the case of NBTI under four stress gate biases (-10, -15, -20, and -25 V) and a stress time of 1 ks. As discussed in the previous paragraphs, a higher  $n$ -type doping level (i.e., a lower  $V_{t,n}$ ) results in greater degradation of the 2D FET. To transfer this information into the FET network model, we perform a global fit of the degradation traces in Fig. 6c with an exponential function, using the same exponent and separate fitted coefficients for each stress bias to reduce the number of free parameters. Next, we simulate the transfer characteristics of the FET network using the  $V_{t,n}$  distribution extracted from PL mapping. For each NBTI stress bias, we repeat the simulation by applying a stress-induced threshold voltage shift to each FET pair, assuming  $\Delta V_{t,n} = \Delta V_{t,p}$ , as each node represents a uniform region where trapped charges exert the same electrostatic impact on both conduction branches. The applied shifts are exponentially proportional to the initial  $V_{t,n}$  values, as extracted from the fit in Fig. 6c. As a result, an empirical  $\Delta V_{t,n}$  distribution—reflecting both the spatially varying  $V_{t,n}$  and the doping-dependent degradation—is incorporated into the equivalent

circuit model. In summary, rather than modeling the physical trapping mechanisms explicitly, our approach uses the experimentally measured correlation between doping and degradation to assign local threshold voltage shifts.

A comparison of the fresh and degraded transfer characteristics of the FET network is shown in Fig. 11a. The model successfully replicates the asymmetric degradation across all stress conditions, with the  $n$ -branch consistently exhibiting a greater shift than the  $p$ -branch. Although the FET network model does not aim to describe the full physical and electrostatic behavior of a 2D FET, the simulated  $\Delta V_{t,n}$  and  $\Delta V_{t,p}$  show good agreement with experimental results (Fig. 11b), indicating that the electrostatic shift induced by a non-uniform distribution of charges (extracted from experiments) can be captured with sufficient accuracy. In particular, while the model slightly overestimates degradation at high stress biases, it correctly reproduces the asymmetry magnitude in all tested cases.

Compared to CPU-intensive 3D TCAD simulations, our equivalent circuit approach offers a fast and flexible framework to evaluate the effects of spatial variability in large-area devices. However, its scope remains

qualitative—or at best semi-quantitative, as demonstrated in this work—since it does not capture full electrostatics or quantum effects at the nanoscale. Therefore, the FET network provides a simplified, easy-to-use tool to corroborate our hypotheses, rather than serving as a replacement for significantly more accurate and rigorous TCAD modeling. Because several electrical parameters of each node's FET can be arbitrarily adjusted, our model is also readily extendable to other phenomena involving spatial variability, such as non-uniform mobility or interface trap density.

## Discussion

Our findings indicate that *n*-doped regions are associated with a substantially higher density of active defects, contributing to the reduced stability of the  $I_{D-V_{BGn}}$ -branch observed in our devices. This scenario is plausible given the well-established sensitivity of 2D TMDs' electronic properties to their chemical environment. In this context, several studies have shown that defects in the gate dielectric (e.g., oxygen vacancies and undercoordinated Al atoms), defects in the channel (e.g., sulfur vacancies), and adsorbates on the TMD surface (e.g., water molecules) play a critical role in modulating local doping<sup>25,32,38,39</sup>. These same defects also introduce localized energy states within the band gap, potentially acting as carrier traps. As a result, spatial variations in doping are likely correlated with the spatial distribution of active traps. Furthermore, the enhanced stability of the *p*-branch aligns with our previous study on 300-mm-integrated 2D FETs with the same gate stack but different channel materials, where WSe<sub>2</sub> pFETs exhibited significantly greater reliability than MoS<sub>2</sub> and WS<sub>2</sub> nFETs<sup>40</sup>. This further supports the notion that, in our 300-mm-integrated devices, *n*-type doping is associated with a higher trap density than *p*-type doping. Nonetheless, a comprehensive comparison remains challenging due to the limited availability of reliability studies on 2D pFETs.

In line with these observations, the occurrence of defects acting simultaneously as dopants and charge traps may not be unique to the WS<sub>2</sub> FETs discussed here. Similar channel-area-dependent doping effects have been observed in our 300-mm integrated MoS<sub>2</sub> FETs, featuring substantially larger crystal domains and higher channel mobility (>100  $\mu\text{m}$  and 20–50  $\text{cm}^2/\text{V} \cdot \text{s}$ , respectively, compared to the ~100 nm domains and ~3  $\text{cm}^2/\text{V} \cdot \text{s}$  mobility of the WS<sub>2</sub> channels investigated here)<sup>28,30,31</sup>. This suggests that the chemical species highlighted in this work—such as intercalated water, oxygen vacancies, undercoordinated Al atoms, and sulfur vacancies—could influence the stability of a broad range of 2D FETs.

While variations in impurity/defect concentrations—responsible for both *n*-type doping and charge trapping—can explain the greater degradation observed in smaller devices compared to larger ones, the origin of these variations, as well as the inhomogeneous doping profile along the channel width in large-area FETs, remains unclear. If the doping variability were caused by contact formation (e.g., via diffusion of impurities from the metal contacts), one would expect a non-uniform profile along the channel length of large-area devices. However, since the observed heterogeneity occurs along the channel width, it is more likely introduced during the patterning step of device fabrication (e.g., water intercalation<sup>32</sup>).

Looking ahead, as fabrication processes advance toward highly scaled devices with channel lengths and widths on the order of 10 nm, improved process control is expected to mitigate unintentional doping effects, which is essential to reduce threshold voltage variability. While the micrometer-scale inhomogeneities observed in our current devices may become less relevant in these future generations, nanoscale fluctuations in the electronic properties of TMDs are likely to remain a key factor affecting device reliability<sup>21–24</sup>. For instance, in scaled ambipolar 2D FETs, degradation asymmetries could still occur, as electrons and holes may traverse different percolation paths subject to distinct defect types and trap densities.

Collectively, these results provide crucial insights into the intricate interplay between charge trapping, channel doping, and channel inhomogeneities, highlighting their critical impact on the performance and long-term stability of WS<sub>2</sub> FETs. While *n*-type doping increases the density of defects that are active during BTI stress, the inhomogeneous doping profile observed in large-area WS<sub>2</sub> FETs leads to asymmetric degradation of their

ambipolar transfer characteristics. Future studies focused on understanding the relationship between defects and the electronic properties of 2D channels will be crucial for optimizing both the performance and reliability of 2D material-based devices, ultimately enabling their use in practical electronic applications.

## Methods

### Device fabrication

All devices are fabricated in a 300 mm pilot line<sup>1,28</sup>. The WS<sub>2</sub> channel (1–2 layers) is grown by metal-organic chemical vapor deposition from W(CO)<sub>6</sub> and H<sub>2</sub>S precursors at 750 °C directly on the 50 nm SiO<sub>2</sub> back-gate oxide. It is then capped with ~1 nm AlO<sub>x</sub> deposited at 100 °C (5 cycles of TMA soak followed by oxidation with H<sub>2</sub>O pulses), which enables the subsequent deposition of 10 nm HfO<sub>2</sub> by atomic layer deposition (ALD) at 350 °C. After active patterning, the channels are encapsulated with SiO<sub>2</sub> (PECVD) ILD0. Source and drain contacts are defined using a damascene process: contact trenches are etched and filled with Ti/TiN/W (TiN by ALD at 380 °C), followed by CMP planarization. The perimeter of the side contacts encompasses the entire contact pads (80  $\mu\text{m} \times 60 \mu\text{m}$ ).

The investigated devices feature channel lengths  $L_{\text{ch}}$  of 30.2  $\mu\text{m}$ , 20.2  $\mu\text{m}$ , 10.2  $\mu\text{m}$ , 5.2  $\mu\text{m}$ , and 2.2  $\mu\text{m}$ , and channel widths  $W_{\text{ch}}$  of 75  $\mu\text{m}$ , 30  $\mu\text{m}$ , and 10  $\mu\text{m}$ .

### Experimental methods and simulations

All electrical measurements are performed using a Süss PA300 probe station equipped with two Keithley 2636B source-meters and a Thermochuck, controlled over GPIB from a PC using a framework of Perl subroutines.

PL spectra are collected at room temperature on a Horiba Scientific LabRAM HR spectrometer using 532 nm excitation through a 100  $\times$ , 0.9 NA objective, yielding a ~1  $\mu\text{m}$  spot size and a laser power density of ~0.3 mW/ $\mu\text{m}^2$ . The laser penetrates the transparent top dielectric stack (300 nm SiO<sub>2</sub>, 10 nm HfO<sub>2</sub>, 1 nm AlO<sub>x</sub>), reaches the WS<sub>2</sub> channel, and generates its photoluminescence response. The emitted and scattered light is collected via the same objective, dispersed by a 300 g/mm grating, and detected with an open-electrode CCD, with a typical integration time of 10 s. Peak parameters are extracted using Fityk software.

SPICE simulations are performed using the Spectre simulator (Cadence).

### Data availability

The datasets generated and analyzed during the current study are not publicly available due to confidentiality agreements with industrial partners collaborating within the imec research program. However, the data are available from the corresponding author upon reasonable request.

Received: 7 August 2025; Accepted: 26 November 2025;

Published online: 12 December 2025

## References

1. Asselberghs, I. et al. Wafer-scale integration of double gated ws<sub>2</sub>-transistors in 300mm si CMOS fab. In *2020 IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2020). <https://doi.org/10.1109/iedm13553.2020.9371926>.

2. Wu, R. et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. *Nat. Electron.* **5**, 497–504 (2022).

3. Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. *Nature* **613**, 274–279 (2023).

4. Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional inse transistors. *Nature* **616**, 470–475 (2023).

5. Jiang, J. et al. Yttrium-doping-induced metallization of molybdenum disulfide for ohmic contacts in two-dimensional transistors. *Nat. Electron.* **7**, 545–556 (2024).

6. Illarionov, Y. Y. & Grasser, T. Reliability of 2d field-effect transistors: from first prototypes to scalable devices. In *2019 IEEE 26th*

*International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA)*, 1–6 (2019).

7. Illarionov, Y. Y. et al. Insulators for 2d nanoelectronics: the gap to bridge. *Nature Commun.* **11**, <https://doi.org/10.1038/s41467-020-16640-8> (2020).

8. Panarella, L. et al. Analysis of bti in 300 mm integrated dual-gate ws<sub>2</sub> fets. In *2022 Device Research Conference (DRC)*, 1–2 (2022).

9. Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by fermi-level tuning. *Nat. Electron.* **5**, 356–366 (2022).

10. Panarella, L. et al. Experimental-modeling framework for identifying defects responsible for reliability issues in 2d fets. *ACS Appl. Mater. Interfaces* **16**, 62314–62325 (2024).

11. Lan, H.-Y. et al. Reliability of high-performance monolayer mos<sub>2</sub> transistors on scaled high- $\kappa$  hfo<sub>2</sub>. *npj 2D Materials and Applications* **9**, <https://doi.org/10.1038/s41699-025-00527-7> (2025).

12. Kaczer, B. et al. A brief overview of gate oxide defect properties and their relation to mosfet instabilities and device and circuit time-dependent variability. *Microelectron. Reliab.* **81**, 186–194 (2018).

13. Grasser, T. Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities. *Microelectron. Reliab.* **52**, 39–70 (2012).

14. Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. *Nat. Electron.* **2**, 230–235 (2019).

15. Grasser, T., Waltl, M. & Knobloch, T. Fluoride dielectrics for 2d transistors. *Nat. Nanotechnol.* **19**, 880–881 (2024).

16. Kang, T. et al. High- $\kappa$  dielectric (hfo<sub>2</sub>)/2d semiconductor (hfse<sub>2</sub>) gate stack for low-power steep-switching computing devices. *Advanced Materials* **36**, <https://doi.org/10.1002/adma.202312747> (2024).

17. Khakbaz, P. et al. Two-dimensional bi<sub>2</sub>seo<sub>2</sub> and its native insulators for next-generation nanoelectronics. *ACS Nano* **19**, 9788–9800 (2025).

18. Sattari-Esfahlan, S. M. et al. Stability and reliability of van der waals high- $\kappa$  srto<sub>3</sub> field-effect transistors with small hysteresis. *ACS Nano* **19**, 12288–12297 (2025).

19. Arimura, H. et al. Ge nfet with high electron mobility and superior pbt<sub>1</sub> reliability enabled by monolayer-si surface passivation and la-induced interface dipole formation. In *2015 IEEE International Electron Devices Meeting (IEDM)*, 21.6.1–21.6.4 (2015).

20. Lan, H.-Y., Oleshko, V. P., Davydov, A. V., Appenzeller, J. & Chen, Z. Dielectric interface engineering for high-performance monolayer mos<sub>2</sub> transistors via taox interfacial layer. *IEEE Trans. Electron Devices* **70**, 2067–2074 (2023).

21. Addou, R. et al. Impurities and electronic property variations of natural mos<sub>2</sub> crystal surfaces. *ACS Nano* **9**, 9124–9133 (2015).

22. Kaushik, V., Varandani, D. & Mehta, B. R. Nanoscale mapping of layer-dependent surface potential and junction properties of cvd-grown mos<sub>2</sub> domains. *J. Phys. Chem. C* **119**, 20136–20142 (2015).

23. Moore, D. et al. Uncovering topographically hidden features in 2d mos<sub>2</sub> with correlated potential and optical nanoprobes. *npj 2D mater. appl.* **4**, <https://doi.org/10.1038/s41699-020-00178-w> (2020).

24. Panarella, L. et al. Evidence of contact-induced variability in industrially-fabricated highly-scaled mos<sub>2</sub> fets. *npj 2D Materials and appl* **8**, <https://doi.org/10.1038/s41699-024-00482-9> (2024).

25. Leonhardt, A. et al. Material-selective doping of 2d tmdc through al<sub>x</sub>o<sub>y</sub> encapsulation. *ACS Appl. Mater. Interfaces* **11**, 42697–42707 (2019).

26. McClellan, C. J., Yalon, E., Smith, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer mos<sub>2</sub> doped by alo<sub>x</sub>. *ACS Nano* **15**, 1587–1596 (2021).

27. Dicks, O. A., Cottom, J., Shluger, A. L. & Afanas'ev, V. V. The origin of negative charging in amorphous al<sub>2</sub>o<sub>3</sub> films: the role of native defects. *Nanotechnology* **30**, 205201 (2019).

28. Schram, T., Sutar, S., Radu, I. & Asselberghs, I. Challenges of wafer-scale integration of 2d semiconductors for high-performance transistor circuits. *Advanced Materials* **34**, (2022). <https://doi.org/10.1002/adma.202109796>.

29. Kaczer, B. et al. The relevance of deeply-scaled fet threshold voltage shifts for operation lifetimes. In *2012 IEEE International Reliability Physics Symposium (IRPS)*, 5A.2.1–5A.2.6 (2012).

30. Ghosh, S. et al. Integration of epitaxial monolayer mx<sub>2</sub> channels on 300mm wafers via collective-die-to-wafer (cod2w) transfer. In *2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits)*, 1–2 (2023).

31. Nuytten, T. et al. Toward characterization and assessment of mos<sub>2</sub> fundamental device properties by photoluminescence. *Mater. Sci. Semiconductor Process.* **193**, 109489 (2025).

32. Serron, J. et al. Conductivity enhancement in transition metal dichalcogenides: A complex water intercalation and desorption mechanism. *ACS Appl. Mater. Interfaces* **15**, 26175–26189 (2023).

33. Shi, W. et al. Raman and photoluminescence spectra of two-dimensional nanocrystallites of monolayer ws<sub>2</sub> and wse<sub>2</sub>. *2D Mater.* **3**, 025016 (2016).

34. Sebait, R., Biswas, C., Song, B., Seo, C. & Lee, Y. H. Identifying defect-induced trion in monolayer ws<sub>2</sub> via carrier screening engineering. *ACS Nano* **15**, 2849–2857 (2021).

35. Mak, K. F. et al. Tightly bound trions in monolayer mos<sub>2</sub>. *Nat. Mater.* **12**, 207–211 (2012).

36. Golovynskyi, S. et al. Trion binding energy variation on photoluminescence excitation energy and power during direct to indirect bandgap crossover in monolayer and few-layer mos<sub>2</sub>. *J. Phys. Chem. C* **125**, 17806–17819 (2021).

37. Dei, M. Heuristic enz–krummenacher–vittoz (ekv) model fitting for low-power integrated circuit design: An open-source implementation. *Electronics* **14**, 1162 (2025).

38. Van Troeye, B. et al. Impact of interface and surface oxide defects on ws<sub>2</sub> electronic properties from first principles. *ACS Nano* **19**, 11664–11674 (2025).

39. Lu, H., Kummel, A. & Robertson, J. Passivating the sulfur vacancy in monolayer mos<sub>2</sub>. *APL Materials* **6**, <https://doi.org/10.1063/1.5030737> (2018).

40. Dorow, C. J. et al. Exploring manufacturability of novel 2d channel materials: 300 mm wafer-scale 2d nmos & pmos using mos<sub>2</sub>, ws<sub>2</sub>, & wse<sub>2</sub>. In *2023 International Electron Devices Meeting (IEDM)*, 1–4 (2023).

## Acknowledgements

This research was supported by the Research Foundation—Flanders (FWO, grant no. 1S72625N) and funded by the imec IIAP Exploratory Logic program, the 2D-PL pilot line project through Horizon Europe (grant no. 101189797), and Horizon 2020 (grant no. 952792).

## Author contributions

L.P. performed the electrical measurements, the modeling, and wrote the manuscript. B.K., Q.S., and V.A. supervised the research. T.N. performed the PL measurements. Q.S., C.L.R., and G.S.K. contributed to the development of imec 300 mm FAB process. B.V.T., S.T., P.S.C., and T.G. contributed to the development of the equivalent circuit model. All authors discussed the results and contributed to the preparation of the manuscript.

## Competing interests

The authors declare no competing interests.

## Additional information

**Correspondence** and requests for materials should be addressed to L. Panarella.

**Reprints and permissions information** is available at <http://www.nature.com/reprints>

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit <http://creativecommons.org/licenses/by/4.0/>.

© The Author(s) 2025