Abstract

Incipient ferroelectricity bridges traditional dielectrics and true ferroelectrics, enabling advanced electronic and memory devices. Firstly, we report incipient ferroelectricity in freestanding SrTiO3 nanomembranes integrated with monolayer MoS2 to create multifunctional devices, demonstrating stable ferroelectric order at low temperatures for cryogenic memory devices. Our observation includes ultra-fast polarization switching (~10 ns), low switching voltage (<6 V), over 10 years of nonvolatile retention, 100,000 endurance cycles, and 32 conductance states (5-bit memory) in SrTiO3-gated MoS2 transistors at 15 K and up to 100 K. Additionally, we exploit room-temperature weak polarization switching, a feature of incipient ferroelectricity, to construct a physical reservoir for pattern recognition. Our results showcase the potential of utilizing perovskite material properties enabled by advancements in freestanding film growth and heterogeneous integration, for diverse functional applications. Notably, the low 180 °C thermal budget for fabricating the 3D-SrTiO3/2D-MoS2 device stack enables the integration of diverse materials into silicon complementary metal-oxide-semiconductor technology, addressing challenges in compute-in-memory and neuromorphic applications.

Similar content being viewed by others

Introduction

Perovskite materials have exhibited substantial potential for advancing the development of electronic devices and memory technologies1,2,3. In addition, a few perovskites stand out due to their exceptional properties, such as incipient ferroelectricity, which can significantly enhance their functionalities. Incipient ferroelectricity in a material indicates the presence of a polar soft mode that does not fully transition to ferroelectricity due to quantum effects inhibiting the change4. The most notable examples of incipient ferroelectrics include strontium titanate (SrTiO3), calcium titanate (CaTiO3), and potassium tantalate (KTaO3)5,6. Although these materials are expected to retain their paraelectric or incipient ferroelectric properties even at low temperatures, stable ferroelectric orders can emerge in thin films due to nonidealities such as strain, defects, doping, and other structural modifications, even at room temperature7,8. Despite these exotic properties, incipient ferroelectric materials remain largely unexplored for developing solid-state devices for computing and storage applications.

In this article, we report the observation of incipient ferroelectricity at room temperature in freestanding nanomembranes of SrTiO3 (STO) synthesized using hybrid molecular beam epitaxy (MBE). In addition, we observe a transition to a stable ferroelectric order below 100 K, which persists down to 15 K. We further exploit the incipient ferroelectricity in STO nanomembranes by integrating them with monolayer and semiconducting MoS2, grown via metal-organic chemical vapor deposition (MOCVD), to develop solid-state devices for computing and cryogenic storage applications. Specifically, we exploit the pseudo-non-volatile polarization switching in STO-gated MoS2 field effect transistors (FETs) at room temperature as a fading memory for reservoir computing (RC). Whereas the stable ferroelectric order at low temperatures allows us to present a cryogenic memory device with a fast-switching speed < 10 nanoseconds, a low-switching voltage < 6 V, nonvolatile retention projected to extend beyond 10 years, endurance surpassing 100,000 cycles, and the capability to store 32 distinct conductance states or 5-bit memory storage at 15 K and up to 100 K.

Note that, achieving high-quality, pinhole-free perovskite films with uniform coverage and minimal defect density on various semiconducting channel materials, including Si, remains a formidable challenge9. In this context, the recent breakthrough in hybrid MBE on the synthesis of freestanding10 single-crystalline, epitaxial perovskite nanomembranes11,12 using a binary oxide sacrificial layer, holds significant importance13. Such freestanding 3D STO nanomembranes14 have already been integrated with mechanically exfoliated 2D semiconductors like MoS2, leading to FETs with a high on/off current ratio of 108 and a minimum subthreshold swing of 66 mV decade−1 at room temperature15. Furthermore, monolayer MoS2 has been integrated with STO membranes to realize a back-gated FET16, resulting in enhanced performance. Given the relatively modest thermal demands for assembling 3D/2D nanomembrane-based devices, they can serve as catalysts for innovation, enabling the development of more compact and efficient devices within the CMOS back-end. Yet, the full potential of 3D/2D stacks becomes evident when they are leveraged for multifunctionality, tapping into the distinct electronic properties of the constituent materials within the stack, such as incipient ferroelectricity. This study bridges this gap by developing a cryogenic memory device and a hardware accelerator for RC based on STO-gated MoS2 FETs. Supplementary Fig. 1 provides a concise overview of the key findings reported in this study.

Results

Characterization of freestanding 3D and 2D nanomembranes

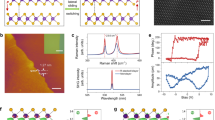

A hybrid MBE system was utilized to synthesize an epitaxial, and crystalline SrO (002) sacrificial layer followed by an STO (001) film on LaAlO3 (001) substrate as shown in Fig. 1a and discussed in detail in an earlier work13. Strontium (Sr) was supplied using an elemental solid source, titanium (Ti) was introduced through a metal-organic precursor, titanium tetra isopropoxide (TTIP), with oxygen (O2) supplied from a radio frequency (RF) plasma source. Before initiating growth, the LAO substrates were heated to a temperature of 950 °C and cleaned with oxygen plasma for 10 minutes. Further details on the synthesis of STO are provided in the Methods section. The film quality was assessed using reflection high-energy electron diffraction (RHEED), as shown in Fig. 1b. The RHEED image displays a streaky pattern, indicating a smooth, epitaxial STO film. The atomic force microscopy (AFM) image in Fig. 1c reveals an atomically smooth surface with a roughness of ~ 0.55 nm. The bright feature on the surface is likely due to hydration spots, attributed to the hygroscopic sacrificial layer17. Figure 1d presents the Wide-angle X-ray diffraction (XRD) 2θ-ω coupled scan of the STO/SrO/LAO (001) structure, confirming single-crystalline and epitaxial growth of SrO (002) and STO (001) on the LAO (001) substrate. The film exhibits clear Bragg peaks corresponding to STO, SrO, and LAO. In addition, the peak position of the as-grown STO (002) diffraction condition is found to be at 46.378° corresponding to an out-of-plane lattice parameter of \({a}_{{{\rm{STO}}}}\) = 3.913 Å, indicating the partially strained STO film. However, as shown in Supplementary Fig. 2, after transferring the STO film onto the SiO2 substrate, the peak position was found to be at 46.473° corresponding to \({a}_{{{\rm{STO}}}}\) = 3.905 Å, indicating that the STO nanomembrane is fully relaxed. Figure 1e presents cross-sectional scanning transmission electron microscopy (STEM) high-angle annular dark-field (HAADF) imaging and energy-dispersive X-ray spectroscopy (EDS) elemental mapping of the as-grown STO film on SrO/LAO. The images confirm the phase purity and crystallinity of the STO layer.

a Schematic illustrating SrTiO3 (STO) thin film on LAO substrate, with a sacrificial layer of SrO grown via the hybrid molecular beam epitaxy (MBE). b Reflection high-energy electron diffraction (RHEED) pattern after STO growth. c The atomic force microscopy (AFM) and (d) X-ray diffraction (XRD) analysis of the as grown STO film. e Cross-sectional high-angle annular dark-field (HAADF)-scanning transmission electron microscopy (STEM) imaging and the accompanying energy-dispersive X-ray spectroscopy (EDS) elemental mapping of the STO/SrO/LAO structure indicate phase purity, single crystallinity, and uniform growth of the STO film. f Raman spectra obtained from metal-organic chemical vapor deposition (MOCVD) MoS2 film using 532 nm laser at 1% power shows the characteristic in-plane \({{{\rm{E}}}}_{2{{\rm{g}}}}^{1}\) and out-of-plane \({{{\rm{A}}}}_{1{{\rm{g}}}}\) modes at 384.7 cm−1 and 405 cm−1 respectively, with a peak-to-peak distance of ~ 20.3 cm−1. Raman maps for (g) \({{{\rm{E}}}}_{2{{\rm{g}}}}^{1}\) peak position, (h) \({{{\rm{A}}}}_{1{{\rm{g}}}}\) peak positions, and (i) peak separation measured over a 20 µm \(\times\) 20 µm area. The mean and standard deviation values are shown in the inset. j Photoluminescence (PL) spectra with characteristic monolayer peak at 1.84 eV. k Colormap for the PL peak position, measured over a 20 µm \(\times\) 20 µm area. l STEM-HAADF image and (m) selected area electron diffraction (SAED) of monolayer MoS2 film viewed down its c-axis at an accelerating voltage of 80 kV. All of these characterizations indicate the quality of the monolayer MoS2.

Next, we characterized the freestanding MoS2 monolayer film grown via MOCVD on a 2-inch a-plane sapphire substrate, as shown in Supplementary Fig. 3. Figure 1f–i shows the Raman spectra and corresponding spatial colormaps of two Raman-active modes, \({E}_{2g}^{1}\) and \({A}_{1g}\), along with their peak separation across a 20 µm \(\times\) 20 µm area. The mean and standard deviation for\({E}_{2g}^{1}\) and \({A}_{1g}\) were ~ 384.7 cm−1 and ~ 0.1 cm−1 and ~ 405.1 cm−1 and ~ 0.1 cm−1, respectively, with a peak separation mean of ~ 20.3 cm−1 and a standard deviation of ~ 0.1 cm−1. Figure 1j, k displays the photoluminescence (PL) spectra and the spatial colormap of the PL peak position across the same area. The PL peak position averaged around 1.84 eV with a standard deviation of ~ 0.008 eV, confirming the monolayer nature of the MoS2 film. Finally, the STEM-HAADF image of MoS₂, viewed along the c-axis (Fig. 1l), along with selected area electron diffraction (SAED) in Fig. 1m, reveals the crystalline 2H phase. Additional information regarding the growth and characterization of STO nanomembrane and monolayer MoS2 films is available in the Methods section.

Integration of 2D/3D nanomembranes

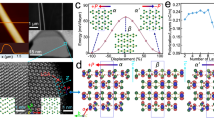

Next, 3D and 2D nanomembranes were stacked using a low-thermal budget fabrication process flow for the construction of FeFETs. Initially, electron beam (e-beam) lithography followed by e-beam evaporation was employed to create patterns for local back-gates comprising a stack of 5 nm Ti/ 25 nm Pt on a commercially acquired SiO2/Si substrate. Next, a thin polydimethylsiloxane (PDMS) sheet was attached to the top of the as-grown STO thin film. Subsequently, the stack was immersed in a deionized (DI) water bath to etch away the sacrificial SrO layer13 This process resulted in the creation of an STO membrane adhering to the PDMS sheets. Supplementary Fig. 4 provides optical images of the STO membrane attached to PDMS. Next, the PDMS/STO membrane was transferred onto our pre-constructed back-gate metal stack, and the PDMS stamp was mechanically extracted, leaving the STO on the substrate to function as the back-gate dielectric. The monolayer MoS2 was then transferred onto the local back-gate islands using a poly(methylmethacrylate) (PMMA)-assisted wet transfer technique. The device’s channel length (L = 1 μm) and width (W = 1 μm) were defined through e-beam lithography, followed by reactive ion etching (RIE) with SF6 plasma at a temperature of 5 °C. Finally, source and drain contacts were patterned via e-beam lithography, and a 40 nm Ni/30 nm Au layer was deposited using e-beam evaporation. Figure 2a–c illustrates the schematic diagram, top-view optical image, and top-view scanning electron microscope (SEM) image of the local back-gated 3D/2D stacked FET, which features Ni/Au contacts, a MoS2 channel, and an STO nanomembrane as the gate dielectric. In addition, Fig. 2d, e present the cross-sectional STEM-HAADF image and corresponding elemental mapping from EDS of the 2D/3D stack, showing the interface between the STO film and MoS2 channel.

a Device schematic, (b) top-view optical image. c Scanning electron microscope (SEM) image of a representative field-effect transistor (FET) based on 2D MoS2/3D STO nanomembranes. The FET is locally back-gated with Ti/Pt serving as the back-gate electrode, 80 nm STO as the gate dielectric, monolayer MoS2 as the semiconducting channel, and Ni/Au as the source and drain contacts. The channel length and width of the devise are \(L=1{{\rm{\mu }}}{{\rm{m}}}\) and \(W=1\,\mu m\), respectively. d Cross-sectional STEM-HAADF image of the fabricated FET based on 2D MoS2/3D STO nanomembranes. e An enlarged STEM-HAADF view of the boxed region in (d) and corresponding EDX elemental mapping. f Transfer characteristics, i.e., source-to-drain current (\({I}_{{{\rm{DS}}}}\)) as a function of the back-gate voltage (\({V}_{{{\rm{BG}}}}\)) for a constant source-to-drain bias of \({V}_{{{\rm{DS}}}}\) = 1 V, of 30 MoS2/STO FETs. Distributions of (g) maximum on-state current (\({I}_{\max }\)), (h) on/off current ratio (\({I}_{{{\rm{ON}}}}/{I}_{{{\rm{OFF}}}}\)), (i) subthreshold slope (\({{\rm{SS}}}\)) measured for 2 orders of magnitude change \({I}_{{{\rm{DS}}}}\), and (j) gate leakage (\({I}_{{{\rm{BG}}}}\)) extracted at \({V}_{{{\rm{BG}}}}\,\)= − 3 V (light green) and \({V}_{{{\rm{BG}}}}\,\)= 3 V (shown in dark green) for these 30 MoS2/STO FETs.

Next, we assessed the electrical characteristics of the 3D/2D stacked FETs. The single-sweep and room-temperature transfer characteristics i.e., source-to-drain current (\({I}_{{{\rm{DS}}}}\)), measured against the local back-gate voltage (\({V}_{{{\rm{BG}}}}\)) at a constant drain-to-source voltage (\({V}_{{{\rm{DS}}}}\)) of 1 V for 30 STO-gated MoS2 FETs plotted in logarithmic scale are shown in Fig. 2f. These FETs display unipolar electron transport consistent with the previous findings, attributed to the Fermi-level pinning of the metal contact in close proximity to the conduction band of MoS2. Furthermore, small variations in the transfer characteristics of the 2D FETs can be noticed across different devices. These variations may be attributed to residues and wrinkles introduced during the 3D and 2D membrane transfer processes involving PDMS and PMMA, respectively.

Figure 2g–i, respectively, show the corresponding distributions for extracted maximum on-state current (\({I}_{\max }\)), on/off current ratio (\({I}_{{{\rm{ON}}}}/{I}_{{{\rm{OFF}}}}\)), and subthreshold slope (\({{\rm{SS}}}\)) measured for 2 orders of magnitude change \({I}_{{{\rm{DS}}}}\). The mean values for \({I}_{\max }\), \({I}_{{{\rm{ON}}}}/{I}_{{{\rm{OFF}}}}\), and \({{\rm{SS}}}\) were found to be 4.8 \({\mu} A {{\mu} { m}}^{-1}\), 4.8 × 106, and 220 mV decade-1, respectively. Here, the large SS values of the STO-gated MoS2 FETs can be attributed to the presence of trap charges at the defect sites located at the MoS2/STO interface. It was noteworthy that, despite having a relatively small bandgap of approximately 3.2 eV, the 80 nm STO nanomembrane exhibited a relatively low gate leakage current (\({I}_{{{\rm{BG}}}}\)), as indicated by the corresponding histograms extracted for \({V}_{{{\rm{BG}}}}\) = 3 V and − 3 V in Fig. 2j.

Incipient ferroelectricity and non-volatile retention

In order to probe the interface between STO and MoS2, dual sweep transfer characteristics of an STO-gated MoS2 FET were measured at room temperature as shown in Fig. 3a. We observe a counterclockwise hysteresis window, a characteristic frequently encountered in ferroelectric FETs. This counterclockwise hysteresis arises from a specific mechanism: when the positive/negative gate voltage exceeds the coercive field (\({E}_{{{\rm{C}}}}\)), the polarization in the FE film aligns toward/away from the channel as shown in Fig. 3b, resulting in accumulation/depletion of electrons in the channel, which give rise to low/high threshold voltage, respectively. The ferroelectric-like behavior was also confirmed by measuring the dual sweep transfer characteristics of 10 other STO-gated MoS2 FETs, as shown in Supplementary Fig. 5, all of which demonstrated counterclockwise hysteresis. This outcome is surprising because bulk and pure STO typically lack ferroelectricity due to quantum fluctuations in atomic positions, categorizing it as an incipient ferroelectric material17. It is well-established that ferroelectric behavior can emerge in STO under certain conditions, such as when it is in the form of a thin-film, subjected to strain or strain gradients, modified by alloying, influenced by an electric field, or exposed to specific stress environments. 18,19,20,21,22,23. Moreover, defects like Ti, Sr, and/or O vacancies have been reported to induce ferroelectricity in STO thin films8,24,25.

a Dual sweep transfer characteristics of a representative STO-gated MoS2 FET measured at T = 300 K. b Schematic showing polarization switching in STO film can lead to low/high threshold voltage in MoS2 FETs. c Optical characterization of the freestanding STO nanomembrane at T = 300 K using second harmonic generation (SHG) at normal incidence as a function of the incident fundamental laser power. d Non-volatile retention of memory states for STO-gated MoS2 FET at T = 300 K. e Dual sweep transfer characteristics and (f) memory retention for STO-gated MoS2 FET measured at different temperatures, \(\it T\) = 225, 200, 150, and 100 K. Counterclockwise hysteresis is retained at all temperatures. However, memory retention improves significantly at lower temperatures. g Temperature-dependent SHG measurements show that the SHG intensity is maximum at 77 K and decreases with increasing temperature up to ~150 K, followed by a gradual increase until 300 K. The enhanced SHG intensity at lower temperatures agrees with memory retention results. h Schematic showing the possible origin of ferroelectricity in STO nanomembrane. i Atomic resolution HAADF STEM image of the STO film under the contact electrode. Corresponding maps of (j) the projected polar displacement vector on the (100) plane, and its (k) magnitude and (l) direction.

To further understand the ferroelectric-like behavior in STO-gated MoS2 FETs, we performed optical second harmonic generation (SHG) on the freestanding STO nanomembrane. The second harmonic response of a material requires inversion symmetry to be broken at the atomic scale, allowing SHG to reveal the presence of local polar order. Our SHG measurements used an 800 nm fundamental beam incident on the sample at normal or 45-degree incidence, and the reflected light at 400 nm was measured. Figure 3c shows the SHG intensity measured at room temperature at normal incidence as a function of the incident fundamental laser power. The incident power was optimized to ensure that the SHG signal from the SiO2/Si substrate underneath the STO membranes was minimized. The quadratic nature of the curve indicates broken inversion symmetry, and hence provides evidence of existing polar order, even at room temperature.

Since the spontaneous and switchable polarization in ferroelectric materials can be harnessed for non-volatile storage devices, we assessed the retention for both the high conductance state (HCS) and low conductance state (LCS) over a period of 100 s, as illustrated in Fig. 3d for our STO-gated MoS2 FET. Interestingly, the retention of the two memory states was found to be poor, suggesting that stable polarization states can be difficult to sustain for a long time in the STO nanomembrane at room temperature, owing to the incipient nature of ferroelectricity in the STO film. We also investigated the piezoresponse force microscopy (PFM) of the STO film on a gold-plated substrate at room temperature. Supplementary Figs. 6a–c shows the topography, PFM amplitude and PFM phase, respectively. The polarization reversal results, shown in Supplementary Fig. 6d, confirm domain switching, whereas the unsaturated ferroelectric phase demonstrates its instability, reaffirming the incipient nature of ferroelectricity at room temperature in STO nanomembranes.

To understand and probe the impact of incipient ferroelectricity in STO-gated MoS2 FETs, we measured the dual sweep transfer characteristics and corresponding retention of the HCS and LCS at different temperatures, \(T\) = 225, 200, 150, and 100 K, as illustrated in Fig. 3e, f, respectively. Notably, a counterclockwise hysteresis is observed at all temperatures. However, as the temperature decreased, we observed a gradual enhancement in the retention of the two memory states. This suggests that stable polarization switching within the STO nanomembrane becomes more reliable at lower temperatures. We also measured the SHG intensity from STO nanomembranes as a function of temperature down to 77 K, as shown in Fig. 3g. The SHG intensity is maximum at the lowest measured temperature and decreases as the temperature is increased up to ~ 150 K, after which it rises gradually with temperature. Our SHG intensity variation is in excellent agreement with the electrical characterization and can explain the observed temperature-dependent nonvolatile retention of polarization switching in STO-gated MoS2 FETs. The electrical data, combined with the SHG measurements, suggest that ferroelectricity in STO nanomembranes can be ascribed to the field-induced long-range correlation between pre-existing nanopolar regions that thermally decay with time23. Increasing the temperature leads to increased thermal fluctuations, that accelerate the destabilization of the polar order. This is depicted schematically in Fig. 3h. While strain-free STO is expected to be paraelectric, we believe that the observed polar order could arise due to defects such as oxygen vacancies, Sr vacancies, etc. Interestingly, the polar order observed in STO membranes persists even up to room temperature.

To further confirm the existence of incipient ferroelectric order in the STO film at room temperature, we took the cross-sectional atomic resolution STEM-HAADF images of the STO layer on [100] zone axis for the region under the electrode as shown in Fig. 3i. The atomic resolution images are further processed using the Atomap software package26 for the detection of positions of the Sr and Ti atom columns. The projection of the polar displacement vector on the (100) plane in STO is determined by measuring the displacement of Ti atom column from the center of the four surrounding Sr atom columns on the (001) plane. A vector plot, with vectors pointing toward the Ti atom columns, is used to illustrate the magnitude and direction of the projected polar displacement on the (100) plane, as shown in Fig. 3j–l. The projected polar displacement vector of STO on (100) plane shown in the image is mostly along the same direction, pointing from bottom to top, with varying magnitudes forming several nanodomains.

It is noteworthy to highlight that a counterclockwise hysteresis may also originate from the presence of mobile ions in the dielectric or incipient ferroelectric material. Moreover, under an external electric field, the mobile ions can migrate throughout the material, resulting in a reversal in the hysteresis27, as observed in many non-ferroelectric transistors. To substantiate that the counterclockwise hysteresis in our STO-gated MoS2 FETs stems from the incipient ferroelectric nature of STO rather than mobile ion migration, we conducted voltage sweep-rate (\({t}_{{{\rm{sweep}}}}\)) dependent measurements on these FETs. Supplementary Fig. 7a shows the transfer characteristics at different temperatures, \(T\) = 200 K, 100 K, and 15 K \({t}_{{{\rm{sweep}}}}\), varying from 2 ms (fastest) to 10 s (slowest). Note that mobile ions need sufficient activation energy to migrate, and at low temperatures, such as 100 K or below, their movement becomes severely restricted. Furthermore, if the \({t}_{{{\rm{sweep}}}}\) is too slow, the mobile ions will reach equilibrium with the applied field, causing the hysteresis to diminish. However, if the gate dielectric exhibits ferroelectric order, the hysteresis window would remain, as polarization switching is not strongly dependent on \({t}_{{{\rm{sweep}}}}\). Supplementary Fig. 7b shows the memory or hysteresis window as a function of \({t}_{{{\rm{sweep}}}}\) for \(T\) = 200 K, 100 K, and 15 K. It is evident that the memory window predominantly remains constant as the \({t}_{{{\rm{sweep}}}}\) varied. Hence, it can be stated that the counterclockwise hysteresis in the STO-gated MoS2 FETs has originated from the incipient ferroelectric nature of the STO nanomembranes.

Construction of cryogenic memory and neuromorphic hardware

The observed temperature-dependent stability of ferroelectric orders in STO-gated MoS2 FET presents an opportunity for developing a fast, low-power, cryogenic memory at lower temperatures as well as hardware for neuromorphic computing at room temperature.

It is quite well known that cryogenic computing and memory components are crucial, particularly in the context of space electronics and in developing quantum computers. Note that conventional superconducting memories often fall short in terms of higher memory density and energy efficiency. Recently, a Si-doped HfO2 FeFET based cryogenic memory has been demonstrated, operating at 6.9 K with large memory window even at lower temperatures28. In this context, we explore the possibility of developing a cryogenic memory system exploiting stable ferroelectric order in STO-gated MoS2 FETs.

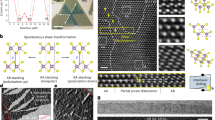

First, we evaluate the switching voltage required to operate the ferroelectric-like STO-gated MoS2 FET at T = 15 K. To extract the switching voltage for the HCS, transfer characteristics were measured with different sweeping ranges, maintaining a constant negative \({V}_{{{\rm{BG}}}}\) = − 3 V and progressively increasing the positive \({V}_{{{\rm{BG}}}}\) from 3 to 7 V in increments of 0.5 V, as depicted in Fig. 4a. To extract the switching voltage for the LCS, similar nested transfer characteristics were measured with constant positive \({V}_{{{\rm{BG}}}}\) = 6 V and gradually increasing negative \({V}_{{{\rm{BG}}}}\) of 0 to − 4 V in the step of 0.5 V, as illustrated in Fig. 4b. The \({{\rm{MW}}}\), which is defined as the difference between the threshold voltages (measured at an iso-current of 10 nA µm−1) corresponding to the HCS and LCS are plotted against the positive and negative sweep range in Fig. 4c, The \({{\rm{MW}}}\) disappears for \({V}_{{{\rm{BG}}}}\) < 3.5 V and reaches saturation for \({V}_{{{\rm{BG}}}}\) > 6 V, indicating complete polarization switching in the STO nanomembrane for \({V}_{{{\rm{BG}}}}\) = 6 V for the HCS. Similarly, the \({{\rm{MW}}}\) vanishes for \({V}_{{{\rm{BG}}}}\) > − 1 V and saturates for \({V}_{{{\rm{BG}}}}\) < − 3.5 V, indicating that the switching voltage for the LCS is established at \({V}_{{{\rm{BG}}}}\) = − 3 V. It is noteworthy that, even with an STO nanomembrane thickness of 80 nm, the switching voltages (\({V}_{{{\rm{SW}}}}\)) remain below 6 V, correlating to \({E}_{{{\rm{C}}}}\) ~ 0.75 MV cm−1.

Dual sweep transfer characteristics of a ferroelectric-like STO-gated MoS2 FET using different \({V}_{{{\rm{BG}}}}\) sweep ranges (a) keeping a constant negative \({V}_{{{\rm{BG}}}}\) = − 3 V and gradually increasing the positive \({V}_{{{\rm{BG}}}}\) from 3 to 7 V and (b) keeping a constant positive \({V}_{{{\rm{BG}}}}\) = 6 V and gradually increasing the negative \({V}_{{{\rm{BG}}}}\) from 0 to − 4 V. c Memory window (MW) plotted as a function of the \({V}_{{{\rm{BG}}}}\) range used in (a) and (b). d Memory retention measured for 1\(\times\)104 s. e HCS and LCS as a function of switching time (\({\tau }_{{{\rm{SW}}}}\)). The STO film can be switched as fast as 60 ns without any degradation to the MR. f HCS and LCS as a function of \({V}_{{{\rm{SW}}}}\) for \({\tau }_{{{\rm{SW}}}}\) = 10 ns. With the application of \({V}_{{{\rm{SW}}}}\,\)= − 6 V, the \({\tau }_{{{\rm{SW}}}}\) can be as low as 10 ns to achieve the same MR obtained in (e). g Switching endurance for the STO film was assessed for 105 cycles with no degradation to the MR. h 32 memory states obtained by applying different amplitude of programming pulses of fixed \({\tau }_{{{\rm{SW}}}}\) = 10 ms to form a 5-bit memory storage device. i output characteristics corresponding to each memory state shown in (h). The output characteristics are linear, even at 15 K.

Next, we evaluated the retention, switching speed, and endurance for a representative STO-gated MoS2 FET. The retention for the HCS and LCS were measured for a duration of 10,000 seconds without any visible degradation in the \({{\rm{MR}}}\) as shown in Fig. 4d, confirming non-volatile polarization switching in the STO nanomembrane at 15 K. The projected retention was found to be more than 10 years. The switching speed for the STO film was accessed using \({V}_{{{\rm{BG}}}}\) pulses with a pulse width (\({\tau }_{{{\rm{SW}}}}\)) down to 10 ns. Figure 4e shows the HCS and LCS as a function of \({\tau }_{{{\rm{SW}}}}\). The extracted \({{\rm{MR}}}\) function \({\tau }_{{{\rm{SW}}}}\) is shown in Supplementary Fig. 8a. We have used \({V}_{{{\rm{BG}}}}\) = 6 V and \({V}_{{{\rm{BG}}}}\) = − 3 V to switch the STO film between HCS and LCS, with \({\tau }_{{{\rm{SW}}}}\) ranging from 10 ms down to 10 ns. We found that the STO film can be switched as fast as 60 ns without any visible degradation in the \({{\rm{MR}}}\). However, with shorter pulses the \({{\rm{MR}}}\) decreases monotonically. Interestingly, by using higher magnitude \({V}_{{{\rm{BG}}}}\) pulses, \({{\rm{MR}}}\) can be recovered even for \({\tau }_{{{\rm{SW}}}}\) = 10 ns, as illustrated in Fig. 4f and Supplementary Fig. 8b. In essence, a reciprocal relationship exists between the pulse width and pulse amplitude when switching the ferroelectric polarization: specifically, a shorter pulse width necessitates a higher pulse amplitude, and conversely, a reduced amplitude can be compensated with a longer pulse width29. Finally, the switching endurance for the STO film was accessed for 105 cycles, as shown in Fig. 4g and no degradation was seen in the \({{\rm{MR}}}\).

Next, we leverage the minor loops found in the transfer characteristics of STO-gated MoS2 FETs to showcase multi-bit memory storage within a single device. The appearance of these minor loops stems from the partial polarization switching of ferroelectric domains beneath the semiconducting channel and can be attributable to the stochastic domain switching dynamics even in incipient ferroelectric materials. Figure 4h illustrates the successful manifestation of 5-bit memory storage corresponding to 32 distinct memory states obtained by applying different amplitudes of programming pulses of fixed \({\tau }_{{{\rm{SW}}}}\) = 10 ms. The \({{\rm{MR}}}\) between the states can be increased by reducing the number of states as shown in Supplementary Fig. 9 for 2-bit and 4-bit memory storage corresponding to 4 and 16 memory states Finally, Fig. 4i presents the output characteristics corresponding to each memory state, revealing linear characteristics even at low temperatures. Similar results were also observed at T = 100 K, as shown in Supplementary Fig. 10.

Multibit operation is a pivotal feature for cryogenic memory technologies that require high-density data storage. While HZO-based FeFETs demonstrate cryogenic storage capability, multi-bit implementations have not been previously achieved. In this context, our demonstration of fast switching, long retention, high endurance, low-voltage operation, and 5-bit memory in STO nanomembrane-gated 2D FETs stands out as a significant advancement in cryogenic memory technology.

Furthermore, we harness the room-temperature non-retentive polarization switching in the STO-gated MoS2 FET to construct a physical reservoir for accelerating RC. Note that, RC, derived from the framework of recurrent neural networks (RNNs), has emerged as a powerful computational paradigm for processing time-series data and performing pattern recognition30,31. It utilizes a fixed, randomly connected network of nonlinear units, known as the reservoir, to map lower-dimensional data into a higher-dimensional space. RC also requires a dynamic or fading memory to ensure that the reservoir gradually forgets previous inputs as new ones are introduced, enabling it to consider both current and past inputs effectively. Here, we leverage the device-to-device variation in STO-gated MoS2 FETs for mapping unidimensional input stimuli (gate voltage) applied to each device into multidimensional conductance space and pseudo-non-volatile retention of polarization switching in STO as fading memory to construct the physical reservoir for RC.

First, we show that it is possible to distinguish between 8 discrete patterns corresponding to the 3 × 3-pixel images using a reservoir consisting of a single STO-gated MoS2 FET. These patterns are shown in Fig. 5a. The pixel values were translated into \({V}_{{{\rm{BG}}}}\) values with \({V}_{{{\rm{BG}}}}\) = − 1 representing the dark pixels and \({V}_{{{\rm{BG}}}}\) = 3 V representing the bright pixels, then transformed into a one-dimensional array and applied to the FET. Figure 5b shows the evolution of each pattern with the final conductance (\({G}_{{{\rm{p}}}}\)) values being different for each pattern. This experiment was repeated multiple times, with the distribution \({G}_{{{\rm{p}}}}\) displayed in Fig. 5c. Evidently, despite the cycle-to-cycle variation, each distribution forms an individual band, facilitating the inference of the 8 patterns. Figure 5d shows the confusion matrix with near 100% accuracy between the predicted and true labels for the tested patterns. The discernible number of distinct patterns can exhibit super-linear growth when multiple devices are used to construct the reservoir. To illustrate, in Fig. 5e, we present a comprehensive library comprising all conceivable combinations (26 = 64) of 3 × 2-pixel images, which can serve as a foundation for generating any N × M pixel image. Supplementary Fig. 11 shows that it is difficult to discern more than 8 random patterns when the reservoir comprises only one FET, as the \({G}_{{{\rm{p}}}}\) distributions overlap. However, when we represent the \({G}_{{{\rm{p}}}}\) distributions of 2 and 3 FETs in 2D and 3D plots, distinct clusters of 20 and 48 patterns emerge, as depicted in Fig. 5f, g, respectively. This underscores the potential to discern an increasingly greater number of patterns by expanding the number of FETs within the reservoir. Notably, the multi-bit memory and the dynamic polarization switching in STO-based 2D FETs can be harnessed across various neuromorphic computing applications, such as reinforcement learning. To address this more directly, the multi-state capabilities of STO-gated 2D FETs can be harnessed to act as multi-bit synapses capable of storing multiple weights (conductance states) in brain-inspired reinforcement learning scenarios, as shown in ref. 32.

a 8 patterns corresponding to 3 × 3-pixel images translated into voltage values (VBG = 3 V and VBG = − 1 V for bright and dark pixels respectively) and applied to the artificial neuron (b) Evolution of conductance values for 8 different patterns resulting in distinct final conductance values (Gp) distinguishing each pattern. c Distribution of measured conductance, Gp, corresponding to each pattern over multiple experimental cycles. d Confusion matrix showing 100% accuracy in distinguishing and predicting the labels for the tested patterns. e Image libraries consist of all possible patterns (26 = 64) corresponding to 3 × 2-pixel images. Corresponding \({G}_{{{\rm{p}}}}\) distributions for (f) 2 neurons and (g) 3 neurons in 2D and 3D plots. Distinct clusters of 18 and 40 patterns emerge, underscoring the potential to discern an increasingly greater number of patterns by expanding the number of neurons. This phenomenon capitalizes on device-to-device variations across STO-gated MoS2 FETs, resulting in distinct conductance bands for the same pattern when applied to different devices.

In addition, a benchmarking table has been illustrated in Supplementary Table 1, which outlines and compares the performance metrics of our STO-based MoS2 FETs against the state-of-the-art FeFET candidates. This table offers a clear, concise comparison, emphasizing the competitive advantages and distinct features of our STO-based FETs compared to other ferroelectric devices in the field.

In conclusion, the integration of crystalline STO nanomembranes with monolayer MoS2 films presents a promising approach for developing BEOL-compatible ferroelectric-like FETs, as well as pioneering cryogenic memory technology. These devices not only display rapid and stable ferroelectric polarization switching at temperatures up to 200 K but also feature high-speed, low-power operation, and long-term retention. Furthermore, we utilized the unstable polarization switching at room temperature, a hallmark of incipient ferroelectricity, to construct a physical reservoir for pattern recognition. This research highlights the potential of exploiting exotic material properties through heterogeneous material integration, enabled by advances in the growth of freestanding films, for a wide range of functional applications.

Methods

Growth and characterization of STO membranes

A hybrid Molecular Beam Epitaxy (MBE) system (EVO-50 by Scienta Omicron Inc), was utilized to synthesize an epitaxial, and single crystalline 15 nm SrO (002) sacrificial layer followed by a 80 nm STO (001) film on LaAlO3 (001) substrate. Sr was supplied using an elemental solid source sublimated in a thermal effusion cell, maintaining a beam equivalent pressure (BEP) of 5.8 × 10−8 Torr during SrO and STO growth. Titanium was introduced using a metal-organic precursor, titanium tetra isopropoxide (TTIP), injected through a gas injector with a vapor inlet system, achieving a BEP of 3.3 × 10−6 Torr for an adsorption-controlled stoichiometric STO growth. Oxygen was supplied via a radio frequency (RF) plasma source at a pressure of 5 × 10−6 Torr, operating at 250 W. Before the beginning of the growth, the LAO substrates were heated to a growth temperature of 950 °C (thermocouple temperature). The substrate was cleaned using the oxygen plasma for 10 minutes. Following the oxygen plasma cleaning, an epitaxial SrO(001) layer was grown using the Sr and oxygen plasma source for 15 min, followed by the growth of the epitaxial STO(001) film by co-supplying Sr, Ti, and oxygen plasma for 30 min. Film surfaces were monitored using reflection high-energy electron diffraction (RHEED) after the growth of the SrO(001) and STO(001) layers. Atomic force microscopy (AFM) was employed for surface characterization using the Nanoscope V Multimode 8 by Bruker. The structural properties of the grown film were assessed through high-resolution X-ray diffraction using the SmartLab XE by Rigaku with Cu K\(\alpha\) radiation.

Fabrication of local back-gate islands

To define features with a local gate island configuration, a commercially sourced p + +-Si substrate with a 285 nm SiO2 layer was prepared by spin-coating with a bilayer of PMMA resist in a two-step process, followed by sequential baking at 185 °C and 95 °C for 60 and 90 s, respectively. Using an EBPG 5200 Vistec Electron Beam Lithography tool, individual islands were precisely patterned on the substrate. The exposed resist was developed in a 1:1 solution of 4-methyl-2-pentanone (MIBK) and 2-propanol (IPA) to reveal the patterned features. After a thorough O2 plasma sputter clean, local-gate electrodes were deposited with a 5 nm titanium and 25 nm platinum stack via a Temescal e-beam evaporator, completing the configuration.

STO nanomembrane transfer to local back-gate substrate

The transfer of the STO membrane onto the fabricated local back-gate islands was accomplished using a PDMS stamp. Initially, the PDMS stamp was delicately applied to the STO/SrO/LAO sample. Subsequently, the PDMS/STO/SrO/LAO assembly was immersed in DI water at room temperature for an hour to dissolve the SrO layer. Following the removal of the sacrificial SrO layer, tweezers were used to separate the LAO substrate from the PDMS/STO assembly. Any remaining water on the STO membrane was expelled using N2 gas. The STO membrane with the PDMS was then positioned on the target substrate (the fabricated local back-gate islands) and manually pressed with a thumb, resulting in the PDMS/STO/target substrate structure. Following this, the PDMS stamp was carefully detached from the substrate using tweezers, resulting in the transfer of the STO membrane onto the fabricated local back-gate substrate.

Large-area MoS2 film growth and its TEM/STEM characterization

The growth of MoS2 film on 2” a-plane sapphire substrates was carried out in a metal-organic chemical vapor deposition (MOCVD) system (DOI: 10.60551/znh3-mj13) equipped with a cold-wall horizontal reactor with an inductively heated graphite susceptor with gas-foil wafer rotation. Molybdenum hexacarbonyl (Mo(CO)6) (99.99%, Sigma-Aldrich) was used as the metal precursor while hydrogen sulfide (H2S) was the chalcogen source with H2 as the carrier gas. The Mo(CO)6 powder was maintained inside stainless-steel bubbler where the temperature and pressure at 25 °C and 625 Torr, respectively. The MoS2 film was grown in a single-step process33. Before the growth, the sapphire was ramped up under N2 to the growth temperature at 1000 °C and pre-annealed for 10 mins. During the growth, H2S and Mo(CO)6 were introduced to the reactor for a designated time to complete MoS2 film growth in a single step. The molybdenum flow rate was set as 4.7 × 10−3 sccm and the chalcogen (H2S) flow rate was set as 400 sccm while the reactor pressure was maintained at 50 Torr. Then, the MoS2 film was annealed under H2 and H2S ambient for 10 min at 1000 °C before cooling down to inhibit the decomposition of the obtained MoS2 film. Using this condition, the growth of a fully coalesced monolayer MoS2 was achieved in 10-30 mins across the 2” sapphire substrate. Additionally, planar view characterization of the monolayer MoS₂ film (in Fig. 1 l,m) was performed with the Thermo Fisher Scientific (TFS) Titan G2 60-300 S/TEM at an accelerating voltage of 80 kV.

MoS2 film transfer on STO nanomembranes

The transfer of the MoS2 film from the growth substrate to the application substrate was accomplished using a PMMA-assisted wet transfer method34. Initially, PMMA was spin-coated onto the MoS2 layer on the sapphire substrate and allowed to sit for 24 hours to promote strong PMMA/MoS2 adhesion. The film’s edges were then lightly scratched with a razor blade before immersion in a 2 M NaOH solution heated to 90 °C. Due to the hydrophilic nature of sapphire and the hydrophobic properties of MoS2 and PMMA, capillary action guided NaOH to the interface between the substrate and MoS2, effectively detaching the PMMA/MoS2 stack from the sapphire. The separated film was retrieved from the NaOH solution using a clean glass slide and rinsed in three consecutive water baths for 15 minutes each. It was then transferred onto the application substrate, which already contained the STO nanomembrane. Following the transfer, the substrate was baked at 50 °C and then 70 °C for 10 min each to eliminate moisture and strengthen adhesion, creating a pristine interface. Finally, the PMMA was removed by immersing the sample in acetone for one hour, followed by a 30-minute IPA bath to complete the cleaning process.

Fabrication of 2D MoS2 transistors

To define the channel regions of the MoS2 transistors in this study, the application substrate, with MoS2 transferred on top, was first spin-coated with PMMA A6 at 4000 RPM for 45 s, followed by baking at 180 °C, for 90 s. The resist was then patterned using a Raith EBPG5200 e-beam lithography tool and developed in a 1:1 solution of MIBK and IPA for 60 s, followed by an IPA rinse for 45 s. The exposed MoS2 monolayer was subsequently etched using sulfur hexafluoride (SF6) RIE at 5 °C, for 30 s. After etching, the sample was cleaned in acetone and IPA to remove the e-beam resist. A second lithography step was conducted to define the source and drain electrodes. The substrate was spin-coated with methyl methacrylate (MMA) EL6 and PMMA A3 at 4000 RPM for 45 seconds, followed by baking at 150 °C and 180 °C, for 90 s each, respectively. E-beam lithography was used again to pattern the source and drain regions, with development in the same 1:1 MIBK/IPA solution and IPA rinse as before. The electrodes were then formed by depositing 40 nm of nickel (Ni) and 30 nm of gold (Au) via e-beam evaporation. Finally, a lift-off process was performed by immersing the sample in acetone for 1 hour, followed by a 30-minute IPA rinse to clean the substrate.

Raman and photoluminescence spectroscopy

For MoS2, Raman and PL spectra were acquired on a Horiba LabRAM HR Evolution confocal Raman microscope, using a 532 nm laser set to 34 mW, filtered at 1%. The setup included a 100 × objective with a numerical aperture of 0.9 and gratings with 1800 gr mm−1 for Raman and 300 gr mm−1 for PL.

SEM analysis

The 2D MoS2 transistors used in this study were examined with SEM on a Zeiss Gemini 500 field emission scanning electron microscope (FESEM) system, operating at an accelerating voltage of 5 kV.

TEM sample preparation of fabricated FET based on 2D MoS2/3D STO nanomembranes

The TEM sample in Figs. 2d, e and 3i was carefully prepared using the TFS Scios 2 Dual Beam Focused Ion Beam Scanning Electron Microscope. To protect the device’s surface during ion beam milling and thinning, a carbon layer was first applied. A cross-section of approximately 2 µm thickness, covering the target area, was then precisely lifted out and transferred in situ to a copper half-grid. Thinning of the lamella was carried out with a Ga ion beam at five sequentially reduced voltages: 30, 16, 8, 5, and 2 kV to minimize potential damage as the sample was made progressively thinner.

STEM characterization of the cross-section of fabricated FET based on 2D MoS2/3D STO nanomembranes

The TFS Titan G2 60-300 S/TEM was utilized for both STEM and EDS analyses, as illustrated in Figs. 2d, e and 3i. The S/TEM was operated at an accelerating voltage of 300 kV, with a spot size of 6, C2 aperture of 70 µm, a convergence angle of 25.2 mrad, and a beam current of 0.07 nA. Elemental mapping was conducted in STEM mode using the SuperX EDS system, producing intensity plot images.

TEM sample preparation and STEM characterization of the cross-section of STO/SrO/LAO

The cross-sectional sample of the STO/SrO/LAO membrane was prepared using an TFS Helios NanoLab G4 dual-beam focused ion beam. To protect the sample surface, an initial 50 nm amorphous carbon layer was deposited via sputter coating, followed by additional protective layers of 1 µm each of amorphous carbon and platinum over the region of interest. The focused ion beam was operated at 30 kV with a 2 kV electron beam. A cross-section roughly 1 µm thick was then lifted out and attached to a copper half-grid. The lamella was subsequently thinned using the ion beam at 30 kV and 5 kV, with progressively reduced current to minimize potential sample damage. A TFS F200X STEM equipped with a Super-X EDX spectrometer was used to obtain HAADF images and EDX elemental maps of the STO/SrO/LAO cross-section, as shown in Fig. 1e. The microscope was operated at 200 kV with probe convergence angle of 10.5 mrad and beam current of 50-150 pA.

Second harmonic generation (SHG) measurements

SHG measurements were done using an 800 nm linearly polarized fundamental beam from a regeneratively amplified Spectra-Physics Solstice Ace Ti:sapphire laser system (1 kHz, 100 fs). The incident power was optimized at normal incidence at room temperature to minimize the SHG signal from the SiO2/Si substrate underneath the SrTiO3 membranes. Temperature-dependent SHG response was measured at a 45-degree incidence and the reflected ppolarized SHG intensity was collected using a photo-multiplier tube via lock-in detection. A Janis 300 gas flow cryostat was used for achieving low temperatures down to 77 K and the data was collected during the heating ramp performed at 5 K/min

Electrical characterization

Electrical characterization of the fabricated devices was performed in a Lake Shore CRX-VF probe station under atmospheric conditions and at 15 K using a Keysight B1500A parameter analyzer.

Data availability

Data on the MoS2 sample produced in the 2DCC-MIP facility, including growth recipes and characterization data, are available at https://doi.org/10.26207/mc6e-xz31. Other data that generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

Code availability

The codes used for plotting the data are available from the corresponding author.

References

Cao, F. et al. A dual‐functional perovskite‐based photodetector and memristor for visual memory. Adv. Mater. 35, 2304550 (2023).

Chen, J. Y., Chiu, Y. C., Li, Y. T., Chueh, C. C. & Chen, W. C. Nonvolatile perovskite‐based photomemory with a multilevel memory behavior. Adv. Mater. 29, 1702217 (2017).

Chen, S. & Shi, G. Two‐dimensional materials for halide perovskite‐based optoelectronic devices. Adv. Mater. 29, 1605448 (2017).

Jiang, M. et al. The origin of incipient ferroelectricity in lead telluride. Nat. Commun. 7, 12291 (2016).

Akbarzadeh, A., Bellaiche, L., Leung, K., Íñiguez, J. & Vanderbilt, D. Atomistic simulations of the incipient ferroelectric KTaO3. Phys. Rev. B Condens. Matter Mater. Phys. 70, 054103 (2004).

Lemanov, V., Sotnikov, A., Smirnova, E., Weihnacht, M. & Kunze, R. Perovskite CaTiO3 as an incipient ferroelectric. Solid State Commun. 110, 611–614 (1999).

Mueller, S. et al. Incipient ferroelectricity in Al‐doped HfO2 thin films. Adv. Funct. Mater. 22, 2412–2417 (2012).

Kim, Y. S. et al. Localized electronic states induced by defects and possible origin of ferroelectricity in strontium titanate thin films. Appl. Phys. Lett. 94, 202906 (2009).

Mikolajick, T. et al. Next generation ferroelectric materials for semiconductor process integration and their applications. J. Appl. Phys. 129, 100901 2021.

Li, Y. et al. Stacking and twisting of freestanding complex oxide thin films. Adv. Mater. 34, 2203187 (2022).

Dahm, R. T. et al. Size-controlled spalling of LaAlO3/SrTiO3 micromembranes. ACS Appl. Mater. Interfaces 13, 12341–12346 (2021).

Luo, Z.-D., Peters, J. J., Sanchez, A. M. & Alexe, M. Flexible memristors based on single-crystalline ferroelectric tunnel junctions. ACS Appl. Mater. Interfaces 11, 23313–23319 (2019).

Varshney, S. et al. Hybrid Molecular Beam Epitaxy for Single-Crystalline Oxide Membranes with Binary Oxide Sacrificial Layers, ACS Nano 18, 6348–6358 (2024).

Zhang, B., Yun, C. & MacManus-Driscoll, J. L. High yield transfer of clean large-area epitaxial oxide thin films. Nano Micro Lett. 13, 1–14 (2021).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

D. Li et al., Stabilization of Sr3Al2O6 growth templates for ex situ synthesis of freestanding crystalline oxide membranes. Nano Letters 21, 4454–4460 (2021).

Uwe, H. & Sakudo, T. Stress-induced ferroelectricity and soft phonon modes in SrTiO3. Phys. Rev. B 13, 271 (1976).

Guennou, M., Bouvier, P., Kreisel, J. & Machon, D. Pressure-temperature phase diagram of SrTiO3 up to 53 GPa. Phys. Rev. B 81, 054115 (2010).

Loetzsch, R. et al. The cubic to tetragonal phase transition in SrTiO3 single crystals near its surface under internal and external strains. Appl. Phys. Lett. 96, 071901 (2010).

Itoh, M. et al. Ferroelectricity induced by oxygen isotope exchange in strontium titanate perovskite. Phys. Rev. Lett. 82, 3540 (1999).

Peng, W.-W. et al. Room-temperature soft mode and ferroelectric like polarization in SrTiO3 ultrathin films: Infrared and ab initio study. Sci. Rep. 7, 2160 (2017).

Zhang, Y. et al. Room-temperature electric field-induced out-of-plane ferroelectric polarization in strain-free freestanding 2D SrTiO3 membranes. APL Mater. 11, 041103 (2023).

Liu, J. et al. Room-temperature ferroelectricity of paraelectric oxides tailored by nano-engineering. ACS Appl. Mater. Interfaces 15, 4226–4233 (2023).

Li, T. et al. Superfine nanodomain engineering unleashing ferroelectricity in incipient ferroelectrics. J. Am. Chem. Soc. 146, 20205–20212 (2024).

Nord, M., Vullum, P. E., MacLaren, I., Tybell, T. & Holmestad, R. Atomap: a new software tool for the automated analysis of atomic resolution images using two-dimensional Gaussian fitting. Adv. Struct. Chem. Imaging 3, 1–12 (2017).

Georgiou, V. et al. Ferroelectricity in polar polymer‐based FETs: A hysteresis analysis. Adv. Funct. Mater. 28, 1705250 (2018).

Wang, Z. et al. Cryogenic characterization of a ferroelectric field-effect-transistor. Appl. Phys. Lett. 116, 042902 (2020).

Mulaosmanovic, H. et al. Ferroelectric field-effect transistors based on HfO2: a review. Nanotechnology 32, 502002 (2021).

Jaeger, H. & Haas, H. Harnessing nonlinearity: Predicting chaotic systems and saving energy in wireless communication. Science 304, 78–80 (2004).

Maass, W., Natschläger, T. & Markram, H. Real-time computing without stable states: A new framework for neural computation based on perturbations. Neural Comput. 14, 2531–2560 (2002).

Zhou, Y. et al. A reconfigurable two‐WSe2‐transistor synaptic cell for reinforcement learning. Adv. Mater. 34, 2107754 (2022).

Xuan, Y. et al. Multi-scale modeling of gas-phase reactions in metal-organic chemical vapor deposition growth of WSe2. J. Cryst. Growth 527, 125247 (2019).

Sebastian, A. et al. Electrochemical polishing of two-dimensional materials. ACS Nano 13, 78–86 (2018).

Acknowledgements

Film growth and structural characterization (S.C, S.V., and B.J.) were supported by the Air Force Office of Scientific Research (AFOSR) through Grant Nos. FA9550-21-1-0025, FA9550-21-0460 and FA9550-23-1-0247. Film growth was performed using instrumentation funded by AFOSR DURIP award FA9550-18-1-0294 and FA9550-23-1-0085. S.V. was supported as part of the Center for Programmable Energy Catalysis, an Energy Frontier Research Center funded by the U.S. Department of Energy, Office of Science, Basic Energy Sciences at the University of Minnesota, under Award No. DE- SC0023464. J.S. and K.A.M. were supported partially by the UMN MRSEC program under Award No. DMR-2011401. Parts of this work were carried out at the Characterization Facility, University of Minnesota, which receives partial support from the NSF through the MRSEC program under award DMR-2011401. Parts of this work were carried out in the Characterization Facility, at the University of Minnesota, which receives partial support from the NSF through the MRSEC (Award Number DMR-2011401). Portions of this work were carried out at the Minnesota Nano Center, which receives support from the NSF through the National Nanotechnology Coordinated Infrastructure (NNCI) under Award No. ECCS-2025124. A.S., S.H., and V.G. acknowledge support from the US Department of Energy under grant no. DE-SC0012375 for optical characterization experiments. The MOCVD samples were grown in the 2D Crystal Consortium Materials Innovation Platform (2DCC-MIP) facility at Penn State, which is supported by the National Science Foundation under cooperative agreement DMR-2039351. The work was supported by the Army Research Office (ARO) through Contract Number W911NF1810268 and the National Science Foundation (NSF) through the CAREER Award under Grant Number ECCS-2042154. We also thank the partial support from the Nano & Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (RS-2024-00460372). We thank Sergei P. Stepanoff at Penn State for planar view characterization of the monolayer MoS2 film by STEM and TEM.

Author information

Authors and Affiliations

Contributions

S.D. conceived the idea and designed the experiments. D.S. fabricated the devices. D.S., H.R., M.D., and P.V. measured the devices. S.C., S.V., and B.J. grew the freestanding SrTiO3 nanomembranes. J.S. and K.A.M. performed the high-resolution (HR) STEM on the as-grown SrTiO3 nanomembranes (Fig. 1e). Z. Z. and Y. S. prepared the cross-sectional TEM sample from a 3D SrTiO3/2D MoS2 FET stack by FIB, and characterized it using STEM (Fig. 2d), under the guidance of Y.Y.. Z. Z. and Y.Y. performed HR-STEM and analyzed the polarization of SrTiO3 film under contact electrode (Fig. 3 i–l). S.H., A.S., and V.G. performed SHG analysis on SrTiO3 nanomembranes. C.C. and J.M.R. grew the large-area monolayer MoS2 films. S.S.R. helped with data analysis. All authors contributed to the preparation of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Adrian Ionescu and the other anonymous reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Sen, D., Ravichandran, H., Das, M. et al. Multifunctional 2D FETs exploiting incipient ferroelectricity in freestanding SrTiO3 nanomembranes at sub-ambient temperatures. Nat Commun 15, 10739 (2024). https://doi.org/10.1038/s41467-024-54231-z

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-024-54231-z

This article is cited by

-

High-throughput exfoliation of multiferroic ternary oxide monolayers with high transition temperature and giant spin splitting

npj Computational Materials (2025)

-

3D Integration of functionally diverse 2D materials for optoelectronic reservoir computing

Nature Communications (2025)

-

Two-Dimensional Materials, the Ultimate Solution for Future Electronics and Very-Large-Scale Integrated Circuits

Nano-Micro Letters (2025)