Abstract

Extending ferroelectric materials to two-dimensional limit provides versatile applications for the development of next-generation nonvolatile devices. Conventional ferroelectricity requires materials consisting of at least two constituent elements associated with polar crystalline structures. Monolayer graphene as an elementary two-dimensional material unlikely exhibits ferroelectric order due to its highly centrosymmetric hexagonal lattices. Here, we report the observations of electronic ferroelectricity in monolayer graphene by introducing asymmetric moiré superlattice at the graphene/h-BN interface, in which the electric polarization stems from electron-hole dipoles. The polarization switching is probed through the measurements of itinerant Hall carrier density up to room temperature, manifesting as standard polarization-electric field hysteresis loops. We find ferroelectricity in graphene moiré systems exhibits generally similar characteristics in monolayer, bilayer, and trilayer graphene, which indicates layer polarization is not essential to observe the ferroelectricity. Furthermore, we demonstrate the applications of this ferroelectric moiré structures in multi-state nonvolatile data storage with high retention and the emulation of versatile synaptic behaviors. Our work not only provides insights into the fundamental understanding of ferroelectricity, but also demonstrates the potential of graphene for high-speed and multi-state nonvolatile memory applications.

Similar content being viewed by others

Introduction

Ferroelectric materials possess electrically switchable spontaneous polarizations, which offer fascinating applications for nonvolatile memories, electric sensors, radio frequency, beyond Boltzmann tyranny transistors, and synaptic devices1,2,3,4. In conventional ferroelectric materials, the spontaneous electric polarization is formed by the spatial separation of the cation and anion, which is switchable by an external electric field (\(E\)) via small lattice displacements inside a unit cell. Recently, the emergence of two-dimensional ferroelectricity not only provides the opportunity for realizing the miniaturization and multifunction of nonvolatile devices but also opens the door to the discovery of novel ferroelectricity5,6,7,8,9. The reduced dimensionality and designable interlayer stacking in two-dimensional ferroelectric materials enable many unconventional properties different from traditional three-dimensional counterparts10,11,12,13,14,15. Among various two-dimensional ferroelectricity, the interfacial ferroelectricity is particularly intriguing because it arises from stacking non-polar constituents and exhibits high tunability and room-temperature functionality16,17,18,19,20,21,22,23. Up to now, there are mainly two kinds of interfacial ferroelectricity discovered in two-dimensional materials: one is the sliding ferroelectricity, where the out-of-plane electric polarization can be switched by in-plane interlayer sliding benefiting from the weak interlayer van der Waals force17,18,19,20,21,22,23,24; the other is the unconventional ferroelectricity observed in Bernal-stacked bilayer graphene/h-BN moiré superlattice. In contrast to lattice-driven polarization, the ferroelectricity in bilayer graphene is believed to arise from spontaneous electronic polarization4,16,25,26, which provides promising applications in ultrafast switchable memories, multiple state storage, and low-power neuromorphic devices4,27. Nevertheless, the two-dimensional materials exhibiting electronic ferroelectricity remain extremely rare, limited to bilayer graphene structures with specific alignment with h-BN16,25,26,28,29.

The origin of unconventional ferroelectricity in bilayer graphene is still elusive. Previous understanding suggested it is highly related to layer-polarized flat moiré bands and tunable quadratic bands of bilayer graphene, as evidenced by the accompanying layer-specific anomalous screening effect16,25,26,30. The switchable electronic states are presumed to arise from layer polarization of charges and interlayer charge transfer between the top and bottom layers. This interlayer charge transfer model is based on the strong electron-electron interactions in the moiré band.

Here we report the observations of unexpected electronic ferroelectricity in monolayer graphene moiré superlattices, where the layer polarization is essentially absent and linear Dirac band weakens the electron-electron interactions, in contrast to bilayer graphene systems. However, we find that in monolayer graphene, the ferroelectricity, as well as gate-specific anomalous screening (GSAS) effect, basically resembles that in bilayer graphene. The ferroelectricity in monolayer graphene manifests as the standard polarization-electric field (\({P}_{2\text{D}}-E\)) hysteresis loops and atypical multiple-state switching. Our results argue that layer polarization is not an essential factor for the observation of electronic ferroelectricity in graphene/h-BN superlattices. The underlying mechanism of electronic dynamics in these systems is unveiled by performing a series of \({P}_{2\text{D}}-E\) loop measurements. Our observations establish graphene as the thinnest ferroelectric material known to exist, enriching the fascinating properties of this wonder material. Furthermore, our discovery will promote the applications of graphene in multi-nonvolatile switchable devices with ultrahigh mobility.

Results

Ferroelectric hysteresis

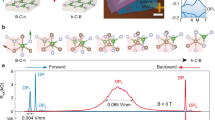

Our high-quality monolayer graphene devices were made from h-BN encapsulated structures with dual-gate configuration as depicted in Fig. 1a, which allows us to independently tune externally injected total carrier density \({n}_{\text{total}}\) and the out-of-plane displacement field \(D\). To create the moiré superlattices, we intentionally aligned the straight edges of graphene with those of both top and bottom h-BN during the assembly process. Raman spectra and second harmonic generation identified the single alignment configuration, namely, graphene crystallographically aligned with the top h-BN and misaligned with the bottom h-BN by 30° (see Methods and Supplementary Fig. 1). The single alignment can be further confirmed from the electronic transport behavior as shown in Fig. 1b, which exhibits typical graphene moiré superlattices hallmark with two satellite peaks at second Dirac point (SDP) besides the main Dirac peak at charge-neutrality point (CNP). The twist angle between graphene and top h-BN is calculated to be 0.68°, resulting in a moiré wavelength of about 12.4 nm (see Supplementary Note 2).

a Schematic of our device with asymmetric moiré interfaces and dual-gate structure. The red wavy line illustrates the moiré potential at top interface trapping holes (green balls) injected by the top gate (\({V}_{\text{t}}\)), which are bound by itinerant electrons (red balls) injected by the bottom gate (\({V}_{\text{b}}\)). The vertical arrow defines the positive electric field. Bottom panel shows conductive atomic force microscopy image of graphene/h-BN moiré superlattices. The scale bar is 50 nm. b, c Four-terminal longitudinal resistance \({R}_{{xx}}\) as a function of \({V}_{\text{t}}\) at fixed \({V}_{\text{b}}=0\) for monolayer graphene (b) and bilayer graphene (c) moiré superlattices. The arrows illustrate the sweep direction. d \({R}_{{xx}}\) as a function of \({V}_{\text{t}}\) by sweeping \({V}_{\text{t}}\) in various ranges (\({\left|{V}_{\text{t}}\right|}_{\max }\)) while fixing \({V}_{\text{b}}=0\). e \({R}_{{xx}}\) as a function of \({V}_{\text{b}}\) by sweeping \({V}_{\text{b}}\) in various ranges (\({\left|{V}_{\text{b}}\right|}_{\max }\)) while fixing \({V}_{\text{t}}=0\). The curves in (d) and (e) are vertically shifted for clarity. The forward and backward sweeps are shown in solid and dashed lines, respectively. The inset in (e) plots the difference of charge-neutrality points between forward and backward sweeps as a function of \({\left|{V}_{\text{b}}\right|}_{\max }\).

To unveil the layer-dependent ferroelectricity in graphene moiré superlattices, we fabricated a device comprising regions of monolayer, bilayer, and trilayer graphene, which allows us to in-situ compare their transport behaviors. The layer number of each region can be easily distinguished from the optical contrast and further confirmed by Raman spectra (see Supplementary Fig. 1). Figure 1b,c show the transport behaviors measured from monolayer and bilayer graphene moiré superlattices, respectively. Compared with bilayer graphene moiré superlattice, the monolayer counterpart exhibits prominent electron-hole asymmetry with hole-side SDP reaching the same order as CNP and weak electron-side SDP, which is consistent with those reported in literatures31,32,33,34,35. More characteristics of monolayer graphene can be identified from the nearly \(D\)-independent CNP (see Supplementary Fig. 2). In the main text, we mainly present the data from monolayer graphene device (Device D1-1), leaving the data from other devices including bilayer, trilayer and twisted bilayer graphene in Supplementary Information. All the data were taken at the base temperature \(T=2.2\) K unless otherwise specified.

Figure 1d, e show the transfer characteristics of monolayer graphene device given by sweeping either the top gate (\({V}_{\text{t}}\)) or bottom gate (\({V}_{\text{b}}\)) forward and backward, while keeping the other gate at zero. For \({V}_{\text{b}}\) sweeps, the forward and backward curves overlap within small gate-sweep ranges (\({\left|{V}_{\text{b}}\right|}_{\max }\le 19\) V). However, when \({\left|{V}_{\text{b}}\right|}_{\max } > 19\) V, four-terminal longitudinal resistance \({R}_{{xx}}\) exhibits remarkable hysteresis, which can be easily identified by tracking the positions of CNP and SDP. We can exclude the extrinsic origins of this hysteresis (see Supplementary Note 3). Although both \({V}_{\text{t}}\) and \({V}_{\text{b}}\) sweeps show hysteresis, they exhibit different responses across various sweeping ranges. Exceeding a critical \({\left|{V}_{\text{b}}\right|}_{\max }\), the amplitudes of hysteretic loops measured by the shift of CNP (\(\Delta {V}_{\text{b}}\)) increase with the increasing \({\left|{V}_{\text{b}}\right|}_{\max }\) as shown in the inset of Fig. 1e, while \(\Delta {V}_{\text{t}}\) are almost unchanged in \({V}_{\text{t}}\) sweep as shown in Fig. 1d. The distinct gate tunability reflects the asymmetric moiré potential at the two interfaces of graphene.

Gate-specific anomalous screening

It’s worth noting that in Fig. 1d, hole-side SDP does not appear as expected when \({\left|{V}_{\text{t}}\right|}_{\max }\le 14\) V even if the sweep range exceeds the full filling of moiré band (corresponding \(\Delta {V}_{\text{t}}^{{\prime} }=9.7\) V in this device). To further investigate this anomaly, we measured the dual-gate maps of \({R}_{{xx}}\) shown in Fig. 2, which strongly depend on the scan directions of both top and bottom gates. For example, when comparing the \({V}_{\text{t}}\) forward (Fig. 2a) with backward (Fig. 2b) maps, remarkable hysteresis can be observed by tracing the positions of CNP and SDPs. The subtraction between the forward and backward maps is plotted in Fig. 2c. Three sets of hysteretic loops consisting of red and blue peaks are associated with CNP and two SDPs.

Dual-gate maps of \({R}_{{xx}}\) by scanning \({V}_{\text{t}}\) forward (a) and backward (b) at each fixed \({V}_{\text{b}}\). c The difference between \({R}_{{xx}}\) in (a) and (b). d The corresponding \({n}_{\text{total}}-D\) plot of (c). Dual-gate maps of \({R}_{{xx}}\) by scanning \({V}_{\text{b}}\) forward (e) and backward (f) at each fixed \({V}_{\text{t}}\). g The difference between \({R}_{{xx}}\) in (e) and (f). h The corresponding \({n}_{\text{total}}-D\) plot of (g). In (a–c, e–g), the fast-scan axis and slow-scan axis are plotted in horizontal axis and vertical axis, respectively. The solid arrows illustrate the fast-scan direction, and the dashed arrows mark the slow-scan direction.

Besides the hysteresis behavior, another prominent feature in Fig. 2a is the nearly horizontal lines, manifesting as \({R}_{{xx}}\) anomalously independent of \({V}_{\text{t}}\). In normal dual-gate maps of graphene devices, the resistance peaks associated with CNP and SDPs trace as straight diagonal lines whose slopes are determined by the capacitances of two gate dielectrics, suggesting that both gates can effectively inject carriers and tune the Fermi energy. If the dual-gate maps are converted to ntotal - D maps, the diagonal lines turn into vertical lines (see Methods). However, in our device, within some regions (for instance, \(-20\,\text{V} < {V}_{\text{t}} < -5\,\text{V}\) for hole-side SDP in Fig. 2a), the position of SDP abruptly freezes, as if \({V}_{\text{t}}\) has been screened and does not work anymore. We denote this phenomenon as GSAS. In this device, \({V}_{\text{t}}\) is the specific gate, stemming from moiré superlattice at the top interface (see Supplementary Note 2). The appearances of GSAS regions depend on the scan direction of fast-scan gate as shown in Fig. 2a, b. As the fast-scan gate is changed from \({V}_{\text{t}}\) to \({V}_{\text{b}}\) as shown in Fig. 2e, f, the GSAS regions tend to shrink but still exist. Moreover, the slopes of the diagonal line are different before and after GSAS occurs. For instance, if tracing the electron-side SDP in Fig. 2f, the slope of diagonal line is normal when the slow-scan gate (\({V}_{\text{t}}\)) is swept from 25 to 12 V. Across the region of \(12\,\text{V} > {V}_{\text{t}} > 7\,\text{V}\), electron-side SDP appears as a vertical line indicating \({V}_{\text{t}}\) is screened. When \({V}_{\text{t}} < 7\,\text{V}\), trajectory of electron-side SDP becomes a diagonal line but with a smaller slope compared with initial states (\({V}_{\text{t}} > 12\,\text{V}\)), indicating that \({V}_{\text{b}}\) is partially screened in this region. The CNP and hole-side SDP show similar evolution trend, although occur at slightly different regions. The GSAS can be identified more clearly as we plot the corresponding ntotal - D maps in Fig. 2d, h, where straight lines represent the normal gating effect and oblique lines indicate screening effect. More detailed results show that GSAS also depends on the scan range of fast-scan gate (see Supplementary Figs. 9 and 10), but independent of the scan direction of slow-scan gate (see Supplementary Fig. 11).

Polarization-electric field hysteresis loops

The presence of GSAS indicates the anomalous external field tunability of charge carrier density in this system. To unveil this, we resort to the Hall measurements. The Hall resistance \({R}_{{xy}}\) directly probes the itinerant charge density given by \({n}_{\text{H}}=-B/e{R}_{{xy}}\), where \(B\) is external magnetic field, and \(e\) is the electron charge. Figure 3a shows the difference of Hall density (\(\Delta {n}_{\text{H}}\)) between forward and backward sweeps as a function of \({n}_{\text{total}}\) and \(E\), in which the fast-scan axis is \(E\), achieved by simultaneously sweeping \({V}_{\text{t}}\) and \({V}_{\text{b}}\) with a fixed relation (see Methods). In normal dual-gate devices, scanning \(E\) will not change nH (=ntotal) when fixing ntotal. Specifically, at ntotal = 0, we should achieve \({n}_{\text{H}}=0\). However, in our device, as shown in Fig. 3b,c, though ntotal is fixed at zero, prominent nonzero polarization \({P}_{2\text{D}}=e{n}_{\text{H}}{d}_{\text{dipole}}\propto {n}_{\text{H}}\) (see Methods) can be achieved and is strongly dependent on the scan history of \(E\). Similar behavior of tunable \(\Delta {n}_{\text{H}}\) by scanning \(E\) at ntotal ≠ 0 can be observed as shown in Fig. 3a. We believe this feature shares common origin as GSAS, which we will discuss later.

a The difference of Hall carrier density \({n}_{\text{H}}\) between the forward and backward sweeps of external electric field \(E\) at each fixed carrier density \({n}_{\text{total}}\). b Two-dimensional polarization \({P}_{2\text{D}}\) as a function of \(E\) measured by sweeping \(E\) sequentially in the direction denoted by the arrows at fixed \({n}_{\text{total}}=0\). c Scan-range dependent \({P}_{2\text{D}}-E\) hysteresis loops measured by the same method as that in (b). The remanent polarization \({P}_{\text{r}}\) and saturation polarization \({P}_{\text{s}}\) are extracted according to the marks in the plots. d Summary of \({P}_{\text{r}}\) and \({P}_{\text{s}}\) as a function of scan range \({\left|E\right|}_{\max }\). e Schematic of charge polarization and saturation at each process marked in (b). The red wavy lines illustrate the moiré potential. The green (red) ball denotes hole (electron). The arrows illustrate the injection (or extraction) process of charge carriers at top and bottom interfaces controlled by \({V}_{\text{t}}\) and \({V}_{\text{b}}\), respectively. The black wavy lines in Process iii and viii denote the recombination of electrons and holes. Process i, iv, v, and vi are GSAS regions. Process ii, iii, vii, and viii are the normal dual-gating regions. All the data in (b) and (c) were measured at fixed \({n}_{\text{total}}=0\). The sharp peaks near \({P}_{2\text{D}}=0\) in (b, c) are due to the measured \({R}_{{xy}}\to 0\) when passing through CNP.

Figure 3b shows a typical \({P}_{2\text{D}}-E\) hysteresis loop. Obviously, two distinct states of nonzero remanent polarization (\({P}_{\text{r}}\)) with opposite signs can be achieved at \(E=0\) after a history of applying \(E\). The signs of the two states can be reversed by applying a large \(E\) with the opposite direction. More generally, the polarization at finite \(E\) is dependent not only on the current \(E\) but also on its applied history, yielding a hysteretic loop. From Fig. 3c, d, we find no obvious hysteresis within the sweep range \({\left|E\right|}_{\max } < 28\) mV nm−1. This feature is a typical ferroelectric characteristic that switching polarization necessitates \(E\) exceeding a critical value. With increasing the sweep range of \({\left|E\right|}_{\max } > 28\) mV nm−1, the hysteresis loops and the corresponding \({P}_{\text{r}}\) dramatically increase, resulting in a large memory window with two nonvolatile states. All the above features, including both spontaneous polarization and its switchable characteristic, unambiguously confirm the observations of ferroelectricity in our system. When \({\left|E\right|}_{\max }\) is increased to \(\sim 73\) mV nm−1, \({P}_{\text{r}}\) approaches the saturation polarization (\({P}_{\text{s}}\)). Further increasing \({\left|E\right|}_{\max }\) does not change \({P}_{\text{r}}\) anymore. However, the window of hysteresis loops continuously enlarges without showing any sign of saturation with increasing \({\left|E\right|}_{\max }\). Figure 3d summarizes the \({P}_{\text{r}}\) and \({P}_{\text{s}}\) as a function of \({\left|E\right|}_{\max }\), showing a step-like increase in \({P}_{\text{r}}\) and \({P}_{\text{s}}\).

Mechanism of electronic ferroelectricity

Likewise, the measurements of \({P}_{2\text{D}}-E\) hysteresis loops provide us essential information to understand the mechanism of the observed ferroelectricity in our system. Herein, the hysteresis loops are divided into eight processes in a half cycle as shown in Fig. 3e. The other half cycle has similar processes. Normally, when we fix total carrier density \({n}_{\text{total}}=0\) and scan the electric field E, the hole density injected by \({V}_{\text{t}}\) is equal to the electron density injected by \({V}_{\text{b}}\). Thus, we will get zero Hall carrier density \({n}_{\text{H}}={n}_{\text{total}}=0\). However, in our devices, the holes injected by \({V}_{\text{t}}\) (green balls in Fig. 3e) are trapped by top moiré potential, which become localized and don’t contribute to channel conductance. This situation is analogous to the case where the holes injected by \({V}_{\text{t}}\) are zero. Meanwhile, the electrons can be injected by \({V}_{\text{b}}\) (red balls in Fig. 3e) normally and become detectable by Hall measurement. Therefore, the net carrier density \({n}_{\text{H}}\) is nonzero.

In Process i shown in Fig. 3b, e, localized holes and itinerant electrons are continuously injected by \({V}_{\text{t}}\) and \({V}_{\text{b}}\), respectively. \({n}_{\text{H}}\) is gradually increased, resulting in a nonzero polarization. The electron-hole dipole moments are formed by the localized holes at top interface and itinerant electrons at bottom interface. It’s worth noting that the bound of localized hole and itinerant electron pairs is dynamic, resembling the formation of Cooper pairs in superconductivity. On reaching Process ii, the density of the injected holes by \({V}_{\text{t}}\) approaches the half-filling of the moiré band. Further increasing \(E\) will trigger Process iii. In this process, the saturated moiré band cannot trap the additionally injected holes by \({V}_{\text{t}}\) anymore. Instead, they recombine with the electrons injected by \({V}_{\text{b}}\). Therefore, \({n}_{\text{H}}\) is saturated, and the dual-gating effect becomes valid. In Process iv, \(E\) is decreased, namely, holes and electrons are extracted by \({V}_{\text{t}}\) and \({V}_{\text{b}}\), respectively. The remaining itinerant electrons (i.e., \({n}_{\text{H}}\)) continuously decrease till zero, arriving at Process v. Further decreasing \(E\) will inject localized electrons at top interface and itinerant holes at the bottom interface, as shown in Process vi. The direction of electron-hole dipole moment (i.e., polarization) is reversed, relative to Process i-iv. In the subsequent Process vii-viii, \({n}_{\text{H}}\) saturates again, similar to Process ii-iii but with opposite values.

Besides the standard hysteresis loop, we also observed several unique switching behaviors which can support the mechanism aforementioned.

Firstly, conventional ferroelectric insulators always show an anticlockwise hysteretic \({P}_{2\text{D}}-E\) loop because the bound charges only occur at the interface17,20. However, ferroelectric semiconductors or metals, due to the presence of mobile carriers, can exhibit partial polarization switching, resulting in clockwise hysteresis36. In our system, the direction of hysteretic loops progresses in a clockwise manner as shown in Fig. 3b and c, due to itinerant charges in graphene effectively reducing the penetration depth of electric fields. This feature indicates the electric dipoles and itinerant carriers are in the same channel in our system.

Secondly, the measured saturation itinerant density \({n}_{\text{H}}^{\text{s}}\approx 1.5\times {10}^{12}\) cm−2 is independent of \({\left|E\right|}_{\max }\) and layer number (see Supplementary Fig. 16), but highly relative to moiré period. In our device, the observation of SDP facilitates the determination of the full-filling carrier density (\({n}_{\text{Full}}=3.0\times {10}^{12}\) cm−2) of a moiré band. We found that the saturation occurs at half-filling of the moiré band, as we have \({n}_{\text{H}}^{\text{s}}\approx 0.5{n}_{\text{Full}}\). Increasing temperature will thermally active the localized carriers, causing them to become itinerant ones. Therefore, we observed the decrease in \({n}_{\text{H}}^{\text{s}}\) (or \({P}_{\text{s}}\)) with increasing temperature, as shown in Fig. 4. The temperature-dependent \({n}_{\text{H}}^{\text{s}}\) follows the thermal activation fitting as shown in Supplementary Fig. 8a.

\({P}_{2\text{D}}-E\) hysteresis loops measured at various temperature for two representatives \({\left|E\right|}_{\max }=80\) mV nm−1 (a) and 36 mV nm−1 (b). The traces in (a, b) are measured from T = 2.2 K to T = 300 K with an interval of 20 K. c Temperature dependent \({P}_{\text{r}}\) at two representatives \({\left|E\right|}_{\max }=36\) mV nm−1 and 80 mV nm−1. Additionally, we observed \({P}_{\text{s}}\) decreased with the increasing of temperature for both (a, b) and the windows of \({P}_{2\text{D}}-E\) hysteresis loops were broadened at elevated temperature. d \({n}_{\text{H}}\) measured as a function of time under repetitive \(E\) pulses alternating between two equal values in amplitude but opposite sign. The upper panel shows repeated cycles of applied \(E\). e Programmable measurement of \({n}_{\text{H}}\) in response to a series of \(E\) pulses. \(E\) pulses were programmed to be alternate positive and negative values with gradually increasing amplitudes. The bottom panel is the corresponding \({n}_{\text{H}}\) as a function of time. All the \({n}_{\text{H}}\) in (d, e) are measured from \({R}_{{xy}}\) at \(B=0.1\) T without anti-symmetric processing. Therefore, there is slightly difference between positive and negative \({n}_{\text{H}}\) due to the unperfect Hall bar geometry. All the data are measured at fixed \({n}_{\text{total}}=0\).

Thirdly, above the threshold (\({\left|E\right|}_{\max } > 73\) mV nm−1), as shown in Fig. 3b, c the \({P}_{\text{r}}\) is approximately identical to the \({P}_{\text{s}}\), indicating the existence of single domain in our sample. The uniform polarization and smooth switching in our system suggest that the ferroelectricity arises more likely from electronic dynamics, rather than sliding ferroelectricity assisted by domain motions. The slope of the curve tracing from Process iv-v-vi-vii remains unchanged, regardless of variations in \({\left|E\right|}_{\max }\) (see Fig. 3c), temperature (see Fig. 4a, b), or layer number (see Supplementary Fig. 16), as it’s only relative to the gating capacity of \({V}_{\text{b}}\). The polarization switching is not due to the domain motion as that in conventional ferroelectricity or sliding ferroelectricity, but arising from the process of injecting and exctracting localized carriers assisted by GSAS as shown in Process iv-v-vi-vii.

Fourthly, when \({\left|E\right|}_{\max } < 73\) mV nm−1, Process ii is absent, because of the insufficient supply of localized carriers in Process i, resulting in \({n}_{\text{H}}^{\text{r}} \, < \, {n}_{\text{H}}^{\text{s}}\). This is also the origin of the nonmonotonic dependence of \({P}_{\text{r}}\) on temperature for \({\left|E\right|}_{\max }=36\) mV nm−1 as shown in Fig. 4b, c, because it needs to keep the slope of the GSAS curves unchanged while decreasing \({n}_{\text{H}}^{\text{s}}\) with increasing temperature. Within the region of \({n}_{\text{H}}^{\text{r}} < {n}_{\text{H}}^{\text{s}}\), quasi-continuous remanent polarizations, which are stable even after \(E\) is removed, endows the device with the functionality of multi-state data storage and multifunctional synapse emulation.

Layer independence of electronic ferroelectricity

The GSAS and ferroelectricity observed in monolayer graphene moiré superlattice resemble that in bilayer counterpart16,26. Based on previous understanding, layer-polarized flat moiré bands and interlayer charge transfer are essential roles in the emergence of ferroelectricity in graphene moiré systems. To explicitly unveil layer-dependent ferroelectricity, we intentionally designed a control device, which allows us to in-situ compare the emerging ferroelectricity in monolayer, bilayer, and trilayer graphene moiré structures. It’s found that all of these three systems exhibit ferroelectric behavior and have some characteristics in common (see Supplementary Figs. 16–19). Firstly, the ferroelectric hysteresis coexists with GSAS. Secondly, the GSAS depends on the gate sweep range and is believed to arise from the asymmetric moiré superlattice. Thirdly, the window of hysteresis loops continuously enlarges without saturation with the increasing \({\left|E\right|}_{\max }\) as shown in Fig. 3c and Supplementary Fig. 16b, which is an atypical behavior distinct from conventional ferroelectricity. Above a critical \({\left|E\right|}_{\max }\), they have the same saturation Hall carrier density \({n}_{\text{H}}^{\text{s}}\), which is independent of layer number, but highly relative to half-filling density of a moiré band (see Supplementary Fig. 16). Our results suggest the electronic ferroelectricity observed here is independent of graphene layer number and the fine band structure of graphene (see in Supplementary Figs. 16–19). However, we believe the semimetal characteristics of graphene plays a crucial role since the formation of electron-hole dipoles hinges on the facile excitation of electron-hole pairs by gates.

Robust ferroelectricity for nonvolatile memory devices

We further study the temperature dependence of electronic ferroelectricity and demonstrate proof-of-concept devices, providing promising applications of monolayer graphene ferroelectricity in multi-state data storage. As shown in Fig. 4a, c, \({P}_{\text{r}}\) decreases with increasing temperature at \({\left|E\right|}_{\max }=80\) mV nm−1, which is opposite to other extrinsic mechanisms such as charge trapping and external adsorbates (see more discussions in Supplementary Note 3), but consistent with the typical ferroelectric behavior. Specially, \({P}_{\text{r}}\) exhibits nonmonotonic dependence on temperature at \({\left|E\right|}_{\max }=36\) mV nm−1 shown in Fig. 4b, c as a unique feature of electronic ferroelectricity. Moreover, we found that the ferroelectric hysteresis loops and spontaneous polarization can persist even at room temperature as shown in Fig. 4a–c. The robustness of our electronic ferroelectricity can be further demonstrated by switching the polarization states using a small \(E\) pulse in a nonvolatile way as shown in Fig. 4d. We also check the stability of the nonvolatile switch by keeping the polarization states for an extended period, which remains almost the same for more than 12 h (see Supplementary Fig. 20).

Apart from two-state switch resembling that in conventional ferroelectric materials, the multiple spontaneous polarization states can be achieved here. It’s noted that the multi-state switch in our system is not arising from domain configurations as that in conventional ferroelectric memristors37. Instead, the tunable \({P}_{\text{r}}\) is achieved by the continuous injection of localized holes (electrons) by the specific gate (\({V}_{\text{t}}\), in this specific device) and electrons (holes) by the other gate. This unique feature endows us to utilize it to realize unconventional applications. As shown in Fig. 4e, positive and negative pulses of \(E\) are sequentially applied with gradual increase in the amplitudes. Under pulses of small \(\left|E\right| < 60\) mV nm−1, \(\left|{n}_{\text{H}}\right|\) increases quasi-continuously with increasing \(\left|E\right|\). Each polarization state is stable over time even after \(E\) is removed and switchable by changing sign of \(E\) pulse. This typical nonvolatile memory state can be widely applied to data storage. Beyond the simple two-state (0 and 1 in digital circuits) storage, our device can function as multiple-state storage.

Synapse emulation

Our ferroelectric devices exhibit diverse electrical characteristics, enabling us to emulate multifunctional synaptic activities such as synaptic plasticity including short-term plasticity (STP), long-term potentiation (LTP), and long-term depression (LTD). By programming the magnitude and sign of \(E\) pulses as shown in Fig. 5a, the nonvolatile and quasi-continuous change of \(\left|{n}_{\text{H}}\right|\) can emulate the synaptic plasticity, which is the key component of artificial synaptic devices for neuromorphic computing. In neuroscience, the long-term synaptic plasticity represents the ability of synapses to strengthen (LTP) or weaken (LTD) over time in response to increases or decreases in their activity and is widely considered as a primary mechanism for learning and memory. Analogously, in our system, by writing \(E\) pulses, the device shows potentiation and depression of \(\left|{n}_{\text{H}}\right|\) (emulating synaptic weight), which is reminiscent of LTP and LTD in synapse transistors, respectively.

a Schematic of a biological synapse. b The emulation of long-term plasticity in synaptic devices by utilizing nonvolatile multiple states in our device. \(\left|{n}_{\text{H}}\right|\) serves as the synaptic weights, which can continuously increase and decrease under a series of input stimuli (here is \(E\)), emulating the long-term potentiation and long-term depression, respectively. c The emulation of short-term plasticity. \(\left|{n}_{\text{H}}\right|\) evolves as a function of time under repetitive stimuli of \(E\). The inset shows one cycle of applied \(E\).

More excitingly, we notice that \(\left|{n}_{\text{H}}\right|\) experiences spontaneous decay in a short time at large \(E \, > \, 60\) mV nm−1, as shown in Fig. 5b. To better understand the behavior under large electric field, we investigated how \(\left|{n}_{\text{H}}\right|\) emulating the synaptic weight evolves upon application of a train of \(E\) pulses. Upon excitation of a high \({E}\) pulse, \(\left|{n}_{\text{H}}\right|\) immediately increases to a high value and gradually relaxes until the application of next pulse as shown in Fig. 5c. This feature can be used to emulate STP for processing temporal information. This process is highly reproducible and can work for over 20 cycles without any degradation in performance as demonstrated in Fig. 5c. The underlying mechanism is still to be understood but may be attributed to the saturation of moiré traps.

Discussion

Our findings of electronic ferroelectricity in monolayer graphene not only enrich its fruitful properties in this wonder material but also offer new opportunities for exploring novel physics. When interplaying with other properties in graphene such as ferromagnetism, topology, and superconductivity, intriguing properties including unconventional multiferroics and topological ferroelectrics may emerge. From the perspective of applications, nonvolatile memory and synaptic devices based on monolayer graphene possess unique advantages in terms of high mobility, high stability, and multifunctionality. Moreover, our graphene ferroelectric devices approach to 2D limit, compatible with post-Moore’s Law era devices. As aforementioned, the main ferroelectric features in monolayer graphene moiré superlattices can survive up to room temperature, further facilitating their applications. The already well-developed growth of scalable monolayer graphene superlattices can be used to construct the novel ferroelectric devices38. The h-BN required for the construction of moiré superlattices also serves as the dielectric material, which simplifies the design of ferroelectric devices.

Methods

Device fabrication

All the devices were made using standard dry-transfer method. In brief, graphene and h-BN flakes were mechanically exfoliated on the 285 nm SiO2/Si substrates. In particular, the graphene flake of Device D1 contains consecutive mono-/bi-/tri-layer parts, which were identified by their optical contrast (Supplementary Fig. 1). The top h-BN, graphene, and bottom h-BN flakes were layer-by-layer assembled using a poly(bisphenol A carbonate)/polydimethylsiloxane (PC/PDMS) stamp. Graphene flake was intentionally aligned with both top and bottom h-BN by utilizing their straight and long edges. The alignment between graphene and h-BN can be determined by transport measurement, while the relative angle between top and bottom h-BN was determined by second harmonic generation (SHG) measurements. The h-BN/graphene/h-BN heterostructure was finally released on a plasma-cleaned SiO2/Si substrate which served as back gates. The contact regions were patterned by electron beam lithography (EBL) and etched as trenches by CHF3/O2 plasma. Metallic contacts (5 nm Cr/60 nm Au) were deposited into the trenches. The metallic top gate was made by a second EBL and e-beam evaporation. The final Hall bar geometry was defined by another round of EBL and plasma etching. The list of devices, including the ferroelectricity behaviors and the stagger angles between top and bottom h-BN, are summarized in Supplementary Table 1.

Optical measurements

Raman measurements were performed at room temperature using a confocal Raman spectrometer (Witec Alpha 300RAS with UHTS 300 spectrometer) equipped with a 532 nm excitation laser. The laser spot size was about 1 μm. The second harmonic generation (SHG) measurements were conducted in the same setup with incident light wavelength of 1064 nm and a fixed excitation power of 20 mW.

Conductive atomic force microscopy measurements

The sample for conductive atomic force microscopy (c-AFM) measurements was made by sequentially picking up h-BN and graphene with PC/PDMS stamp. The stack was then flipped on a fresh PDMS. After dissolving PC with n-methyl-2-pyrrolidone (NMP), the stack was released on a new SiO2/Si substrate. The c-AFM measurements were performed on Asylum Research Jupiter XR at room temperature.

Transport measurements

The devices were wire-bonded on the LCC-44 chip carriers (Kyocera) and measured in a 4 K closed cycle refrigerator system (Janis SHI-4-2) cooled down by a Sumitomo F-20L cold head. The base temperature was 2.2 K, recorded by a calibrated sensor mounted near the sample and controlled by a Lake Shore temperature controller. All the measurements presented in the manuscript, such as dual gate mappings and \({P}_{2\text{D}}-E\) loops, except the temperature-dependent measurements, were carried out at this base temperature. The longitudinal and Hall resistances were measured by lock-in amplifier (SR-830) with constant excitation current of 100 nA. The top and bottom gates were applied by source meters (Keithley 2450).

Our dual-gate structure allows us to convert \({V}_{\text{t}}-{V}_{\text{b}}\) maps to \({n}_{\text{total}}-D\) maps. The total gate-induced carrier density is \({n}_{\text{total}}=({C}_{\text{b}}{V}_{\text{b}}+{C}_{\text{t}}{V}_{\text{t}})/e\), and the displacement field is \(D=({C}_{\text{b}}{V}_{\text{b}}-{C}_{\text{t}}{V}_{\text{t}})/2{\varepsilon }_{0}\), where \({C}_{\text{t}}\) and \({C}_{\text{b}}\) are the capacitance per area of top and bottom gate measured by Hall effect, respectively, \(e\) is the elementary charge, and \({\varepsilon }_{0}\) is the vacuum permittivity. The four-terminal longitudinal resistance \({R}_{{xx}}\) maps were acquired at zero magnetic fields unless otherwise specified.

To convert \(D\) to \(E\), we note that \({V}_{\text{b}}\) was applied on SiO2 and bottom h-BN. Therefore, the voltage across the bottom h-BN is \({V}_{\text{bBN}}=\frac{{V}_{\text{b}}{\varepsilon }_{{\text{SiO}}_{2}}{d}_{\text{bBN}}}{{\varepsilon }_{\text{BN}}{d}_{{\text{SiO}}_{2}}+{\varepsilon }_{{\text{SiO}}_{2}}{d}_{\text{bBN}}}\), where \({d}_{\text{bBN}}\) and \({d}_{{\text{SiO}}_{2}}\) are the thickness of bottom h-BN and SiO2, respectively39, \({\varepsilon }_{{\text{SiO}}_{2}}=4.3\) and \({\varepsilon }_{\text{BN}}=3.8\) are the dielectric constant of h-BN and SiO2, respectively, calibrated by capacitance measurements through Hall effect at normal gating region. The electric field across graphene is \(E=(\,{V}_{\text{bBN}}/{d}_{\text{bBN}}-{V}_{\text{t}}/{d}_{\text{tBN}}\,)/2=D/{\varepsilon }_{{BN}}\), where \({d}_{\text{tBN}}\) is the thickness of top h-BN.

n H and P 2D \(-{\boldsymbol{E}}\) loops measurements

The itinerant carrier density \({n}_{\text{H}}\) is determined from Hall effect by measuring Hall resistance \({R}_{{xy}}\) under small magnetic field of \(B=\pm 0.1\) T. \({R}_{{xy}}\) is anti-symmetrized by \({R}_{{xy}}=({R}_{{xy}}^{0.1T}-{R}_{{xy}}^{-0.1T})/2\) to remove residual values induced by unperfect sample geometry. The Hall (itinerant) carrier density is calculated to be \({n}_{\text{H}}=-B/e{R}_{{xy}}\). To measure Fig. 3a, we simultaneously swept \({V}_{\text{b}}\) and \({V}_{\text{t}}\) with a specific relation by fixing \({n}_{\text{total}}=({C}_{\text{b}}{V}_{\text{b}}+{C}_{\text{t}}{V}_{\text{t}})/e\) as a constant value, and measured \({n}_{\text{H}}\). In this way, we can realize the sweeps of \(E\) at fixed \({n}_{\text{total}}\), namely, \(E\) as fast-scan axis and \({n}_{\text{total}}\) as slow-scan axis. The \(\Delta {n}_{\text{H}}\) is the difference of \({n}_{\text{H}}\) between forward and backward sweeps of \(E\).

In order to measure \({P}_{2\text{D}}-E\) loops, we always fixed \({n}_{\text{total}}=0\). By sweeping \(E\) forward and backward in a given rang of \({\left|E\right|}_{\max }\), we acquired the response of \({n}_{\text{H}}\). The 2D polarization \({P}_{2\text{D}}\) follows \({P}_{2\text{D}}=e{n}_{\text{H}}{d}_{\text{dipole}}\)17,20, where \({d}_{\text{dipole}}\) is the size of dipole moment, i.e., the thickness of graphene. For monolayer graphene, \({d}_{\text{dipole}}=0.26\) nm40, while for bilayer graphene, \({d}_{\text{dipole}}\) is doubled as that of monolayer graphene. To compare with other ferroelectrics, we can convert \({P}_{2\text{D}}\) to \({P}_{3\text{D}}=\frac{{P}_{2\text{D}}}{{d}_{\text{dipole}}}=e{n}_{\text{H}}\). At \({\left|E\right|}_{\max }\) = 80 mV/nm, the measured saturation itinerant density is \({n}_{\text{H}}^{s}\approx 1.5\times {10}^{12}\) cm−2, yields 2D saturation polarization \({P}_{2\text{D}}=0.63\,\text{pC}/\text{m}\), which is corresponding to P3D = 0.24 μC/cm2. This value is in the same order as those in other 2D ferroelectrics, such as bilayer graphene superlattices16,25, twisted h-BN17, 3R-MoS220, while much smaller than those in other traditional ferroelectrics probably because of its 2D nature.

Reporting summary

Further information on research design is available in the Nature Portfolio Reporting Summary linked to this article.

Data availability

Relevant data supporting the findings of this study are available from the corresponding authors upon request. Source data are provided with this paper.

References

Valasek, J. Piezo-electric and allied phenomena in Rochelle salt. Phys. Rev. 17, 475–481 (1921).

Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 3, 588–597 (2020).

Khan, A. I. et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 14, 182–186 (2015).

Yan, X. et al. Moiré synaptic transistor with room-temperature neuromorphic functionality. Nature 624, 551–556 (2023).

Chang, K. et al. Discovery of robust in-plane ferroelectricity in atomic-thick SnTe. Science 353, 274–278 (2016).

Liu, F. et al. Room-temperature ferroelectricity in CuInP2S6 ultrathin flakes. Nat. Commun. 7, 12357 (2016).

Fei, Z. et al. Ferroelectric switching of a two-dimensional metal. Nature 560, 336–339 (2018).

Yuan, S. et al. Room-temperature ferroelectricity in MoTe2 down to the atomic monolayer limit. Nat. Commun. 10, 1775 (2019).

Gou, J. et al. Two-dimensional ferroelectricity in a single-element bismuth monolayer. Nature 617, 67–72 (2023).

Zhang, D., Schoenherr, P., Sharma, P. & Seidel, J. Ferroelectric order in van der Waals layered materials. Nat. Rev. Mater. 8, 25–40 (2023).

Wang, C., You, L., Cobden, D. & Wang, J. Towards two-dimensional van der Waals ferroelectrics. Nat. Mater. 22, 542–552 (2023).

Cao, Y. et al. Nematicity and competing orders in superconducting magic-angle graphene. Science 372, 264–271 (2021).

Jiang, Y. et al. Charge order and broken rotational symmetry in magic-angle twisted bilayer graphene. Nature 573, 91–95 (2019).

Cao, Y. et al. Unconventional superconductivity in magic-angle graphene superlattices. Nature 556, 43–50 (2018).

Sharpe, A. L. et al. Emergent ferromagnetism near three-quarters filling in twisted bilayer graphene. Science 365, 605–608 (2019).

Zheng, Z. et al. Unconventional ferroelectricity in moiré heterostructures. Nature 588, 71–76 (2020).

Yasuda, K., Wang, X., Watanabe, K., Taniguchi, T. & Jarillo-Herrero, P. Stacking-engineered ferroelectricity in bilayer boron nitride. Science 372, 1458–1462 (2021).

Stern, M. V. et al. Interfacial ferroelectricity by van der Waals sliding. Science 372, 1462–1466 (2021).

Weston, A. et al. Interfacial ferroelectricity in marginally twisted 2D semiconductors. Nat. Nanotechnol. 17, 390–395 (2022).

Wang, X. et al. Interfacial ferroelectricity in rhombohedral-stacked bilayer transition metal dichalcogenides. Nat. Nanotechnol. 17, 367–371 (2022).

Rogée, L. et al. Ferroelectricity in untwisted heterobilayers of transition metal dichalcogenides. Science 376, 973–978 (2022).

Woods, C. R. et al. Charge-polarized interfacial superlattices in marginally twisted hexagonal boron nitride. Nat. Commun. 12, 347 (2021).

Yang, T. H. et al. Ferroelectric transistors based on shear-transformation-mediated rhombohedral-stacked molybdenum disulfide. Nat. Electron. 7, 29–38 (2024).

Jindal, A. et al. Coupled ferroelectricity and superconductivity in bilayer Td-MoTe2. Nature 613, 48–52 (2023).

Niu, R. et al. Giant ferroelectric polarization in a bilayer graphene heterostructure. Nat. Commun. 13, 6241 (2022).

Zheng, Z. et al. Electronic ratchet effect in a moiré system: signatures of excitonic ferroelectricity. Preprint at https://arxiv.org/abs/2306.03922 (2023).

Wang, P. et al. Moiré synaptic transistor for homogeneous-architecture reservoir computing. Chin. Phys. Lett. 40, 117201 (2023).

Klein, D. R. et al. Electrical switching of a bistable moiré superconductor. Nat. Nanotechnol. 18, 331–335 (2023).

Wang, Y. et al. Ferroelectricity in hBN intercalated double-layer graphene. Front. Phys. 17, 43504 (2022).

Zhu, Z., Carr, S., Ma, Q. & Kaxiras, E. Electric field tunable layer polarization in graphene/boron-nitride twisted quadrilayer superlattices. Phys. Rev. B 106, 205134 (2022).

Hunt, B. et al. Massive Dirac fermions and Hofstadter butterfly in a van der Waals heterostructure. Science 340, 1427–1430 (2013).

Wang, L. et al. Evidence for a fractional fractal quantum Hall effect in graphene superlattices. Science 350, 1231–1234 (2015).

Ponomarenko, L. A. et al. Cloning of Dirac fermions in graphene superlattices. Nature 497, 594–597 (2013).

Dean, C. R. et al. Hofstadter’s butterfly and the fractal quantum Hall effect in moiré superlattices. Nature 497, 598–602 (2013).

Berdyugin, A. I. et al. Out-of-equilibrium criticalities in graphene superlattices. Science 375, 430–433 (2022).

Si, M. et al. A ferroelectric semiconductor field-effect transistor. Nat. Electron. 2, 580–586 (2019).

Chanthbouala, A. et al. A ferroelectric memristor. Nat. Mater. 11, 860–864 (2012).

Yang, W. et al. Epitaxial growth of single-domain graphene on hexagonal boron nitride. Nat. Mater. 12, 792–797 (2013).

Si, M., Lyu, X. & Ye, P. D. Ferroelectric polarization switching of hafnium zirconium oxide in a ferroelectric/dielectric stack. ACS Appl. Electron. Mater. 1, 745–751 (2019).

Rickhaus, P. et al. The electronic thickness of graphene. Sci. Adv. 6, eaay8409 (2020).

Acknowledgements

This work was funded by National Natural Science Foundation of China (Grant No. 12274354), the Zhejiang Provincial Natural Science Foundation of China (Grant No. LR24A040003; XHD23A2001), and Westlake Education Foundation at Westlake University. We thank Chao Zhang and Zhen Yang from the Instrumentation and Service Center for Physical Sciences (ISCPS) at Westlake University for technical support in data acquisition. We also thank Westlake Center for Micro/Nano Fabrication and the Instrumentation and Service Centers for Molecular Science for facility support. L.Z. acknowledges to the Zhejiang Province Selected Funding for Postdoctoral Research Projects (ZJ2023077). K.W. and T.T. acknowledge support from the JSPS KAKENHI (Grant Numbers 21H05233 and 23H02052) and World Premier International Research Center Initiative (WPI), MEXT, Japan.

Author information

Authors and Affiliations

Contributions

S.X. and N.X. conceived the idea and supervised the project. N.X. and L.Z. fabricated the devices. L.Z. performed the transport measurements with the assistance of J.D., W.Z., N.L., and L.W. H.X. performed AFM measurements. L.Z., W.Z., and H.X. performed Raman and SHG measurements. K.W. and T.T. grew h-BN crystals. L.Z., N.X., and S.X. analyzed the data and wrote the paper. All the authors contributed to the discussions.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Martino Aldrigo and the other anonymous reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhang, L., Ding, J., Xiang, H. et al. Electronic ferroelectricity in monolayer graphene moiré superlattices. Nat Commun 15, 10905 (2024). https://doi.org/10.1038/s41467-024-55281-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-024-55281-z

This article is cited by

-

The interplay of ferroelectricity and magneto-transport in non-magnetic moiré superlattices

Nature Communications (2025)