Abstract

Reconfigurable devices have garnered significant attention for alleviating the scaling requirements of conventional complementary metal-oxide-semiconductor technology by reducing the number of components needed to construct functional circuits. Prior work required continuous voltage application to programming gate terminal(s) alongside the primary gate, undermining the advantages of reconfigurable devices in achieving compact and power-efficient integrated circuits. Here, we realize scalable reconfigurable devices based on single-gate field-effect transistors that integrate highly aligned single-walled carbon nanotube channels with a ferroelectric aluminum scandium nitride gate dielectric. The devices exhibit ambipolar characteristics with high, well-balanced on-state currents (~270 μA μm−1 at a drain voltage of 3 V) and on/off ratios exceeding 105, along with large memory windows and excellent retention behavior. Ferroelectric polarization switching also enables reconfiguration between p- and n-channel transistors, allowing ternary content-addressable memory to be realized with far fewer devices than circuits based on conventional silicon technology or alternative memory devices.

Similar content being viewed by others

Introduction

The rapid development of artificial intelligence and the Internet of Things has accelerated data generation, thereby placing greater demands for high-capacity data processing1,2. However, scaling both device dimensions and supply voltage to meet this demand is becoming more challenging with conventional silicon (Si) complementary metal-oxide-semiconductor (CMOS) technology3,4. In particular, further size reduction of field-effect transistors (FETs) is hindered by various short-channel effects3,4, while reducing the supply voltage to deep sub-1 V levels is constrained by the Boltzmann limit4,5. These limitations not only hinder efforts to increase the device density but also result in substantial power dissipation4.

Reconfigurable devices, which can be configured into various circuit elements post-fabrication, have garnered significant attention to address the challenges associated with device downscaling and power consumption6,7,8,9,10,11,12,13. Most notable among these devices is a single reconfigurable device which can dynamically switch between p and n polarity in a FET geometry6,7,8. This reconfigurable aspect allows a circuit to perform multiple functions within a given physical layout, thereby reducing both the number of devices and the overall circuit dimensions needed to achieve specific functions10,14,15,16,17. For instance, a single circuit consisting of reconfigurable FETs demonstrated the ability to perform various Boolean logic functions, each requiring fewer unit devices compared to individual logic circuits based on standard CMOS transistors10,14,15,16. Additionally, in the design of a full adder, the use of reconfigurable FETs led to a 40% reduction in area and a 25% reduction in critical path delay15,17,18. Power consumption and circuit delay can also be reduced by using reconfigurable device-based circuits compared to CMOS counterparts, as fewer devices are required to achieve the same function14,16,17. Despite these notable advantages, the practical application of reconfigurable devices over CMOS technology is hindered by their reliance on Si nanowire channels for sufficient electrostatic doping6,7. These nanowires are either produced by bottom-up synthesis, which prevents deterministic fabrication for high device integration density8,13,19, or by top-down methods with complex processes that lead to low throughput9,11. Achieving balanced electron and hole current levels in Si channels is also challenging due to the marked differences in electron and hole effective masses8,13,20,21.

Due to their atomically thin nature and absence of surface dangling bonds, ambipolar low-dimensional semiconductors allow for effective electrostatic doping of both carrier types and support shorter scaling length than bulk semiconductors, which provides an advantage over Si22,23,24,25. Within the family of ambipolar low-dimensional semiconductors—most notably two-dimensional (2D) black phosphorous (BP), tungsten diselenide (WSe2), and molybdenum ditelluride (MoTe2), and one-dimensional (1D) single-walled carbon nanotubes (CNTs)22,26— SWCNTs distinguish themselves by having nearly equal effective masses for electron and hole as this feature enables highly balanced current levels in both n- and p-channel FET operations26,27,28. Additionally, SWCNTs can be produced at large volumes with over 99.9999% semiconducting purity using well-established growth and solution-based sorting processes29. The ability of SWCNTs to be deposited on various substrates at room temperature, combined with their chemical inertness, also enables compatibility with back-end-of-line (BEOL) processing for monolithic integration with silicon CMOS technology30,31,32,33,34, further enhancing their merit. However, obtaining high-performance, high-reliability, and low-variation semiconducting channels from SWCNTs is challenging because the SWCNTs must be assembled from solution into films at high density, with their longitudinal direction aligned parallel to the channel29,35,36,37.

In addition to the discovery of alternative channel materials, improvements in device architecture are crucial to fully leverage the benefits of reconfigurable devices. Specifically, reconfigurable FETs require additional gate terminal(s) to program the polarity of the channel (program gate), which poses a drawback for device downscaling compared to conventional three-terminal FETs consisting of a source, drain, and gate6,7,8,9,10,11,12,13. Furthermore, maintaining the designed polarity of the device necessitates continuous application of voltage on the program gate, thereby limiting power consumption reduction6,7,8,9,10,11,12,13. A viable solution involves the inclusion of a ferroelectric insulator into the gate stack, which can reduce both device dimensions and power consumption. Through spontaneous polarization, the ferroelectric layer can facilitate non-volatile adjustment of device polarity38,39 and hence support device reconfiguration without additional gate terminals and continuous gate biasing. Although SWCNT-based ferroelectric FETs (FeFETs) have been demonstrated using ferroelectric metal oxides and polymers as gate insulators, only p-type operation has been achieved40,41,42,43,44,45,46,47,48. The limited tunability of charge carrier polarity in previous SWCNT FeFETs arises because water and oxygen adsorbates can screen the electric field under positive gate bias, rendering the ferroelectric polarization insufficient to induce electron doping49,50. Ferroelectric materials with high polarizability offer the potential for enabling electrostatic n-doping of SWCNT FeFETs. Among various candidate materials, aluminum scandium nitrides (Al1−xScxN) have recently attracted significant attention due to their high remnant polarization (>100 µC cm−2)38,51, which is much higher than that of state-of-the-art hafnium zirconium oxide (HZO) films (1–40 µC cm−2)52,53. Additionally, Al1−xScxN has successfully demonstrated its compatibility with CMOS processes54,55,56 and can be deposited at BEOL-compatible growth temperature (<400 °C)38,39,57, thus serving as a promising candidate for integration with SWCNTs to potentially realize BEOL-compatible reconfigurable devices.

Here, we demonstrate reconfigurable SWCNT FeFETs that can switch between p- and n-channel FETs, as well as a non-volatile memory (NVM), by employing ferroelectric Al0.68Sc0.32N film as the gate dielectric. A dense monolayer film of semiconducting SWCNTs is first assembled with a high degree of alignment on an Al0.68Sc0.32N-deposited Si wafer to fabricate centimeter-scale device arrays with high on-state current and gate tunability. The scalability of SWCNT and Al0.68Sc0.32N films enables reliable and spatially uniform device characteristics across the array. By engineering the metal−semiconductor contact interface, we realize ambipolar behavior in the SWCNT/Al0.68Sc0.32N FeFETs. The device achieves well-balanced, high on-state hole and electron current densities (~270 μA μm−1 at a drain voltage of 3 V) and current on/off ratios exceeding 105, placing our device among the highest-performing ambipolar FeFETs reported. When operated as an NVM, the SWCNT FeFET exhibits large memory windows of 0.26 V nm−1 and 0.08 V nm−1 in the hole and electron conduction regions, respectively, with retention behavior up to 2 days. Reconfiguration between p- and n-channel FETs is also achieved by first switching the ferroelectric polarization direction and then operating the device within a gate voltage range below the coercive voltage. Both the on-state current and current on/off ratio remain similar and balanced throughout the repeated polarity switching cycles, highlighting the potential of SWCNT FeFETs in reconfigurable circuits. Lastly, we demonstrate ternary content-addressable memory (TCAM) based on SWCNT FeFETs through computer-aided circuit simulation, using significantly fewer devices compared to the conventional TCAMs that rely on multiple silicon FETs or alternative technologies based on NVM devices.

Results and discussion

Ambipolar carbon nanotube ferroelectric transistors

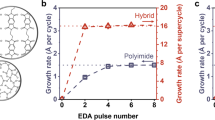

Figure 1a schematically illustrates the SWCNT FeFET fabricated in a back-gate FET configuration, which consists of a monolayer film of aligned semiconducting SWCNTs (average diameter: 1.5 nm29) as the channel and a 45-nm Al0.68Sc0.32N (hereafter denoted as AlScN) ferroelectric insulator film as the gate dielectric. A wurtzite-phase AlScN layer is first epitaxially grown on a platinized 300 nm SiO2/silicon (100) wafer, followed by the poly(methyl methacrylate) (PMMA)-assisted wet transfer process of a highly aligned SWCNT film from an SiO2/Si substrate (Methods and Supplementary Fig. 1)58,59. Notably, the dense and highly aligned nature of the monolayer SWCNT film is preserved during the transfer process, as confirmed by atomic force microscope (AFM) images of the film before and after the transfer (Supplementary Figs. 2 and 3). After the SWCNT transfer process, the channel and source/drain (S/D) electrodes are fabricated with the channel length oriented parallel to the SWCNT alignment to achieve high current density, while the AlScN in the corner region of the substrate is etched to expose the Pt back gate (G) (Methods). When a sufficiently high positive gate voltage (VGS) is applied to induce partial polarization of the AlScN, the ferroelectric polarization orients toward the channel, thereby accumulating electrons in the channel. Conversely, applying a sufficiently high negative VGS switches the polarization in the opposite direction and thus induces holes in the channel.

a Scheme describing the device architecture and operating principles. b Optical microscope images of SWCNT FeFET arrays. The scale bars in the left and right images are 60 μm and 20 μm, respectively. c Angle-resolved polarized Raman spectra of the aligned SWCNT channel measured with a 633-nm laser source. Polarization angles are defined with respect to the channel length direction. Transfer characteristics of SWCNT FeFETs fabricated using d Au and e Cr contacts. f Output characteristics of ambipolar SWCNT FeFETs (Cr-contacted) for the p- and n-type operations. Plots comparing the performance of ambipolar SWCNT FeFETs (this work) with previous works using various channel and ferroelectric materials: g on-current densities (solid data: hole current, open data: electron current) and h current on/off ratios and normalized memory windows (solid data: p-FeFET operation mode, open data: solid data: n-FeFET operation mode). i Plot showing the performance comparison of p-type SWCNT FeFETs (this work, at |VDS| of 0.1 and 1 V) with previously reported SWCNT FeFETs. Gr: graphene, HZO: HfxZr1−xO2, P(VDF-TrFE): poly(vinylidenefluoride-trifluoroethylene), CIPS: CuInP2S6, PZT: Pb(ZrxTi1−x)O3, BNT: (Bi,Nd)4Ti3O12, BTO: BaTiO3.

The wafer-scale, densely aligned SWCNT film with a purity close to industry-standard (99.9999%) enables scalable fabrication of FeFETs, as demonstrated by an optical microscope image of a centimeter-scale SWCNT FeFET array with the channel length (Lch) and width (Wch) of Lch = 500 nm and Wch = 20 μm, respectively (Fig. 1b). Importantly, our aligned SWCNT channel retains high quality with a low level of atomic-scale defects despite the wet transfer process involved in device fabrication, which is confirmed by the intensity ratio of the Raman D peak (at 1330 cm−1) to the G+ peak (at 1594 cm−1) of only 0.0229. Highly aligned nature of SWCNTs along the channel is further validated by angle-resolved polarized Raman spectra using a linearly polarized 633-nm laser source (Fig. 1c). The intensities of Raman peaks, including radial breathing mode (RBM, 156 cm−1) and the G− and G+ bands (1572 and 1594 cm−1), significantly decrease from their maximum to minimum as the polarization direction changes from parallel (polarization angle: 0°) to perpendicular (polarization angle: 90°) to the channel. The ratio of the G+ peak intensity at 0° to that at 90° is only 0.026, indicating the highly aligned assembly of SWCNTs parallel to the channel direction.

Engineering the Fermi level of the contact metal used for source/drain electrodes enables the design of the polarity of our SWCNT FeFETs, as demonstrated by the representative transfer curves obtained by measuring the drain current (IDS) as a function of VGS at a fixed drain voltage (VDS) of −0.1 V (Fig. 1d, e). In particular, we realize p-type FeFETs by employing metals with high work functions (ΦM) such as Au (ΦM = 5.1 eV60) and Pd (ΦM = 5.2 eV61), as their Fermi levels (EF) before contact (EF = − 5.1 eV for Au and −5.2 eV for Pd with respect to the vacuum level) are located below the valence band minimum (EV) of the SWCNT channel (EV = −4.75 eV62) (Supplementary Fig. 4). For gate voltage sweep ranges of VGS ≥ ± 10 V, both Au- and Pd-contacted devices exhibit clear clockwise hysteresis behavior in the hole conduction region (Fig. 1d, Supplementary Fig. 5a, b, and Supplementary Note 1), indicating that the ferroelectric polarization switching in the AlScN layer dominates the channel conductance57. The memory window (MW) and the current on/off ratio (Ion/Ioff) reach their maximum at the largest tested sweep range of VGS = ± 15 V, which is attributed to a greater degree of partial polarization switching between up and down states compared to narrower sweeps, rather than full switching, as the applied electric field (±3.3 MV cm−1) remains below the coercive field of the AlScN (–4.5/5.1 MV cm–1, as reported in our previous study on the same AlScN wafer38). The MW and Ion/Ioff ratio are 11.9 V and 4.4 × 105 for the Au-contacted devices, and 10.4 V and 2.6 × 105 for the Pd-contacted devices, with the on-current levels being similar for both types of devices. The comparison between MW and Ion/Ioff ratio indicates that the Au contact enhances the performance of SWCNT/AlScN devices as p-type FeFETs relative to the Pd contact. The p-type behavior and ferroelectricity-induced hysteresis are also robust at higher drain voltage for both Au and Pd contacts (Supplementary Fig. 6a, b).

In addition to p-type FeFETs, ambipolar FeFETs can also be fabricated using contact metals with similar Schottky barrier heights for hole and electron injection (Fig. 1d). This approach benefits from the high remnant polarization of AlScN, which can induce substantial doping levels for both types of carriers38,39. To this end, we test Ti (EF = − 4.3 eV61) and Cr (EF = − 4.5 eV61) due to their work functions being close to that of SWCNTs (EF = − 4.5 eV62) and their good adhesion with low-dimensional material channels (Supplementary Fig. 4)63,64,65,66,67. Although the Ti-contacted SWCNT FeFET exhibit ambipolar transfer characteristics, hysteresis corresponding to ferroelectric switching is observed only in the electron conduction region (Supplementary Figs. 5c and 6c). In addition, Ion and Ion/Ioff ratio are more than 2 orders of magnitude lower than those of Au- and Pd-contacted counterparts. The unexpected hysteresis behavior, along with the low Ion and Ion/Ioff ratio, most likely results from the defective channel/electrode interface caused by a reaction between the SWCNT and Ti68,69,70. Notably, unlike the Ti-contacted device, the Cr-contacted FeFET demonstrates ambipolar transfer characteristics governed by ferroelectric switching (clockwise hysteresis in the hole conduction region and counterclockwise hysteresis in the electron conduction region), with the current levels similar for both hole and electron conduction. Furthermore, Ion and Ion/Ioff ratio are comparable to those observed for the case of Au and Pd contacts (Fig. 1d and Supplementary Figs. 5d and 6d), thus motivating the use of Cr over Ti for realizing ambipolar SWCNT FeFETs. The MW and Ion/Ioff ratio are 11.0 V and 1.9 × 105 in the hole conduction region, and 3.5 V and 4.8 × 105 in the electron conduction region, for the widest VGS sweep range tested (VGS = ± 15 V). The ferroelectricity-dominated ambipolar characteristics are also evident at higher drain voltage (Supplementary Fig. 6d). In Supplementary Table 1, we summarize the device polarity and performance metrics of SWCNT FeFETs for different contact metals.

To further validate that the hysteresis of the SWCNT FeFETs originates from the ferroelectric switching of AlScN, we compare the current–voltage characteristics with those measured from back-gate SWCNT FETs fabricated using 50-nm SiO2 /Si wafers (Supplementary Fig. 7). For this comparative study, we focus on Au and Cr as representative contact metals because they achieved the best performance for p-type and ambipolar FeFETs, respectively. The SWCNT FeFET and FET employ identical electrode designs and channel dimensions (Lch = 500 nm and Wch = 20 μm) to directly examine the effect of 45-nm AlScN and 50-nm SiO2 gate dielectrics on device characteristics. Under the gate voltage sweep of VGS = ± 15 V, both the Au- and Cr-contacted FETs exhibit a p-type behavior with charge-trapping-induced hysteresis (counterclockwise) due to the absence of ferroelectricity in the SiO2 layer38. Thus, the comparison of hysteresis behavior between the SWCNT FeFET and FET further confirms that the electrical characteristics of the SWCNT FeFET are governed by the ferroelectric switching in the AlScN layer.

The switching speed of the SWCNT FeFETs provides additional support that the hysteresis behavior is mainly attributed to the ferroelectric switching rather than charge trapping. By investigating the voltage pulse conditions required to fully switch ambipolar FeFETs, we find that the required pulse width decreases approximately linearly from 500 ms to 300 μs on a semilogarithmic scale when the pulse amplitude increased from 14 V to 35 V (Supplementary Fig. 8). Previous studies revealed that charge-trapping-induced hysteresis in SWCNT FETs occurs on a time scale of hundreds of milliseconds to tens of seconds71,72, whereas our device can switch within the microsecond range, thus validating the ferroelectricity-dominant behavior of our SWCNT FeFETs. Notably, the timescale of SWCNT FeFET switching (μs–ms range) is still slower than that of the AlScN capacitor without the SWCNT channel (500 ns) due to the additional time required by other parasitic capacitances, such as channel capacitance (Supplementary Fig. 9).

Memory behavior of carbon nanotube ferroelectric transistor

One of the major advantages of semiconducting SWCNTs for electronic applications is their ability to achieve nearly equal current levels for both electron and hole conduction, a characteristic critical for ambipolar devices but often challenging to achieve with other semiconducting materials26,27,28. By measuring the output characteristics of the ambipolar FeFETs for both p- and n-type operations, we evaluate how closely hole and electron current levels align in our SWCNT channel integrated with the AlScN layer (Fig. 1f). Notably, the on-current densities for the p-type and n-type operation modes are similar for the tested drain voltage range (0 V to ±5 V). The on-current densities are ~100 μA μm−1 and ~120 μA μm−1 at |VDS | = 1 V for hole and electron conduction, respectively, under VGS of −15 V and 15 V. The on-current densities increase to ~270 μA μm−1 (hole) and ~270 μA μm−1 (electron) at |VDS | = 3 V, and further to ~375 μA μm−1 (hole) and ~340 μA μm−1 (electron) at |VDS | = 5 V. This balanced electron and hole current levels are particularly noteworthy because silicon transistors dominating the current semiconductor industry exhibit imbalanced current densities between p-type and n-type transistors, thus necessitating additional engineering efforts such as channel width adjustments8,13,20,21.

To ensure a fair assessment of our work, we compare the performance metrics of our SWCNT device with other reported FeFETs (Fig. 1g–i). As illustrated in Fig. 1g, we first compare the on-current densities, where our ambipolar SWCNT FeFET outperforms previous ambipolar FeFETs39,73,74,75,76,77,78,79,80,81,82,83,84,85, including state-of-the-art silicon technologies, such as ferroelectric FinFETs at the 14-nm technology node using HfxZr1−xO273, and graphene-based FeFETs76,77,79,80,81,82,83,84, benefiting from the large remnant polarization of AlScN ( > 100 μC cm−2) and the ability of the SWCNT channel to sustain a high charge carrier density. Notably, the hole (solid red star) and electron (open red star) currents of the SWCNT FeFET are well-balanced, and the on-current densities exceed those of all reported ambipolar FeFETs, reaching more than 4 times the densities achieved by the state-of-the-art ambipolar FeFETs fabricated with WSe2 and AlScN39. In addition to the current densities, our work demonstrates among the highest FeFET performance metrics reported for ambipolar devices, considering both the normalized MW (MW normalized by the ferroelectric thickness) and the Ion/Ioff ratio when operated as p-FeFET (solid red star) and n-FeFET (open red star) modes (Fig. 1h). Especially when comparing the Ion/Ioff ratio with graphene FeFETs (e.g., Gr/perovskite and Gr/CIPS in Fig. 1h), the advantage of using an SWCNT channel is clearly highlighted, as graphene shows poor current Ion/Ioff ratios (<10) due to its lack of bandgap76,77,79,80,81,82,83,84. We also compare our device performance with FeFETs based on SWCNTs and various ferroelectric materials40,41,42,43,44,45,46,47,48, such as metal oxide perovskites and poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) (Fig. 1i). We focus our comparison on p-type FeFETs, as all previous SWCNT FeFETs exhibit p-type behavior due to the predominance of p-type characteristics in SWCNTs when used in transistors. Our device achieves the highest performance in terms of normalized MW and on-current density, along with the third-highest Ion/Ioff ratio among the reported SWCNT FeFETs. The performance comparisons clearly demonstrate the high potential of the proposed SWCNT/AlScN system for scalable, circuit-level fabrication of ambipolar FeFETs. Furthermore, the high ferroelectric polarization of the AlScN enables electrostatic doping of electrons into the SWCNT channel under the positive gate bias, thereby and achieving ambipolar FeFETs, which was not possible in previously reported SWCNT FeFETs fabricated with other ferroelectrics40,41,42,43,44,45,46,47,48.

Based on the gate voltage and time required for switching our ambipolar SWCNT FeFETs, the writing energy is estimated to be 88 nJ bit−1. Compared to state-of-the-art commercial memory devices such as SRAM and DRAM, this energy consumption is relatively high, though comparable to NAND flash (Supplementary Table 2). However, an important point to note is that FeFETs are voltage-controlled devices, where an electric field induces threshold voltage modulation. We expect that the energy consumption can thus be reduced by lowering the switching voltage of our SWCNT FeFET through the use of an AlScN wafer with reduced thickness and higher Sc concentration38,51.

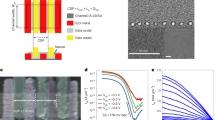

Benefiting from the scalability of SWCNT and AlScN films, the device characteristics of our FeFETs demonstrate excellent spatial uniformity across the centimeter-scale array (Fig. 2a–c and Supplementary Figs. 10 and 11). As shown in Fig. 2a, transfer curves measured from different ambipolar FeFETs (Cr contact) within the array closely match and overlap with each other. The p-type FeFETs (Au contact) also exhibit a good uniformity in transfer characteristics across the array (Supplementary Fig. 10). The device-to-device uniformity of ambipolar FeFETs is further investigated by performing statistical analyses of the key performance metrics, including MW, voltages corresponding to the minimum current in the high-resistance states (VHRS) in both the hole and electron conduction regions, and the current ratio of low-resistance state (LRS) to high-resistance state (HRS) measured at VHRS (ILRS/IHRS). The average and standard deviation (SD) of MW are 11.8 V and 0.9 V for the hole conduction side and 3.8 V and 0.6 V for electron conduction side (Supplementary Fig. 11). VHRS values are also narrowly distributed, with an average of −1.8 V (SD: 0.5 V) for hole conduction side and 5.9 V (SD: 0.5 V) for electron conduction side (Fig. 2b). The average ILRS/IHRS values corresponding to these operation voltages are 4.7 × 104 (SD: 2.3 × 104) and 3.0 × 103 (SD: 2.4 × 103) for hole and electron conduction sides, respectively (Fig. 2c).

a Transfer curves of 16 devices in the FeFET array. Histograms showing (b) HRS voltages and c ILRS/IHRS ratios at HRS voltages. d Transfer curves of the device used for retention measurements (VGS sweep range: ±15 V). Retention characteristics of memory states in e hole conduction and f electron conduction sides. Read voltages were VGS = − 0.2 V and VDS = − 0.1 V for the memory states on the p side and VGS = 5 V and VDS = 0.1 V for those on the n side.

Next, we assess the retention characteristics of the ambipolar SWCNT FeFET as a non-volatile memory device by measuring the time evolution of current levels in both LRS and HRS across hole and electron conduction regimes (Fig. 2d). Prior to the retention measurement, each state is set by applying a gate voltage pulse of |VGS | = 18 V with a pulse width of 80 ms to achieve the desired polarization. In specific, VGS = 18 V is used to achieve upward polarization for LRS in the electron conduction region and HRS in the hole conduction region, while VGS = −18 V is applied to induce downward polarization for LRS in the hole conduction region and HRS in the electron conduction region (Supplementary Fig. 12). The drain current at different time points is then read by applying VGS = −0.2 V and VDS = −0.1 V for the memory states in the hole conduction region (Fig. 2e), and VGS = 5 V and VDS = 0.1 V for the memory states in the electron conduction region (Fig. 2f). Remarkably, the LRS and HRS in both the hole and electron conduction regions exhibit fairly stable retention behavior, with ILRS/IHRS on both p and n sides exceeding 3 × 102 for up to 5 × 104 s after the initial program/erase pulse (Fig. 2e, f and Supplementary Fig. 13). The memory states are retained for an extended duration, with ILRS/IHRS values of 50 on the p side and 160 on the n side observed after 2 days (Supplementary Fig. 14), further confirming the non-volatility of our SWCNT FeFETs. To further support the non-volatile behavior of the SWCNT FeFETs, we perform retention tests at elevated temperatures up to 85 °C, which is the standard maximum temperature commonly used to evaluate the lifetime of memory devices under accelerated aging conditions86,87,88,89,90,91. Retention with a distinguishable separation between the LRS and HRS is confirmed for up to 9 h at 85 °C (Supplementary Fig. 15), although the rate of retention loss increases with temperature. Based on the observation that AlScN in a metal/ferroelectric/metal capacitor does not show retention loss within this time range (Supplementary Fig. 16), we conclude that (1) the depolarization field arising from incomplete charge compensation at the SWCNT/AlScN interface and (2) trapped charges resulting from gate leakage current are two of the possible origins of the decrease in ILRS/IHRS over time for the SWCNT FeFET92,93. The accelerated retention degradation and increased gate leakage current at the program/erase voltage (|VGS | = 18 V) at elevated temperatures further support these mechanisms (Supplementary Fig. 17 and Supplementary Note 2). Additionally, because the SWCNT channel remains under an electric field after the program/erase pulse due to the remnant polarization of AlScN, water and oxygen molecules from the ambient can become trapped at the SWCNT/AlScN interface, leading to threshold voltage shifts and contributing to retention degradation (Supplementary Note 2)94,95. Although the SWCNT FeFETs in this work show retention loss over the course of days, we would like to point out that all FeFETs inherently exhibit reduced retention compared to ferroelectric capacitor structures due to the presence of a depolarization field when the ferroelectric thin film is placed between the semiconducting channel and the metal92,93.

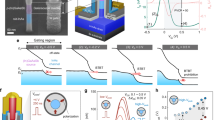

Reconfiguration between p- and n-channel transistors

In addition to serving as memory devices, our ambipolar SWCNT array enables the realization of FETs with switchable polarities, which is greatly beneficial for reducing the number of device components needed to construct circuits compared to unipolar FETs, as well as for realizing multiple circuits through reconfiguration (Fig. 3). By programming the polarization direction of AlScN with a gate bias pulse (VGS = ± 18 V, 80 ms) and operating within a VGS range smaller than the coercive voltage, we achieve switching between p-channel (polarization opposite to the channel) and n-channel (polarization toward the channel) FETs using a single SWCNT device (Fig. 3a). Figure 3b,c shows transfer curves measured over 100 cycles of device polarity reconfiguration. The stability of the SWCNT channel and AlScN layer during reconfiguration is demonstrated by the nearly consistent transfer curves. The device exhibits similar Ion and Ion/Ioff ratio for p-channel and n-channel FET operations, highlighting the advantage of the SWCNT channel in achieving symmetry between the two modes (Fig. 3d,e). Furthermore, the Ion/Ioff ratio remains above 2.5 × 103 throughout the 100 cycles of reconfiguration, which is sufficient for constructing digital circuits (Ion/Ioff > 103)96,97. Current-voltage measurements over prolonged reconfiguration cycles reveal that the device could endure 1100 cycles, after which reliable switching between p- and n-polarity is no longer achieved due to a decrease in on-current and an increase in off-current in the n-FET mode with further cycling (Supplementary Fig. 18). Additionally, the threshold voltage of the n-FET mode shifts toward a higher positive voltage, causing the device to behave like a p-FET. Comparison of the endurance between the SWCNT FeFET and the metal/AlScN/metal capacitor (11,800 cycles, Supplementary Fig. 19) indicates that the endurance of the SWCNT FeFET is limited by the SWCNT/AlScN interface.

Ternary content-addressable memory using a single device

The experimental results presented thus far demonstrate that our SWCNT FeFET offers a variety of multifunctional capabilities, including p-polar and ambipolar NVM devices, as well as p- and n-type polarity switchable FETs. In this section, we show the practical utility of the SWCNT FeFET in circuit applications, specifically by demonstrating its use in ternary content-addressable memory (TCAM). Notably, as will be compared in more detail, a single ambipolar SWCNT FeFET provides the full functionality required for a non-volatile TCAM, in contrast to conventional CMOS-based TCAM designs, which typically require 10 or more transistors98.

To validate this, we perform circuit simulations using Cadence Virtuoso. The TCAM circuit comprises an SWCNT FeFET, a PMOS transistor, and a pre-charge capacitor (Fig. 4a). The SWCNT FeFET serves as the core-cell of the TCAM (whereas conventional silicon-based TCAM requires at least 10 transistors as will be discussed), while the PMOS transistor charges the pre-charge capacitor, which is used to evaluate whether the input to the search line (SL) matches the stored state in the core SWCNT FeFET. It is important to note that the PMOS transistor and pre-charge capacitor are peripheral components to the TCAM core-cell, and multiple TCAM core-cells are typically connected to the peripheral circuitry.

a Schematic illustration of the TCAM circuit based on an ambipolar SWCNT FeFET. b Transfer curves of the ambipolar FeFET, showing the distinct behavior in different polarization states: “0” (red), “1” (blue), and “don’t care” (“X”) (purple) states. c Scheme describing the channel conduction across all possible cases, demonstrating how the match or mismatch between the search voltage (VSL) and the stored state in the FeFET affects conduction. d Simulation results reflecting the behavior of the TCAM for each matching and mismatching scenario, with corresponding voltage outputs for the match line (ML). e A comparison table showcasing various TCAM circuit configurations, including conventional silicon-based transistors, RRAM or PCM-based systems, and FeFET-based designs. The table highlights the significant reduction in component count achieved with the ambipolar FeFET, which requires only a single device for full TCAM functionality, thus representing the most compact non-volatile solution.

Figure 4b presents the experimental transfer curves of the ambipolar SWCNT FeFET, where each curve exhibits a different threshold voltage due to shifts caused by varying degrees of ferroelectric polarization. We define the curve with the leftmost threshold voltage (red) as state “0,” the one with the rightmost threshold voltage (blue) as state “1,” and the middle curve (purple) as the “don’t care” state, “X.” Note that the leftmost and rightmost threshold voltages differ slightly from those in Fig. 3b, c, as a wider gate voltage range (VG from −8 to 10 V, instead of −2 to 5 V) is swept to achieve sufficiently high contrast between current levels for the three states. Sweeping this wider voltage range might have induced partial polarization of the pre-polarized AlScN, resulting in shifts in threshold voltages compared to when a narrower gate voltage sweep range is used. For reliable circuit simulations, we emphasize that the experimentally obtained transfer curves are directly used to create an accurate model within Cadence. As shown in Supplementary Fig. 20, this model precisely replicates the experimental transfer curves and serves as the basis for the TCAM demonstration.

To provide a comprehensive understanding of the TCAM operation, we schematically illustrate different scenarios in Fig. 4c based on the input and stored states of the ambipolar FeFET. When the stored state and the search voltage (VSL) match—meaning the FeFET state is “0” (or “1”) and VSL is likewise “0” (or “1”)—the current through the FeFET channel is low. Conversely, when the stored state of the FeFET and VSL do not match, the current is high. In cases where the “don’t care” state (“X”) is stored, the current remains low regardless of whether VSL is “0” and “1,” enabling full TCAM functionality. These current levels, as functions of the FeFET state and VSL, are visually illustrated in Fig. 4b for better clarity.

Based on this operational principle, a full TCAM circuit simulation is performed as shown in Fig. 4d and Supplementary Fig. 21. The topmost curve (black) in Fig. 4d represents the pre-charge voltage (VPre), which is applied to charge the pre-charge capacitor to 1 V. The orange curve shows the applied VSL, while the red, blue, and purple curves represent the voltage on the match line (ML) corresponding to the stored states of the FeFET: “0,” “1,” and “X.” Depending on whether the stored state matches or mismatches with the applied VSL, the voltage across the pre-charged capacitor is either discharged to ground or maintained. In this simulation, a 1 pF capacitor is used, yielding a discharge time (t) of 1 μs, which is determined using the equation I × t = C × V, where I is the current, C is the capacitance, and V is the voltage. When the stored state and VSL do not match, the current through the FeFET is approximately 1 μA, and with a 1 V charge across the capacitor, the discharge time is around 1 μs with a 1 pF capacitor. In contrast, when the stored state and VSL match, the current is two orders of magnitude lower than the mismatched case, resulting in a discharge time that is more than 100 times longer, allowing for a clear distinction between the stored “0” and “1” states. In the case of the “X” state, the current is more than an order of magnitude lower than 1 μA, which yields a discharge time more than 10 times longer compared to the mismatched case. This difference in discharge times enables reliable TCAM operation with clear state distinction, as reflected in Fig. 4d. The charge in the capacitor is quickly discharged, lowering the ML voltage only when the stored state and VSL do not match. Conversely, when the stored state matches VSL or is “X”, the capacitor charge and thus the ML voltage are retained.

This demonstration of full TCAM functionality using a single ambipolar FeFET as the core component represents a significant advancement in reducing the number of components required, especially when compared to conventional silicon CMOS-based TCAM designs. As shown in Fig. 4e, traditional TCAM configurations typically require more than 10 transistors98. Recent developments using alternative technologies, such as resistive random-access memory (RRAM)99, phase-change memory (PCM)100, or even unipolar FeFETs101,102, have managed to lower the number of components to around 4 or 2 components. However, the ambipolar FeFET-based TCAM presented here stands out as the most compact design, requiring only a single ambipolar FeFET (Fig. 4e), which significantly simplifies the circuit architecture while maintaining functionality. This reduction in component count could offer substantial benefits in terms of integration density and power efficiency when scaled to large arrays and implemented in highly miniaturized devices.

In summary, we have demonstrated a scalable array of single-gate reconfigurable devices capable of switching between p-type and n-type FETs as well as NVMs, based on SWCNT/AlScN FeFETs. The strong spontaneous polarization of AlScN, combined with the excellent ambipolarity of the SWCNT channel, enables high and balanced on-state current densities (~270 μA μm−1 at a drain voltage of 3 V) and wide memory windows (0.26 V nm−1 and 0.08 V nm−1, respectively) in both the hole and electron conduction regimes. These performance metrics are among the highest reported for ambipolar FeFETs with different channel materials and ferroelectric combinations. Remarkably, the balanced on-current densities for both types of carriers represent a significant advancement over previous devices based on silicon and other state-of-the-art ambipolar semiconductors such as WSe2 and MoTe2, where the asymmetry of electron and hole effective masses makes achieving balance highly challenging. Leveraging the reliable reconfiguration between p-type and n-type FETs, a TCAM cell can be constructed with significantly fewer devices compared to conventional MOSFETs with fixed polarities and other recent technologies, highlighting the potential of SWCNT FeFETs for miniaturized, low-power circuit applications.

We emphasize that the optimization of device architecture should enable further enhancement in performance and reduce energy consumption. First, our work uses a global bottom gate instead of individual gates for each device, and hence, all devices on the substrate are affected when a gate bias is applied to a specific device. This issue can be addressed by patterning the AlScN and bottom Pt gate electrodes using reactive ion etching, which allows each device to have a designated AlScN/Pt back gate while the devices remain electrically isolated. Also, the operating gate voltage of the SWCNT/AlScN FeFET in the present study (±15 V) is higher compared to the FeFETs based on hafnium zirconium oxides and silicon (typically < ±5 V)103,104,105. In addition, while the SWCNT/AlScN FeFET-based TCAM cell introduces the innovation of using a single device to realize a TCAM cell, our TCAM cell remains larger, slower, and less energy-efficient than conventional SRAM-based counterparts. Reducing the operating voltage and switching energy for both the FeFET and TCAM cell can be achieved by decreasing the AlScN thickness and lowering the coercive voltage through increased scandium concentration. As AlScN exhibits robust ferroelectricity even at a thickness of 5 nm based on our on-going work, we anticipate that reducing the AlScN thickness from 45 nm (used in this work) to 5 nm in future research is expected to significantly scale down the switching voltage and energy. Additionally, further scaling of voltage and energy is expected by using a higher Sc concentration (36% or 39%, instead of 32% used in this work) in AlScN. Reducing the device size can decrease both cell size and switching time for the single FeFET-based TCAM, potentially offering significant advantages over SRAM-based TCAM cells, which typically consist of 10 or more transistors. Lastly, the channel length can be further reduced to increase the on-current density and reduce the device size for potential high-density integration in the future.

Overall, our device demonstrates strong potential towards commercialization since both AlScN and SWCNTs have been widely adopted in the industry and are reported to be compatible with CMOS BEOL integration. Our work promises the realization of high-performance reconfigurable devices based on highly scalable 1D semiconductors and III-nitride ferroelectric films, creating opportunities for post-Moore’s Law innovations.

Methods

Production of aligned semiconducting SWCNT films

Aligned semiconducting SWCNT films are produced based on a procedure reported in a previous work29. First, high-purity ( > 99.9999%) semiconducting SWCNT dispersions are obtained by sorting arc-discharged CNT powders, which consist of a mixture of semiconducting and metallic CNTs, as well as metallic catalysts used for CNT synthesis. Commercially purchased arc-discharged CNT powders (AP-SWNT from Carbon Solutions, Inc.) are dissolved in in toluene with the presence of conjugated poly[9-(1-octylonoyl)-9H-carbazole-2,7-diyl] (PCz) molecules as dispersants, followed by multiple iterations of ultracentrifugation, rinsing with tetrahydrofuran, and redispersion in 1,1,2-trichloroethane to enrich semiconducting SWCNTs with diameters narrowly distributed around 1.5 nm. Next, the resulting SWCNTs are assembled into an aligned film using dip coating in the presence of interfacial confinement. Specifically, after vertically dipping a 4-inch 300 nm SiO2/Si wafer into the dispersion, 2-butene-1,4-diol, which is immiscible with the subphase 1,1,2-trichloroethane but can interact with the PCz-wrapped SWCNTs, is spread around the interface between the wafer, 1,1,2-trichloroethane, and air. Because SWCNTs in the 1,1,2-trichloroethane do not stick to the wafer surface, only the SWCNTs confined at the 1,1,2-trichloroethane/2-butene-1,4-diol/wafer interface are deposited on the wafer during the withdrawal stage, while SWCNTs are continually supplied from the 1,1,2-trichloroethane subphase. The wafer is withdrawn at a speed of 2 μm s−1, resulting in a dense, monolayer film of highly aligned SWCNTs.

AlScN growth

To grow AlScN (Al0.68Sc0.32N) films with the desired crystal orientation via sputter deposition, we use a Pt (111) surface as the growth seed. Specifically, we employ commercially available 4-inch Si (100) wafers with a 300 nm SiO2 layer, sequentially deposited with a 10 nm Ti seed/adhesion layer and a 150 nm Pt film exhibiting (111) crystal orientation (Pt/Ti/SiO2/Si) (MTI Corporation). On these wafers, Al and Sc are co-sputtered using a 150 kHz pulsed DC sputter deposition instrument (CLUSTERLINE® 200 II, Evatec) with a nitrogen flow of 20 sccm under a pressure of 8.3 × 10−4 mbar. We kept the chamber temperature at 350 °C to maintain the compatibility with potential BEOL integration. Diced pieces from the AlScN/Pt/Ti/SiO2/Si wafer produced in our previous works38,39 are used as substrates in this study.

Devices fabrication

To fabricate ferroelectric field-effect transistors, the aligned SWCNT film is first transferred from the 300 nm SiO2/Si substrate onto an AlScN/Pt/Ti/SiO2/Si substrate using the poly(methyl methacrylate) (PMMA)-assisted wet transfer method58,59. Specifically, a 640-nm thick PMMA support layer is coated on a ~ 1 cm2 piece of the aligned SWCNT/300 nm SiO2/Si wafer by spin coating an 8% PMMA solution in anisole (495 PMMA A8, Kayaku Advanced Materials Inc.) at 2500 rpm for 60 s, followed by baking on a hot plate at 180 °C for 5 min. The PMMA/SWCNT bilayer film is then released from the substrate by etching the SiO2 layer with 2 M KOH (Sigma Aldrich) at 60 °C for approximately 90 min. The PMMA/SWCNT stack is floated sequentially on three baths of deionized water to rinse off residual KOH from the surface of SWCNT and then transferred on a 2:1 volume mixture of water and isopropanol (IPA). The addition of IPA is critical for reducing the surface tension of the liquid, enabling the transfer of PMMA/SWCNT onto the hydrophobic surface of AlScN106,107. After etching the aluminum capping layer from the AlScN/Pt/Ti/SiO2/Si substrate using 1% hydrofluoric acid, the PMMA/SWCNT film is immediately transferred on the AlScN surface by dipping the substrate into the water/IPA mixture and scooping the bilayer stack. Following solvent evaporation, the PMMA layer is removed from the SWCNT film using acetone and IPA. Subsequently, the sample is annealed at 350 °C with a 100 sccm H2/Ar (15 % H2, balance Ar) flow for 2 h to further remove residual PMMA.

Next, we fabricate the electrode and channel by performing electron-beam lithography using a bilayer PMMA resist. The first resist layer is created by spin coating a 4% PMMA solution in anisole (495 PMMA A4, Kayaku Advanced Materials Inc.) at 2500 rpm for 60 seconds and baking at 180 °C for 5 min. Subsequently, another spin coating procedure is conducted at 2500 rpm for 60 seconds using an 8% PMMA solution (495 PMMA A8, Kayaku Advanced Materials Inc.), followed by baking at 180 °C for 5 min to create the second resist layer. We then define the source and drain electrode regions by exposing the PMMA layer to a 50 kV electron beam using an electron-beam lithography instrument (Elionix ELS-7500EX, Elionix Inc.), after which the sample is immersed in a methyl isobutyl ketone (MIBK)/IPA mixture (1:3 volume ratio) for 40 seconds to develop the resist. Through the patterned PMMA layer, we selectively deposit contact metals on the exposed SWCNT surface via electron-beam evaporation (PVD 75 electron-beam evaporator, Kurt J. Lesker Company). To create devices with gold and palladium contacts, we deposit a total of 50 nm of the metal, with the initial 20 nm deposited at 0.2 Å s−1 and the remaining 30 nm at 2 Å s−1. For the fabrication of chromium and titanium contact devices, 20 nm of chromium or titanium is first deposited at 0.2 Å s−1. To prevent surface oxidation of the chromium and titanium contact under ambient conditions, a 30 nm gold capping layer is deposited at 2 Å s−1 without breaking vacuum. After the metal deposition, the PMMA layer is removed from the SWCNT film via lift-off using acetone, resulting in an array of source and drain electrodes in areas that are not covered by the patterned PMMA. To define channels in the SWCNT film, another bilayer PMMA resist is spin-coated onto the sample using 4% and 8% PMMA solutions, followed by electron-beam lithography and development in a 1:3 mixture of MIBK/IPA. SWCNTs in regions outside the PMMA patterns are etched by performing reactive ion etching (Jupiter II tabletop reactive ion etcher, March Instruments) with oxygen gas (flow rate: 90 sccm) at a power of 100 W for 40 s. Then, PMMA is removed from the surface using acetone to complete the device fabrication.

Metal/AlScN/metal capacitors for characterizing the switching speed, retention, and endurance of the AlScN are fabricated using the same electron-beam lithography procedure described above. After patterning an array of circular (radius: 20 µm) regions into the bilayer PMMA resist film spin-coated on the AlScN/Pt/Ti/SiO2/Si substrate, 10 nm of Ti and 50 nm of Au are sequentially deposited, followed by PMMA lift-off to create the top electrodes. The Pt film beneath the AlScN serves as the bottom electrode of the capacitor.

Electrical characterization of devices

Electrical measurements are conducted at room temperature using a probe station (Cascade Microtech MPS 150, FormFactor Inc.) connected to a semiconductor parameter analyzer (Keithley 4200A-SCS parameter analyzer, Tektronix Inc.).

Raman spectroscopy

Polarized Raman spectra of aligned SWCNT films are obtained using a confocal Raman spectrometer (LabRAM HR Evolution, Horiba Scientific) equipped with a 633 nm laser excitation source and a 100× objective lens. The incident laser from the source is linearly polarized using a polarizer, with the polarization angle controlled by a half-wave plate. Samples are excited with a power below 2 mW to minimize damage to SWCNTs. Raman scattering signals from the sample are dispersed by a diffraction grating with 600 grooves per millimeter and recorded by a charged-coupled device (CCD) detector.

Microscopy

Optical microscope images of devices are obtained using a bright-field optical microscope (Olympus BX51, Olympus Corporation). The surface topography of aligned SWCNT films is characterized using an atomic force microscope (Bruker ICON, Bruker Corporation) operated in tapping mode.

Data availability

The data that support the findings of this study are present in the Article and the Supplementary information or available from the corresponding authors upon request.

References

López, C. Artificial intelligence and advanced materials. Adv. Mater. 35, 2208683 (2023).

Sugiura, T., Yamamura, K., Watanabe, Y., Yamakiri, S. & Nakano, N. Circuits and devices for standalone large-scale integration (LSI) chips and Internet of Things (IoT) applications: A review. Chip 2, 100048 (2023).

Ratnesh, R. K. et al. Advancement and challenges in MOSFET scaling. Mater. Sci. Semicond. Process. 134, 106002 (2021).

Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479, 310–316 (2011).

Beckers, A., Jazaeri, F. & Enz, C. Theoretical limit of low temperature subthreshold swing in field-effect transistors. IEEE Electron. Device Lett. 41, 276–279 (2020).

Mikolajick, T. et al. 20 Years of reconfigurable field-effect transistors: From concepts to future applications. Solid State Electron 186, 108036 (2021).

Mikolajick, T. et al. Reconfigurable field effect transistors: A technology enablers perspective. Solid State Electron 194, 108381 (2022).

Heinzig, A., Slesazeck, S., Kreupl, F., Mikolajick, T. & Weber, W. M. Reconfigurable silicon nanowire transistors. Nano Lett. 12, 119–124 (2012).

Marchi, M. D. et al. Polarity control in double-gate, gate-all-around vertically stacked silicon nanowire FETs. 2012 International Electron Devices Meeting; 2012. p. 8.4.1-8.4.4.

Trommer, J., et al. Reconfigurable nanowire transistors with multiple independent gates for efficient and programmable combinational circuits. 2016 Design, Automation & Test in Europe Conference & Exhibition; 2016. p. 169-174.

Lim, D. & Kim, S. Polarity control of carrier injection for nanowire feedback field-effect transistors. Nano Res 12, 2509–2514 (2019).

Lim, D., Cho, K. & Kim, S. Reconfigurable logic-in-memory using silicon transistors. Adv. Mater. Technol. 7, 2101504 (2022).

Qian, W., Wang, J., Xu, J. & Yu, L. Channel-bias-controlled reconfigurable silicon nanowire transistors via an asymmetric electrode contact strategy. Chip 3, 100098 (2024).

Amarú, L., Gaillardon, P. E. & Micheli, G. D. A circuit synthesis flow for controllable-polarity transistors. IEEE Trans. Nanotechnol. 13, 1074–1083 (2014).

Raitza, M. et al. Exploiting transistor-level reconfiguration to optimize combinational circuits. Design, Automation & Test in Europe Conference & Exhibition; 2017. p. 338-343.

Rai, S. et al. Designing efficient circuits based on runtime-reconfigurable field-effect transistors. IEEE Trans. Very Large Scale Integr. VLSI Syst. 27, 560–572 (2019).

Gore, G., Cadareanu, P., Giacomin, E. & Gaillardon, P. E. A predictive process design kit for three-independent-gate field-effect transistors. 2019 IFIP/IEEE 27th International Conference on Very Large Scale Integration (VLSI-SoC); 2019. p. 172-177.

Fei, W., Trommer, J., Lemme, M. C., Mikolajick, T. & Heinzig, A. Emerging reconfigurable electronic devices based on two-dimensional materials: A review. InfoMat 4, e12355 (2022).

Trommer, J., Heinzig, A., Slesazeck, S., Mikolajick, T. & Weber, W. M. Elementary aspects for circuit implementation of reconfigurable nanowire transistors. IEEE Electron Device Lett. 35, 141–143 (2014).

Barber, H. D. Effective mass and intrinsic concentration in silicon. Solid State Electron 10, 1039–1051 (1967).

Green, M. A. Intrinsic concentration, effective densities of states, and effective mass in silicon. J. Appl. Phys. 67, 2944–2954 (1990).

Hu, W. et al. Ambipolar 2D semiconductors and emerging device applications. Small Methods 5, 2000837 (2021).

Wei, T. et al. Two dimensional semiconducting materials for ultimately scaled transistors. iScience 25, (2022).

Lin, Y. et al. Scaling aligned carbon nanotube transistors to a sub-10 nm node. Nat. Electron. 6, 506–515 (2023).

Rhee, D., Jariwala, D., Cho, J. H. & Kang, J. Solution-processed 2D van der Waals networks: Fabrication strategies, properties, and scalable device applications. Appl. Phys. Rev. 11, 021310 (2024).

Zorn, N. F. & Zaumseil, J. Charge transport in semiconducting carbon nanotube networks. Appl. Phys. Rev. 8, 041318 (2021).

Zhang, Z. et al. Almost perfectly symmetric SWCNT-based CMOS devices and scaling. ACS Nano 3, 3781–3787 (2009).

Peng, L.-M., Zhang, Z. & Wang, S. Carbon nanotube electronics: Recent advances. Mater. Today 17, 433–442 (2014).

Liu, L. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 368, 850–856 (2020).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Bishop, M. D. et al. Fabrication of carbon nanotube field-effect transistors in commercial silicon manufacturing facilities. Nat. Electron. 3, 492–501 (2020).

Hills, G. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 572, 595–602 (2019).

Li, Y. et al. Monolithic three-dimensional integration of RRAM-based hybrid memory architecture for one-shot learning. Nat. Commun. 14, 7140 (2023).

Cheng, C. C. et al. Monolithic heterogeneous integration of BEOL power gating transistors of carbon nanotube networks with FEOL Si ring oscillator circuits. 2019 IEEE International Electron Devices Meeting (IEDM); 2019. p. 19.12.11-19.12.14.

Li, X. et al. Langmuir−Blodgett assembly of densely aligned single-walled carbon nanotubes from bulk materials. J. Am. Chem. Soc. 129, 4890–4891 (2007).

Shekhar, S., Stokes, P. & Khondaker, S. I. Ultrahigh density alignment of carbon nanotube arrays by dielectrophoresis. ACS Nano 5, 1739–1746 (2011).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

Kim, K.-H. et al. Scalable CMOS back-end-of-line-compatible AlScN/two-dimensional channel ferroelectric field-effect transistors. Nat. Nanotechnol. 18, 1044–1050 (2023).

Kim, K.-H. et al. Tuning polarity in WSe2/AlScN FeFETs via contact engineering. ACS Nano 18, 4180–4188 (2024).

Sakurai, T., Yoshimura, T., Akita, S., Fujimura, N. & Nakayama, Y. Single-wall carbon nanotube field effect transistors with non-volatile memory operation. Jpn. J. Appl. Phys. 45, L1036 (2006).

Sun, Y. et al. Ferroelectric polarization effect on hysteresis behaviors of single-walled carbon nanotube network field-effect transistors with lead zirconate-titanate gating. Curr. Appl. Phys. 18, 324–328 (2018).

Fu, W., Xu, Z., Bai, X., Gu, C. & Wang, E. Intrinsic memory function of carbon nanotube-based ferroelectric field-effect transistor. Nano Lett. 9, 921–925 (2009).

Fu, W. Y., Xu, Z., Liu, L., Bai, X. D. & Wang, E. G. Two-bit ferroelectric field-effect transistor memories assembled on individual nanotubes. Nanotechnology 20, 475305 (2009).

Tan, Q. et al. Carbon nanotube nonvolatile thin-film transistors with (Bi,Nd)4Ti3O12 gate insulators. IEEE Trans. Electron Devices 61, 2628–2632 (2014).

Tan, Q. et al. Single-walled carbon nanotube dominated micron-wide stripe patterned-based ferroelectric field-effect transistors with HfO2 defect control layer. Nanoscale Res. Lett. 13, 127 (2018).

Son, J. Y. et al. A nonvolatile memory device made of a ferroelectric polymer gate nanodot and a single-walled carbon nanotube. ACS Nano 4, 7315–7320 (2010).

Sun, Y.-L. et al. Controllable hysteresis and threshold voltage of single-walled carbon nanotube transistors with ferroelectric polymer top-gate insulators. Sci. Rep. 6, 23090 (2016).

Li, M. et al. Tailoring neuroplasticity in a ferroelectric-gated multi-terminal synaptic transistor through bi-directional modulation for improved pattern edge recognition. Adv. Funct. Mater. 33, 2307986 (2023).

Duong, D. L., Lee, S. M. & Lee, Y. H. Origin of unipolarity in carbon nanotube field effect transistors. J. Mater. Chem. 22, 1994–1997 (2012).

Aguirre, C. M. et al. The role of the oxygen/water redox couple in suppressing electron conduction in field-effect transistors. Adv. Mater. 21, 3087–3091 (2009).

Fichtner, S., Wolff, N., Lofink, F., Kienle, L. & Wagner, B. AlScN: A III-V semiconductor based ferroelectric. J. Appl. Phys. 125, 114103 (2019).

Asapu, S. et al. Large remnant polarization and great reliability characteristics in W/HZO/W ferroelectric capacitors. Front. Mater. 9, 969188 (2022).

Lederer, M., Lehninger, D., Ali, T. & Kämpfe, T. Review on the microstructure of ferroelectric hafnium oxides. Phys. Status Solidi - Rapid Res. Lett. 16, 2200168 (2022).

Pinto, R. M. R., Gund, V., Dias, R. A., Nagaraja, K. K. & Vinayakumar, K. B. CMOS-integrated aluminum nitride MEMS: A review. J. Microelectromech, Syst. 31, 500–523 (2022).

Liu, Y., et al. Characterization of AlScN on CMOS. 2020 Joint Conference of the IEEE International Frequency Control Symposium and International Symposium on Applications of Ferroelectrics (IFCS-ISAF); 2020. p. 1-5.

Liu, Y., Kuo, J., Lal, A., Sharma, J. & Singh, N. Characterization of metal effect on solidly mounted AlScN on CMOS. 2020 IEEE International Ultrasonics Symposium (IUS); 2020. p. 1-4.

Liu, X. et al. Post-CMOS compatible aluminum scandium nitride/2D channel ferroelectric field-effect-transistor memory. Nano Lett. 21, 3753–3761 (2021).

Rhee, D. et al. Hierarchical nanoscale structuring of solution-processed 2D van der Waals networks for wafer-scale, stretchable electronics. ACS Appl. Mater. Interfaces 14, 57153–57164 (2022).

Rhee, D., Lee, Y.-A. L. & Odom, T. W. Area-specific, hierarchical nanowrinkling of two-dimensional materials. ACS Nano 17, 6781–6788 (2023).

Ofuonye, B. et al. Electrical and microstructural properties of thermally annealed Ni/Au and Ni/Pt/Au Schottky contacts on AlGaN/GaN heterostructures. Semicond. Sci. Technol. 29, 095005 (2014).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Hirana, Y. et al. Empirical prediction of electronic potentials of single-walled carbon nanotubes with a specific chirality (n,m). Sci. Rep. 3, 2959 (2013).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Mleczko, M. J. et al. Contact engineering high-performance n-type MoTe2 transistors. Nano Lett. 19, 6352–6362 (2019).

Kim, S. Y., Park, S. & Choi, W. Variability of electrical contact properties in multilayer MoS2 thin-film transistors. Appl. Phys. A 117, 761–766 (2014).

Popov, I., Seifert, G. & Tománek, D. Designing electrical contacts to MoS2 monolayers: A computational study. Phys. Rev. Lett. 108, 156802 (2012).

Qiu, H. et al. Electrical characterization of back-gated bi-layer MoS2 field-effect transistors and the effect of ambient on their performances. Appl. Phys. Lett. 100, 123104 (2012).

Matsuda, Y., Deng, W.-Q. & Goddard, W. A. Contact resistance properties between nanotubes and various metals from quantum mechanics. J. Phys. Chem. C. 111, 11113–11116 (2007).

Hsu, A. L. et al. Surface-induced hybridization between graphene and titanium. ACS Nano 8, 7704–7713 (2014).

Felten, A. et al. The role of oxygen at the interface between titanium and carbon nanotubes. ChemPhysChem 10, 1799–1804 (2009).

Estrada, D., Dutta, S., Liao, A. & Pop, E. Reduction of hysteresis for carbon nanotube mobility measurements using pulsed characterization. Nanotechnology 21, 085702 (2010).

Kim, W. et al. Hysteresis caused by water molecules in carbon nanotube field-effect transistors. Nano Lett. 3, 193–198 (2003).

Luo, J. et al. A novel ambipolar ferroelectric tunnel FinFET based content addressable memory with ultra-low hardware cost and high energy efficiency for machine learning. 2022 IEEE Symp. VLSI Technol. Circuits; 2022. p. 226-227.

Zhang, Z. et al. An ultra-dense one-transistor ternary-content-addressable memory array based on non-volatile and ambipolar Fin field-effect transistors. IEEE Trans. Electron Devices 70, 1029–1033 (2023).

Naber, R. C. G., Blom, P. W. M., Gelinck, G. H., Marsman, A. W. & de Leeuw, D. M. An organic field-effect transistor with programmable polarity. Adv. Mater. 17, 2692–2695 (2005).

Zheng, Y. et al. Gate-controlled nonvolatile graphene-ferroelectric memory. Appl. Phys. Lett. 94, 163505 (2009).

Hassanpour Amiri, M., Heidler, J., Müllen, K. & Asadi, K. Design rules for memories based on graphene ferroelectric field-effect transistors. ACS Appl. Electron. Mater. 2, 2–8 (2020).

Li, D. et al. The ambipolar evolution of a high-performance WSe2 transistor assisted by a ferroelectric polymer. Nanotechnology 29, 105202 (2018).

Baeumer, C., Rogers, S. P., Xu, R., Martin, L. W. & Shim, M. Tunable carrier type and density in graphene/PbZr0.2Ti0.8O3 hybrid structures through ferroelectric switching. Nano Lett. 13, 1693–1698 (2013).

Lipatov, A. et al. Polarization-dependent electronic transport in graphene/Pb(Zr,Ti)O3 ferroelectric field-effect transistors. Adv. Electron. Mater. 3, 1700020 (2017).

Rajapitamahuni, A., Hoffman, J., Ahn, C. H. & Hong, X. Examining graphene field-effect sensors for ferroelectric thin film studies. Nano Lett. 13, 4374–4379 (2013).

Yusuf, M. H., Nielsen, B., Dawber, M. & Du, X. Extrinsic and intrinsic charge trapping at the graphene/ferroelectric interface. Nano Lett. 14, 5437–5444 (2014).

Wan, S. et al. Nonvolatile ferroelectric memory effect in ultrathin α-In2Se3. Adv. Funct. Mater. 29, 1808606 (2019).

Ghani, M. A. et al. Ferroelectric field effect transistors based on two-dimensional CuInP2S6 (CIPS) and graphene heterostructures. MRS Energy Sustain. 11, 616–623 (2024).

Ram, A. et al. Reconfigurable multifunctional van der Waals ferroelectric devices and logic circuits. ACS Nano 17, 21865–21877 (2023).

Seyedzadeh Sany, B. & Ebrahimi, B. FinFET based ultra-low power 3T GC-eDRAM with very high retention time in sub-22 nm. Analog Integr. Circuits Signal Process. 113, 27–39 (2022).

Lee, D. et al. Adaptive-latency DRAM: Optimizing DRAM timing for the common-case. 2015 IEEE 21st International Symposium on High Performance Computer Architecture (HPCA); 2015. p. 489-501.

Yang, S. et al. Retention accelerated testing for 3D QLC NAND flash memory: Characterization, analysis, and modeling. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., 1–1 (2025).

Ma, R. et al. RBER-aware lifetime prediction scheme for 3D-TLC NAND flash memory. IEEE Access 7, 44696–44708 (2019).

Stolichnov, I., Tagantsev, A. K., Colla, E., Setter, N. & Cross, J. S. Physical model of retention and temperature-dependent polarization reversal in ferroelectric films. J. Appl. Phys. 98, 084106 (2005).

Li, Q.-H. & Sakai, S. Characterization of Pt∕SrBi2Ta2O9∕Hf–Al–O∕Si field-effect transistors at elevated temperatures. Appl. Phys. Lett. 89, 222910 (2006).

Ma, T. P. & Jin-Ping, H. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron Device Lett. 23, 386–388 (2002).

Pan, X. & Ma, T. P. Retention mechanism study of the ferroelectric field effect transistor. Appl. Phys. Lett. 99, 013505 (2011).

Lee, S. W., Suh, D., Lee, S. Y. & Lee, Y. H. Passivation effect on gate-bias stress instability of carbon nanotube thin film transistors. Appl. Phys. Lett. 104, 163506 (2014).

Libsch, F. R. & Kanicki, J. Bias-stress-induced stretched-exponential time dependence of charge injection and trapping in amorphous thin-film transistors. Appl. Phys. Lett. 62, 1286–1288 (1993).

Cao, Q. et al. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 454, 495–500 (2008).

Ha, M. et al. Printed, sub-3V digital circuits on plastic from aqueous carbon nanotube inks. ACS Nano 4, 4388–4395 (2010).

Jeloka, S., Akesh, N. B., Sylvester, D. & Blaauw, D. A 28 nm configurable memory (TCAM/BCAM/SRAM) using push-rule 6T bit cell enabling logic-in-memory. IEEE J. Solid-State Circuits 51, 1009–1021 (2016).

Pan, K., Tosson, A. M. S., Wang, N., Zhou, N. Y. & Wei, L. A novel cascadable TCAM using RRAM and current race scheme for high-speed energy-efficient applications. IEEE Trans. Nanotechnol. 22, 214–221 (2023).

Li, J., Montoye, R. K., Ishii, M. & Chang, L. 1 Mb 0.41 µm² 2T-2R cell nonvolatile TCAM with two-bit encoding and clocked self-referenced sensing. IEEE J. Solid-State Circuits 49, 896–907 (2014).

Dutta, S. et al. Lifelong learning with monolithic 3D ferroelectric ternary content-addressable memory. 2021 IEEE International Electron Devices Meeting (IEDM); 2021. p. 1-4.

Yin, X. et al. An ultra-dense 2FeFET TCAM design based on a multi-domain FeFET model. IEEE Trans. Circuits Syst. II Express Briefs 66, 1577–1581 (2019).

Xiao, W. et al. Memory window and endurance improvement of Hf0.5Zr0.5O2-based FeFETs with ZrO2 seed layers characterized by fast voltage pulse measurements. Nanoscale Res. Lett. 14, 254 (2019).

Ali, T. et al. Silicon doped hafnium oxide (HSO) and hafnium zirconium oxide (HZO) based FeFET: A material relation to device physics. Appl. Phys. Lett. 112, 222903 (2018).

Kim, B. H. et al. Low operating voltage and immediate read-after-write of HZO-based Si ferroelectric field-effect transistors with high endurance and retention characteristics. Adv. Electron. Mater. 10, 2300327 (2024).

Cha, S., Cha, M., Lee, S., Kang, J. H. & Kim, C. Low-temperature, dry transfer-printing of a patterned graphene monolayer. Sci. Rep. 5, 17877 (2015).

Rhee, D. et al. Soft skin layers enable area-specific, multiscale graphene wrinkles with switchable orientations. ACS Nano 14, 166–174 (2020).

Acknowledgements

This work was primarily supported by the Air Force Office of Scientific Research GHz-THz program (FA9550-23-1-0391). D.R. acknowledges primary support from the Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (P0017305, Human Resource Development Program for Industrial Innovation (Global)) and the BrainLink program funded by the Ministry of Science and ICT through the National Research Foundation of Korea (RS-2023-00237308). S.S. acknowledges support from the Institute for Basic Science (IBS-R036-D1). This work was carried out in part at the Singh Center for Nanotechnology at the University of Pennsylvania, which is supported by the National Science Foundation National Nanotechnology Coordinated Infrastructure Program under grant NNCI-2025608.

Author information

Authors and Affiliations

Contributions

D.J. supervised all aspects of the project and collaboration. D.R., K.-H.K., D.J., and R.H.O. conceived the idea of integrating large-area SWCNTs with AlScN for the scalable fabrication of unipolar and ambipolar FeFET arrays, as well as for the realization of reconfigurable device applications. D.R. and K.-H.K. designed the experiments and performed device fabrication. D.R. conducted materials characterization of SWCNT channels, including AFM and polarized Raman spectroscopy. K.-H.K. performed circuit simulations for the application of reconfigurable SWCNT FeFETs in TCAM. D.R., K.-H.K., and S.S. conducted current-voltage measurements and retention tests. R.H.O. supervised the growth process of AlScN films, and J.Z. performed AlScN deposition and characterization. L.-M.P. provided films of aligned semiconducting SWCNTs. D.R., K.-H.K., and D.J. analyzed the data, prepared figures, and wrote the manuscript. J.K. supervised materials integration and device characterization. All the authors contributed to the discussion/analysis of the results and manuscript writing.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Cheolmin Park and the other anonymous reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Rhee, D., Kim, KH., Zheng, J. et al. Reconfigurable single-walled carbon nanotube ferroelectric field-effect transistors. Nat Commun 16, 7655 (2025). https://doi.org/10.1038/s41467-025-62827-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-025-62827-2