Abstract

III-V semiconductors have been intensively studied with the goal of realizing metal-oxide-semiconductor field-effect transistors (MOSFETs) with high mobility, a high on-off ratio, and low power consumption as next-generation transistors designed to replace current Si technology. Of these semiconductors, a narrow band-gap semiconductor InAs has strong Rashba spin-orbit interaction, thus making it advantageous in terms of both high field-effect transistor (FET) performance and efficient spin control. Here we report a high-performance InAs nanowire MOSFET with a gate-all-around (GAA) structure, where we simultaneously control the spin precession using the Rashba interaction. Our FET has a high on-off ratio (104~106) and a high field-effect mobility (1200 cm2/Vs) and both values are comparable to those of previously reported nanowire FETs. Simultaneously, GAA geometry combined with high- κ dielectric enables the creation of a large and uniform coaxial electric field (>107 V/m), thereby achieving highly controllable Rashba coupling (1 × 10−11 eVm within a gate-voltage swing of 1 V), i.e. an operation voltage one order of magnitude smaller than those of back-gated nanowire MOSFETs. Our demonstration of high FET performance and spin controllability offers a new way of realizing low-power consumption nanoscale spin MOSFETs.

Similar content being viewed by others

Introduction

The high electron mobility of III-V semiconductors makes them good candidates for the development of field-effect transistors that can be operated with high speed, a high on-off ratio, and a low power consumption. Of these semiconductors, those showing band structures with large spin-orbit splitting have been independently attracting great interest in relation to spin FET applications1. The large band splitting is mostly associated with the Rashba spin-orbit interaction (SOI) generated with an electric field induced by structural inversion asymmetry. The Rashba SOI is given by the Hamiltonian, H = eα0 ∙ (σ × k), where e is an elementary charge, α0 is a Rashba coefficient determined from the band structure of a bulk material, σ is the Pauli matrix, k is the electron wave vector and E is the electric field vector2,3,4. The Rashba coupling parameter given by α ≡ α0 eE is an important index as a measure of modulating electron spin, and increasing and controlling α with the gate voltage has been a focus of attention.

To obtain better electric-field control of the Rashba SOI, III-V semiconductors such as GaAs/AlGaAs, GaInAs/InP, InAs, InSb and InGaAs have been investigated for various structures including two-dimensional electron gas (2DEG) in heterostructures5,6,7, quantum wells (QW)8,9,10 and quantum wires11 using a top-down microfabrication process. These studies reported that Rashba parameters range from α = 0.3 × 10−11 to 1 × 10−11 eVm (refs 6,7,8,9,10,11) and have a gate voltage V g tunability of ~1.4 × 10−12 eVm/V (refs 5,6,7,8,9). On the other hand, InAs nanowires with surface electron confinement potential in a sub-micron width have been examined mostly in the form of conventional bottom- or top-gated devices12,13,14,15,16. They have shown a larger α (1 × 10−11–3 × 10−11 eVm) but the V g tunability was as small as that of former reports using a top-down approach7,8,9,10,11 within a gate voltage range of 0–20 V. Recently, Liang et al.17 reported ion-gated InAs nanowire device, exhibiting V g tunable efficiency more than ten times higher than previously reported13, 14, 16, 18. This marked progress in efficiency brought about low-gate voltage operation leading to low-power consumption. However, since ion-gated device requires very long response time, a prototype device employing standard MOS design that excels in operation speed is critically needed.

Here, we report high gate-tunability of the Rashba SOI in an InAs nanowire MOSFET employing gate-all-around (GAA) geometry19, in which gate-induced electric field is more enhanced and more uniform than those in conventional bottom- or top-gated nanowire devices13,14,15,16, multigated nanowires18, and Ω-shape (partially coaxial) gated devices20,21,22. The Rashba parameter that we obtained by weak antilocalization measurements is 0.6 × 10−11–2 × 10−11 eVm, and the gate voltage tunability is 1.2 × 10−11–2.4 × 10−11 eVm/V, the latter being ten times larger than that obtained for various types of III-V semiconductors including InAs nanowire MOSFETs6,7,8,9,10,11,12,13,14,15,16. This is also comparable to the best V g tunability achieved for an ion-gated InAs nanowire FET17. In addition to the excellent V g tunability of the Rashba SOI, our device exhibits excellent FET characteristics including a high on-off ratio (104~106) and a high field-effect mobility (1200 cm2/Vs). As MOSFETs have faster responses than ion-gated devices, which normally require considerable time for electric double layer stabilization23, our demonstration of both the excellent FET performance and high tunability of the Rashba SOI in a small V g range could lead to the development of a practical spin nanowire MOSFET with low power consumption that is compatible with the currently used Si transistor platform.

Results

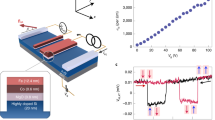

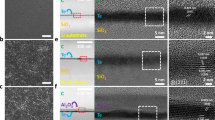

Figure 1(a) is a schematic illustration of our GAA InAs nanowire FET, which we fabricated using a similar method to the one we used for our previous nanowire FETs24, 25. GAA geometry, which is also called surrounding gate26 or wrap-gate27 geometry, has been used not only to induce a uniform electric field but also to suppress the short-channel effect of transistors28 with an improvement in nanowire FET performance29, 30. To obtain a high carrier density and thus induce a strong electric field, we used the high-κ gate dielectrics of Al2O3/HfO2 (2 nm/4 nm) grown by atomic layer deposition (ALD). The InAs nanowire coated with the above dielectrics was deposited on a pre-patterned substrate and then gate metal was evaporated onto the nanowire. This two-stage deposition of gate metal allows us to fabricate a GAA structure. As shown in Fig. 1(b), our sample is covered by the gate electrode over 90% of the channel length, which allows us to ignore the contributions of the ungated regions (for details see Method). Figure 1(c) shows a TEM image of a cross-section of a typical nanowire FET. We find that layered gate dielectrics and GAA geometry are formed according to our MOSFET design. These structures are also examined with energy dispersive X-ray spectrometry (EDS). The false colour images in Fig. 1(d–i) rule out any significant migration or diffusion of the deposited elements or contamination during the device processing along the entire channel.

(a) Schematic illustration of our InAs nanowire GAA MOSFET together with circuit set up. (b) Top view of device used in this paper and (c) cross-sectional view of our typical device. (d–i) EDS images of device shown in (c). (d–i) correspond to the elemental mapping for (d) indium, (e) arsenic, (f) aluminium, (g) hafnium, (h) titanium, and (i) gold.

We first describe FET operation at various temperatures. Figure 2(a) shows the transfer characteristics of the device measured at room temperature for different source drain voltages V sd of 100 to 500 mV. As shown in the inset, the subthreshold slope (SS) and on-off ratio are 350 mV/dec and over 104 at room temperature (RT). Here SS is defined as dV g/dlogI sd with the source-drain current I sd. While the SS values for our typical devices fabricated in the same manner usually exceed 200 mV/dec at RT, which is larger than the ideal RT limit of 60 mV/dec, the on-off ratio exhibits good performance and is generally higher than ~104. When we decrease the measurement temperature to 1.5 K, the SS and on-off ratio are greatly improved to 25 mV/dec and 106, respectively, as shown in Fig. 2(c). The high on-off ratio at RT and 1.5 K are comparable to the excellent previously reported values for GAA InAs nanowires24, 25, 31,32,33 and GAA InGaAs nanowires34. Moreover, steep increase in I sd within V g~1 V indicates that our GAA device is operated at lower voltage than conventional back-gated nanowire FETs with cylinder-on-plane (COP) geometry13,14,15,16. Figure 2(b,d) show the output characteristics for various V g values measured at RT and 1.5 K, showing that a good saturation is obtained within a V sd of 0.5 V.

To investigate how robust our FET is under ambient conditions, we compare the same device in different measurement runs. Figure 3(a) compares the device transfer characteristics measured before the first cooling with those measured after 6 months, during which time the sample was stored in ambient air when not in use. Although reduction in I sd is accompanied by a reduction in the on-off ratio from 2 × 104 to 1 × 104, we observe no notable change in SS values between the two cases. Moreover, our GAA device shows robust and clear transfer characteristics for various temperatures down to 1.5 K [Fig. 3(b)] after 6 months interval. We note that the data shown in Fig. 2(a–d) were measured after several cooling cycles, indicating that our FET performs well even after being affected by thermal cycles and the ambient conditions.

(a) Transfer characteristics of the device measured for the first cooling and after several coolings performed over 6 months. The device was stored in ambient conditions for 6 months when not in use. (b) Transfer characteristics of the device measured for various temperatures at V sd = 50 mV. (c) Field-effect mobility and (d) SS values of the device plotted as a function of temperature for the first cooling and for the cooling after 6 months interval.

We next compare the field-effect mobility μ for the two cases and examine the temperature dependence. μ is given by \(\frac{{{L}_{g}}^{2}}{C}\frac{d}{d{V}_{g}}(\frac{{I}_{sd}}{{V}_{sd}})\), where L g is a gate length of 3.3 μm, C is a gate capacitance of 2.29 × 10−14 F, and V sd is the source-drain bias. The sample exposed to the first thermal cycle shows mobilities of 1000 cm2/Vs at RT and 1200 cm2/Vs at 1.5 K, as shown in Fig. 3(c). Our device shows less T dependence than other InAs nanowire GAA devices32, 33. Indeed, many of our GAA devices possess mobilities of 1000–1500 cm2/Vs at room temperature. The value is one order of magnitude higher than that of a previously reported InAs GAA device using the gate dielectrics of HfO2 (~109 cm2/Vs)31, and comparable to single-crystalline and pure-phase InAs nanowire with GAA geometry33 (1500 cm2/Vs) and high-mobility InGaAs nanowire FETs (1030 cm2/Vs)34. However, after several thermal cycles and long-time storage under ambient conditions, the mobility decreased to around 400 cm2/Vs, which is nevertheless higher than the mobility of a high-κ gated MoS2 2D transistor35 or a Si nanowire FET36. The decreased mobility may be attributed to increase in access resistance resulting from the nanowire segment that is not coated by the gate metal, possibly due to impurities adhered to that segment by repeated thermal cycles or during sample storage. Therefore, the decrease is merely in the extrinsic mobility, not the intrinsic one. This is also supported by the fact that SS after 6 months, which shows linear temperature dependence that is characteristic to standard FETs [Fig. 3(d)], has no notable difference from SS for the first cooling from room temperature to 1.5 K, indicating that surface states of the nanowire under the gate electrode are expected to be unaffected. In this paper, we use data obtained for the sample when it had a field effect mobility of ~400 cm2/Vs unless otherwise stated. However, we emphasize that gate efficiency on the nanowire channel was not degraded during 6 months, as is seen from virtually unchanged SS values. This is also consistent with the results obtained by magnetotransport measurements as we discuss later, in which we confirm that the gate controllability of the Rashba parameter was not degraded after 6 months.

Having examined the FET performance of our device, we then investigated the effects of a spin-orbit interaction by conducting magnetotransport measurements at 1.5 K. Figure 4(a) shows the correction of magnetoconductance (ΔG ≡ ΔG(B) − ΔG(0)) as a function of a magnetic field (B), where the magnetoconductance was deduced from the two-terminal dc-transport at V sd = 10 mV. The data have been smoothed over V g ± 15 mV and B ± 15 mT to exclude universal conductance fluctuations or other random fluctuations caused by impurities, as in refs 14, 16. In addition, our data are further averaged with respect to the reversed magnetic field sweep direction to fit the data with better accuracy as described below. As V g increases, B dependence of ΔG changes from a dip to a peak, indicating a crossover from weak localization to weak antilocalization37, 38, which occurs for conducting channels in a variety of materials and devices9, 39, 40 in the presence of a strong spin-orbit interaction.

(a) Correction of conductance ΔG ≡ ΔG(B) − ΔG(0) as a function of magnetic field B for various gate voltages. The solid lines are fits using one-dimensional weak antilocalization model. The inset shows more data set near weak localization/weak antilocalization crossover. (b) V g dependence of spin-orbit relaxation length l so and phase coherence length l ϕ extracted from ΔG shown in (a) (bottom) and corresponding relaxation time τso and τϕ vs. V g (top).

Such a crossover from weak localization to weak antilocalization has also been observed for various types of InAs FETs12,13,14,15,16,17, where spin-orbit interaction is considered to be the Rashba SOI originating from a strong electric field. These devices have a mean free path shorter than the nanowire diameter, indicating that an electrical channel in a nanowire can be reasonably analysed in the framework of the disordered one-dimensional weak antilocalization model reported in ref. 38,

where h is Planck constant, L g is the gate length, l ϕ is the phase coherence length, l so is the spin-orbit relaxation length, D is the diffusion constant, and τB is the magnetic relaxation time. Here τB is given by

with l B being the magnetic length given by \({l}_{B}=\sqrt{h/(2\pi eB)}\). Note that using this relation reduces fitting parameters to only l so and l ϕ.

Our device has a typical mean free path of 12 nm, which is smaller than the nanowire diameter of 100 nm. Therefore, the use of Eq. (1) is justified, as plotted by the solid lines in Fig. 4(a), which fit well with our data. l so and l ϕ are shown in Fig. 4(b), together with τso and τϕ, which are deduced from τso(τϕ) = l so(l ϕ)2/D with diffusion constant D given by D = vF 2 τ/3. Here v F is the Fermi velocity and τ is the momentum scattering time given by τ = μm */e (m *: effective electron mass) with m * = 0.023 m e (m e: electron mass). We also note that l ϕ > W, which is required for a one-dimensional weak antilocalization condition, is satisfied as shown in Fig. 4(b). As V g increases, l so decreases and l ϕ increases, reaching a crossover at V g ~ 0.5 V. This corresponds to the gate voltage at which a crossover from weak localization to weak antilocalization occurs. The decreasing l so accompanied by a rapid decrease in τso demonstrates that the spin-orbit relaxation length is tuned significantly by the electric field induced by the gate voltage.

Discussion

We in turn compare the V g tunability of l so obtained for our device with those already reported for other InAs nanowire FETs13,14,15,16,17,18. As is clearly seen in Fig. 5(a), where l so is plotted against V g, our GAA MOS-type device shows superior V g tunability; l so is modulated several times in a V g range an order of magnitude smaller than that used to operate back or top-gated (cylinder-on-plane) InAs nanowires13,14,15,16, 18, indicating that our GAA MOSFET can offer much lower power consumption than conventional nanowire MOSFETs. The tunability for our device also reaches a high level comparable to the previously reported best controllability obtained for an InAs nanowire device operated with electrolyte gating17. It is noteworthy that such high V g tunability is achieved for a MOSFET, which has an advantage of easier and faster operation than ion-gated devices particularly in temperature-variable measurements. This is because ion-gated devices typically require the temperature to be increased to change the carrier density for ion polarization41, which itself requires a long time to stabilize23. These types of devices sometimes take more than ten hours for temperature variation to minimize sample electrochemical degrading42.

(a) Comparison of V g dependence of l so in our device and those in previously reported InAs nanowire devices. They are categorized as having GAA geometry and back- and/or top-gate (cylinder-on-plane) geometry. (b) Rashba parameter αR and associated electric field E R plotted as a function of V g for our GAA InAs nanowire MOSFET, an InAs nanowire device using electrolyte17, an InAs nanowire device using a back-gate with cylinder-on-plane (COP) geometry13, InGaAs QW8, and InAs 2DEG used to develop a spin FET7. Data shown with red and blue symbols were obtained from measurement runs for the first cooling and for the cooling after 6 months interval in Fig. 3. (c) E R as a function of E L for our device and that in ref. 17. (d) E R to E L ratio as a function of V g for our device and that in ref. 17.

Using experimentally extracted l so, we calculated the Rashba coupling parameter αR and corresponding electric field E R. Here αR is given by \({\alpha }_{R}=\frac{{\hslash }^{2}}{2{m}^{\ast }{l}_{so}}={\alpha }_{0}e{E}_{R}\), where ħ is the reduced Planck constant and α0 is the Rashba coefficient of bulk InAs α0 = 1.17 nm2 (ref. 43). Figure 5(b) shows αR and E R as a function of V g. The red and blue circles indicate data obtained for the first cooling [with a mobility of 1200 cm2/Vs, as shown in Fig. 3(a,c and d)] and for the cooling carried out with an interval of 6 months [with a mobility of 400 cm2/Vs, as shown in Fig. 3(a–d)]. Despite the long time interval and difference in mobility, the αR and E R values obtained from two measurements are in good agreement. When V g is increased above the threshold voltage V th, αR and E R increase linearly as expected. A rapid increase in αR up to V g ~ 1.5 V provides Rashba parameter tunability reaching 1.2 × 10−11 eVm/V.

Figure 5(b) also summarizes the V g tunability of the Rashba SOI extracted from various devices, where our device is compared with an ion-gated InAs nanowire device17, a back-gated cylinder-on-plane InAs nanowire13, and other two-dimensional FETs fabricated from strong SOI material7, 8. Here αR is estimated by analysing the crossover from weak localization to weak anti-localization for the nanowire devices, and is extracted from beating patterns in magnetotransport for the two-dimensional FETs. While the V g tunabilities of αR and E R for our sample are about a quarter of their counterparts for the ion-gated device17, they greatly exceed the values obtained for a conventional back-gated cylinder-on-plane InAs nanowire MOSFET13 as well as those obtained for two-dimensional FETs fabricated from III-V material7, 8.

We further investigate the ratio of the calculated electric field E L expected from GAA geometry and the E R value that is directly associated with the Rashba SOI. In the cylinder capacitance model, the charge line density Q L and associated electric field E L are given by,

where C is the cylindrical gate capacitance (see Method), V fb is the gate voltage that gives flat band condition, W is the nanowire diameter, and ε0 and εInAs are the vacuum and relative permittivities. The slope of the V g dependence of E L is extracted for our device from these equations. We use C = 2.29 × 10−14 F, L g = 3.3 μm, W = 100 nm for our sample. As for V fb. we use gate voltage given by the intercept of E R = 0 for the Rashba measurements. The dash-dotted line in Fig. 5(b) tracing our data has a slope that is twenty times smaller than that for calculated E L. We then consider the ion-gated device described in ref. 17, where the authors adapted the same cylinder capacitance model to their device. We calculate E L using the corresponding values shown in Supplementary Information in ref. 17 (C = 1.44 × 10−14 F, L g = 2 μm, W = 25 nm). Their data are also traced by the dashed line with a slope twenty times smaller than E L calculated for their device.

The inconsistency between E L and E R is pointed out in ref. 17, and they attributed it to electric field decay due to screening by the gate-induced charge in the nanowire channel44, also noting that this decay would appear similarly in GAA MOS-type nanowires. We consider that the inconsistency we found with our device is partly associated with this charge screening, which is mainly due to surface-state pinning15. We also mention that the field gradient on V g can be reduced by trap states or interface states possibly incorporated in a gate insulator, which would act as a reservoir for gate-induced carriers45, 46, even though our device is expected to have less interface state density due to the insertion of an Al2O3 layer before HfO2 growth47. When we assume the presence of interface states located between the InAs surface and the Al2O3 gate insulator, the interface state density required to explain the dash-dotted line would be very large, reaching ~3 × 1014 eV−1cm−2 based on a model similar to that described in ref. 45. This unreasonably large value of the interface-state density itself suggests that our device is significantly affected by the charge screening effect.

To highlight the efficiency of our device, we compare E L, E R and E R/E L between the two devices. As expected from the device geometry, E L for V g–V fb of 1 V is calculated to be 4.0 × 108 V/m for an ion-gated device (with their assumption of a Debye length of 1 nm (ref. 22), which corresponds to the gate insulator thickness in GAA geometry) and 1.0 × 108 V/m for our device. It should be noted that, while we compare devices with different nanowire diameters, E L is determined solely by the gate insulator material and gate geometry, and is thus inherently nearly independent of nanowire width. Although E L for our device is about one quarter of its electrolyte counterpart, it is significant that a MOSFET has such a high E L value owing to its thin high-κ gate dielectrics.

When E R is plotted as a function of E L, instead of V g, as shown in Fig. 5(c), data from our MOS device and those from the ion-gated device fall on almost the same line. This consistency between totally different devices highlights the fact that our GAA device is fabricated as well as an ion-gated device as regards the gate-control efficiency that affects the Rashba SOI. Although the E R to E L ratio decreases to about 5% for both devices, our MOS device does not require any thermal cycle for gate voltage change unlike ion-gated device, and therefore enables in-situ continuous tuning of αR. Furthermore, the E R to E L ratio in our device is nearly independent of V g [see Fig. 5(d)], thus ensuring more stable SOI operation by sweeping gate voltage.

The above results demonstrate that our GAA geometry with high-κ gate dielectrics has the Rashba SOI tuning efficiency close to the best value ever achieved, at the same time as enabling the continuous in-situ tuning due to the faster response of MOS design. We believe that these advantages will make our device a prototype nanoscale MOSFET for use in realizing practical spin control application.

Method

InAs nanowires are grown by vapour-liquid-solid method using gold nanoparticles as catalysts48. For the gate dielectrics, we combined two high-κ gate dielectrics of Al2O3 (2 nm) and HfO2 (4 nm) grown by ALD. The growth of Al2O3 before HfO2 can improve the interface between InAs and gate dielectrics, which may reduce the interface state density in ALD-grown gate dielectrics47. As shown in Fig. 1(b), more than 90% of the channel length of our device is coated with a gate electrode. When we considered the contributions of ungated regions and deduced the corrected mobility as in refs 33 and 34, we found that the corrected mobility differs less than 5%, which allows us to disregard the contributions of the ungated regions. The sample was measured with a standard DC transport method or ac lock-in techniques at room temperature down to 1.5 K using a cryostat.

To obtain the gate capacitance, we used a standard cylindrical model. When a gate insulator with a thickness of h coats a nanowire with a radius r and length L g, the gate capacitance C is given by \(C=\frac{2\pi {\varepsilon }_{0}{\varepsilon }_{h}{L}_{g}}{\mathrm{ln}(1+\frac{h}{r})}\), where εh is relative permittivity of the gate insulator. Since our device employed a double layer of high-κ gate dielectrics, Al2O3 and HfO2, we use the total gate capacitance C tot given by \(\frac{1}{{C}_{tot}}=\frac{1}{{C}_{1}}+\frac{1}{{C}_{2}}\), where \({C}_{1}=\frac{2\pi {\varepsilon }_{0}{\varepsilon }_{h1}{L}_{g}}{\mathrm{ln}(1+\frac{{h}_{1}}{r})}\) and \({C}_{2}=\frac{2\pi {\varepsilon }_{0}{\varepsilon }_{h2}{L}_{g}}{\mathrm{ln}(1+\frac{{h}_{2}}{(r+{h}_{1})})}\) with h 1 being the thickness of Al2O3 (2 nm) and h 2 being the thickness of HfO2 (4 nm). The values used for our calculation are C tot = 2.29 × 10−14 F, L g = 3.3 μm, r = 50 nm (W = 100 nm), and εInAs = 12.5.

Reference

Datta, S. & Das, B. Electronic analog of the electro-optic modulator. Appl. Phys. Lett. 56, 665–667, doi:10.1063/1.102730 (1990).

Rashba, E. Properties of semiconductors with an extremum loop. 1. Cyclotron and combinational resonance in a magnetic field perpendicular to the plane of the loop. Sov. Phys. Solid State 2, 1109–1122 (1960).

Bychkov, Y. A. & Rasbha, E. I. Properties of a 2D electron gas with liſted spectral degeneracy. P. Zh. Eksp. Teor. Fiz. 39, 66–69 (1984).

Manchon, A., Koo, H. C., Nitta, J., Frolov, S. M. & Duine, R. A. New perspectives for Rashba spin-orbit coupling. Nat. Mater. 14, 871–882 (2015).

Miller, J. B. et al. Gate-controlled spin-orbit quantum interference effects in lateral transport. Phys. Rev. Lett. 90, 076807 (2003).

Guzenko, V. A., Schäpers, Th. & Hardtdegen, H. Weak antilocalization in high mobility GaxIn1−xAs/InP two-dimensional electron gases with strong spin-orbit coupling. Phys. Rev. B 76, 165301 (2007).

Koo, H. C. et al. Control of spin precession in a spin-injected field effect transistor. Science 325, 1515–1518 (2009).

Nitta, J., Akazaki, T., Takayanagi, H. & Enoki, T. Gate control of spin-orbit interaction in an inverted In0.53Ga0.47As/In0.52Al0.48As heterostructure. Phys. Rev. Lett. 78, 1335–1338 (1997).

Koga, T., Nitta, J., Akazaki, T. & Takayanagi, H. Rashba spin-orbit coupling probed by the weak antilocalization analysis in InAlAs/InGaAs/InAlAs quantum wells as a function of quantum well asymmetry. Phys. Rev. Lett. 89, 046801 (2002).

Kallaher, R. L., Heremans, J. J., Goel, N., Chung, S. J. & Santos, M. B. Spin-orbit interaction determined by antilocalization in an InSb quantum well. Phys. Rev. B 81, 075303 (2010).

Schäpers, Th., Knobbe, J. & Guzenko, V. A. Effect of Rashba spin-orbit coupling on magnetotransport in InGaAs/InP quantum wire structures. Phys. Rev. B 69, 235323 (2004).

Schierholz, C., Matsuyama, T., Merkt, U. & Meier, G. Weak localization and spin splitting in inversion layers on p-type InAs. Phys. Rev. B 70, 233311 (2004).

Hansen, A. E., Björk, M. T., Fasth, C., Thelander, C. & Samuelson, L. Spin relaxation in InAs nanowires studied by tunable weak antilocalization. Phys. Rev. B 71, 205328 (2005).

Dhara, S. et al. Magnetotransport properties of individual InAs nanowires. Phys. Rev. B 79, 121311 (2009).

Estévez Hernández, S. et al. Spin-orbit coupling and phase coherence in InAs nanowires. Phys. Rev. B 82, 235303 (2010).

Roulleau, P. et al. Suppression of weak antilocalization in InAs nanowires. Phys. Rev. B 81, 155449 (2010).

Liang, D. & Gao, X. P. A. Strong tuning of Rashba spin-orbit interaction in single InAs nanowires. Nano Lett. 12, 3263 (2012).

Scherübl, Z. et al. Electrical tuning of Rashba spin-orbit interaction in multigated InAs nanowires. Phys. Rev. B 94, 035444 (2016).

del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. Nature 479, 317–323 (2011).

Dahl Nissen, P. et al. Comparison of gate geometries for tunable, local barriers in InAs nanowires. J. Appl. Phys. 112, 084323 (2012).

Keem, K. et al. Fabrication and device characterization of omega-shaped-gate ZnO nanowire field-effect transistors. Nano Lett. 6, 1454–1458 (2006).

van Weperen, I. et al. Spin-orbit interaction in InSb nanowires. Phys. Rev. B 91, 201413(R) (2015).

Allain, A. & Kis, A. Electron and hole mobilities in single-layer WSe2. ACS Nano 8, 7180–7185 (2014).

Sasaki, S. et al. Encapsulated gate-all-around InAs nanowire field-effect transistors. Appl. Phys. Lett. 103, 213502 (2013).

Sasaki, S. et al. Self-aligned gate-all-around InAs/InP core-shell nanowire field-effect transistors. J. J. of Appl. Phys 54, 04DN04 (2015).

Ng, H. T. et al. Single crystal nanowire vertical surround-gate field-effect transistor. Nano Lett. 4, 1247–1252 (2004).

Thelander, C. et al. Development of a vertical wrap-gated InAs FET. IEEE Trans. Electron Devices 55, 3030–3036 (2008).

Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316 (2011).

Dey, A. W. et al. High-performance InAs nanowire MOSFETs. IEEE Electron Device Lett. 33, 791–793 (2012).

Tomioka, K., Yoshimura, M. & Fukui, T. A III–V nanowire channel on silicon for high-performance vertical transistors. Nature 488, 189–192 (2012).

Storm, K., Nylund, G., Samuelson, L. & Micolich, A. P. Realizing lateral wrap-gated nanowire FETs: Controlling gate length with chemistry rather than lithography. Nano Lett. 12, 1–6 (2012).

Dhara, S. et al. Facile fabrication of lateral nanowire wrap-gate devices with improved performance. Appl. Phys. Lett. 99, 173101 (2011).

Li, Q. et al. Suspended InAs nanowire gate-all-around field-effect transistors. Appl. Phys. Lett. 105, 113106 (2014).

Shen, L.-F. et al. High-performance wrap-gated InGaAs nanowire field-effect transistors with sputtered dielectrics. Sci. Rep. 5, 16871 (2015).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Gunawan, O. et al. Measurement of carrier mobility in silicon nanowires. Nano Lett. 8, 1566–1571 (2008).

Hikami, S., Larkin, A. I. & Nagaoka, Y. Spin-Orbit Interaction and Magnetoresistance in the Two Dimensional Random System. Prog. Theor. Phys. 63, 707 (1980).

Kurdak, Ç., Chang, A. M., Chin, A. & Chang, T. Y. Quantum interference effects and spin-orbit interaction in quasi-one-dimensional wires and rings. Phys. Rev. B 46, 6846 (1992).

Wang, Z. et al. Strong interface-induced spin-orbit interaction in graphene on WS2. Nat. Commun. 6, 8339 (2015).

Bao, L. et al. Weak Anti-localization and Quantum Oscillations of Surface States in Topological Insulator Bi2Se2Te. Sci. Rep. 2, 726 (2012).

Gallagher, P. et al. A high-mobility electronic system at an electrolyte-gated oxide surface. Nat Commun 6, 6437 (2015).

Gallagher, P., Lee, M., Williams, J. R. & Goldhaber-Gordon, D. Gate-tunable superconducting weak link and quantum point contact spectroscopy on a strontium titanate surface. Nat. Phys. 10, 748–752 (2014).

Winkler, R. Spin orbit coupling effects in two-dimensional electron and hole systems. (Springer–Verlag: Berlin, Heidelberg, New York, 2003).

Gao, X. P. A., Zheng, G. & Lieber, C. M. Subthreshold regime has the optimal sensitivity for nanowire FET biosensors. Nano Lett. 10, 547–552 (2010).

Takase, K., Tanabe, S., Sasaki, S., Hibino, H. & Muraki, K. Impact of graphene quantum capacitance on transport spectroscopy. Phys. Rev. B 86, 165435 (2012).

Takase, K., Hibino, H. & Muraki, K. Probing the extended-state width of disorder-broadened Landau levels in epitaxial graphene. Phys. Rev. B 92, 125407 (2015).

Suzuki, R. et al. 1 nm-capacitance-equivalent-thickness HfO2/Al2O3/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density. Appl. Phys. Lett. 100, 132906 (2012).

Tateno, K., Zhang, G., Gotoh, H. & Sogawa, T. VLS growth of alternating InAsP/InP heterostructure nanowires for multiple-quantum-dot structures. Nano Lett. 12, 2888–2893 (2012).

Acknowledgements

We thank H. Murofushi and S. Saito for technical support.

Author information

Authors and Affiliations

Contributions

K.Takase and S.S. conceived the experiments. K.Takase and Y.A. measured and analyzed the data. Y.A. fabricated the devices under the supervision of S.S. K.Tateno and G.Z. grew InAs nanowires. K.Takase wrote the manuscript with input from all the authors.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Takase, K., Ashikawa, Y., Zhang, G. et al. Highly gate-tuneable Rashba spin-orbit interaction in a gate-all-around InAs nanowire metal-oxide-semiconductor field-effect transistor. Sci Rep 7, 930 (2017). https://doi.org/10.1038/s41598-017-01080-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-01080-0

This article is cited by

-

Electrically and mechanically tunable Rashba splitting in SbSeI Janus layer: a density functional theory study

Scientific Reports (2025)

-

Origin of Rashba Spin-Orbit Coupling in 2D and 3D Lead Iodide Perovskites

Scientific Reports (2020)

-

Study of Rashba Spin–Orbit Field at LaAlO3/SrTiO3 Heterointerfaces

Journal of Electronic Materials (2019)