Abstract

In this article, a 12 switch 31 L multi-level inverter (MLI) is proposed with the benefits of least switching devices for electric vehicle applications. In most electric vehicles (EV), conventional inverters are utilized so the lifetime of electric vehicle induction motors is reduced due to the high THD level and high voltage stress. To rectify this, a new inverter topology is proposed with minimum switching devices by increasing the level to 31, and also the THD should be maintained within IEEE standards. This inverter topology is constructed with variable DC sources (PV system) along with required capacitors and a polarity changer. The specific feature of this topology is that it can generate any level of voltage with minimum switching devices, less voltage stress, minimum THD, and less cost are tabulated in the comparison. This type of inverter can also applicable for high voltage (HV) applications and grid-connected systems. Furthermore, the proposed topology is simulated with MATLAB software and the downscale prototype model is developed using the DSPIC30f2010 controller.

Similar content being viewed by others

Introduction

Power quality is a serious issue when considering the performance analysis of every electrical apparatus1. Particularly in the power system, the third-order harmonics increase the undesirable sharp currents and flow to the neutral conductor, so the detrimental neutral current increases2. In Electric vehicles, conventional cascaded types of multilevel inverters are used in induction motors (IM). These inverters have more THD which does not meet the IEEE standard with less power conversion efficiency, moreover, the voltage stress is greater across the switching devices, and each section has to be isolated from high electromagnetic interference by providing a suitable isolation transformer3. Existing IM-based EVs utilize these inverters, so the induction motor gets affected in terms of performance and the quality of output gets affected which is sensed by advanced-type sensors4. The factors that affect the motor’s performance are as follows: (1) uneven torque is generated due to unbalanced voltage, (2) Magnetic saturation and unequal air gaps occur due to the space harmonics in the windings, moreover, it induce the opposite voltage circulating harmonic currents, (3) The considerable range of power loss, oscillations, rise in temperature, and vibrations are occurring due to the increase of cumulative order of harmonics, (4) Finally, the detrimental effect is gradually built up so that the efficiency and lifetime of the motor are reduced5,6. To solve the above-mentioned problems, the induction motor should receive nearly sinusoidal magnitudes even received from a DC source7. To get a pure sinusoidal voltage from the DC source, a filter can be used but Based on the power quality issue the filter size and cost will increase so the best choice is a multilevel inverter is bringing the DC magnitude into sinusoidal with less THD8. In this modern era, the multilevel inverter is the state of the art in power conversion technology, and due to inherent qualities, the utilizing ratio is increasing drastically rather to the conventional inverter. Several fields like industries, grid-connected systems, solar PV conversion systems, electric vehicle systems, and so on9,10. The traditional MLI is categorized as a diode-clamped inverter, a Flying capacitor type, and a Cascaded H-bridge inverter. Each type is affected by the utilization of switching devices, and their concerning auxiliary components, thereby increasing the cost11. In recent years, researchers have developed many topologies with less switching devices and different voltage levels12,21. In the topology porposed12, shown recently developed reduced switch MLI topologies. These MLIs categorized with several domains like (a) no of phases, (b) no of levels, (c) based on construction, (d) merits and demerits, (e) coordinated operation of symmetric and asymmetric, and finally (f) STATCOM-based inverter.

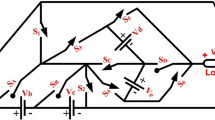

Moreover, in topology12 different voltage levels are compared with a minimum of 5 levels to 27 levels, and a 31 L–12 S MLI is introduced which has the fewest switching devices with only two sources. In modular hybrid converters13, different unbalanced problems arise, so active balance theory is introduced to solve this issue. However, this is only for complex topologies with high dynamic systems. Fourteen switches are used to generate 13-level voltage with the help of two sets of H bridges with switched capacitor units. These two sets of capacitors operate in series and parallel combinations with different levels of voltage generation, so voltage balancing and maintenance levels are decreased14. This work focuses on the Induction motor’s THD analysis with various pulse width modulation (PWM) techniques but earlier research was done in15,16. The neutral point clamped inverter, symmetrical, and hybrid asymmetrical inverters are utilized in induction motors with symmetrical, asymmetrical, phase disposition, phase shift, and hybrid modulation techniques using triangular carrier waves. But it fails to explain the generated voltage level and percentage of harmonics content that occurred in the AC induction motor. To reduce the THD, several reduced switches with dual-source inverters are proposed with higher levels17,18,19,20,21. 12 switches connected with two voltage sources form a new type of symmetrical and asymmetrical-based multilevel inverter proposed in17 illustrated in Fig. 1a and the generated voltage level is 9 and 13. Figure 1. (a) 13 level output is Proposed in ref17, (b) presented in18 and generated 13 level output, (c) four sources with nine level output presented in19, (d). Asymmetrical-based nineteen-level voltage generated with three sources referred in20, (e) Asymmetrical-based thirty-one-level voltage generated with four sources referred in21. The obtained THD levels are 9.09% and 6.25%. To maintain the capacitor voltage, the voltage balancing circuits are used externally. In Fig. 1b, a Switched capacitor-based 13-level voltage is generated18, and in this topology, selective harmonic elimination techniques are used with closed-loop which is complicated. In between the two basic units, the H bridge units are connected with four sources and generate 9 and 17 levels19, and the detailed structure is represented in Fig. 1c. An asymmetrical-based 19 L voltage is generated through the three voltage sources and thirteen switches, with a reduced THD level of 3.89%20 is shown in Fig. 1d. A dynamic load is connected in a 31-level asynchronous-based inverter, to produce this level of voltage only ten switches are required but sources of voltage are increased to four and connected in a cascaded manner21 with 3.71% of THD in a dynamic loading system are shown in Fig. 1e. In the topologies22– 24 different modulation techniques are used to reduce the THD level in an induction motor.

A number of topologies based on switched capacitors have been suggested in25,26,27,28,29,30 for increasing the output voltage levels with boosting ability. In topology26, a 5-level (5 L) extendable topology for centralized photovoltaic systems is introduced. However, achieving higher output voltage levels requires a significant increase in the number of power components, which can impact system complexity and efficiency. As similar to the topology26, the topology proposed in27 also uses more SCs that results in increase in ripple voltage. In28, a 13-level inverter topology with a single DC source is proposed. However, over 67% of its power switches must be rated higher than the output voltage, potentially increasing the cost and complexity of the design. A 17 L SCMLI presented in29 includes the complexity of managing multiple components, potential reliability concerns due to the reliance on several diodes and capacitors, and the need for precise implementation of the soft-charging technique to avoid inefficiencies under varying load conditions. In topology30, a 19-level ANPC-SCMLI was proposed for high-frequency AC power distribution. The topology faces challenges with soft charging inductor design as power increases and requires complex control due to its high component count. Despite a self-balancing feature, maintaining capacitor balance remains difficult, with efficiency peaking at 94.42% at 500 W but likely decreasing at higher power levels. In this work, a 31 L MLI is incorporated in a battery-connected induction motor-based EV which results in low THD. The THD of the existing MLIs is compared to prove the superiority of the 31 L MLI. In this work, a 31 L, twelve switches MLI is introduced which minimizes the THD to a greater extent when compared to the existing topologies.

(a) 13 level output is proposed in ref17, (b) presented in18 and generated 13 level output, (c) four sources with nine level output presented in19, (d) Asymmetrical-based nineteen-level voltage generated with three sources referred in20, (e) Asymmetrical-based thirty-one-level voltage generated with four sources referred in21.

Proposed electric vehicle system with inverter circuits

In high-power electric vehicles, the drive system is a significant part of an induction motor and it has several notable advantages like high efficiency for any speed change, less weight with a high-power rating and better speed regulation, and high-performance characteristics. So, in most of the high-power EVs, an induction motor is used, and to run this IM smoothly without any power quality issues, the inverter part is essential. Commonly, the inverter part in of the system is the “brain of the Electric vehicle system” because without power conversion the induction motor cannot be utilized, so an inverter is the state of the art in power conversion technology. The inverter should produce a good quality of power as per IEEE standards and based on the motor’s speed, the inverter can generate the alternating voltage and current at a suitable frequency.

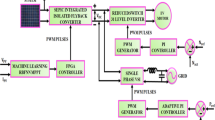

Description of the overall system

The overall system description is illustrated in Fig. 2, in which the large storage battery is charged through the connector. The DC supply from the battery storage (DC-DC Converter) is fed to the proposed 31-level MLI. The induction motor receives an alternating supply through the inverter and also controls the AC power frequency. so that the motor speed is controlled. The inverter is considered most important because of an induction motor driving system”, and it varies the amplitude of the AC power which in turn controls the motor power output. The switching operation of the proposed inverter is controlled using an ANN controller. The Induction motor is affected by THD when the low-level topology is utilized, hence a 31 L asymmetric-based inverter topology is employed in this application to minimize the THD.

Proposed double source 31-level inverter topology

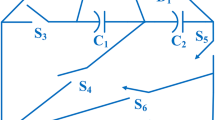

Two different voltage sources VDC1 and VDC2 and the polarity changer are considered as a significant part of this inverter are shown in Fig. 3. The variable source and capacitors are integrated several times into the polarity changer to obtain synthesized step level generating output like a pure sinusoidal. To increase the output waveform, the capacitor part is essential. To get an alternating terminal change in the inverter circuits, mostly H-bridges are used as polarity changers. The main advantage of this type of inverter is, that this inverter can extended at any level by the connection of additional sources. In the level adder portion, only eight switches (S1, S2, S3, S4 and S5, S6, S7, and S8) are integrated into the lower and upper arm of the sources which form the proposed 31 L. Across each source, two capacitors (C1, C2 and C3, C4) are connected with the same and different ratings. But in this paper, two different voltage ratings are used as this is an asymmetrical-based inverter (VDC1 and 3VDC2). The optimum switches and levels are calculated and formed through the equation represented in [17] for symmetrical and unsymmetrical-based inverters. So based on this equation, to generate a 31-level voltage a minimum of 12 switches is required. The generalized structure of the proposed topology and its equations are shown in Fig. 4 and in Table 1.

Description of the switching sequence

The two different voltages are obtained from renewable energy sources. The upper arm source voltage is VDC1 = 18 V and the lower arm source voltage is VDC2 = 4*VDC1 = 72 V, to get different levels four capacitors (C1, C2, and C3, C4) are connected across each of the sources. The Capacity of C1 = 6 V, C2 = 12 V, C3 = 24 V, and C4 = 48 V, during various modes of the Switching Sequence The 31 Level output voltage received in the sum of all possible voltage, i.e. 90 as shown in Fig. 5a,b, a 31 L synthesized waveform is obtained. Table 2 shows the switching state sequence. Figure 5c,d shows a zero-level switching state and 31-level output. Every cycle waveform magnitude and time steps are represented as 6 V and 0.33 ms as per the switching operation represented in Table 2. During this level of generation, a minimum of four switches are triggered along with the polarity changer switches. This topology ensures minimum stress and loss when compared with other mentioned inverter models as the conduction period is less. Table 2 shows the switching state sequence. Figure 5c,d shows a zero-level switching state and 31-level output. Every cycle waveform magnitude and time steps are represented as 6 V and 0.33 ms as per the switching operation represented in Table 2. During this level of generation, a minimum of four switches are triggered along with the polarity changer switches. This topology ensures minimum stress and loss when compared with other mentioned inverter models as the conduction period is less.

Multicarrier PWM technique

The output AC voltage for the multilevel inverter is generated by using (m-1) carriers for m-levels. At the intersection of the carrier and the sinusoidal signal, the switching periods are attained by comparing the triangular carriers with the reference signal. In the positive half cycle, m-1/2 carrier signals are given and during the negative half cycle the remaining m-1/2 carrier signals are given for m- level. The positive voltage levels are produced when the sinusoidal wave is higher than the carrier signal and so m-1/2 carriers are produced above the reference levels. The negative voltage levels are produced when the carrier signal is higher than the sinusoidal signal and so m-1/2 carriers are produced lower than the reference levels. The carrier signal for frequency is chosen as high and the pulse width is directly proportional to the magnitude of the sine wave. When compared to another existing method, the control circuit for the PWM technique is so easy. In this logic, circuit (m-1) carriers are chosen from the generation of the m-level carrier waveform. The Multicarrier PWM signal is illustrated in Fig. 6.

Generally, in this technique, the amplitude of carrier signals and the frequency are found to be equal. In the carrier signal, the modulation index-based PWM is given as the ratio of the reference signal’s amplitude to that of the carrier and it is expressed by the relation,

where Ma denotes the modulation index of amplitude, the amplitude of the sine and the carrier signals is denoted as Am and Ac respectively. The amplitude of the carrier and the modulated signals are 15 V and 14.9 V so the modulation index obtained is 0.993. For the multicarrier technique, the modulation index is varied between 0 and 1, if the value is greater than 1, over-modulation occurs and so the output waveform obtained is a square wave. The frequency ratio is given as the ratio of the carrier wave’s frequency to the reference wave’s frequency and it is expressed by the relation,

where fc denotes the carrier frequency and fm denotes the reference signal frequency. As the frequency of the carrier and the modulated signals are 10 kHz and 50 Hz, the frequency ratio is 200. The inverter is designed to work in the 31 states for one fundamental frequency.

The expressions for the PWM generation are obtained as31 below, From Fig. 7 the expression for the different switches have been obtained as follows (3),

where x denotes the zero state.

Results and discussions

Electric vehicles have attracted more researchers as it preserves the environment and for the enhanced working of EV, a 31 L MLI is introduced in this work with multi-carrier modulation. The key interest of selecting this MLI is that it minimizes the THD so that the performance of the EV gets enhanced. The overall system configuration is simulated in MATLAB and the objectives are verified. The description of the parameters is shown in Table 3. A DC-DC converter is utilized for the step-up function and its output is linked to the capacitor. The 31 L MLI has four capacitors and the input to the capacitors C1, C2, C3, and C4 are set around 6 V, 12 V 24 V, and 48 V respectively as illustrated in Fig. 8. To achieve higher voltage levels, any number of variable sources are coupled with the polarity changer, here H-bridge is utilized as a polarity changer. The output voltage representation of the 31 L MLI as obtained in the simulation is highlighted in Fig. 9.

The proposed topology is tested under various loading conditions, including resistive (R) load, inductive-resistive (RL) load, and motor load, to evaluate its performance. Figure 10a illustrates the output voltage (Vo) and load current (io) waveforms when an R load of 22.5 Ω is applied, showing a load current of 4 A. Similarly, under an RL load of 50 + j90 Ω, the load current obtained is 1.56 A, as depicted in Fig. 10b. For a 0.25 HP motor load, the current increases significantly to 10.4 A, as shown in Fig. 10c. Furthermore, the proposed topology is tested under load variations, transitioning from one RL load to another and from an R load to an RL load, with the corresponding results shown in Fig. 11a,b. Figure 11a presents the output voltage (Vo) and load current (io) waveforms when the load changes from 90 + j50 Ω to 50 + j90 Ω. In Fig. 11b, the load is varied from 22.5 Ω (R load) to 50 + j90Ω (RL load). These results demonstrate the reliable operation of the proposed 31-level inverter topology during transient conditions. Figure 11c shows the main winding current of the motor load while the speed is varied. The proposed 31 L MLI is coupled with the Induction motor-based EV and the motor’s speed is given in Fig. 12 which settles around 1.5 s. The THD of the proposed scheme by incorporating 31 L MLI is obtained as 2.16% in Fig. 13.

Hardware implementation

The proposed induction motor-based EV with 31 L MLI is implemented in hardware using DSPIC30f2010 in Fig. 14. Similar to the simulation, the results are attained for the experimental setup also. Initially, the battery gets charged through the charging port and the DC/DC step-up converter boosts the battery voltage which is then fed to the proposed 31 L MLI. The voltage across each capacitor VC1, VC2, VC3, and VC4 is shown in Fig. 15. The 31 L MLI has four capacitors and 12 switches, the input to the inverter is fed through the capacitor by setting desired voltages. The gate pulses for the switches S1, S4, S8, H1 and H3 are illustrated in Fig. 16.

Figure 17 shows the output voltage of the 31-level. The 31 L MLI is controlled by the pulses generated, and multi-carrier modulation is utilized here. The output of this MLI is fed to the IM-based EV, and the speed of the IM is illustrated in Fig. 18, with the THD of 3.04% in Fig. 19.

Comparative analysis

A comparison table for different multilevel inverters is presented in Table 4 and discussed in this section. The comparison is done considering the following parameters, the number of (levels, sources, switches, capacitors, diodes, switches per level), total standing voltage per unit (TSVp.u.), THDs, CF with different weigh factors (α = 0.5, 1, 1.5), and applications as listed in Table 4. Although the proposed topology and the one presented in23 use the same number of 12 power switches, the TSVp.u. is significantly higher in the23, which also impacts the CF, as shown in Table 4. Similarly, the topology in21 uses one additional switch and an extra DC source compared to the proposed topology, increasing circuit complexity and impacting performance through higher conduction and switching losses. The extra DC source complicates control and adds to the inverter’s size and cost, making the proposed topology more efficient, as shown in Table 4. For a fair comparison among the different topologies listed in Table 4, the metric ‘number of switches per level’ has been calculated and thoroughly analyzed. The analysis reveals that the proposed topology requires fewer switches per level compared to all other topologies, with the exception of the one presented in23. This highlights the proposed topology’s advantages in terms of reduced component count and potential cost savings, making it a more efficient choice. For example, the topology in26 requires only 8 switches to generate a 5 L output. However, due to its extendable nature, scaling it up to a 31 L output demands 47 switches and 15 capacitors, with a TSVp.u. of 35. This value is significantly very higher than that of the proposed topology, indicating that the proposed design offers a more efficient solution with fewer components and lower complexity. The cost function (CF) is calculated using29 as,

The NS/NL/NSW/ND/NC shows the number of sources/levels/switches/diodes/capacitors, “α” represents the weight factor in measuring the importance between the number of components and TSV. The 31 L topologies, including the proposed design and the topologies from21,23,26 have been selected for the Cost Function (CF) comparisons to ensure a fair evaluation. Among the 31 L topologies listed in Table 4, the Cost Function (CF) of the proposed topology is the lowest, indicating that it offers a more cost-effective solution compared to all other topologies examined. This reduced CF reflects the proposed topology’s efficient use of components.

Conclusion

The 31 L–12 S MLI for IM-based EV is analyzed in this work. The generated THD in the induction motor greatly affects the performance of the EV. Hence an MLI that generates more voltage levels is necessary which increases the lifetime of the motor. A 31 L MLI with 12 switches and two DC sources is introduced in this work which has minimized devices with low switching loss and stress across the switches. The working of the proposed 31-level MLI is controlled using an ANN controller. The proposed MLI is validated in MATLAB and it is observed that THD 2.16% is attained. A downscale prototype is developed with DSPIC30F2010 as a controller and this MLI can be extended for HV applications & grid incorporated systems also.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonablerequest.

References

Abur, A. & Kezunovic, M. A simulation and testing laboratory for addressing power quality issues in power systems. IEEE Trans. Power Syst. 14, 3–8 (1999).

Khade, B. R. & Virulkar, V. B. Mitigation of harmonics in a neutral conductor for three-phase four-wire distribution system using series active power filter. In Proc. 2015 IEEE Int. Conf. Electr. Comput. Commun. Technol. ICECCT 2015. https://doi.org/10.1109/ICECCT.2015.7225998 (2015).

Zhang, Y., Chen, G., Hu, Y., Gong, C. & Wang, Y. Cascaded multilevel inverter based power and signal multiplex transmission for electric vehicles. CES Trans. Electr. Mach. Syst. 4, 123–129 (2020).

Corres, J. M., Bravo, J., Arregui, F. J. & Matias, I. R. Unbalance and harmonics detection in induction motors using an optical fiber sensor. IEEE Sens. J. 6, 605–612 (2006).

Duarte, S. X. & Kagan, N. A power-quality index to assess the impact of voltage harmonic distortions and unbalance to three-phase induction motors. IEEE Trans. Power Deliv. 25, 1846–1854 (2010).

Carbonieri, M., Bianchi, N. & Alberti, L. Direct analysis of three-phase induction motor considering Rotor parameters’ variation and Stator Belt Harmonics Effect. IEEE Trans. Ind. Appl. 56, 3559–3570 (2020).

Raymond, C. et al. Induction motor performance testing with an inverter power supply. IEEE Transa Mags. 43, 275–278 (2007).

Akagi, H. Multilevel converters: fundamental circuits and systems. Proc. IEEE 105, 2048–2065 (2017).

Sathik, M. J. et al. Improved dual boost mid-point clamped five-level inverter topology. IEEE Trans. Circuits Syst. II Express Briefs. 71, 3221–3225 (2024).

Kouro, S. et al. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 57, 2553–2580 (2010).

Taghvaie, A., Adabi, J. & Rezanejad, M. A. Multilevel inverter structure based on a combination of switched-capacitors and DC sources. IEEE Trans. Ind. Inf. 13, 2162–2171 (2017).

Salem, A., Van Khang, H., Robbersmyr, K. G., Norambuena, M. & Rodriguez, J. Voltage source multilevel inverters with reduced device count: topological review and novel comparative factors. IEEE Trans. Power Electron. 36, 2720–2747 (2021).

Mariethoz, S. Design and control of high-performance modular hybrid asymmetrical cascade multilevel inverters. IEEE Trans. Ind. Appl. 50, 4018–4027 (2014).

Ye, Y., Lin, M. & Wang, X. Asymmetric cascade multilevel inverter with self-balanced switched-capacitor unit and single source. IET Power Electron. 13, 3254–3262 (2020).

Matsui, K., Kawata, Y. & Ueda, F. Application of parallel connected NPC-PWM inverters with multilevel modulation for AC motor drive. IEEE Trans. Power Electron. 15, 901–907 (2000).

Zambra, D. A. B., Rech, C. & Pinheiro, J. R. Comparison of neutral-point-clamped, symmetrical, and hybrid asymmetrical multilevel inverters. IEEE Trans. Ind. Electron. 57, 2297–2306 (2010).

Prem et al. A new multilevel inverter topology with reduced power components for domestic solar PV applications. IEEE Access. 8, 187483–187497 (2020).

Siddique, M. D., Mekhilef, S., Sarwar, A., Alam, A. & Shah, N. M. Dual asymmetrical dc voltage source based switched capacitor boost multilevel inverter topology. IET Power Electron. 13, 1481–1486 (2020).

Hamidi, M. N., Ishak, D., Zainuri, M. A. A. M. & Ooi, C. A. Multilevel inverter with improved basic unit structure for symmetric and asymmetric source configuration. IET Power Electron. 13, 1445–1455 (2020).

Dhanamjayulu, C., Kaliannan, P., Padmanaban, S., Maroti, P. K. & Holm-Nielsen, J. B. A new three-phase multi-level asymmetrical inverter with optimum hardware components. IEEE Access. 8, 212515–212528 (2020).

Dhanamjayulu, C. et al. Real-time implementation of a 31-level asymmetrical cascaded multilevel inverter for dynamic loads. IEEE Access. 7, 51254–51266 (2019).

Kiadehi, A. D., Drissi, K. E. K. & Pasquier, C. Angular modulation of dual-inverter fed open-end motor for electrical vehicle applications. IEEE Trans. Power Electron. 31, 2980–2990 (2016).

Prabaharan, N. & Palanisamy, K. Comparative analysis of symmetric and asymmetric reduced switch MLI topologies using unipolar pulse width modulation strategies. IET Power Electron. 9, 2808–2823 (2016).

Reddy Sudharshana, K., Muralidhara, V., Ramachandran, A. & Srinivasan, R. Analysis of total harmonic distortion in 5-level inverter fed induction motor. In 2018 Int. Conf. Comput. Power Commun. Technol. GUCON 2018, 800–804. https://doi.org/10.1109/GUCON.2018.8674891 (2019).

Anand, V., Singh, V. & Ali, J. S. M. Symmetrical flying capacitor based multilevel inverter with reduced voltage stress for high frequency aircraft application. In ICPC2T 2022–2nd Int. Conf. Power, Control Comput. Technol. Proc. 1–6. https://doi.org/10.1109/ICPC2T53885.2022.9777065 (2022).

Anand, V., Singh, V., Sathik, J. & Almakhles, D. Single-stage five-level common ground transformerless inverter with extendable structure for centralized photovoltaics. CSEE J. Power Energy Syst. 9, 37–49 (2023).

Anand, V., Singh, V. & Mohamed Ali, J. S. Dual boost five-level switched-capacitor inverter with common ground. IEEE Trans. Circuits Syst. II Express Briefs. 70, 556–560 (2023).

Anand, V. & Singh, V. A 13-Level switched-Capacitor Multilevel Inverter with single DC source. IEEE J. Emerg. Sel. Top. Power Electron. 10, 1575–1586 (2022).

Anand, V. et al. Seventeen level switched capacitor inverters with the capability of high voltage gain and low inrush current. IEEE J. Emerg. Sel. Top. Ind. Electron. 4, 1138–1150 (2023).

Anand, V., Sathik, J., Garcia, C., Blaabjerg, F. & Rodriguez, J. ANPC switched-capacitor 19-L inverter using SHE PWM for 1-ϕ HFAC PDS applications. IEEE J. Emerg. Sel. Top. Power Electron. 12, 4494–4505 (2024).

Islam, S., Siddique, M. D., Iqbal, A., Mekhilef, S. & Al-Hitmi, M. A switched capacitor-based 13-Level inverter with reduced switch count. IEEE Trans. Ind. Appl. 58, 7373–7383 (2022).

Prasad, D. et al. Design and implementation of 31-Level asymmetrical inverter with reduced components. IEEE Access. 9, 22788–22803 (2021).

Srivastava, A., Chauhan, A. & Tripathi, A. Design and performance evaluation of a novel modular asymmetrical multilevel inverter with minimal switches. e-Prime-adv. Electr. Eng. Electron. Energy 9 (2024).

Hussain, S. et al. A New Topology with 31-Levels for cascaded Multilevel Inverters. In SIELMEN 2021—Proc. 11th Int. Conf. Electromechanical Energy Syst., 393–397. https://doi.org/10.1109/SIELMEN53755.2021.9600424 (2021).

Siddique, M. D., Mekhilef, S., Shah, N. M. & Memon, M. A. Optimal design of a new cascaded multilevel inverter topology with reduced switch count. IEEE Access. 7, 24498–24510 (2019).

Ye, Y., Cheng, K. W. E., Liu, J. & Ding, K. A step-up switched-capacitor multilevel inverter with self-voltage balancing. IEEE Trans. Ind. Electron. 61, 6672–6680 (2014).

Dhanamjayulu, C., Padmanaban, S., Ramachandaramurthy, V. K., Holm-Nielsen, J. B. & Blaabjerg, F. Design and implementation of multilevel inverters for electric vehicles. IEEE Access. 9, 317–338 (2021).

Author information

Authors and Affiliations

Contributions

K.S., M.S., N.P.G., M.K., R.A.: Conceptualization, methodology, software, visualization, investigation, writing-original draft preparation. N.P.G.: Data curation, validation, supervision, resources, writing—review and editing. K.S., M.S., N.P.G.: Project administration, supervision, resources, writing—review and editing.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Saravanan, K., Sivasubramanian, M., Gopinath, N.P. et al. A 31 L multilevel inverter topology with less switching devices for hybrid electric vehicle applications. Sci Rep 14, 27459 (2024). https://doi.org/10.1038/s41598-024-78529-6

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-024-78529-6