Abstract

This article presents a technique in nanoscale field effect diode structure to overcome the challenges in conventional field effect diode structures. By reducing the impurity, the amount of additional minority carriers injected from the source and drain areas into the channel and the possibility of band-to-band tunneling between the reservoirs is reduced. But with the decrease of impurity, the ON current also decreases. Using the properties of germanium material in the field effect diode has led to an increase in the ON current, a decrease in gate delay, and an increase in the speed of this device compared to conventional silicon-based structures. In addition, due to the small bandgap of germanium compared to silicon, this device can be used in low-power applications. By comparing the results obtained in the proposed structure with conventional structures, the ON/OFF current ratio is 500 times better, as well as the gate delay and EDP have been reduced from 114 to 0.26 ps and 5.023 × 10–26 to 1.87 × 10–28 j.s, respectively.

Similar content being viewed by others

Introduction

Devices are getting smaller in size as technology requires circuits with faster processing speed and reduced power use. As the device’s size reduces to nanometers, short-channel effects appear, increasing leakage current as well as power consumption1,2,3,4. To reduce such effects, novel structures are needed. The field effect diode, which has good electrical properties and high current capability, is an appropriate alternative to the usual field effect transistor designs in nano dimensions5,6,7,8,9,10,11. Field effect diodes can be used for many different kinds of applications, including electrostatic discharge (ESD) protection12,13, switches, memory cells14,15,16,17, sensors18,19, and integrated circuits20,21. Still, the field effect diode has some downsides. Because of the different impurities in the source and drain regions, as well as the channel being controlled through two gates in the field effect diode, reducing the length of the channel and applying a positive voltage between the drain and the source increases the injection of additional minority carriers into the channel in the OFF state22,23,24. The OFF current increases when more minority carriers are injected. To decrease this problem, reservoirs have been created under the source as well as the drain regions. These reservoirs have different impurities than the source and drain areas, thus in the off state, the injection of additional carriers into the channel is prevented, and the OFF current is minimized25,26. Nevertheless, by reducing the length of the channel below 40 nm and adding reservoirs containing high impurity and a positive electrical voltage between the drain and the source, the possibility of band-to-band tunneling between the reservoirs grows, which causes current leaking to increase27,28,29. In reference30, using materials with a wide band gap in the connection between the channel and the source and drain regions in the channel’s depth reduces the injection rate of additional minority carriers in the OFF-state under the influence of the channel’s drain-source field, resulting in a reduction in the OFF current. In reference31, in order to overcome the injection of additional minority carriers from the side of the source and drain areas into the channel, embedded doped pockets in the source and drain areas at the border of the channel and extended gates on the embedded doped pockets were used. In reference32, using a non-uniform impurity technique in the source and drain regions, it reduces the amount of carrier injection in the OFF state.

In this article, to solve the problem of injecting additional minority carriers from the source and drain areas into the channel, the amount of impurity in the reservoirs and source and drain areas should be reduced, but with the reduction of impurity, the ON current decreases and important parameters such as gate delay and energy-delay product (EDP) also increase. If we reduce the possibility of band-to-band tunneling between the reservoirs, the injected additional minority carriers will be eliminated. Therefore, a field effect diode structure based on germanium material is presented to overcome the challenges in conventional field effect diode structures. Using germanium’s properties (high carrier mobility and narrow band gap) in the field effect diode instead of silicon and creating two current paths increased ON current, a decrease in gate delay, and an increase in speed when compared to conventional structures. Unlike conventional structures, in the proposed structure using reservoirs in the middle, and channel control through the top and bottom gates, the p–n junction under the gates is well formed and creates two current paths. However, this structure can also be employed in low-power applications due to germanium’s narrower energy gap than silicon. According to the results, the proposed structure is a viable option for digital and low-power applications. The proposed structure in this paper is called Ge-DGFED.

Device structure

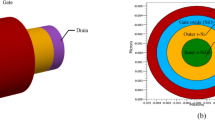

Figure 1 depicts the structure of a conventional Double-Gate field effect diode (C-DGFED). Reservoirs with different impurities are used under the source and drain regions in the C-DGFED diode. These reservoirs are placed to reduce the injection of additional minority carriers from the source and drain areas into the channel within those areas. The field effect diode bias method is presented in Table 1.

In the OFF state, by applying a negative voltage to the gate beside the source and a positive voltage to the gate beside the drain, the channel is replaced by a p–n junction; by applying a positive voltage to the drain, this p–n junction is reverse biased in the channel, and the device is turned OFF. In the state that is OFF, only the minority carriers are involved in the OFF current; so, by reducing the length of the channel and due to the reduction of the length of the passage of the carriers, the amount of the injection of the majority carriers in the source and drain areas into the channel increases. According to the polarity of the gates in the OFF state (the voltage of the gate beside the source is negative and the voltage of the gate beside the drain is positive), these carriers injected from the source and drain regions are considered as minority carriers in the channel. Because of the reverse bias of the p–n junction in the channel, these additional minority carriers injected from the source and drain regions into the channel contribute to the OFF current; thus, as the channel length decreases, this destructive effect increases and the p–n junction does not form well in the channel. As a result, the OFF current rises. By using reservoirs, the amount of carrier injection into the channel is reduced and this destructive effect is improved. The reason the reservoirs are used in FED is that, when the device is OFF, the excess minority carrier injection takes place across the forward-biased n+-p (source side) and n-p+ (drain side) junctions, causing an increase in the electron and hole concentrations in the p region (under GS) and n region (under GD), respectively. This increase of the electron and hole concentrations obstructs the formation of a reverse-biased p–n junction in the channel. Therefore, to achieve a proper OFF current, excess electrons and holes under GS and GD should be reduced. Hence the reservoirs, decrease the forward biases of the n+p and np+ junctions, and the carrier injection into the channel. However, if the channel length is reduced to under 40 nm, there’s a possibility of band-to-band tunneling between the reservoirs with high impurity in the depth of the channel due to their proximity and the drain-source voltage applied, so the OFF current increases again.

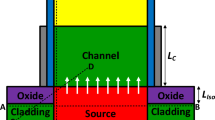

Figure 2 shows a cross-section of the germanium-based field effect diode. In this proposed structure, by using the properties of germanium (high mobility of carriers and narrow band-gap) instead of silicon and creating two current paths with the presence of reservoirs, the amount of ON current, gate delay, and EDP is improved compared to the conventional structure. On the other hand, due to the narrow band gap of germanium compared to silicon, this structure can also be used in low-power applications.

The steps of a process flow for the fabrication of the Ge-DGFED are shown in Fig. 3. The fabrication process is similar to Fin-FET structures33,34. In the first step, we use a weak doped Germanium layer (Fig. 3a). Next, using a suitable mask, consisting of a glass plate (transparent) coated with a pattern, we create n+ and p+ regions by ion implantation (Fig. 3b,c). SiO2 can be deposited to the top of the channel by the thermal deposition method, as shown in Fig. 3d. Finally, the gate electrodes and source/drain contact are deposited (Fig. 3e). The most important challenges in fabricating Ge-DGFED are the distance between the gates and creating thin reservoirs.

All the parameters of the proposed structure (Ge-DGFED) used in the simulation are listed in Table 2. Hurkx band-to-band tunneling (BTBT), SRH and Auger recombination, narrowband (BGN), field-dependent mobility (Fldmob), and impurity-dependent mobility (Conmob) models have been used in this work. The BTBT model activated the band-to-band tunneling calculation between the valence band of a p-region and the conduction band of an n-region. We use Fldmob model due to the high electric field. Because of high impurity values, we need to consider BGN and Conmob models. All the simulations were done by Silvaco software35.

Result and discussion

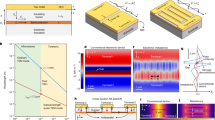

Figure 4 shows the density of carriers and energy bands of the proposed structure at 1 nm below the gate under the gate voltages of 0.7 V and 1.2 V in the OFF state. As can be seen in the figure, the p–n junction is well formed in the depth of the channel for the gate voltages of 0.7 V and 1.2 V, and because of that, a good potential barrier is created in front of the majority of carriers in the source and drain regions.

Figure 5 shows an ON current for the proposed structure and C-DGFED structures. According to the figure, it can be seen that the ON current in the proposed structure has increased significantly compared to conventional structures. This improvement is due to the low band gap of germanium and the high mobility of its carriers compared to silicon. On the other hand, according to the current–voltage characteristic of the proposed structure, it is observed that with the decrease of the drain-source voltage to 0.7 V, the ON current remains almost constant. As current increases, the series resistance of the semiconductor causes a greater voltage drop. This resistance causes the applied voltage to increase to compensate for this drop. Therefore, the proposed structure can be used in low-power applications as well.

The effect of the space between the gates on the gate delay and the ON/OFF current ratio under the bias voltages of 1.2 V and 0.7 V has been investigated in Fig. 6. The results show that by reducing the space between the gates due to the increase in the length of the gate electrode and consequently the increase in the gate capacitor, the gate delay increases. On the other hand, by reducing the distance between the gates, the ON/OFF current ratio decreases. This is caused by the increase in OFF-current due to band-to-band tunneling in the channel.

In Fig. 7, the energy bands of the proposed structure are displayed at 1 nm below the gate under the bias voltages of 1.2 V and 0.7 V in the OFF state for different spaces between the gates. As can be seen in the figure, the probability of band-to-band tunneling in the channel increases as the space between the gates decreases. Hence, the Ge-DGFED structure with 9 nm gate spacing performs best.

The effect of the reservoir thickness on the gate delay and the ON/OFF current ratio under the bias voltages of 1.2 V and 0.7 V has been investigated in Fig. 8. By increasing the thickness of the reservoirs, the ON and OFF currents decrease and, finally the gate delay increases. Therefore, according to Fig. 8, in the proposed structure, the thickness of the reservoirs at 4 nm has the best performance.

Figure 9 shows the changes of the EDP and gate delay in terms of channel length under the biases 1.2 V and 0.7 V. The EDP value is calculated by multiplying energy with gate delay and the gate delay is the time needed to charge the constant gate capacitor to the Vdd at a constant ON-current26. As can be seen in Fig. 9, the proposed structure has less gate delay and EDP due to its high ON-current compared to the C-DGFED structure, hence the proposed structure can be a suitable alternative to common structures in digital applications.

Figure 10 shows the ON/OFF current ratio in terms of channel length. By reducing the amount of impurity, the injection of additional minority carriers into the channel and the possibility of band-to-band tunneling between reservoirs are reduced. But with the reduction of impurity, the ON current also decreases. Therefore, by using germanium instead of silicon in the field effect diode and due to the special properties of germanium, the ON current is also improved, so the Ge-DGFED structure has a better ON/OFF current ratio compared to the conventional structure.

In Table 3, the results of the proposed structure in the same conditions are compared with conventional structures. Table 3 shows that the proposed structure can be a suitable alternative to the common structures.

Conclusion

In this paper, we propose a germanium-based field-effect diode structure with low gate delay and a high ON/OFF current ratio compared to conventional silicon-based structures. By reducing the length of the channel, the injection of additional minority carriers into the channel and the possibility of band-to-band tunneling between reservoirs increases. Therefore, with the reduction of impurity, the amount of carrier injection and the probability of band-to-band tunneling are reduced. On the other hand, the reduction of impurities has a destructive effect on the ON current. Therefore, by using germanium material in the field effect diode instead of silicon, and considering the special properties of germanium, the ON current is significantly improved, and due to the small bandgap of germanium compared to silicon, the proposed structure can be used in low-power applications. The effect of the space between the gates and the reservoir thickness on the ON/OFF current ratio and the gate delay has also been investigated, and according to the obtained results, the proposed structure is a suitable alternative for digital and low-power applications.

Data availability

The datasets and materials used and/or analyzed during the current study are available from the corresponding author on reasonable request (author corresponding: Ali A. Orouji).

References

Moore. G. E. Progress in digital integrated electronics. In Proceedings of International Electron Devices Meeting 11–13 (1975).

Yu, B., Wang, L., Yuan, Y., Asbeck, P. M. & Taur, Y. Scaling of nanowire transistors. IEEE Trans. Electron Devices 55(11), 2846–2858 (2008).

Joshi, G. & Choudhary, A. Analysis of short channel effects in nanoscale MOSFETs. Int. J. Nanosci. 10(01n02), 275–278 (2011).

Kranti, A., Chung, T. M. & Raskin, J. P. Gate length scaling and microwave performance of double gate nanotransistors. Int. J. Nanosci. 4(05n06), 1021–1024 (2005).

Raissi, F. A brief analysis of the field effect diode and breakdown transistor. IEEE Trans. Electron Devices 43(2), 362–365 (1996).

Sheikhian, I. & Raissi, F. High-speed digital family using field effect diode. Electron. Lett. 39(4), 345–347 (2003).

Sheikhian, I. Bulk field effect diode. IEEE Trans. Electron Devices 69(9), 5055–5058 (2022).

Panneerselvam, S., Bhattacharjee, T., Chandramani, P. V. & Raj, S. Impact of process variation on leakage and drive currents of FED structures using linear regression and random forest algorithms. SILICON 16(2), 955–964 (2024).

Rezaei, A. & Orouji, A. A. Performance improvement of nanoscale field effect diode (FED) with modified charge channel: 2D simulation and an analytical surface potential model. Silicon (2021).

Sheikhian, I. & Sharafi, F. Improved nanoscale field effect diode. IET Circuits Devices Syst. 13(4), 544–547 (2019).

Vadizadeh, M. Dual material gate nanowire field effect diode (DMG-NWFED): Operating principle and properties. Microelectron. J. 71, 1–7 (2018).

Cao, S. et al. Design and characterization of ESD protection devices for high-speed I/O in advanced SOI technology. IEEE Trans. Electron Devices 57(3), 644–653 (2010).

Cao, S., Chen, T. W., Beebe, S. G. & Dutton, R. W. ESD design challenges and strategies in deeply-scaled integrated circuits. In Proceedings of Conference on Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 681–688 (2009).

Amirmazlaghani, M. & Raissi, F. Memory cell using modified field effect diode. IEICE Electron. Express. 6(22), 1582–1586 (2009).

PanneerSelvam, S., Pal, S. K., Chandramani, P. V. & Raj, S. Single event performance of FED based SRAMs using numerical simulation. Microelectron. Reliab. 142, 114930 (2023).

Badwan, A. Z. et al. SOI field-effect diode dram cell: Design and operation. IEEE Electron Device Lett. 34(8), 1002–1004 (2013).

Badwan, A. Z., Chbili, Z., Li, Q. & Ioannou, D. E. SOI FED-SRAM cell: Structure and operation. IEEE Trans. Electron Devices 62(9), 2865–2870 (2015).

Mohammadi, E. & Manavizadeh, N. An innovative ion sensitive device based on side-contacted field effect diode. Phys. Status Solidi C 14(12), 1700202 (2017).

Mohammadi, E. & Manavizadeh, N. Performance evaluation of innovative ion-sensitive field effect diode for pH sensing. IEEE Sens. J. 19(4), 1239–1244 (2018).

Jazayeri, F., Forouzandeh, B. & Raissi, F. Low-power variable gain amplifier with UGBW based on nanoscale Field Effect Diode. IEICE Electron. Express 6(1), 51–57 (2009).

Jazaeri, F., Soleimani-Amiri, S., Ebrahimi, B., Forouzandeh, B., Ahmadi, H. R. & Raissi, F. Pseudo-Linear automatic gain control system based on nanoscale field effect diode and SOI-MOSFET. In Proceedings of International Conference on Design and Test workshop, 154–158 (2008).

Rezaei, A., Azizollah-Ganji, B. & Gholipour, M. Effects of the channel length on the nanoscale field effect diode performance. J. Optoelectron. Nanostruct. 3(2) (2018).

Sheikhian, I. & Raissi, F. Simulation results for nanoscale field effect diode. IEEE Trans. Electron Devices 54(3), 613–617 (2007).

Manavizadeh, N., Raissi, F., Soleimani, E. A., Pourfath, M. & Selberherr, S. Performance assessment of nanoscale field-effect diodes. IEEE Trans. Electron Devices 58(8), 2378–2384 (2011).

Manavizadeh, N., Raissi, F., Soleimani, E. A. & Pourfath, M. Geometrical study of nanoscale field effect diodes. Semicond. Sci. Technol. 27(4), 045011 (2012).

Touchaee, B. J. & Manavizadeh, N. An inverter gate design based on nanoscale S-FED as a function of reservoir thickness. IEEE Trans. Electron Devices 62(10), 3147–3152 (2015).

Touchaei, B. J. & Manavizadeh, N. Design and simulation of low-power logic gates based on nanoscale side-contacted FED. IEEE Trans. Electron Devices 64(1), 306–311 (2017).

Rezaei, A., Azizollah-Ganji, B. & Gholipour, M. Nanoscale field effect diode (FED) with improved speed and I ON/I OFF ratio. IET Circuits Devices Syst. 13(3), 309–313 (2018).

Hashemi, S. A., Pourmolla, P. & Jit, S. Double-gate field-effect diode: A novel device for improving digital-and-analog performance. IEEE Trans. Electron Devices 67(1), 18–25 (2019).

Rezaei, A. & Orouji, A. A. Suppression of injected minority carriers in nanoscale field effect diodes to improve the off-current. Eur. Phys. J. Plus 137, 1050 (2022).

Rezaei, A. & Orouji, A. A. Superior energy-delay-production in nanoscale field effect diode by embedded doped pockets for digital applications. J. Mater. Sci. Mater. Electron. 35(1) (2024).

Sharafi, F., Orouji, A. A. & Soroosh, M. The novel structure to enhancement I on/I off ratio based on field effect diode. IEEE Trans. Device Mater. Reliab. 21(3), 389–393 (2021).

Maszara, W. P. Integration challenges for double-gate MOSFET technologies. Proc. Mater. Res. Soc. Symp. 686, 59–68 (2002).

Colinge, J. P. (ed.) FinFETs and Other Multi-gate Transistors 73 (Springer, 2008).

International Device Simulation Software, SILVACO TCAD (2015).

Sotoudeh, A. & Amirmazlaghani, M. Graphene-based field effect diode. Superlattices Microstruct. 120, 828–836 (2018).

Funding

The authors received no financial support for the research, authorship, and/or publication of this article.

Author information

Authors and Affiliations

Contributions

A. Rezaei: Conceptualization, Writing—original draft, Software. Ali A. Orouji: Supervision—review & editing.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Rezaei, A., Orouji, A.A. A technique to reduce the probability of band-to-band tunneling for eliminating injected minority carriers in nano scale field-effect diode. Sci Rep 15, 21891 (2025). https://doi.org/10.1038/s41598-025-07072-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-025-07072-9