Abstract

Medium voltage direct current shipboard power system (MVDC SPS) is the development trend of navy in the future. At present, one of the bottlenecks restricting the development of MVDC SPS is that the short fault. This paper presents a method of applying a hybrid type superconducting fault current limiter (H-SFCL) to MVDC SPS protection. The topology and working principle of H-SFCL are introduced, and current limiting performance is evaluated. The small-scale prototype experiment is done to analyze the current limiting process of common SFCLs and H-SFCLs. The optimal allocation of H-SFCL in MVDC SPS is studied. A novel three-objectives optimal method is proposed to cope with the optimal allocation problems considering both inductive, resistive components and break time of the CBs. The three objective optimization configuration evaluation model for current limiters with both resistive and inductive current limiting components is proposed, which can also optimize the breaking time of external circuit breakers with good convergence.

Similar content being viewed by others

Introduction

With the rapid development of power electronic devices and the urgent need for ship electrification, the medium voltage direct current (MVDC) integrated power system is regarded as the development trend of future ship power systems1. The system has high energy density, high load, and multiple nonlinear loads. The power supply line is short, the system damping is low, and the rise rate of short-circuit current is high. Therefore, it is very difficult to break the DC side fault2, which seriously restricts the expansion of high-energy weapons on board ships and ship power systems. As a forward-looking current limiting method, DC superconducting current limiters meet the current limiting needs of ship systems in terms of fast response, repeatability, protection selectivity, and high automation level. The development of DC superconducting current limiters has led to various topology types, such as resistive, inductive, flux constrained, and hybrid types. Different current limiting topologies have significant differences in current limiting effects and system adaptability.

In terms of studying the role of SFCL in ship power grids, National Kaohsiung University of Marine Science and Technology in Taiwan conducted modeling and simulation on ship power grids and SFCL, analyzing the fault currents at various points of SFCL at different installation positions3. The university of Standard in the UK studied the relationship between the installation position of resistive SFCL and the structure of ship power grids4. The university of South Carolina at Columbia in the United States has proposed the concept of soft reclosing to address the issue of long recovery time for SFCL, which prevents circuit breaker mis-operation by controlling the action of the parallel switch of the current limiter5. However, these studies are primarily focused on traditional AC ship power grids, and to date, few research institutions have reported relevant application studies on SFCLs in ship MVDC systems.

Currently, research on the application of current limiters in optimizing the configuration of ship power systems mainly focuses on resistive and inductive current limiters. For the optimization configuration of resistive current limiters, Reference6 iteratively calculates the short-circuit current limiter of a multi-terminal flexible DC system, and utilizes immune algorithms for single-objective cost optimization of the current limiters; Reference7 considers the maximum fault current and maximum fault removal time as constraints, and applies the genetic algorithm to perform single-objective optimization for the cost of resistive current limiters.

For the optimization configuration of inductive current limiters, Reference8 employs a numerical method for fault current calculation suitable for multi-node flexible DC systems, and applies genetic algorithm to optimize both the total inductance value of the current limiters and the maximum fault current across all circuit breakers; Reference9 utilizes the built-in simplex algorithm in PSCAD to perform a multi-objective optimization, aiming to minimize the sum of the cut-off currents of each DC port circuit breaker and the total absorbed energy of the mental oxide arrester (MOA) in the circuit breaker. However, during the solving process, the problem is transformed into a single-objective optimization problem by applying weight coefficients.

In summary, existing optimization strategies for current limiters are mostly focused on resistive or inductive types, with relatively single variables to be optimized, and the topology types applicable to the optimization methods are very limited; Although some optimization configuration methods mention multi-objective optimization, the vast majority of them are single objective optimization, and a considerable portion of research even transforms multi-objective optimization into weighted single-objective optimization; The current studies only focus on optimizing the configuration of resistors and inductors, without considering the temporal coordination between current limiters and external circuit breakers.

In this paper, the current limiting performance of H-SFCL in MVDC SPS is analyzed. Then, the topology and working principle of H-SFCL are verified by small-scale prototype experiment. Furthermore, the optimal allocation of H-SFCL in MVDC SPS is done.

Current limiting performance of H-SFCL on MVDC SPS

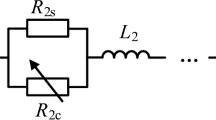

The topology of H-SFCL

The two-stage hybrid superconducting current limiter10 is a non-quenching type current limiter, and its circuit topology is shown in Fig. 1. It is composed of a superconducting coil Lsc, current limiting resistors R1 and R2, a DC fast switch S1 and a metal oxide arrester RMOA. Under normal operating conditions, switch S1 is closed, and steady-state direct current only passes through the superconducting coil without generating electrical energy loss. At the moment of a short-circuit fault, the inductance current does not suddenly change. Most of the short-circuit current is transferred to the R1 branch, and a small portion of the current continues to flow through the LSC. At this stage, the superconducting coil does not quench, and LSC and R1 jointly limit the rise rate of short-circuit current. Subsequently, the rapid increase in the induced voltage at both ends of the superconducting inductor triggers the disconnection of the fast switch S1, and the resistor R2 is put into the circuit. The LSC branch current is limited, and the superconducting coil does not quench. The resistive components provided by R1 and R2 can limit steady-state short-circuit current. The parameter selection of these three components in H-SFCL topology, as well as the breaking time of the circuit breaker, not only determines whether the current limiter can achieve its intended function but also affects the economic efficiency of the system.

Current limiting performance

To investigate the impact of H-SFCL on the DC side faults of the system, connect it in series to the system line, and the system is set to experience an inter pole short circuit fault in the 3 s. The internal component parameters of the hybrid current limiters are R1 = 1 Ω, R2 = 5 Ω, L = 15 mH, and the switch S1 breaking time is 5 ms. When a DC side inter pole short circuit fault occurs in the system, the comparison results of the system characteristics with or without the current limiter are shown in Fig. 2.

From Fig. 2, it can be seen that when a DC side short circuit fault occurs in the system, the output power of the generator will sharply increase from 0.24 pu to 0.97 pu, the speed will decrease from 1 pu to 0.97 pu then back to 1 pu, the output voltage will decrease from 4 kV to 260 V, and the output current will rapidly increase from 4 kA to 20 kA, posing a serious threat to the normal operation of the generator. The DC side current increases from 3.33 kA at a rate of approximately 5.87 kA/s to 29.35 kA, and the DC side voltage decreases to 250 V. The current of the inverter bridge arm increases from 4 kA at a rate of 83.05 kA/s to 20.61 kA, posing a serious threat to the DC side of the inverter and other line equipment. When the H-SFCL is connected to the system, the output power of the generator only increases by 0.02 pu, and the speed is almost the same as normal working conditions. The rate and amplitude of the decrease in excitation voltage and terminal voltage are also effectively slowed down. Within 3 s following the fault occurrence, the decrease is only 0.03 pu, and the output voltage remains almost unchanged. The maximum increase in output current is only 400 A. The maximum increase in bridge arm current of the inverter is 50 A, and the DC side voltage only decreases by 140 V within 3 s after the fault. The peak current on DC side is 7.15 kA, and the steady-state fault current is 3.81 kA. The current limiting rate of the current limiter is about 75.64%. The H-SFCL can effectively alleviate the impact of DC side pole to pole short circuit faults on generator operating conditions, and has a strong inhibitory effect on fault current.

Prototype experiment

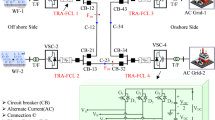

The experiment uses an RLC series connected high-power pulse supply with adjustable parameters to generate DC impact and simulate the short-circuit fault conditions of ships. During the experiment, the current limiting prototype was connected in series to the impact circuit, and the current waveform parameters and coil voltage waveform parameters of the impact circuit were recorded using a wave recorder. Figure 3 is a schematic diagram of the circuit wiring for this experiment.

During the experiment, the superconducting coil is always immersed in liquid nitrogen at 77 K. Platform RLC parameters are set as follows: C1 = 6 mF, R1 = 0.2 Ω, L1 = 0.5 mH, which have been optimally matched in previous work11. The initial voltage at both ends of capacitor C1 is set to 440 V. The experimental data is collected using a DL750 waveform recorder, with a data acquisition duration of 10 ms and a sampling accuracy of 10− 6 seconds. And 105 data points are sampled. The current data is measured through a Rogowski coil and collected by a waveform recorder.

This experiment is conducted under the premise that the total amount of wire used in the coil is the same. Two almost identical superconducting pancakes are used to make three different topologies of current-limiting device prototypes. The superconducting pancakes are made using the second-generation superconducting tape produced by Shanghai Superconducting Technology Company. Its model is ST-12-L/120, with a width of 4.8 mm and a thickness of 0.29 mm. The parameters of the coil after winding are shown in Table 1. The superconducting coil unit of the resistive current limiter is a superconducting non-inductive coil, so the two superconducting pancakes are coupled in a reverse-parallel configuration. The superconducting coil unit of the flux-coupling SFCL and hybrid type SFCL are both superconducting inductive coils, so the two pancakes are positively coupled in series. As shown in Fig. 3, in the hybrid current limiting prototype, the resistance values are set to R1 = 2.1 Ω and R4 = 4 Ω.

Both resistive and inductive prototype experiments do not require additional control units, while hybrid current limiting prototype experiments require two controllable switches. As shown in Fig. 3, switch S1 is the main circuit switch, called the discharge switch. S2 is a branch switch, called a current limiting switch. Switches S1 and S2 are both IGBTs with nominal 400 A and 1200 V. The emission stage of IGBT is connected to the negative terminal of ± 15 V DC power supply, and the gate is connected to the switch action port of the small relay. The microcontroller sends a signal to activate the relay, causing VGE to switch between + 15 V and − 15 V.

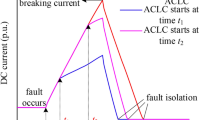

In the experimental preparation stage, S1 is disconnected and S2 is closed. At t = t1, the microcontroller sends a signal to close S1 and discharge the capacitor. After time ∆t (t = t2), S2 is disconnected and resistor R2 is put into the circuit to limit the fault current and protect LSC from overshoot. The time interval ∆t is set to 0.3 ms.

Resistive SFCL prototype experiment

The experimental impulse voltage is 240–440 V, the impulse current is 528–970 A, and the impulse duration is 5.8 ms. Select an impact current limiting condition with an impact voltage of 440 V for analysis. The DC current before and after current limiting and the coil voltage during the current limiting process are shown in Fig. 4. From Fig. 4a, it can be seen that in the absence of current limiter, the peak short − circuit current can reach 970 A. After installing the resistive current limiter, the peak short-circuit current is only 862 A. At this time, the coil current is greater than its critical current of 280 A, and the coil is in a quench state. The current limiting rate is defined as the ratio of the difference between the first peak value before and after the installation of the current limiting device, to the first peak value before installation. The current limiting rate of this resistive current limiting device is approximately 11.1%. As shown in Fig. 4b, the total voltage of the coil is determined by the voltage and inductance corresponding to the quench resistance (13.8 µH). The induced voltage is divided into leading and lagging waveform. The voltage corresponding to the quench resistance is basically synchronized with the DC impulse current, and the induced voltage generated by the inductance is ahead of the impulse current.

The short-circuit current and quench resistance under an impulse voltage of 440 V are shown in Fig. 5a, and the quenching resistance corresponding to 6 impact voltage levels in a group of 240–440 V with intervals of 40 V is shown in Fig. 5b. As shown in Fig. 5a, in the 1–3 ms, the impact current rapidly increases to 862 A, and part of the tapes in the superconducting coil transition from the superconducting state to the quench state and accumulate heat continuously. As the temperature of the tapes increases, the quench resistance gradually increases. In the 3-5.5 ms, as the impact current continues to decrease, liquid nitrogen cooling heat transfer exceeds the heat generation within the tapes, leading to a decrease in both tape temperature and quench resistance. During the entire DC impact process, the superconducting coil partially quenches, with a maximum quench resistance of only 14 mΩ. The higher the impulse voltage, the greater the peak value of the impulse current. As shown in Fig. 5b, the larger the impulse current, the larger the peak value of the quench resistance. The maximum quench resistance corresponding to the 440 V impulse voltage can reach 14 mΩ, the maximum quench resistance corresponding to the 400 V impulse voltage is about 12 mΩ, and the maximum quench resistance corresponding to the 240 V impulse voltage is about 6 mΩ.

Flux-coupling SFCL prototype experiment

The experimental impulse voltage is 240–440 V, the impulse current is 528–970 A, and the impulse duration is 5.8 ms. A quench type flux-coupling SFCL is selected for analysis under 440 V impulse voltage, which limits the current through inductance and quench impedance. The DC current before and after current limiting and the coil voltage during the current limiting process are shown in Fig. 6. From Fig. 6a, it can be seen that the peak current reaches 970 A in the absence of the current limiter. The peak current after installing a flux-coupling SFCL is about 701 A, with a current limiting rate of 27.7%. As shown in Fig. 6b, the total voltage of the coil is composed of both induced voltage and resistance voltage. The maximum forward voltage of the coil can reach 182.38 V, and the maximum reverse voltage can reach 58.83 V. The current exhibits the highest increase rate near 1ms, leading to a sharp increase in the induced voltage, which peaks at 45.8 V; Four seconds later, the impulse current begins to decrease, and the rate of decrease gradually increases. The induced voltage reverses and reaches a maximum of 76.48 V. The trend of voltage of the two branch coils is basically consistent, with the maximum forward voltage reaching 85.87 V.

The flux-coupling SFCL current limiting impedance and quench resistance are presented in Fig. 7a. At 0.8 ms, the system is in the early stage of short-circuit fault, and the inductive component of the superconducting coil plays the primary role in limiting the rise rate of short-circuit current. The current limiting impedance at the moment of short-circuit can reach 26 Ω. In the middle of the short-circuit current, the quench resistance of the superconducting coil plays a major role in limiting the peak impulse current, with a current limiting impedance of approximately 0.1 Ω. As illustrated in Fig. 7b, during the entire current limiting process, the maximum quench resistance of the coil can reach 0.075 Ω.

Hybrid-type SFCL prototype experiment

The experimental impulse voltage is 240–440 V, the impulse current is 528–970 A, and the impulse duration is 5.8 ms. The internal resistance of the hybrid SFCL is specified as R1 = 2.1 Ω and R2 = 4 Ω. The action of switch S2 is triggered 0.3 ms after the occurrence of the short circuit. The mixed DC current and current limiting impedance situation is shown in Fig. 8. From Fig. 8a, it can be seen that the peak short-circuit current without a current limiter is 970 A. After the installation of the current limiter, the peak current is reduced to 252 A, with a current limiting rate of 74.1%. Under the circumstance, the maximum current of the superconducting coil is 95.4 A, which is less than 145 A, ensuring that the coil maintained in a non-quench state. Furthermore, it can be observed that at approximately 7 ms, due to the freewheeling effect of the inductor in the H-SFCL, the current without the H-SFCL decreases to zero, whereas with H-SFCL, it does not; From Fig. 8b, it can be concluded that at the moment of a short-circuit fault, the experimental impedance can reach a maximum of 2.5 Ω, and the simulated impedance can reach a maximum value of 2.25 Ω. The current limiting impedance at the moment of fault is composed of R1 and L, which are used to suppress the rate of short-circuit current change. R1 serves as a shunt to ensure that L remains in a non-quenching state; After 0.3 ms from the fault occurrence, R2 is introduced, further enhancing the current limiting impedance. Subsequently, after 2 ms, the current limiting impedance stabilizes at 1.4 Ω. In the steady state, the current limiting impedance is primarily composed of R1 and R2.

The comparison between simulation and experimental results for hybrid voltage and current are shown in Fig. 9. According to Fig. 9a, the maximum voltage of R1 in the experiment can reach 370 V, exhibiting a variation trend that aligns with the impulse current. During the current limiting process, coil L primarily mitigates the short-circuit current by suppressing the rate of current changes through its inductive properties. Therefore, at the beginning of the experiment, the maximum forward voltage of the coil can reach 150 V, and the maximum reverse voltage can reach 148 V. After 2 ms, the current limiting impedance of the coil is approximately 0. According to Fig. 9b, the maximum current of the experimental coil can reach 85.34 A, the maximum current of R1 can reach 261.28 A, and the maximum total current flowing through the current limiter can reach 249.87 A. The reason why the R1 voltage in Fig. 9a and the current simulation value in Fig. 9b are generally higher than the experimental values is because that there are line resistance and contact resistance in the experiment. The simulation of the coil voltage amplitude is larger because the current rise rate in the experiment is lower than that in the simulation, and the overall trend and amplitude of the experimental and simulated curves exhibit a high degree of consistency.

The current limiting characteristics of R-SFCL, FC-SFCL, and H-SFCL under a 440 V impulse voltage are presented in Table 2. It can be observed that the current limiting rate of H-SFCL is significantly higher than that of R-SFCL and FC-SFCL. Moreover, H-SFCL doesn’t quench, thus doesn’t require quench recovery, and has good safety and stability. The maximum quenching resistance of R-SFCL and FC-SFCL are 14 mΩ and 75 mΩ, respectively. They both use quenching resistance to limit steady-state current. R-SFCL is difficult to limit short circuit current effectively in the rising stage of short circuit current, so its limiting effect on the peak value of DC fault current is not obvious. Due to the continuous current effect of inductance, FC-SFCL and H-SFCL exhibit poor current limiting performance during the fault current decay phase. Among the three configurations, R-SFCL has the lowest peak coil voltage, FC-SFCL has the highest, while H-SFCL exhibits an intermediate peak coil voltage. Consequently, special attention should be paid to the coil insulation issues of both H-SFCL and FC-SFCL.

Optimal allocation of H-SFCL on MVDC SPS

There is a triple game between the performance and economy of H-SFCL and circuit breakers:

(1) is the game between the breaking time, breaking current and the cost of the circuit breakers (the shorter the breaking time, the greater the breaking current, the stronger the performance but also the higher the cost).

(2) is the game between the cost of current limiters and the cost of circuit breakers (the better the current limiting effect of current limiters, the smaller the current flowing through the circuit breakers, the lower the breaking pressure of the circuit breakers, and the lower the cost of the circuit breakers. However, a better current limiting effect means that the cost of the circuit breakers will increase).

(3) is the game between the current limiting performance of the current limiters and their cost (the greater the resistance and inductance, the better the current limiting effect, but the larger the inductance (superconducting tape winding) will increase the cost of the current limiters).

Using a three objective immune algorithm, starting from the optimization objectives of current limiting effect, current limiter economy, circuit breaker economy, and their impact on current limiting effect, the three internal parameters of each current limiter and the circuit breaker opening time of each branch are optimized. In a three-terminal system, the number of current limiters is set to 3. The optimization variables are R1, L and R2 values inside the three current limiters, as well as the opening time of the three circuit breakers. The initial population is set to 100 individuals and the maximum number of iterations is set to 20. The lower bounds for R1, L, R2, and tCB of the three sets of current limiting isolation devices are 1 Ω, 5 mH, 1 Ω and 4 ms, respectively, while the upper bounds are 5 Ω, 20 mH, 5 Ω, and 10ms. The immune algorithm performs crossover with a probability of 90% and mutation with a probability of 10%, as shown in Table 3.

Optimization objective:

-

(1)

The minimum sum of the maximum breaking currents of all circuit breakers.

The objective function is shown in Eq. (1), Where M is the set of all ports, p is any one of them, and k is the port that makes \(i_{j}^{{\hbox{max} }}\)maximum. \(i_{{j,\text{C}\text{B},k}}^{{\hbox{max} }}\)is the maximum current flowing through port j when the most severe short-circuit fault occurs on all ports (in this case, port k).

-

(2)

The maximum sum of the breaking time of all circuit breakers.

When considering the current limiting and breaking configuration comprehensively, one of the objective functions is the maximum sum of the breaking time of all circuit breakers, as shown in Eq. (2), \(t_{{\text{C}\text{B}}}^{j}\)is the breaking time of the jth port circuit breaker.

-

(3)

The sum of the maximum inductive energy all current limiters is the smallest.

The objective function is to minimize the sum of the maximum inductive energy in all current limiters, as shown in Eq. (3), where M is the set of all ports, p is any one of them, and k is the port that maximizes \(E_{j}^{{\hbox{max} }}\). \(E_{{j,\text{S}\text{F}\text{C}\text{L},k}}^{{\hbox{max} }}\)is the maximum energy on the inductor in the jth port current limiter.

The iterative process of the 1-20th generation optimization corresponding to the three objective optimization is shown in Fig. 10. It can be observed that after 20 iterations, the values of the three optimization objectives have largely converged. The sum of the maximum current through the circuit breakers ranges from 10 to 15 kA, the sum of the maximum inductive energy is concentrated between 0 and 320 kJ, and the sum of the breaking time of the circuit breakers falls between 24 and 28 ms. Specifically, the sum of the breaking time of the circuit breaker was mainly concentrated between 10 kA and 20 kA from the first to the fourth generation. From 11th generation to 20th generation, this value almost fully converges to a range of 10–18 kA. Regarding the sum of the maximum inductive energy, it has almost entirely converged below 320 kJ by 4th generation, with little distribution variation among individuals starting from 14th generation. The sum of the breaking time of the circuit breakers saw minimal change by 16th generation, fully converging to a range of 18 ms to 28 ms, with the majority concentrated between 24 ms and 28 ms.

Conclusion

The article evaluates the performance of H-SFCL in current limiting applications in MVDC SPS, and studies the current limiting process of three types of SFCL. An innovative model is proposed for a three-objective optimization configuration of H-SFCL in MVDC SPS. The results indicate that:

-

(1)

The current-limiting effect of the H-SFCL in MVDC SPS is significant, achieving a current limiting-rate of approximately 75.64%;

-

(2)

In resistive and inductive experiments, the coil does not completely quench, and the quench resistance undergoes a process of first increasing and then decreasing with the short-circuit current;

-

(3)

Among the three current limiting topologies, the H-SFCL not only has the best short-circuit current limiting effect, but also enhances the reliability of the system due to the non-quench working mode of its superconducting coil;

-

(4)

The proposed three-objective optimization configuration method can effectively solve the optimization configuration problem of current limiters with both resistive and inductive current limiting components, and can optimize the breaking time of external circuit breakers with good convergence.

Data availability

The datasets generated from this work are available from the corresponding author on reasonable request.

References

Andrea, V., Giorgio, S., Robert, C. & Vikas, S. Simplified analytical modeling and experimental validation of diode bridge rectifier operation during rail-to-rail short-circuit faults in synchronous generator-fed dc distribution systems. In IEEE Second International Conference on DC Microgrids (ICDCM), 596–601 (2017).

Kuntal, S., Abhisek, U. & Josep, P. Short-circuit fault management in DC electric ship propulsion system: protection requirements, review of existing technologies and future research trends. IEEE Trans. Transp. Electrif. 4, 272–291 (2017).

Su, C. L., Su, C. Y., Lee, C. C. & Chen, C. J. Fault current limiter allocation in electric ship power systems. In IEEE Electric Ship Technologies Symposium, 53–58 (2017).

Blair, S. M., Booth, C. D. & Elders, N. K. Superconducting fault current limiter application in a power-dense marine electrical system. IET Electr. Syst. Transp. 1 (3), 93–102 (2011).

Zhang, Y., Ali, H. & Dougal, R. Soft reclosing of fault current limiters in electric ship power systems. In IEEE Electric Ship Technologies Symposium (ESTS). 244–247 (2011).

Yu, P., Venkatesh, B., Yazdani, A. & Singh, B. Optimal location and sizing of fault current limiters in mesh networks using iterative mixed integer nonlinear programming. IEEE Trans. Power Syst. 31 (6), 4776–4783 (2016).

Teng, J. H. c. N., L. Optimum fault current limiter placement with search space reduction technique. IET Gener Transm Distrib. 4 (4), 485–494 (2010).

Yang, H., Tang, W. & Lubicki, P. Placement of fault current limiters in a power system through a two-stage optimization approach. IEEE Trans. Power Syst. 33 (1), 131–140 (2018).

Pham, T. & Jai, G. Short circuit current level reduction in power system by optimal placement of fault current limiter. Int. Trans. Electr. Energy Syst. 27, 1–16 (2017).

Liang, S. Study on the current limiting performance of a novel SFCL in DC systems. IEEE Trans. Appl. Supercond. 27 (4), 1–6 (2017).

Li, Z. et al. Electromagnetic design and performance analysis of a hybrid-type superconducting fault current limiter in shipboard MVDC IPS. IEEE Trans. Appl. Supercond. 32 (6), 5601104 (2022).

Author information

Authors and Affiliations

Contributions

Z.Y. conducted data ananlysis and wrote the maunscript. R.L. conducted project administration and supervision. All authors contributed to the revision of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Zhou, Y., Ren, L., Xu, Y. et al. Optimal application research of superconducting fault current limiters on medium voltage direct current shipboard power system. Sci Rep 15, 14568 (2025). https://doi.org/10.1038/s41598-025-97751-4

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-97751-4