Abstract

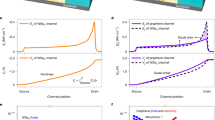

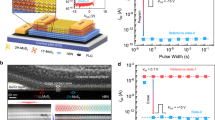

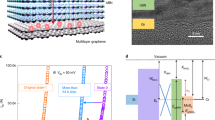

Data-driven computing is highly dependent on memory performance. Flash memory is presently the dominant non-volatile memory technology but suffers from limitations in terms of speed. Two-dimensional (2D) materials could potentially be used to create ultrafast flash memory. However, due to interface engineering problems, ultrafast non-volatile performance is presently restricted to exfoliated 2D materials, and there is a lack of performance demonstrations with short-channel devices. Here, we report a scalable integration process for ultrafast 2D flash memory that can be used to integrate 1,024 flash-memory devices with a yield of over 98%. We illustrate the approach with two different tunnelling barrier configurations of the memory stack (HfO2/Pt/HfO2 and Al2O3/Pt/Al2O3) and using transferred chemical vapour deposition-grown monolayer molybdenum disulfide. We also show that the channel length of the ultrafast flash memory can be scaled down to sub-10 nm, which is below the physical limit of silicon flash memory. Our sub-10 nm devices offer non-volatile information storage (up to 4 bits) and robust endurance (over 105).

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Source data are provided with this paper. Other data that support the plots in this paper and the other findings of this study are available from the corresponding authors on reasonable request.

Code availability

The codes used for the simulation are available from the corresponding authors on reasonable request.

References

Kahng, D. & Sze, S. M. A floating gate and its application to memory devices. Bell Syst. Tech. J. 46, 1288–1295 (1967).

International Technology Roadmap for Semiconductors 2.0 (ITRS, 2015); www.itrs2.net/

Liu, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotechnol. 16, 874–881 (2021).

Wu, L. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021).

Huang, X. et al. An ultrafast bipolar flash memory for self-activated in-memory computing. Nat. Nanotechnol. 18, 486–492 (2023).

Yu, J. et al. Simultaneously ultrafast and robust two-dimensional flash memory devices based on phase-engineered edge contacts. Nat. Commun. 14, 5662 (2023).

Migliato Marega, G. et al. A large-scale integrated vector–matrix multiplication processor based on monolayer molybdenum disulfide memories. Nat. Electron. 6, 991–998 (2023).

Vu, Q. A. et al. A high‐on/off‐ratio floating‐gate memristor array on a flexible substrate via CVD‐grown large‐area 2D layer stacking. Adv. Mater. 29, 1703363 (2017).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Marega, G. M. et al. How to achieve large-area ultra-fast operation of MoS2 monolayer flash memories? IEEE Nanotechnol. Mag. 17, 39–43 (2023).

Helm, M. et al. A 128Gb MLC NAND-flash device using 16nm planar cell. In Proc. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 326–327 (IEEE, 2014).

Sako, M. et al. A low power 64 Gb MLC NAND-flash memory in 15 nm CMOS technology. IEEE J. Solid-State Circuits 51, 196–203 (2015).

Lee, S. et al. A 128Gb 2b/cell NAND flash memory in 14nm technology with tPROG= 640µs and 800MB/s I/O rate. In Proc. 2016 IEEE International Solid-State Circuits Conference (ISSCC) 138–139 (IEEE, 2016).

International Roadmap for Devices and Systems (IRDS, 2022); https://irds.ieee.org/

Sun, X. et al. Reconfigurable logic-in-memory architectures based on a two-dimensional van der Waals heterostructure device. Nat. Electron. 5, 752–760 (2022).

Migliato Marega, G. et al. Low-power artificial neural network perceptron based on monolayer MoS2. ACS Nano 16, 3684–3694 (2022).

Wang, S. et al. New floating gate memory with excellent retention characteristics. Adv. Electron. Mater. 5, 1800726 (2019).

Vu, Q. A. et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat. Commun. 7, 12725 (2016).

Zhang, E. et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 9, 612–619 (2015).

Wang, J. et al. Floating gate memory-based monolayer MoS2 transistor with metal nanocrystals embedded in the gate dielectrics. Small 11, 208–213 (2015).

Sup Choi, M. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 4, 1624 (2013).

Li, D. et al. Nonvolatile floating-gate memories based on stacked black phosphorus–boron nitride-MoS2 heterostructures. Adv. Funct. Mater. 25, 7360–7365 (2015).

Lee, D. et al. Black phosphorus nonvolatile transistor memory. Nanoscale 8, 9107–9112 (2016).

Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano 7, 3246–3252 (2013).

Huang, M. et al. Energy-band parameters of atomic-layer-deposition Al2O3/InGaAs heterostructure. Appl. Phys. Lett. 89, 012903 (2006).

Naitoh, Y., Tsukagoshi, K., Murata, K. & Mizutani, W. A reliable method for fabricating sub-10 nm gap junctions without using electron beam lithography. e-J. Surf. Sci. Nanotechnol. 1, 41–44 (2003).

Miao, J., Zhang, S., Cai, L., Scherr, M. & Wang, C. Ultrashort channel length black phosphorus field-effect transistors. ACS Nano 9, 9236–9243 (2015).

Patel, K. A., Grady, R. W., Smithe, K. K., Pop, E. & Sordan, R. Ultra-scaled MoS2 transistors and circuits fabricated without nanolithography. 2D Mater. 7, 015018 (2019).

Acknowledgements

This work was supported by the National Natural Science Foundation of China (Grant Nos. 61925402, 62322405, 62374042 and 62090032), the Shanghai Pilot Programme for Basic Research-FuDan University (Grant Nos. 21TQ1400100 and 21TQ011), the Shanghai Rising-Star Programme (Grant No. 22QA1400700), the Innovation Programme of Shanghai Municipal Education Commission (Grant No. 2021-01-07-00-07-E00077) and the young scientist project of the Ministry of Education’s innovation platform. Part of the sample fabrication was conducted at Fudan Nano-fabrication Lab.

Author information

Authors and Affiliations

Contributions

C. Liu and P.Z. conceived the idea. C. Liu, Y.J. and Z.C. designed and conducted the experiments. C. Li and Z.L. provided valuable input on sub-10 nm device fabrication. C.W. provided valuable input on sub-10 nm device simulation. Y.X. provided valuable input on device fabrication. C. Liu and Y.J. co-wrote the manuscript, and all authors contributed to the discussion and revision of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Jing-Kai Huang, Fei Xue and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Sections 1–13 containing Figs. S2-1, S2-2, S2-3, S2-4, S2-5, S2-6, S2-7, S3-1, S3-2, S4-1, S5-1, S7-1, S8-1, S9-1, S9-2, S9-3, S10-1, S11-1 and S13-1, Tables S1-1, S2-1 and S12-1, and corresponding discussions.

Source data

Source Data Fig. 1

Statistical source data.

Source Data Fig. 2

Statistical source data.

Source Data Fig. 3

Statistical source data.

Source Data Fig. 4

Statistical source data.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jiang, Y., Liu, C., Cao, Z. et al. A scalable integration process for ultrafast two-dimensional flash memory. Nat Electron 7, 868–875 (2024). https://doi.org/10.1038/s41928-024-01229-6

Received:

Accepted:

Published:

Issue date:

DOI: https://doi.org/10.1038/s41928-024-01229-6

This article is cited by

-

Subnanosecond flash memory enabled by 2D-enhanced hot-carrier injection

Nature (2025)

-

8-bit states in 2D floating-gate memories using gate-injection mode for large-scale convolutional neural networks

Nature Communications (2025)

-

In-sensor compressing via programmable optoelectronic sensors based on van der Waals heterostructures for intelligent machine vision

Nature Communications (2025)