Abstract

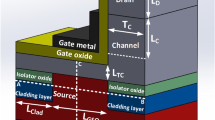

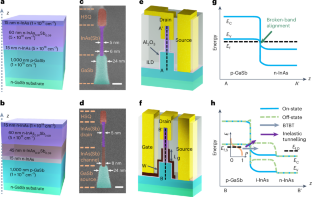

The development of data-centric computing requires new energy-efficient electronics that can overcome the fundamental limitations of conventional silicon transistors. A range of novel transistor concepts have been explored, but an approach that can simultaneously offer high drive current and steep slope switching while delivering the necessary scaling in footprint is still lacking. Here, we report scaled vertical-nanowire heterojunction tunnelling transistors that are based on the broken-band GaSb/InAs system. The devices offer a drive current of 300 µA µm−1 and a sub-60 mV dec−1 switching slope at an operating voltage of 0.3 V. The approach relies on extreme quantum confinement at the tunnelling junction and is based on an interface-pinned energy band alignment at the tunnelling heterojunction under strong quantization.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Source data are provided with this paper. Other data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat. Electron. 1, 442–450 (2018).

Ionescu, A. M. Energy efficient computing and sensing in the zettabyte era: from silicon to the cloud. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) Technical Digest 1.2.1–1.2.8 (IEEE, 2017).

Zhou, Z. et al. Edge intelligence: paving the last mile of artificial intelligence with edge computing. Proc. IEEE 107, 1738–1762 (2019).

Datta, S., Chakraborty, W. & Radosavljevic, M. Toward attojoule switching energy in logic transistors. Science 378, 733–740 (2022).

Mehonic, A. & Kenyon, A. J. Brain-inspired computing needs a master plan. Nature 604, 255–260 (2022).

Horowitz, M. et al. Scaling, power, and the future of CMOS. In Proc. 2005 IEEE International Electron Devices Meeting (IEDM) Technical Digest 7–15 (IEEE, 2005).

Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59, 1813–1828 (2012).

Lundstrom, M. S. & Alam, M. A. Moore’s law: the journey ahead. Science 378, 722–723 (2022).

Ferain, I., Colinge, A. A. & Colinge, J.-P. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479, 310–316 (2011).

Frank, D. J. et al. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89, 259–288 (2001).

Khan, A. I. et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 14, 182–186 (2015).

Cheema, S. et al. Ultrathin ferroic HfO2–ZrO2 superlattice gate stack for advanced transistors. Nature 604, 65–71 (2022).

Qiu, C. et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science 361, 387–392 (2018).

Shukla, N. et al. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 6, 7812 (2015).

Lu, H. & Seabaugh, A. Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Devices Soc. 2, 44–49 (2014).

Avci, U. E., Morris, D. H. & Young, I. A. Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Devices Soc. 3, 88–95 (2015).

Esseni, D., Pala, M., Palestri, P., Alper, C. & Rollo, T. A review of selected topics in physics based modeling for tunnel field-effect transistors. Semicond. Sci. Technol. 32, 083005 (2017).

Luisier, M. & Klimeck, G. Performance comparisons of tunneling field-effect transistors made of InSb, carbon, and GaSb-InAs broken gap heterostructures. In Proc. 2009 IEEE International Electron Devices Meeting (IEDM) Technical Digest 37.6.1–37.6.4 (IEEE, 2009).

Brocard, S., Pala, M. G. & Esseni, D. Design options for hetero-junction tunnel FETs with high on current and steep sub-threshold voltage slope. In Proc. 2013 IEEE International Electron Devices Meeting (IEDM) Technical Digest 5.4.1–5.4.4 (IEEE, 2013).

Convertino, C. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Krishnaraja, A. et al. Tuning of source material for InAs/InGaAsSb/GaSb application-specific vertical nanowire tunnel FETs. ACS Appl. Electron. Mater. 2, 2882–2887 (2020).

Memisevic, E., Svensson, J., Lind, E. & Wernersson, L.-E. Vertical nanowire TFETs with channel diameter down to 10 nm and point SMIN of 35 mV/decade. IEEE Electron Device Lett. 39, 1089–1091 (2018).

Alian, A. et al. Record 47 mV/dec top-down vertical nanowire InGaAs/GaAsSb tunnel FETs. In Proc. 2018 IEEE Symposium on VLSI Technology 133–134 (IEEE, 2018).

Zhao, X., Vardi, A. & del Alamo, J. A. Sub-thermal subthreshold characteristics in top-down InGaAs/InAs heterojunction vertical nanowire tunnel FETs. IEEE Electron Device Lett. 38, 855–858 (2017).

Memisevic, E., Svensson, J., Hellenbrand, M., Lind, E. & Wernersson, L.-E. Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion = 10 μA/μm for Ioff = 1 nA/μm at Vds = 0.3 V. In Proc. 2016 IEEE International Electron Devices Meeting (IEDM) Technical Digest 19.1.1–19.1.4 (IEEE, 2016).

Bijesh, R. et al. Demonstration of In0.9Ga0.1As/GaAs0.18Sb0.82 near broken-gap tunnel FET with ION = 740 μA/μm, GM = 700 μS/μm and gigahertz switching performance at VDS = 0.5 V. In Proc. 2013 IEEE International Electron Devices Meeting (IEDM) Technical Digest 28.2.1–28.2.4 (IEEE, 2013).

Dey, A. W. et al. High-current GaSb/InAs(Sb) nanowire tunnel field-effect transistors. IEEE Electron Device Lett. 34, 211–213 (2013).

Yakimets, D. et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans. Electron Devices 62, 1433–1439 (2015).

Shao, Y., Pala, M., Esseni, D. & del Alamo, J. A. Sub-10-nm diameter GaSb/InAs vertical nanowire Esaki diodes with ideal scaling behavior: experiments and simulations. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) Technical Digest 32.1.1–32.1.4 (IEEE, 2021).

Zhao, X. & del Alamo, J. A. Nanometer-scale vertical-sidewall reactive ion etching of InGaAs for 3-D III-V MOSFETs. IEEE Electron Device Lett. 35, 521–523 (2014).

Lu, W. et al. 10-nm fin-width InGaSb p-channel self-aligned FinFETs using antimonide-compatible digital etch. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) Technical Digest 17.7.1–17.7.4 (IEEE, 2017).

Pawlik, D. et al. Benchmarking and improving III-V Esaki diode performance with a record 2.2 MA/cm2 peak current density to enhance TFET drive current. In Proc. 2012 IEEE International Electron Devices Meeting (IEDM) Technical Digest 27.1.1–27.1.3 (IEEE, 2012).

Bhatnagar, K. et al. Integration of broken-gap heterojunction InAs/GaSb Esaki tunnel diodes on silicon. J. Vac. Sci. Technol. B 33, 062203 (2015).

Convertino, C. et al. Investigation of InAs/GaSb tunnel diodes on SOI. In Proc. 017 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS) 148–151 (IEEE, 2017).

Cutaia, D. et al. Complementary III–V heterojunction lateral NW tunnel FET technology on Si. In Proc. 2016 Symposium on VLSI Technology 1–2 (IEEE, 2018).

Borg, B. M. et al. Influence of doping on the electronic transport in GaSb/InAs(Sb) nanowire tunnel devices. Appl. Phys. Lett. 101, 043508 (2012).

Afzalian, A. et al. Physics and performances of III–V nanowire broken-gap heterojunction TFETs using an efficient tight-binding mode-space NEGF model enabling million-atom nanowire simulations. J. Phys.: Condens. Matter 30, 254002 (2018).

Yan, R. et al. Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment. Nano Lett. 9, 5791–5798 (2015).

Sajjad, R. N., Chern, W., Hoyt, J. L. & Antoniadis, D. A. Trap assisted tunneling and its effect on subthreshold swing of tunnel FETs. IEEE Trans. Electron Devices 63, 4380–4387 (2016).

Zhao, X. et al. Sub-10 nm diameter InGaAs vertical nanowire MOSFETs. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) Technical Digest 17.2.1–17.2.4 (IEEE, 2017).

Memisevic, E. et al. Individual defects in InAs/InGaAsSb/GaSb nanowire tunnel field-effect transistors operating below 60 mV/decade. Nano Lett. 17, 4373–4380 (2017).

Pala, M. G. & Esseni, D. Interface traps in InAs nanowire tunnel-FETs and MOSFETs. Part I. Model description and single trap analysis in tunnel-FETs. IEEE Trans. Electron Devices 60, 2795–2801 (2013).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) Technical Digest 29.1.1–29.1.4.44 (IEEE, 2017).

Lu, W. et al. First transistor demonstration of thermal atomic layer etching: InGaAs FinFETs with sub-5 nm fin-width featuring in situ ALE-ALD. In Proc. 2018 IEEE International Electron Devices Meeting (IEDM) Technical Digest 39.1.1–39.1.4 (IEEE, 2018).

Esaki, L. New phenomenon in narrow germanium p–n junctions. Phys. Rev. 109, 603–604 (1958).

Wang, Z., Wang, L., En, Y. & Jiang, X.-W. Quantum confinement modulation on the performance of nanometer thin body GaSb/InAs tunnel field-effect transistors. J. Appl. Phys. 121, 224503 (2017).

Na, J. et al. Low-frequency noise in multilayer MoS2 field-effect transistors: the effect of high-k passivation. Nanoscale 6, 433–441 (2014).

Kilpi, O.-P., Svensson, J. & Wernersson, L.-E. Sub-100-nm gate-length scaling of vertical InAs/InGaAs nanowire MOSFETs on Si. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) Technical Digest 17.3.1–17.3.4 (IEEE, 2017).

Tomioka, K., Yoshimura, M. & Fukui, T. A III–V nanowire channel on silicon for high-performance vertical transistors. Nature 488, 189–192 (2012).

Tomioka, K., Gamo, H., Motohisa, J. & Fukui, T. Vertical gate-all-around tunnel FETs using InGaAs nanowire/Si with core-multishell structure. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM) Technical Digest 21.1.1–21.1.4 (IEEE, 2020).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Knoll, L. et al. Inverters with strained Si nanowire complementary tunnel field-effect transistors. IEEE Electron Device Lett. 34, 813–815 (2013).

Krishnamohan, T., Kim, D., Raghunathan, S. & Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and ≪60 mV/dec subthreshold slope. In Proc. 2008 IEEE International Electron Devices Meeting (IEDM) Technical Digest 1–3 (IEEE, 2008).

Kim, S. et al. Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nat. Nanotechnol. 15, 203–206 (2020).

Rangasamy, G., Zhu, Z. & Wernersson, L.-E. High current density vertical nanowire TFETs with I60 > 1 μA/μm. IEEE Access 11, 95692–95696 (2023).

Vandenberghe, W. G. et al. Figure of merit for and identification of sub-60 mV/decade devices. Appl. Phys. Lett. 102, 013510 (2013).

Sharma, A., Goud, A. A. & Roy, K. GaSb-InAs n-TFET with doped source underlap exhibiting low subthreshold swing at sub-10-nm gate-lengths. IEEE Electron Device Lett. 35, 1221–1223 (2014).

Afzalian, A., Passlack, M. & Yeo, Y.-C. Atomistic simulation of gate-all-around GaSb/InAs nanowire TFETs using a fast full-band mode-space NEGF model. In Proc. 2016 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2016).

Lu, W., Zhao, X., Choi, D., El Kazzi, S. & del Alamo, J. A. Alcohol-based digital etch for III–V vertical nanowires with sub-10 nm diameter. IEEE Electron Device Lett. 38, 548–551 (2017).

Shao, Y., Pala, M., Esseni, D. & del Alamo, J. A. Scaling of GaSb/InAs vertical nanowire Esaki diodes down to sub-10-nm diameter. IEEE Trans. Electron Devices 69, 2188–2195 (2022).

Krishnaraja, A., Svensson, J., Lind, E. & Wernersson, L.-E. Reducing ambipolar off-state leakage currents in III-V vertical nanowire tunnel FETs using gate-drain underlap. Appl. Phys. Lett. 115, 143505 (2019).

Kresse, G. & Furthmüller, J. Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set. Phys. Rev. B 54, 11169–11186 (1996).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865–3868 (1996).

Dudarev, S. L., Botton, G. A., Savrasov, S. Y., Humphreys, C. J. & Sutton, A. P. Electron-energy-loss spectra and the structural stability of nickel oxide: an LSDA+U study. Phys. Rev. B 57, 1505–1509 (1998).

Kresse, G. & Joubert, D. From ultrasoft pseudopotentials to the projector augmented-wave method. Phys. Rev. B 59, 1758–1775 (1999).

Yu, M., Yang, S., Wu, C. & Marom, N. Machine learning the Hubbard U parameter in DFT+U using Bayesian optimization. npj Comput. Mater. 6, 180 (2020).

Monkhorst, H. J. & Pack, J. D. Special points for Brillouin-zone integrations. Phys. Rev. B 13, 5188–5192 (1976).

Smidstrup, S. et al. QuantumATK: an integrated platform of electronic and atomic-scale modelling tools. J. Phys.: Condens. Matter 32, 015901 (2020).

van Setten, M. J. et al. The PseudoDojo: training and grading a 85 element optimized norm-conserving pseudopotential table. Comput. Phys. Commun. 226, 39–54 (2018).

Tao, S. X., Cao, X. & Bobbert, P. A. Accurate and efficient band gap predictions of metal halide perovskites using the DFT-1/2 method: GW accuracy with DFT expense. Sci. Rep. 7, 14386 (2017).

Çakır, D. & Peeters, F. M. Dependence of the electronic and transport properties of metal-MoSe2 interfaces on contact structures. Phys. Rev. B 89, 245403 (2014).

Birner, S. et al. nextnano: general purpose 3-D simulations. IEEE Trans. Electron Devices 54, 2137–2142 (2007).

Cardona, M. & Pollak, F. H. Energy-band structure of germanium and silicon: the k · p method. Phys. Rev. 142, 530–543 (1966).

Vurgaftman, I., Meyer, J. R. & Ram-Mohan, L. R. Band parameters for III–V compound semiconductors and their alloys. J. Appl. Phys. 89, 5815 (2001).

Bahder, T. B. Eight-band k · p model of strained zinc-blende crystals. Phys. Rev. B 41, 11992–12001 (1990).

Brocard, S., Pala, M. & Esseni, D. Large on-current enhancement in hetero-junction tunnel-FETs via molar fraction grading. IEEE Electron Device Lett. 35, 184–186 (2014).

Jain, S. C., McGregor, J. M. & Roulston, D. J. Band-gap narrowing in novel III-V semiconductors. J. Appl. Phys. 68, 3747–3749 (1990).

Stollwerck, G., Sulima, O. V. & Bett, A. W. Characterization and simulation of GaSb device-related properties. IEEE Trans. Electron Devices 47, 448–457 (2000).

Conzatti, F., Pala, M., Esseni, D., Bano, E. & Selmi, L. Strain-induced performance improvements in InAs nanowire tunnel FETs. IEEE Trans. Electron Devices 59, 2085–2092 (2012).

Cleveland, W. S. Robust locally weighted fitting and smoothing scatterplots. J. Am. Stat. Assoc. 74, 829–836 (1979).

Savitzky, A. & Golay, M. J. E. Smoothing and differentiation of data by simplified least squares procedures. Anal. Chem. 36, 1627–1639 (1964).

Acknowledgements

This work was supported by Intel Corporation and MIT Donner Endowed Chair. B.M. and J.L. acknowledge support from DTRA (Award No. HDTRA1-20-2-0002) through the Interaction of Ionizing Radiation with Matter University Research Alliance. Device fabrication was carried out at MIT.nano, MTL and SEBL of MIT. We thank G. Dewey, U. E. Avci and A. V. Penumatcha at Intel Corporation for fruitful discussions. We thank M. Robinson at Intel Corporation for SIMS measurements. We thank X. Zhao, W. Lu and A. Vardi for insightful suggestions. We thank J. Zhu, Q. Xie and T. Zeng for helpful suggestions during device fabrication and measurements. We thank Z. Hu and P. Zhang for discussions on the physical properties of InAs.

Author information

Authors and Affiliations

Contributions

Y.S. and J.A.d.A. designed the study. Y.S. fabricated the devices and performed SEM imaging, electrical characterization and two-dimensional device simulations. M.P. and D.E. carried out the NEGF-based 3D quantum-transport simulations. H.T. and Y.S. carried out the first-principles calculations supervised by J.L. B.W. performed the FIB and TEM imaging of materials and devices supervised by J.L. Y.S. and J.A.d.A. wrote the manuscript. All authors read and revised the manuscript in its current form.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Aryan Afzalian and Cezar Zota for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary text, Scheme 1, Figs. 1–10, Tables 1 and 2, and refs. S1–S5.

Source data

Source Data Fig. 2

Statistical source data.

Source Data Fig. 3

Statistical source data.

Source Data Fig. 4

Statistical source data.

Source Data Fig. 5

Statistical source data.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Shao, Y., Pala, M., Tang, H. et al. Scaled vertical-nanowire heterojunction tunnelling transistors with extreme quantum confinement. Nat Electron 8, 157–167 (2025). https://doi.org/10.1038/s41928-024-01279-w

Received:

Accepted:

Published:

Issue date:

DOI: https://doi.org/10.1038/s41928-024-01279-w

This article is cited by

-

Nanosheet transistors: materials, devices, systems and applications

Journal of Materials Science (2025)