Abstract

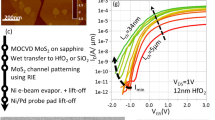

Two-dimensional semiconductors are a potential channel material for transistors with highly scaled contacted poly pitch (CPP). Total scaling of CPP requires the simultaneous reduction of channel length and contact length. However, the physical width limit of contact metals makes it difficult to form effective small-size contacts. In addition, decreasing the contact length below the transfer length induces a current crowding phenomenon, resulting in an exponential increase in contact resistance and poor device performance. Here we show that composite metal contact electrodes of gold/titanium/nickel can offer shape-preserving effects that allow the extreme scaling of contact length in two-dimensional transistors while maintaining a low contact resistance. We use the approach to create molybdenum disulfide transistors with a CPP of around 60 nm—contact length and channel length scaled to around 30 nm and transfer length scaled to under 30 nm—that exhibit on/off ratios over 108, on-state currents of around 300 μA μm−1 and off-state currents down to around 1 pA μm−1. We also fabricate arrays of all-out scaled two-dimensional transistors that exhibit low variability in key performance metrics and demonstrate their integration into advanced logic circuits.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Source data are provided with this paper. Other data that support the plots in this paper and other findings of this study are available from the corresponding authors on reasonable request.

References

Li, W., Shen, H., Qiu, H., Shi, Y. & Wang, X. Two-dimensional semiconductor transistors and integrated circuits for advanced technology nodes. Natl Sci. Rev. 11, nwae001 (2024).

Chang, C. H. et al. Critical process features enabling aggressive contacted gate pitch scaling for 3 nm CMOS technology and beyond. In Proc. 2022 International Electron Devices Meeting (IEDM) 27.21.21–27.21.24 (IEEE, 2022).

International Roadmap for Devices and Systems (IRDS, 2022); https://irds.ieee.org/

Fan, D. et al. Two-dimensional semiconductor integrated circuits operating at gigahertz frequencies. Nat. Electron. 6, 879–887 (2023).

Lin, Y. et al. Scaling aligned carbon nanotube transistors to a sub-10 nm node. Nat. Electron. 6, 506–515 (2023).

Irisawa, T., Numata, T., Tezuka, T., Sugiyama, N. & Takagi, S. I. Electron transport properties of ultrathin-body and tri-gate SOI nMOSFETs with biaxial and uniaxial strain. In Proc. 2006 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2006).

Uchida, K. et al. Experimental study on carrier transport mechanism in ultrathin-body SOI n- and p-MOSFETs with SOI thickness less than 5 nm. In Proc. 2002 International Electron Devices Meeting (IEDM) 47–50 (IEEE, 2002).

He, X. et al. Impact of aggressive fin width scaling on FinFET device characteristics. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 20.22.21–20.22.24 (IEEE, 2017).

Wang, S. et al. Two-dimensional devices and integration towards the silicon lines. Nat. Mater. 21, 1225–1239 (2022).

Dorow, C. J. et al. Gate length scaling beyond Si: Mono-layer 2D channel FETs robust to short channel effects. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.5.1–7.5.4 (IEEE, 2022).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Cheng, Z. et al. Distinct contact scaling effects in MoS2 transistors revealed with asymmetrical contact measurements. Adv. Mater. 35, 2210916 (2023).

Wu, W. C. et al. Scaled contact length with low contact resistance in monolayer 2D channel transistors. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023).

Smets, Q. et al. Ultra-scaled MOCVD MoS2 MOSFETs with 42 nm contact pitch and 250 µA/µm drain current. In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) 23.22.21–23.22.24 (IEEE, 2019).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS2 devices. 2D Mater. 4, 011009 (2017).

Guo, Y. et al. Study on the resistance distribution at the contact between molybdenum disulfide and metals. ACS Nano 8, 7771–7779 (2014).

Yuan, H. et al. Field effects of current crowding in metal-MoS2 contacts. Appl. Phys. Lett. 108, 103505 (2016).

Cheng, Z. et al. Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Lett. 19, 5077–5085 (2019).

Andrews, K., Bowman, A., Rijal, U., Chen, P.-Y. & Zhou, Z. Improved contacts and device performance in MoS2 transistors using a 2D semiconductor interlayer. ACS Nano 14, 6232–6241 (2020).

Arutchelvan, G. et al. From the metal to the channel: a study of carrier injection through the metal/2D MoS2 interface. Nanoscale 9, 10869–10879 (2017).

Szabó, Á., Jain, A., Parzefall, M., Novotny, L. & Luisier, M. Electron transport through metal/MoS2 interfaces: edge- or area-dependent process? Nano Lett. 19, 3641–3647 (2019).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Schranghamer, T. F. et al. Ultrascaled contacts to monolayer MoS2 field effect transistors. Nano Lett. 23, 3426–3434 (2023).

Schroder, D. K. Semiconductor Material and Device Characterization 3rd edn (Wiley, 2005).

Berger, H. H. Models for contacts to planar devices. Solid-State Electron. 15, 145–158 (1972).

Berger, H. H. Contact resistance and contact resistivity. J. Electrochem. Soc. 119, 507 (1972).

Gong, C. et al. Metal contacts on physical vapor deposited monolayer MoS2. ACS Nano 7, 11350–11357 (2013).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Shi, Y. et al. Superior electrostatic control in uniform monolayer MoS2 scaled transistors via in-situ surface smoothening. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 37.31.31–37.31.34 (IEEE, 2021).

Tang, J. et al. Low power flexible monolayer MoS2 integrated circuits. Nat. Commun. 14, 3633 (2023).

Liu, H. et al. Statistical study of deep submicron dual-gated field-effect transistors on monolayer chemical vapor deposition molybdenum disulfide films. Nano Lett. 13, 2640–2646 (2013).

Arutchelvan, G. et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 11, 6610 (2021).

Xu, K. et al. Sub-10 nm nanopattern architecture for 2D material field-effect transistors. Nano Lett. 17, 1065–1070 (2017).

Kumar, A. et al. Sub-200 Ω·µm alloyed contacts to synthetic monolayer MoS2. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.3.1–7.3.4 (IEEE, 2021).

Natarajan, S. et al. A 32 nm logic technology featuring 2nd-generation high-k + metal-gate transistors, enhanced channel strain and 0.171 μm2 SRAM cell size in a 291 Mb array. In Proc. 2008 IEEE International Electron Devices Meeting (IEDM) 1–3 (IEEE, 2008).

Auth, C. et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proc. 2012 Symposium on VLSI Technology (VLSIT) 131–132 (IEEE, 2012).

Natarajan, S. et al. A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. In Proc. 2014 IEEE International Electron Devices Meeting (IEDM) 3.7.1–3.7.3 (IEEE, 2014).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 29.21.21–29.21.24 (IEEE, 2017).

Liu, L. et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 368, 850–856 (2020).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Lanza, M., Smets, Q., Huyghebaert, C. & Li, L.-J. Yield, variability, reliability, and stability of two-dimensional materials based solid-state electronic devices. Nat. Commun. 11, 5689 (2020).

Acknowledgements

This work was supported by the National Key Research and Development Program of China (2021YFA1200500 to P.Z.), National Natural Science Foundation of China (61925402, 62090032 to P.Z., 62304042 to S.W.) and Science and Technology Commission of Shanghai Municipality (19JC1416600 to P.Z., 24JD1400200, 23YF1402100 to S.W.). This work was supported by the New Cornerstone Science Foundation through the XPLORER PRIZE. Part of the sample fabrication was performed at Fudan Nano-fabrication Laboratory.

Author information

Authors and Affiliations

Contributions

S.W. and P.Z. conceived the idea and supervised the work. S.C. and S.W. designed and conducted the experiments with the assistance of C.L.; Z.L., T.W., Y.Z. and H.W. provided valuable input on testing and characterization; S.C. and S.W. co-wrote the manuscript. All authors provided suggestions for revisions and improvements to the work.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Yann-Wen Lan, Ye Zhou and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Sections 1–12.

Source data

Source Data Fig. 1

Statistical source data.

Source Data Fig. 2

Statistical source data.

Source Data Fig. 3

Statistical source data.

Source Data Fig. 4

Statistical source data.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chen, S., Wang, S., Liu, Z. et al. Channel and contact length scaling of two-dimensional transistors using composite metal electrodes. Nat Electron 8, 394–402 (2025). https://doi.org/10.1038/s41928-025-01382-6

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-025-01382-6

This article is cited by

-

Van der Waals materials for energy-efficient electronic devices

Nature Reviews Materials (2026)

-

100 years of field-effect transistors

Nature Electronics (2025)

-

Towards 1-nm-node electronics with two-dimensional transistors

Nature Electronics (2025)

-

Scaling the contacted poly pitch of 2D transistors

Nature Electronics (2025)

-

Epitaxial growth of wafer-scale 2D superconductor single crystals by metal-organic chemical vapor deposition

Nature Communications (2025)