Abstract

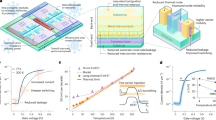

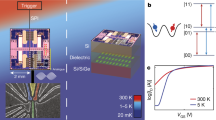

Universal cryogenic computing, encompassing von Neumann, neuromorphic and quantum computing, paves the way for future big-data processing with high energy efficiency. Complementary metal oxide semiconductor (CMOS) technology operating at cryogenic temperatures with ultra-low power consumption is a key component of this advancement. However, classical CMOS technology, designed for room temperature applications, suffers from band-tail effects at cryogenic levels, leading to an increased subthreshold swing and decreased mobility values. In addition, threshold voltages are enlarged. Thus, classical CMOS technology fails to meet the low power requirements when cooled close to zero Kelvin. In this Perspective, we show that steep slope cryogenic devices can be realized by screening the band tails with the use of high-k dielectrics and wrap-gate architectures and/or reducing them through the optimization of the surfaces and interfaces within the transistors. Cryogenic device functionality also strongly benefits from appropriate source/drain engineering employing dopant segregation from silicides. Furthermore, the threshold voltage control can be realized with back-gating, work-function engineering and dipole formation. As a major implication, future research and development towards cryogenic CMOS technology requires a combination of these approaches to enable universal cryogenic computing at the necessary ultra-low power levels.

Key points

-

Computing technologies — including classical von Neumann, advanced quantum and neuromorphic computing — at cryogenic temperatures offer power-saving solutions for big-data centres and even new computing paradigms. A cryogenic complementary metal oxide semiconductor (cCMOS) with ultra-low power consumption is a key component for cryogenic computing.

-

Conventional CMOS technology designed for room temperature applications does not meet the ultra-low power requirements because of critical issues such as dopant freeze-out, band-tailing and Fermi-energy shifting at cryogenic temperatures.

-

Band-tailing is a major challenge for reducing power consumption because it increases the subthreshold swing and noise while decreasing the carrier mobility. Potential solutions to mitigate band-tailing include interface engineering, source/drain engineering and improved screening using high-k dielectrics and gate-all-around nanowire device architectures.

-

Power reduction is also limited by the increase in threshold voltages at cryogenic temperatures. New materials with small bandgaps, metals with appropriate work functions and dielectrics with dipoles are proposed to control the threshold voltage.

-

A net power reduction factor of 0.27 at 77 K and 0.22 at 4 K compared with room temperature is expected at the system level after improving the subthreshold swing and threshold voltage, making it suitable for quantum computing.

This is a preview of subscription content, access via your institution

Access options

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Jones, N. How to stop data centres from gobbling up the world’s electricity. Nature 561, 163–166 (2018).

Knoch, J. et al. Toward low‐power cryogenic metal‐oxide semiconductor field‐effect transistors. Phys. Status Solidi A 220, 2300069 (2023). This review discusses the band-tail effects and the reduction of band tails by improved screening.

Moroz, V., Svizhenko, A., Choi, M., Asenov, P. & Lee, J. Exploring power savings of gate-all-around cryogenic technology. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185420 (IEEE, 2023). This paper discusses the power saving of central processing units at cryogenic temperatures.

Chiang, H. L. et al. Cold CMOS as a power-performance-reliability booster for advanced FinFETs. In Proc. 2020 IEEE Symposium on VLSI Technology https://doi.org/10.1109/VLSITechnology18217.2020.9265065 (IEEE, 2020). This paper reports the power saving for FinFETs down to 77 K.

Vandersypen, L. M. K. et al. Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent. Npj Quantum Inf. 3, 34 (2017). This paper discusses the scalability of device architectures for quantum computation with spin qubits, control signals and co-integrations of classical von Neumann circuits.

Zwerver, A. M. J. et al. Qubits made by advanced semiconductor manufacturing. Nat. Electron. 5, 184–190 (2022).

Burkard, G., Ladd, T. D., Pan, A., Nichol, J. M. & Petta, J. R. Semiconductor spin qubits. Rev. Mod. Phys. 95, 025003 (2023).

Neyens, S. et al. Probing single electrons across 300-mm spin qubit wafers. Nature 629, 80–85 (2024).

Philips, G. et al. Universal control of a six-qubit quantum processor in silicon. Nature 609, 919–924 (2022).

Xue, X. et al. CMOS-based cryogenic control of silicon quantum circuits. Nature 593, 205–210 (2021).

Pauka, S. J. et al. A cryogenic CMOS chip for generating control signals for multiple qubits. Nat. Electron. 4, 64–70 (2021).

Moon, H. et al. Machine learning enables completely automatic tuning of a quantum device faster than human experts. Nat. Commun. 11, 4161 (2020).

Struck, T. et al. Robust and fast post-processing of single-shot spin qubit detection events with a neural network. Sci. Rep. 11, 16203 (2021).

Gebhart, V. et al. Learning quantum systems. Nat. Rev. Phys. 5, 141–156 (2023).

Battistel, F. et al. Real-time decoding for fault-tolerant quantum computing: progress, challenges and outlook. Nano Futur. 7, 032003 (2023).

Hafez, I. M., Ghibaudo, G. & Balestra, F. Assessment of interface state density in silicon metal-oxide-semiconductor transistors at room, liquid-nitrogen, and liquid-helium temperatures. J. Appl. Phys. 67, 1950–1952 (1990).

Gutierrez-D, E. A., Deen, M. J. & Claeys, C. L. Low Temperature Electronics: Physics, Devices, Circuits, and Applications (Elsevier, 2001).

Balestra, F. & Ghibaudo, G. Physics and performance of nanoscale semiconductor devices at cryogenic temperatures. Semicond. Sci. Technol. 32, 023002 (2017).

Ando, T., Fowler, A. B. & Stern, F. Electronic properties of two-dimensional systems. Rev. Mod. Phys. 54, 437–672 (1982).

Beckers, A., Jazaeri, F. & Enz, C. Theoretical limit of low temperature subthreshold swing in field-effect transistors. IEEE Electron. Device Lett. 41, 276–279 (2020). This paper describes theoretically the saturation of the SS at cryogenic temperatures due to band-tailing.

Beckers, A., Jazaeri, F. & Enz, C. Inflection phenomenon in cryogenic MOSFET behavior. IEEE Trans. Electron. Devices 67, 1357–1360 (2020). This paper identifies and explains the physics behind the inflection phenomenon.

Parihar, S. S. et al. Cryogenic characterization and model extraction of 5nm technology node FinFETs. In Proc. 2023 7th IEEE Electron Devices Technology & Manufacturing Conference (EDTM) https://doi.org/10.1109/EDTM55494.2023.10102942 (IEEE, 2023).

Taur, Y. & Ning, T. H. Fundamentals of Modern VLSI Devices (Cambridge Univ. Press, 1998).

Han, H.-C., Zhao, Z., Lehmann, S., Charbon, E. & Enz, C. Analytical modeling of cryogenic subthreshold currents in 22-nm FDSOI technology. IEEE Electron. Device Lett. 45, 92–95 (2024). This paper covers the modelling of cryogenic subthreshold current in short channel devices caused by the hopping and SDT transports.

Bohuslavskyi, H. et al. Cryogenic subthreshold swing saturation in FD-SOI MOSFETs described with band broadening. IEEE Electron. Device Lett. 40, 784–787 (2019).

Beckers, A., Beckers, D., Jazaeri, F., Parvais, B. & Enz, C. Generalized Boltzmann relations in semiconductors including band tails. J. Appl. Phys. 129, 045701 (2021).

Kang, M.-S. et al. Influence of substrate impurity concentration on sub-threshold swing of Si n-channel MOSFETs at cryogenic temperatures down to 4 K. Jpn. J. Appl. Phys. 62, SC1062 (2023).

Han, H.-C., Chiang, H.-L., Radu, I. P. & Enz, C. Analytical modeling of source-to-drain tunneling current down to cryogenic temperatures. IEEE Electron. Device Lett. 44, 717–720 (2023).

Jing W. & Lundstrom, M. Does source-to-drain tunneling limit the ultimate scaling of MOSFETs? In Proc. Digest. International Electron Devices Meeting 707–710 (IEEE, 2002).

Kao, K.-H. et al. Subthreshold swing saturation of nanoscale MOSFETs due to source-to-drain tunneling at cryogenic temperatures. IEEE Electron. Device Lett. 41, 1296–1299 (2020).

Jiao, T., Antunez, E. & Wong, H. Y. Study of cryogenic MOSFET sub-threshold swing using ab initio calculation. IEEE Electron. Device Lett. 44, 1604–1607 (2023).

Yilmaz, K., Iniguez, B., Lime, F. & Kloes, A. Cryogenic temperature and doping analysis of source-to-drain tunneling current in ultrashort-channel nanosheet MOSFETs. IEEE Trans. Electron. Devices 69, 1588–1595 (2022).

Hiblot, G., Rafhay, Q., Boeuf, F. & Ghibaudo, G. Analytical relationship between subthreshold swing of thermionic and tunnelling currents. Electron. Lett. 50, 1745–1747 (2014).

Kamgar, A. Subthreshold behavior of silicon MOSFETs at 4.2 K. Solid-State Electron. 25, 537–539 (1982).

Takagi, S., Toriumi, A., Iwase, M. & Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: part I—effects of substrate impurity concentration. IEEE Trans. Electron. Devices 41, 2357–2362 (1994).

Matsumoto, Y. & Uemura, Y. Scattering mechanism and low temperature mobility of MOS inversion layers. Jpn. J. Appl. Phys. 13, 367 (1974).

Melnikov, M. Y. et al. Ultra-high mobility two-dimensional electron gas in a SiGe/Si/SiGe quantum well. Appl. Phys. Lett. 106, 092102 (2015).

Sumita, K., Kang, M.-S., Toprasertpong, K., Takenaka, M. & Takagi, S. Formulation of ground states for 2DEG at rough surfaces and application to nonlinear model of surface roughness scattering in nMOSFETs. IEEE J. Electron. Devices Soc. 11, 216–229 (2023).

Abrahams, E., Kravchenko, S. V. & Sarachik, M. P. Metallic behavior and related phenomena in two dimensions. Rev. Mod. Phys. 73, 251–266 (2001).

Mouis, M. et al. Source/drain induced defects in advanced MOSFETs: what device electrical characterization tells. Phys. Status Solidi C. 11, 138–145 (2014). This paper shows that neutral scattering can degrade the mobility for short channel devices at cryogenic temperatures.

Habicht, S., Feste, S., Zhao, Q.-T., Buca, D. & Mantl, S. Electrical characterization of Ω-gated uniaxial tensile strained Si nanowire-array metal-oxide-semiconductor field effect transistors with <100>- and <110> channel orientations. Thin Solid. Films 520, 3332–3336 (2012).

Cardoso Paz, B. et al. Integrated variability measurements of 28 nm FDSOI MOSFETs down to 4.2 K for cryogenic CMOS applications. In Proc. 2020 IEEE 33rd International Conference on Microelectronic Test Structures (ICMTS) https://doi.org/10.1109/ICMTS48187.2020.9107906 (IEEE, 2020).

Cassé, M. et al. FDSOI for cryoCMOS electronics: device characterization towards compact model. In Proc. 2022 International Electron Devices Meeting (IEDM) 34.6.1–34.6.4 (IEEE, 2022).

Hart, P. A. T., Babaie, M., Charbon, E., Vladimirescu, A. & Sebastiano, F. Characterization and modeling of mismatch in cryo-CMOS. IEEE J. Electron. Devices Soc. 8, 263–273 (2020).

Han, H.-C. et al. Back-gate effects on DC performance and carrier transport in 22 nm FDSOI technology down to cryogenic temperatures. Solid-State Electron. 193, 108296 (2022).

Han, Y. et al. Characterization of fully silicided source/drain SOI UTBB nMOSFETs at cryogenic temperatures. Solid-State Electron. 192, 108263 (2022).

Han, H.-C. et al. Cryogenic characterization of 16 nm FinFET technology for quantum computing. In Proc. ESSCIRC 2021 - IEEE 47th European Solid State Circuits Conference (ESSCIRC) 71–74 (IEEE, 2021).

Bonen, S. et al. Cryogenic characterization of 22 nm FDSOI CMOS technology for quantum computing ICs. IEEE Electron. Device Lett. 40, 127–130 (2019).

Ono, Y. et al. Conductance modulation by individual acceptors in Si nanoscale field-effect transistors. Appl. Phys. Lett. 90, 102106 (2007).

Catapano, E., Cassé, M. & Ghibaudo, G. Cryogenic MOSFET subthreshold current: from resistive networks to percolation transport in 1-D systems. IEEE Trans. Electron. Devices 70, 4049–4054 (2023).

Pierre, M. et al. Single-donor ionization energies in a nanoscale CMOS channel. Nat. Nanotechnol. 5, 133–137 (2009).

Hart, P. A. T., Babaie, M., Charbon, E., Vladimirescu, A. & Sebastiano, F. Subthreshold mismatch in nanometer CMOS at cryogenic temperatures. IEEE J. Electron. Devices Soc. 8, 797–806 (2020).

Paz, B. C. et al. Variability evaluation of 28nm FD-SOI technology at cryogenic temperatures down to 100mK for quantum computing. In Proc. 2020 IEEE Symposium on VLSI Technology https://doi.org/10.1109/VLSITechnology18217.2020.9265034 (IEEE, 2020).

Grill, A. et al. Temperature dependent mismatch and variability in a Cryo-CMOS array with 30k transistors. In Proc. 2022 IEEE International Reliability Physics Symposium (IRPS) https://doi.org/10.1109/IRPS48227.2022.9764594 (IEEE, 2022).

Ghibaudo, G., Casse, M., Serra di Santa Maria, F., Theodorou, C. & Balestra, F. Modeling of self-heating effect in FDSOI and bulk MOSFETs operated in deep cryogenic conditions. Solid. State Electron. 192, 108265 (2022).

Asheghi, M., Kurabayashi, K., Kasnavi, R. & Goodson, K. E. Thermal conduction in doped single-crystal silicon films. J. Appl. Phys. 91, 5079–5088 (2002).

Triantopoulos, K. et al. Self-heating effect in FDSOI transistors down to cryogenic operation at 4.2 K. IEEE Trans. Electron. Devices 66, 3498–3505 (2019).

Scholten, A. J. et al. Experimental assessment of self-heating in SOI FinFETs. In Proc. 2009 IEEE International Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2009.5424362 (IEEE, 2009).

Tenbroek, B. M., Lee, M. S. L., Redman-White, W., Bunyan, J. T. & Uren, M. J. Self-heating effects in SOI MOSFETs and their measurement by small signal conductance techniques. IEEE Trans. Electron. Devices 43, 2240–2248 (1996).

Nyssens, L. et al. Self-heating in FDSOI UTBB MOSFETs at cryogenic temperatures and its effect on analog figures of merit. IEEE J. Electron. Devices Soc. 8, 789–796 (2020).

Han, H.-C. et al. Cryogenic RF characterization and simple modeling of a 22 nm FDSOI technology. In Proc. ESSDERC 2022 - IEEE 52nd European Solid-State Device Research Conference (ESSDERC) 269–272 (IEEE, 2022).

Krantz, P. et al. A quantum engineer’s guide to superconducting qubits. Appl. Phys. Rev. 6, 021318 (2019).

Yoneda, J. et al. A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%. Nat. Nanotechnol. 13, 102–106 (2018).

Gong, J., Chen, Y., Sebastiano, F., Charbon, E. & Babaie, M. 19.3 A 200dB FoM 4-to-5GHz cryogenic oscillator with an automatic common-mode resonance calibration for quantum computing applications. In Proc. 2020 IEEE International Solid-State Circuits Conference (ISSCC) 308–310 (IEEE, 2020).

Ghibaudo, G., Roux, O., Nguyen-Duc, C., Balestra, F. & Brini, J. Improved analysis of low frequency noise in field-effect MOS transistors. Phys. Status Solidi A 124, 571–581 (1991).

Kiene, G., Sreenivasulu, A. G., Overwater, R. W. J., Babaie, M. & Sebastiano, F. Cryogenic comparator characterization and modeling for a Cryo-CMOS 7b 1-GSa/s SAR ADC. In Proc. ESSCIRC 2022 - IEEE 48th European Solid State Circuits Conference (ESSCIRC) 53–56 (IEEE, 2022).

Kiene, G., İlik, S., Mastrodomenico, L., Babaie, M. & Sebastiano, F. Cryogenic characterization of low-frequency noise in 40-nm CMOS. IEEE J. Electron. Devices Soc. 12, 573–580 (2024).

Inaba, T. et al. Determining the low-frequency noise source in cryogenic operation of short-channel bulk MOSFETs. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185298 (IEEE, 2023).

Michl, J. et al. Evidence of tunneling driven random telegraph noise in cryo-CMOS. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 31.3.1–31.3.4 (IEEE, 2021).

Asanovski, R. et al. Understanding the excess 1 / f noise in MOSFETs at cryogenic temperatures. IEEE Trans. Electron. Devices 70, 2135–2141 (2023).

Cardoso Paz, B. et al. Performance and low-frequency noise of 22-nm FDSOI down to 4.2 K for cryogenic applications. IEEE Trans. Electron. Devices 67, 4563–4567 (2020).

Chen, X., Elgabra, H., Chen, C.-H., Baugh, J. & Wei, L. Estimation of MOSFET channel noise and noise performance of CMOS LNAs at cryogenic temperatures. In Proc. 2021 IEEE International Symposium on Circuits and Systems (ISCAS) https://doi.org/10.1109/ISCAS51556.2021.9401136 (IEEE, 2021).

Richstein, B. et al. Interface engineering for steep slope cryogenic MOSFETs. IEEE Electron. Device Lett. 43, 2149–2152 (2022). This paper shows the importance of interface engineering by using an ultra-thin SiN layer that improves the SS at 4 K.

Han, Y. et al. Improved performance of FDSOI FETs at cryogenic temperatures by optimizing ion implantation into silicide. Solid-State Electron. 208, 108733 (2023). This paper demonstrates that the source/drain engineering using IIS can improve the cryogenic MOSFETs.

Han, Y. et al. High performance 5 nm Si nanowire FETs with a record small SS = 2.3 mV/dec and high transconductance at 5.5 K enabled by dopant segregated silicide source/drain. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185373 (IEEE, 2023). This paper illustrates that GAA silicon nanowire transistors fabricated with IIS technology can achieve a very steep SS of 2.3 mV dec–1 at 5.5 K.

Han, Y. et al. Steep switching Si nanowire p-FETs with dopant segregated silicide source/drain at cryogenic temperature. IEEE Electron. Device Lett. 43, 1187–1190 (2022).

Knoll, L. et al. Demonstration of improved transient response of inverters with steep slope strained Si NW TFETs by reduction of TAT with pulsed I-V and NW scaling. In Proc. 2013 IEEE International Electron Devices Meeting 4.4.1–4.4.4 (IEEE, 2013).

Luong, G. V. et al. Complementary strained Si GAA nanowire TFET inverter with suppressed ambipolarity. IEEE Electron. Device Lett. 37, 950–953 (2016).

Feste, S. F. et al. Formation of steep, low Schottky-barrier contacts by dopant segregation during nickel silicidation. J. Appl. Phys. 107, 044510 (2010).

Knoll, L. et al. Ultrathin Ni silicides with low contact resistance on strained and unstrained silicon. IEEE Electron. Device Lett. 31, 350–352 (2010).

Houssa, M. et al. Trap-assisted tunneling in high permittivity gate dielectric stacks. J. Appl. Phys. 87, 8615–8620 (2000).

Fischetti, M. V., Neumayer, D. A. & Cartier, E. A. Effective electron mobility in Si inversion layers in metal-oxide-semiconductor systems with a high-k insulator: the role of remote phonon scattering. J. Appl. Phys. 90, 4587–4608 (2001).

Galy, P. et al. Cryogenic temperature characterization of a 28-nm FD-SOI dedicated structure for advanced CMOS and quantum technologies co-integration. IEEE J. Electron. Devices Soc. 6, 594–600 (2018).

Han, H.-C., Zhao, Z., Lehmann, S., Charbon, E. & Enz, C. Novel aproach to FDSOI threshold voltage model validated at cryogenic temperatures. IEEE Access. 11, 56951–56957 (2023).

Mamun, F. A., Vasileska, D. & Sanchez Esqueda, I. Impact of back-gate biasing on the transport properties of 22 nm FD-SOI MOSFETs at cryogenic temperatures. IEEE Trans. Electron. Devices 69, 5417–5423 (2022).

Gámiz, F. & Fischetti, M. V. Remote Coulomb scattering in metal-oxide-semiconductor field effect transistors: screening by electrons in the gate. Appl. Phys. Lett. 83, 4848–4850 (2003).

Rudenko, T. et al. Experimental study of transconductance and mobility behaviors in ultra-thin SOI MOSFETs with standard and thin buried oxides. Solid State Electron. 54, 164–170 (2010).

Overwater, R. W. J., Babaie, M. & Sebastiano, F. Cryogenic-aware forward body biasing in bulk CMOS. IEEE Electron. Device Lett. 45, 152–155 (2024).

Bao, R. et al. High performance nanosheet technology optimized for 77 K. In Proc. 2023 International Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM45741.2023.10413745 (IEEE, 2023).

Liu, M. et al. Vertical GeSn nanowire MOSFETs for CMOS beyond silicon. Commun. Eng. 2, 7 (2023).

Geng, P. et al. A novel theoretical model for the temperature dependence of band gap energy in semiconductors. J. Phys. Appl. Phys. 50, 40LT02 (2017).

Oka, H. et al. Origin of low-frequency noise in Si n-MOSFET at cryogenic temperatures: the effect of interface quality. IEEE Access. 11, 121567–121573 (2023).

Theodorou, C. G. et al. Impact of front-back gate coupling on low frequency noise in 28 nm FDSOI MOSFETs. In Proc. 2012 Proc. European Solid-State Device Research Conference (ESSDERC) 334–337 (IEEE, 2012).

Das, K. & Lehmann, T. Effect of deep cryogenic temperature on silicon-on-insulator CMOS mismatch: a circuit designer’s perspective. Cryogenics 62, 84–93 (2014).

Saligram, R. et al. Power performance analysis of digital standard cells for 28 nm bulk CMOS at cryogenic temperature using BSIM models. IEEE J. Explor. Solid-State Comput. Devices Circuits 7, 193–200 (2021).

Saligram, R., Prasad, D., Pietromonaco, D., Raychowdhury, A. & Cline, B. A 64-bit arm CPU at cryogenic temperatures: design technology co-optimization for power and performance. In Proc. 2021 IEEE Custom Integrated Circuits Conference (CICC) https://doi.org/10.1109/CICC51472.2021.9431559 (IEEE, 2021).

Chiang, H.-L. et al. Design technology co-optimization for cold CMOS benefits in advanced technologies. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 13.2.1–13.2.4 (IEEE, 2021).

Chakraborty, W., Ni, K., Smith, J., Raychowdhury, A. & Datta, S. An empirically validated virtual source fet model for deeply scaled cool CMOS. In Proc. 2019 IEEE International Electron Devices Meeting (IEDM) 39.4.1–39.4.4 (IEEE, 2019).

Gaidhane, A. D. et al. Design exploration of 14 nm FinFET for energy-efficient cryogenic computing. IEEE J. Explor. Solid-State Comput. Devices Circuits 9, 108–115 (2023).

Prasad, D. et al. Cryo-computing for infrastructure applications: a technology-to-microarchitecture co-optimization study. In Proc. 2022 International Electron Devices Meeting (IEDM) 23.5.1–23.5.4 (IEEE, 2022).

Chiang, H. L. et al. Cold MRAM as a density booster for embedded NVM in advanced technology. In Proc. 2021 Symposium on VLSI Technology (IEEE, 2021).

Hur, J. et al. Characterizing ferroelectric properties of Hf0.5Zr0.5O2 from deep-cryogenic temperature (4 K) to 400 K. IEEE J. Explor. Solid State Comput. Devices Circuits 7, 168–174 (2021).

Wang, Z. et al. Cryogenic characterization of a ferroelectric field-effect-transistor. Appl. Phys. Lett. 116, 042902 (2020).

Garzon, E., Greenblatt, Y., Harel, O., Lanuzza, M. & Teman, A. Gain-cell embedded DRAM under cryogenic operation—a first study. IEEE Trans. Very Large Scale Integr. VLSI Syst. 29, 1319–1324 (2021).

Saligram, R., Datta, S. & Raychowdhury, A. CryoMem: a 4–300-K 1.3-GHz hybrid 2T-gain-cell-based eDRAM macro in 28-nm logic process for cryogenic applications. IEEE Solid State Circuits Lett. 4, 194–197 (2021).

Sanuki, T. et al. Cryogenic operation of 3-D flash memory for storage performance improvement and bit cost scaling. IEEE J. Explor. Solid-State Comput. Devices Circuits 7, 159–167 (2021).

Hao, Z. et al. Cryogenic HfOx-based resistive memory with a thermal enhancement capping layer. IEEE Electron. Device Lett. 42, 1276–1279 (2021).

Icking, E. et al. Ultrasteep slope cryogenic FETs based on bilayer graphene. Nano Lett. https://doi.org/10.1021/acs.nanolett.4c02463 (2024).

Alam, S., Hossain, M. S., Srinivasa, S. R. & Aziz, A. Cryogenic memory technologies. Nat. Electron. 6, 185–198 (2023).

Hironaka, Y. et al. Demonstration of a single-flux-quantum microprocessor operating with Josephson–CMOS hybrid memory. IEEE Trans. Appl. Supercon. 30, 1301206 (2020).

Suzuki, H., Inoue, A., Imamura, T. & Hasuo, S. A Josephson driver to interface Josephson junctions to semiconductor transistors. In Proc. Technical Digest., International Electron Devices Meeting (IEDM) 290–293 (IEEE, 1988).

Boter, J. M. et al. Spiderweb array: a sparse spin-qubit array. Phys. Rev. Appl. 18, 024053 (2022).

Li, R. et al. A crossbar network for silicon quantum dot qubits. Sci. Adv. 4, eaar3960 (2018).

Borsoi, F. et al. Shared control of a 16 semiconductor quantum dot crossbar array. Nat. Nanotechnol. 19, 21–27 (2024).

Künne, M. et al. The SpinBus architecture for scaling spin qubits with electron shuttling. Nat. Commun. 15, 4977 (2024).

Zwerver, A. M. J. et al. Shuttling an electron spin through a silicon quantum dot array. PRX Quantum 4, 030303 (2023).

Langrock, V. et al. Blueprint of a scalable spin qubit shuttle device for coherent mid-range qubit transfer in disordered Si/SiGe/SiO2. PRX Quantum 4, 020305 (2023).

Noiri, A. et al. A shuttling-based two-qubit logic gate for linking distant silicon quantum processors. Nat. Commun. 13, 5740 (2022).

Xue, R. et al. Si/SiGe QuBus for single electron information-processing devices with memory and micron-scale connectivity function. Nat. Commun. 15, 2296 (2024).

Liu, Y. et al. Cryogenic characteristics of multinanoscales field-effect transistors. IEEE Trans. Electron. Devices 68, 456–463 (2021).

Serra di Santa Maria, F. et al. Lambert-W function-based parameter extraction for FDSOI MOSFETs down to deep cryogenic temperatures. Solid-State Electron. 186, 108175 (2021).

Han, Y. et al. Cryogenic characteristics of UTBB SOI Schottky-barrier MOSFETs. Solid State Electron. 194, 108351 (2022).

Artanov, A. A. et al. Self-heating effect in a 65 nm MOSFET at cryogenic temperatures. IEEE Trans. Electron. Devices 69, 900–904 (2022).

Hart, P. A. T., Babaie, M., Vladimirescu, A. & Sebastiano, F. Characterization and modeling of self-heating in nanometer bulk-CMOS at cryogenic temperatures. IEEE J. Electron. Devices Soc. 9, 891–901 (2021).

Duan, G. X. et al. Effects of negative-bias-temperature-instability on low-frequency noise in SiGe pMOSFETs. IEEE Trans. Device Mater. Reliab. 16, 541–548 (2016).

Zhao, Q.-T. et al. High storage and energy efficient memory for cryogenic computing. Preprint at https://doi.org/10.21203/rs.3.rs-3300928/v1 (2023).

Van Dijk, J. P. G. et al. Impact of classical control electronics on qubit fidelity. Phys. Rev. Appl. 12, 044054 (2019).

Hornibrook, J. M. et al. Cryogenic control architecture for large-scale quantum computing. Phys. Rev. Appl. 3, 024010 (2015).

Geck, L., Kruth, A., Bluhm, H., Waasen, S. V. & Heinen, S. Control electronics for semiconductor spin qubits. Quantum Sci. Technol. 5, 015004 (2020).

Schreckenberg, L. et al. SiGe qubit biasing with a cryogenic CMOS DAC at mK temperature. In Proc. ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ESSCIRC) 161–164 (IEEE, 2023).

Hollmann, A. et al. 30 GHz-voltage controlled oscillator operating at 4 K. Rev. Sci. Instrum. 89, 114701 (2018).

Curry, M. J. et al. Single-shot readout performance of two heterojunction-bipolar-transistor amplification circuits at millikelvin temperatures. Sci. Rep. 9, 16976 (2019).

Björk, M. T., Schmid, H., Knoch, J., Riel, H. & Riess, W. Donor deactivation in silicon nanostructures. Nat. Nanotechnol. 4, 103–107 (2009).

Smit, G. D. J., Rogge, S., Caro, J. & Klapwijk, T. M. Gate-induced ionization of single dopant atoms. Phys. Rev. B 68, 193302 (2003).

Author information

Authors and Affiliations

Contributions

Q.-T.Z., Y.H., H.-C.H., L.R.S., T.-E.L., H.-L.C., C.S., S.T. and J.K. researched data for the article. Q.-T.Z., Y.H., H.-C.H., L.R.S., T.-E.L., H.-L.C., S.T. and J.K. contributed to the discussions of the content and the writing of the manuscript. All authors reviewed/edited the manuscript before submission.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Reviews Electrical Engineering thanks Fabio Sebastiano and the other, anonymous, reviewers for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Glossary

- Automatic placement and routing

-

The process of physically implementing a gate-level netlist by placing standard cells and auto-routing them based on inferred connections.

- Hyperfine contact interaction

-

The interaction between the magnetic moments of the electron and the nucleus due to the electron’s non-zero probability density at the position of the nucleus.

- Silicidation

-

A process in complementary metal oxide semiconductor technology to form metal silicide at the source/drain by solid-state reaction of a metal layer with silicon at high temperature.

- Static timing analysis

-

A method for validating a design’s timing performance by analysing all possible paths for timing violations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Zhao, QT., Han, Y., Han, HC. et al. Ultra-low-power cryogenic complementary metal oxide semiconductor technology. Nat Rev Electr Eng 2, 277–290 (2025). https://doi.org/10.1038/s44287-025-00157-7

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s44287-025-00157-7