Abstract

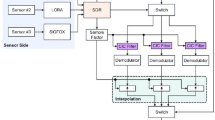

Most communication is now done in the digital realm due to the advancement of more potent and compact techniques for creating digital circuitry on silicon chips. This work introduces an efficient approach for developing a reconfigurable multiplier-less decimation filter, which is appropriate for multi-standard wireless applications. The proposed work utilizes cascaded integrator comb (CIC), polyphase and half-band filters, designed with the assistance of high-speed adders. Endeavoring to enhance passband and stopband performance, a unique polynomial function is used to design the filter, which shows better results than the existing work. Ultimately, these filter structures are integrated with a control switch to create the proposed decimation filter, making it well-suited for multi-standard wireless applications, including IEEE 802.11g/n/ac/ax. The decimation filter has been built on Xilinx Kintex 7 Field Programmable Gate Array, and utilization of LUTs, power consumption and delay are examined. Based on the attained results, the proposed decimation filter with HCA shows a 46.38% minimization in LUTs, a 36.93% reduction in path delay and an 85.39% drop in power consumption than the previous work. Moreover, the input and output spectrum of all four IEEE 802.11 applications are analyzed using MATLAB.

Similar content being viewed by others

Data availability

The data supporting the findings of this study are available from the corresponding author upon reasonable request.

References

Ghazel, A., Naviner, L. & Grati, K. On design and implementation of a decimation filter for multistandard wireless transceivers. IEEE Trans. Wirel. Commun. 1(4), 558–562. https://doi.org/10.1109/TWC.2002.805093 (2002).

Gao, Y., Jia, L. & Tenhunen, H. A fifth-order comb decimation filter for multi-standard transceiver applications. In 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland vol. 3, 89–92 (2000). https://doi.org/10.1109/ISCAS.2000.856003

Datta, D. & Dutta, H. S. CIC decimation filter implementation on FPGA. J. Inst. Eng. India Ser. B 104, 85–90. https://doi.org/10.1007/s40031-022-00840-5 (2023).

Datta, D. & Dutta, H. S. Hardware optimized digital down converter for multi-standard radio receiver. Analog Integr. Circuits Signal Process. 118, 567–575. https://doi.org/10.1007/s10470-023-02227-y (2024).

Datta, D., Dutta, H. S. & Naskar, M. K. Heuristic analysis of digital down converter design for software-defined radio applications. Circuits Syst. Signal Process. 44, 684–700. https://doi.org/10.1007/s00034-024-02874-0 (2025).

Sikka, P., Asati, A. R. & Shekhar, C. Power-and area-optimized high-level synthesis implementation of a digital down converter for software-defined radio applications. Circuits Syst. Signal Process. 40, 2883–2894. https://doi.org/10.1007/s00034-020-01601-9 (2021).

Esposito, D., De Caro, D. & Strollo, A. G. M. Variable latency speculative parallel prefix adders for unsigned and signed operands. IEEE Trans. Circuits Syst. I Regul. Pap. 63(8), 1200–1209. https://doi.org/10.1109/TCSI.2016.2564699 (2016).

Abinaya, A. & Maheswari, M. Heuristic analysis of multiplierless desensitized half-band decimation filter for wireless applications. J. Circuits Syst. Comput. 31(14), 2250246-1–2250246-27. https://doi.org/10.1142/S0218126622502462 (2022).

Abinaya, A., Maheswari, M. & Jebaraj, J. R. Pragmatic analysis of polyphase CIC decimation filter for next generation wireless applications. Multiscale Multidiscip. Model. Exp. Des. 8, 20. https://doi.org/10.1007/s41939-024-00636-8 (2025).

Li, D., Chen, Z., Liu, X., Shen, Z., Xing, Y. & Wan, P. Digital decimation filter design for a 3rd-order sigma-delta modulator with achieving 129 dB SNR. In 2021 IEEE 15th International Conference on Anti-counterfeiting, Security, and Identification (ASID), Xiamen, China 187–190 (2021). https://doi.org/10.1109/ASID52932.2021.9651718

Datta, D. & Dutta, H. S. High efficient polyphase digital down converter on FPGA. Circuits Syst. Signal Process. 40, 5787–5798. https://doi.org/10.1007/s00034-021-01749-y (2021).

Niveditha, V. R. et al. High speed low area decimation filter for hearing aid application. Int. J. Speech Technol. 25, 633–639. https://doi.org/10.1007/s10772-021-09857-5 (2022).

Datta, D., Mitra, P. & Dutta, H. S. FPGA implementation of high performance digital down converter for software defined radio. Microsyst. Technol. 28, 533–542. https://doi.org/10.1007/s00542-019-04579-w (2022).

Bellalta, B., Bononi, L., Bruno, R. & Kasslerd, A. Next Generation IEEE 802.11 Wireless Local Area Networks: Current Status, Future Directions and Open Challenges’, Computer Communications, vol. 75, pp. 1–25 (Elsevier, 2016). https://doi.org/10.1016/j.comcom.2015.10.007

Pahlavan, K. & Krishnamurthy, P. Evolution and impact of Wi-Fi technology and applications: A historical perspective. Int. J. Wirel. Inf. Netw. 28, 3–19. https://doi.org/10.1007/s10776-020-00501-8 (2021).

Hassan, E. E. & Ragheb, H. A. Design of narrow band decimation filter for sigma delta modulator. Arab. J. Sci. Eng. 36, 1287–1296. https://doi.org/10.1007/s13369-011-0128-7 (2011).

Tong, Y., Li, W. & Kang, F. A design of digital high multiple decimation filter in intermediate frequency domain. In Advanced Hybrid Information Processing. ADHIP 2021. Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering Vol. 417 (eds Liu, S. & Ma, X.) (Springer, 2022). https://doi.org/10.1007/978-3-030-94554-1_17.

Dolecek, G. J. Design of decimation filter with improved magnitude characteristic and low complexity. IEEE Access 10, 63455–63465. https://doi.org/10.1109/ACCESS.2022.3183100 (2022).

Miriyala, M. & Harigovindan, V. P. Improving aggregate utility and service differentiation of IEEE 802.11ah restricted access window mechanism using ANFIS. Iran. J. Sci. Technol. Trans. Electr. Eng. 45, 1165–1177. https://doi.org/10.1007/s40998-021-00422-z (2021).

Srivastava, A. K., Raj, K. & Kumar, A. Design and analysis of CIC decimation filter using redundant number system. In VLSI, Communication and Signal Processing. VCAS 2022. Lecture Notes in Electrical Engineering Vol. 1024 (eds Nagaria, R. K. et al.) (Springer, 2023). https://doi.org/10.1007/978-981-99-0973-5_56.

Datta, D. & Dutta, H. S. High efficient half-band decimation filter on FPGA. Trans. Indian Natl. Acad. Eng. 8, 317–323. https://doi.org/10.1007/s41403-023-00392-0 (2023).

Molnar, G., Dudarin, A. & Vucic, M. Design and multiplierless realization of maximally flat sharpened-CIC compensators. IEEE Trans. Circuits Syst. II Express Briefs 65(1), 51–55. https://doi.org/10.1109/TCSII.2017.2700081 (2018).

Sinha, D. & Kumar, S. CIC filter for sample rate conversion in software defined radio. In 2016 World Conference on Futuristic Trends in Research and Innovation for Social Welfare (Startup Conclave), Coimbatore, India 1–5 (2016). https://doi.org/10.1109/STARTUP.2016.7583972

Aggarwal, S. & Meher, P. K. Enhanced sharpening of CIC decimation filters, implementation and applications. Circuits Syst. Signal Process. 41, 4581–4603. https://doi.org/10.1007/s00034-022-01993-w (2022).

Teymourzadeh, R. & Othman, M. VLSI implementation of cascaded integrator comb filters for DSP applications (2018). https://arxiv.org/pdf/1808.0936

Abinaya, A., Maheswari, M. & Alqahtani, A. S. Heuristic analysis of CIC filter design for next-generation wireless applications. Arab. J. Sci. Eng. 46, 1257–1268. https://doi.org/10.1007/s13369-020-05016-1 (2021).

Mehrnia, A., Dai, M. & Willson, A. N. Efficient halfband FIR filter structures for RF and IF data converters. IEEE Trans. Circuits Syst. II Express Briefs 63(1), 64–68. https://doi.org/10.1109/TCSII.2015.2468932 (2016).

Huang, X. & Wang, Z. Novel approach for the design of half-band filter. In Information Computing and Applications. ICICA 2010. Lecture Notes in Computer Science Vol. 6377 (eds Zhu, R. et al.) (Springer, 2010). https://doi.org/10.1007/978-3-642-16167-4_74.

Mehrnia, A. & Willson, A. N. FIR filter design via extended optimal factoring. IEEE Trans. Signal Process. 64(4), 1061–1075. https://doi.org/10.1109/TSP.2015.2494846 (2016).

Willson, A. N. Desensitized half-band filters. IEEE Trans. Circuits Syst. I Regul. Pap. 57(1), 152–167. https://doi.org/10.1109/TCSI.2009.2018941 (2010).

Gustafsson, O. A difference based adder graph heuristic for multiple constant multiplication problems. In 2007 IEEE International Symposium on Circuits and Systems (ISCAS), New Orleans, LA, USA 1097–1100 (2007). https://doi.org/10.1109/ISCAS.2007.378201

Harris, F. J. Reduce energy requirements by coupling a poly-phase pre-filter and cic filter in high-performance Sigma-Delta A/D converters. In 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia 1600–1603 (2014). https://doi.org/10.1109/ISCAS.2014.6865456

Ramon, H. et al. Efficient parallelization of polyphase arbitrary resampling FIR filters for high-speed applications. J. Sign. Process. Syst. 90, 295–303. https://doi.org/10.1007/s11265-017-1235-9 (2018).

Funding

This research is supported by Multimedia University (MMU) through its Article Page Charge (APC) Sponsorship Scheme.

Author information

Authors and Affiliations

Contributions

A. Abinaya, M. Maheswari, Arfat Ahmad Khan, S. Dheenathayalan, Shahid Kamal, Fasee Ullah, and Karthikeyan N. jointly contributed to the conception and design of the study. A. Abinaya and M. Maheswari carried out the methodology development, data collection, and preliminary analysis. Arfat Ahmad Khan provided overall supervision, contributed to the formal analysis, and guided the theoretical framework and interpretation of results. S. Dheenathayalan and Shahid Kamal assisted with experimentation, validation, and result visualization. Fasee Ullah and Karthikeyan N. contributed to software implementation, data curation, and performance evaluation. All authors participated in drafting the manuscript, critically revising it for important intellectual content, and approving the final version for publication.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Abinaya, A., Maheswari, M., Khan, A.A. et al. Heuristic optimization of multiplierless decimation filter for multi-standard wireless applications. Sci Rep (2026). https://doi.org/10.1038/s41598-026-48104-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-026-48104-2