Abstract

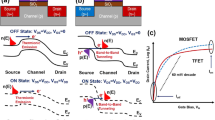

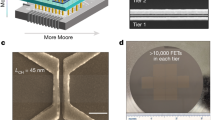

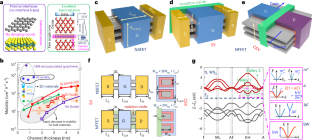

Atomically thin two-dimensional (2D) semiconductors—particularly transition metal dichalcogenides—are potential channel materials for post-silicon complementary metal–oxide–semiconductor (CMOS) field-effect transistors. However, their application in CMOS technology will require implementation in three-dimensional (3D) transistors. Here we report a framework for designing scaled 3D transistors using 2D semiconductors. Our approach is based on non-equilibrium Green’s function quantum transport simulations that incorporate the effects of non-ideal Schottky contacts and inclusive capacitance calculations, with material inputs derived from density functional theory simulations. A comparative performance analysis of different 3D transistors (2D and silicon based) and channel thicknesses is carried out for both low-standby-power and high-performance applications. This suggests that trilayer tungsten disulfide is the most promising material, offering an improvement in energy–delay product of over 55% compared with silicon counterparts, potentially extending CMOS scaling down to a few nanometres. We also show that 2D semiconductors could be uniquely engineered to create 2D nanoplate field-effect transistors that offer nearly tenfold improvement in integration density and drive current over both 2D- and silicon-based 3D field-effect transistors with similar footprints.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Ajayan, P., Kim, P. & Banerjee, K. Two-dimensional van der Waals materials. Phys. Today 69, 38–44 (2016).

Pal, A. et al. Quantum‐engineered devices based on 2D materials for next‐generation information processing and storage. Adv. Mater. 35, 2109894 (2023).

Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs—projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices 62, 3459–3469 (2015).

Yeh, C. H., Cao, W., Pal, A., Parto, K. & Banerjee, K. Area-selective-CVD technology enabled top-gated and scalable 2D-heterojunction transistors with dynamically tunable Schottky barrier. In 2019 IEEE International Electron Devices Meeting 23.4.1–23.4.4 (IEEE, 2019).

Cao, W., Liu, W. & Banerjee, K. Prospects of ultra-thin nanowire gated 2D-FETs for next-generation CMOS technology. In 2016 IEEE International Electron Devices Meeting 14.7.1–14.7.4 (IEEE, 2016).

Kang, J. et al. Computational study of gate-induced drain leakage in 2D-semiconductor field-effect transistors. In 2017 IEEE International Electron Devices Meeting 31.2.1–31.2.4 (IEEE, 2017).

Pal, A., Cao, W., Kang, J. & Banerjee, K. How to derive the highest mobility from 2D FETs—a first-principle study. In 2017 IEEE International Electron Devices Meeting 31.3.1–31.3.4 (IEEE, 2017).

Penumatcha, A. et al. High mobility TMD NMOS and PMOS transistors and GAA architecture for ultimate CMOS scaling. In 2023 International Electron Devices Meeting 1.4.1–1.4.4 (IEEE, 2023).

Chung, Y.-Y., et al. First demonstration of GAA monolayer-MoS2 nanosheet nFET with 410μA μm ID 1V VD at 40nm gate length. In 2022 International Electron Devices Meeting (IEDM) 34.5.1–34.5.4 (IEEE, 2022).

Dorow, C. J. et al. Gate length scaling beyond Si: mono-layer 2D channel FETs robust to short channel effects. In 2022 International Electron Devices Meeting 7.5.1–7.5.4 (IEEE, 2022).

Pal, A. et al. Two-dimensional materials enabled next-generation low-energy compute and connectivity. MRS Bull. 46, 1211–1228 (2021).

Cao, W. et al. 2-D layered materials for next-generation electronics: opportunities and challenges. IEEE Trans. Electron Devices 65, 4109–4121 (2018).

Wang, J., Polizzi, E., Ghosh, A., Datta, S. & Lundstrom, M. Theoretical investigation of surface roughness scattering in silicon nanowire transistors. Appl. Phys. Lett. 87, 043101 (2015).

Ng, H. K. et al. Improving carrier mobility in two-dimensional semiconductors with rippled materials. Nat. Electron. 5, 489–496 (2022).

Kumar, A. et al. Strain engineering in 2D FETs: physics, status, and prospects. J. Appl. Phys. 136, 090901 (2024).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Yu, Z. et al. Towards intrinsic charge transport in monolayer molybdenum disulfide by defect and interface engineering. Nat. Commun. 5, 5290 (2014).

Liu, T. et al. Crested two-dimensional transistors. Nat. Nanotechnol. 14, 223–226 (2019).

Mertens, H. et al. Vertically stacked gate-all-around Si nanowire transistors: key process optimizations and ring oscillator demonstration. In 2017 IEEE International Electron Devices Meeting 37.4.1–37.4.4 (IEEE, 2017).

Weckx, P. et al. Novel forksheet device architecture as ultimate logic scaling device towards 2nm. In 2019 IEEE International Electron Devices Meeting 36.5.1–36.5.4 (IEEE, 2019).

Datta, S. Nanoscale device modeling: the Green’s function method. Superlattices Microstruct. 28, 253–278 (2000).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Kang, J., Liu, W., Sarkar, D., Jena, D. & Banerjee, K. Computational study of metal contacts to monolayer transition-metal dichalcogenide semiconductors. Phys. Rev. 4, 031005 (2014).

Pal, A. et al. Characterization and closed-form modeling of edge/top/hybrid metal-2D semiconductor contacts. In 2022 International Electron Devices Meeting 28.5.1–28.5.4 (IEEE, 2022).

International Roadmap for Devices and Systems 2023 Edition (IRDS, 2023); https://irds.ieee.org/editions/2023

Dorow, C. et al. Exploring manufacturability of novel 2D channel materials: 300 mm wafer-scale 2D NMOS & PMOS using MoS2, WS2 & WSe2. In 2023 International Electron Devices Meeting (IEDM) 1.4.1–1.4.4 (IEEE, 2023).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Silvestri, L. et al. Hierarchical modeling for TCAD simulation of short-channel 2D material-based FETs. Solid-State Electron. 200, 108533 (2023).

Sentaurus Device QTX User Guide v.T-2022.03 (Synopsys, 2021).

Atomistix Toolkit v.2022.03 (Synopsys QuantumWise, 2022).

Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865–3868 (1996).

Cao, W., Kang, J., Liu, W. & Banerjee, K. A compact current–voltage model for 2D semiconductor based field-effect transistors considering interface traps, mobility degradation, and inefficient doping effect. IEEE Trans. Electron Devices 61, 4282–4290 (2014).

Zhang, F., Lee, C.-H., Robinson, J. A. & Appenzeller, J. Exploration of channel width scaling and edge states in transition metal dichalcogenides. Nano Res. 11, 1768–1774 (2018).

Cui, Y., Zhong, Z., Wang, D., Wang, W. U. & Lieber, C. M. High performance silicon nanowire field effect transistors. Nano Lett. 3, 149–152 (2003).

Gilardi, C. et al. Barrier booster for remote extension doping and its DTCO for 1D and 2D FETs. In IEEE International Electron Devices Meeting 1.4.1–1.4.4 (IEEE, 2023).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

O’Brien, K. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In 2021 IEEE International Electron Devices Meeting 7.1.1–7.1.4 (IEEE, 2021).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In 2021 IEEE International Electron Devices Meeting 7.2.1–7.2.4 (IEEE, 2021).

Jiang, J., Parto, K., Cao, W. & Banerjee, K. Ultimate monolithic-3D integration with 2D materials: rationale, prospects, and challenges. IEEE J. Electron Devices Soc. 7, 878–887 (2019).

Parto, K., Pal, A., Xie, X., Cao, W. & Banerjee, K. Interfacial thermal conductivity of 2D layered materials: an atomistic approach. In 2018 IEEE International Electron Devices Meeting 24.1.1–24.1.4 (IEEE, 2018).

Sahoo, S., Gaur, A. P. S., Ahmadi, M., Guinel, M. J.-F. & Katiyar, R. S. Temperature-dependent Raman studies and thermal conductivity of few-layer MoS2. J. Phys. Chem. C 117, 9042–9047 (2013).

Balandin, A. A. Thermal properties of graphene and nanostructured carbon materials. Nat. Mater. 10, 569–581 (2011).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Wu, X. et al. Dual gate synthetic MoS2 MOSFETs with 4.56 μF/cm2 channel capacitance, 320 μS/μm Gm and 420 μA/μm Id at 1V Vd/100nm Lg. In 2021 International Electron Devices Meeting 7.4.1–7.4.4 (IEEE, 2021).

Lin, Y. C. et al. Dielectric material technologies for 2-D semiconductor transistor scaling. IEEE Trans. Electron Devices 70, 1454–1473 (2022).

Radosavljević, M. et al. Demonstration of a stacked CMOS inverter at 60nm gate pitch with power via and direct backside device contacts. In 2023 International Electron Devices Meeting 1–4 (IEEE, 2023).

Zhang, Y. et al. Recent progress in CVD growth of 2D transition metal dichalcogenides and related heterostructures. Adv. Mater. 31, 1901694 (2019).

Kaasbjerg, K., Thygesen, K. S. & Jacobsen, K. W. Phonon-limited mobility in n-type single-layer MoS2 from first principles. Phys. Rev. B 85, 115317 (2012).

Acknowledgements

The research outlined in this Article and all contributing authors from the Nanoelectronics Research Lab at the University of California, Santa Barbara were supported by an EAGER Award (grant no. 2332341) and a CMOS + X Award (grant no. 2424696), both from the National Science Foundation, as well as by the Army Research Office (grant no. W911NF1810366).

Author information

Authors and Affiliations

Contributions

K.B. initiated the research, conceptualized the NPFET architecture (with input from A.P.) and supervised the work. A.P. carried out the design and analysis of the various device architectures, with simulation and analysis support from T.C. and W.C., and methodology support from J.J. A.P., W.C. and K.B reviewed the results and drew the conclusions. A.P. and K.B. wrote the paper with input from all other authors.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Shunri Oda and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary information

Supplementary Figs. 1–7, Sections 1–9 and Table 1.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Pal, A., Chavan, T., Jabbour, J. et al. Three-dimensional transistors with two-dimensional semiconductors for future CMOS scaling. Nat Electron 7, 1147–1157 (2024). https://doi.org/10.1038/s41928-024-01289-8

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-024-01289-8

This article is cited by

-

Indium selenides for next-generation low-power computing devices

Nature Reviews Electrical Engineering (2026)

-

Gate structuring on n-type bilayer MoS2 field-effect transistors for ultrahigh current density

Nature Materials (2026)

-

Electrostatic-repulsion-based transfer of van der Waals materials

Nature (2025)

-

Seamless in two dimensions: prospects of lateral heterostructures from integration to quantum devices

npj 2D Materials and Applications (2025)

-

High-κ dielectric van der Waals integration on 2D semiconductors for three-dimensional complementary logic systems

Nature Communications (2025)