Abstract

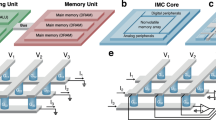

Analogue in-memory computing (AIMC) is an emerging computational approach that executes operations directly within memory arrays, reducing the need for data transfer between memory and processing units. AIMC-based accelerators are, in particular, being explored for deep neural network (DNN) inference, with the key element of such accelerators being the AIMC tile, which can be implemented using various conventional volatile charge-based and emerging non-volatile resistive memory (memristive) technologies. Here we examine the design of non-volatile memristive AIMC tiles for DNN accelerators. We explore the different components of a memristive AIMC tile and the range of mapping techniques for encoding signed multibit weights and inputs. We provide an analysis of the efficiency and accuracy of output encoding schemes, including various analogue-to-digital converter approaches. We also provide a comparative analysis of the different memory technologies being explored and projections for how technology scaling may impact key design components.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper are available from the corresponding authors upon reasonable request.

References

Hooker, S. The hardware lottery. Commun. ACM 64, 58–65 (2021).

Touvron, H. et al. LLaMA: open and efficient foundation language models. Preprint at https://arxiv.org/abs/2302.13971 (2023).

Chen, J. & Ran, X. Deep learning with edge computing: a review. Proc. IEEE 107, 1655–1674 (2019).

Murmann, B. Mixed-signal computing for deep neural network inference. IEEE Trans. Very Large Scale Integr. VLSI Syst. 29, 3–13 (2021).

Reuther, A. et al. AI and ML accelerator survey and trends. In 2022 IEEE High Performance Extreme Computing Conference (HPEC) 1–10 (IEEE, 2022).

Horowitz, M. Computing’s energy problem (and what we can do about it). In International Solid-State Circuits Conference (ISSCC) 10–14 (IEEE, 2014).

He, M. et al. Newton: a DRAM-maker’s accelerator-in-memory (AiM) architecture for machine learning. In IEEE/ACM International Symposium on Microarchitecture (MICRO) 372–385 (IEEE, 2020).

Kwon, D. et al. A 1ynm 1.25V 8Gb, 16Gb/s/pin GDDR6-based accelerator-in-memory supporting 1TFLOPS MAC operation and various activation functions for deep-learning applications. IEEE J. Solid State Circuits 58, 291–302 (2022).

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

d-Matrix Corsair Redefines Performance and Efficiency for AI Inference at Scale White Paper (d-Matrix, 2025); https://d-matrix.ai/pdf/d-Matrix-WhitePaper-Technical-FINAL.pdf

Hager, P. A. et al. 11.3 Metis AIPU: a 12nm 15TOPS/W 209.6 TOPS SoC for cost-and energy-efficient inference at the edge. In 2024 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67, 212–214 (IEEE, 2024).

Le Gallo, M. et al. A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference. Nat. Electron. 6, 680–693 (2023).

Hsu, H.-H. et al. A nonvolatile AI-edge processor with SLC–MLC hybrid ReRAM compute-in-memory macro using current–voltage-hybrid readout scheme. IEEE J. Solid State Circuits 59, 116–127 (2023).

Abts, D. et al. The Groq software-defined scale-out tensor streaming multiprocessor: from chips-to-systems architectural overview. In Hot Chips Symposium (HCS) 1–69 (IEEE Computer Society, 2022).

Xie, S. et al. eDRAM-CIM: compute-in-memory design with reconfigurable embedded-dynamic-memory array realizing adaptive data converters and charge-domain computing. In International Solid-State Circuits Conference (ISSCC) Vol. 64, 248–250 (IEEE, 2021).

Kim, S. et al. Scaling-CIM: an eDRAM-based in-memory-computing accelerator with dynamic-scaling ADC for SQNR-boosting and layer-wise adaptive bit-truncation. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023).

Song, J. et al. A calibration-free 15-level/cell eDRAM computing-in-memory macro with 3T1C current-programmed dynamic-cascoded MLC achieving 233-to-304-TOPS/W 4b MAC. In Custom Integrated Circuits Conference (CICC) 1–2 (IEEE, 2023).

Burr, G. W., Sebastian, A., Ando, T. & Haensch, W. Ohm’s law + Kirchhoff’s current law = better AI: neural-network processing done in memory with analog circuits will save energy. IEEE Spectrum 58, 44–49 (2021).

Boybat-Kara, I. et al. Heterogeneous embedded neural processing units utilizing PCM-based analog in-memory computing. In IEEE International Electron Devices Meeting 1–4 (IEEE, 2024).

Büchel, J. et al. Efficient scaling of large language models with mixture of experts and 3D analog in-memory computing. Nat. Comput. Sci. 5, 13–26 (2025).

Rasch, M. J. et al. Hardware-aware training for large-scale and diverse deep learning inference workloads using in-memory computing-based accelerators. Nat. Commun. 14, 5282 (2023).

Mittal, S., Verma, G., Kaushik, B. & Khanday, F. A. A survey of SRAM-based in-memory computing techniques and applications. J. Syst. Archit. 119, 102276 (2021).

Jhang, C.-J., Xue, C.-X., Hung, J.-M., Chang, F.-C. & Chang, M.-F. Challenges and trends of SRAM-based computing-in-memory for AI edge devices. IEEE Trans. Circuits Syst. I 68, 1773–1786 (2021).

Spetalnick, S. & Raychowdhury, A. A practical design-space analysis of compute-in-memory with SRAM. IEEE Trans. Circuits Syst. I 69, 1466–1479 (2022).

Yu, S., Sun, X., Peng, X. & Huang, S. Compute-in-memory with emerging nonvolatile-memories: challenges and prospects. In Custom Integrated Circuits Conference (CICC) 1–4 (IEEE, 2020).

Hung, J.-M., Jhang, C.-J., Wu, P.-C., Chiu, Y.-C. & Chang, M.-F. Challenges and trends of nonvolatile in-memory-computation circuits for AI edge devices. IEEE Open J. Solid State Circuits Soc. 1, 171–183 (2021).

Shanbhag, N. R. & Roy, S. K. Benchmarking in-memory computing architectures. IEEE Open J. Solid State Circuits Soc. 2, 288–300 (2022).

Sun, J., Houshmand, P. & Verhelst, M. Analog or digital in-memory computing? Benchmarking through quantitative modeling. In International Conference on Computer Aided Design (ICCAD) 1–9 (IEEE, 2023).

Wu, P.-C. et al. A 22nm 832Kb hybrid-domain floating-point SRAM in-memory-compute macro with 16.2–70.2 TFLOPS/W for high-accuracy AI-edge devices. In International Solid-State Circuits Conference (ISSCC) 126–128 (IEEE, 2023).

Guo, A. et al. A 28 nm 128-kb exponent- and mantissa-computation-in-memory dual-macro for floating-point and INT CNNs. IEEE J. Solid State Circuits 60, 3639–3654 (2025).

Khwa, W.-S. et al. A mixed-precision memristor and SRAM compute-in-memory AI processor. Nature 639, 617–623 (2025).

Le Gallo, M. et al. Precision of bit slicing with in-memory computing based on analog phase-change memory crossbars. Neuromorphic Comput. Eng. 2, 014009 (2022).

Ambrogio, S. et al. An analog-AI chip for energy-efficient speech recognition and transcription. Nature 620, 768–775 (2023).

Mackin, C. et al. Optimised weight programming for analogue memory-based deep neural networks. Nat. Commun. 13, 3765 (2022).

Vasilopoulos, A. et al. Exploiting the state dependency of conductance variations in memristive devices for accurate in-memory computing. IEEE Trans. Electron Devices 70, 6279–6285 (2023).

Xiao, T. P., Bennett, C. H., Feinberg, B., Agarwal, S. & Marinella, M. J. Analog architectures for neural network acceleration based on non-volatile memory. Appl. Phys. Rev. 7, 031301 (2020).

Lee, J., Valavi, H., Tang, Y. & Verma, N. Fully row/column-parallel in-memory computing SRAM macro employing capacitor-based mixed-signal computation with 5-b inputs. In Symposium on VLSI Circuits 1–2 (IEEE, 2021).

Xue, C.-X. et al. A 22nm 4Mb 8b-precision ReRAM computing-in-memory macro with 11.91 to 195.7 TOPS/W for tiny AI edge devices. In International Solid-State Circuits Conference (ISSCC) Vol. 64, 245–247 (IEEE, 2021).

Le Gallo, M. et al. Demonstration of 4-quadrant analog in-memory matrix multiplication in a single modulation. npj Unconv. Comput. 1, 11 (2024).

Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. Nature 601, 211–216 (2022).

Fick, L., Skrzyniarz, S., Parikh, M., Henry, M. B. & Fick, D. Analog matrix processor for edge AI real-time video analytics. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 260–262 (IEEE, 2022).

Li, W., Sun, X., Jiang, H., Huang, S. & Yu, S. A 40nm RRAM compute-in-memory macro featuring on-chip write-verify and offset-cancelling ADC references. In European Solid State Circuits Conference (ESSCIRC) 79–82 (IEEE, 2021).

Khaddam-Aljameh, R. et al. HERMES-core—a 1.59-TOPS/mm 2 PCM on 14-nm CMOS in-memory compute core using 300-ps/LSB linearized CCO-based ADCs. J. Solid State Circuits 57, 1027–1038 (2022).

Xue, C.-X. et al. A 22nm 2Mb ReRAM compute-in-memory macro with 121-28TOPS/W for multibit MAC computing for tiny AI edge devices. In International Solid-State Circuits Conference (ISSCC) 244–246 (IEEE, 2020).

Sinangil, M. E. et al. A 7-nm compute-in-memory SRAM macro supporting multi-bit input, weight and output and achieving 351 TOPS/W and 372.4 GOPS. J. Solid State Circuits 56, 188–198 (2020).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Jia, H., Valavi, H., Tang, Y., Zhang, J. & Verma, N. A programmable heterogeneous microprocessor based on bit-scalable in-memory computing. IEEE J. Solid State Circuits 55, 2609–2621 (2020).

Burr, G. W. et al. Recent progress in phase-change memory technology. IEEE J. Emerg. Sel. Top. Circuits Syst. 6, 146–162 (2016).

Sun, X. et al. PCM-based analog compute-in-memory: impact of device non-idealities on inference accuracy. IEEE Trans. Electron Devices 68, 5585–5591 (2021).

Le Gallo, M. & Sebastian, A. An overview of phase-change memory device physics. J. Phys. D 53, 213002 (2020).

Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

Deaville, P., Zhang, B. & Verma, N. A fully row/column-parallel in-memory computing macro in foundry MRAM with differential readout for noise rejection. IEEE J. Solid State Circuits 59, 2070–2080 (2024).

Le Gallo, M., Sebastian, A., Cherubini, G., Giefers, H. & Eleftheriou, E. Compressed sensing with approximate message passing using in-memory computing. IEEE Trans. Electron Devices 65, 4304–4312 (2018).

Giannopoulos, I. et al. 8-bit precision in-memory multiplication with projected phase-change memory. In International Electron Devices Meeting (IEDM) 27.7 (IEEE, 2018).

Roy, S. K. et al. Compute SNDR-boosted 22-nm MRAM-based in-memory computing macro using statistical error compensation. IEEE J. Solid State Circuits 60, 1092–1102 (2025).

Jia, H. et al. Scalable and programmable neural network inference accelerator based on in-memory computing. IEEE J. Solid State Circuits 57, 198–211 (2021).

Miyashita, D., Kousai, S., Suzuki, T. & Deguchi, J. A neuromorphic chip optimized for deep learning and CMOS technology with time-domain analog and digital mixed-signal processing. IEEE J. Solid State Circuits 52, 2679–2689 (2017).

Joshi, V. et al. Accurate deep neural network inference using computational phase-change memory. Nat. Commun. 11, 2473 (2020).

Vignali, R. et al. Designing circuits for AiMC based on non-volatile memories: a tutorial brief on trade-off and strategies for ADCs and DACs co-design. IEEE Trans. Circuits Syst. II 71, 1650–1655 (2023).

Yin, S. et al. High-throughput in-memory computing for binary deep neural networks with monolithically integrated RRAM and 90-nm CMOS. IEEE Trans. Electron Devices 67, 4185–4192 (2020).

Yoon, J.-H. et al. A 40-nm, 64-Kb, 56.67 TOPS/W voltage-sensing computing-in-memory/digital RRAM macro supporting iterative write with verification and online read-disturb detection. IEEE J. Solid State Circuits 57, 68–79 (2021).

Khwa, W.-S. et al. A 40-nm, 2M-cell, 8b-precision, hybrid SLC–MLC PCM computing-in-memory macro with 20.5-65.0 TOPS/W for tiny-Al edge devices. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 1–3 (IEEE, 2022).

Liu, Q. et al. A fully integrated analog ReRAM based 78.4 TOPS/W compute-in-memory chip with fully parallel MAC computing. In International Solid-State Circuits Conference (ISSCC) 500–502 (IEEE, 2020).

Si, X. et al. A 28nm 64Kb 6T SRAM computing-in-memory macro with 8b MAC operation for AI edge chips. In International Solid-State Circuits Conference (ISSCC) 246–248 (IEEE, 2020).

Caselli, M., Bhattacharjee, D., Mallik, A., Debacker, P. & Verkest, D. Tiny ci-SAR A/D converter for deep neural networks in analog in-memory computation. In International Symposium on Circuits and Systems (ISCAS) 1823–1827 (IEEE, 2022).

Chen, Z. et al. CAP-RAM: a charge-domain in-memory computing 6T-SRAM for accurate and precision-programmable CNN inference. IEEE J. Solid State Circuits 56, 1924–1935 (2021).

Biswas, A., Sanghvi, H., Mehendale, M. & Preet, G. An area-efficient 6T-SRAM based compute-in-memory architecture with reconfigurable SAR ADCs for energy-efficient deep neural networks in edge ML applications. In Custom Integrated Circuits Conference (CICC) 1–2 (IEEE, 2022).

Um, J.-Y., Kim, Y.-J., Song, E.-W., Sim, J.-Y. & Park, H.-J. A digital-domain calibration of split-capacitor DAC for a differential SAR ADC without additional analog circuits. IEEE Trans. Circuits Syst. I 60, 2845–2856 (2013).

Kull, L. et al. A 3.1 mW 8b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. IEEE J. Solid State Circuits 48, 3049–3058 (2013).

Chiu, Y.-C. et al. A 22nm 4Mb STT-MRAM data-encrypted near-memory computation macro with a 192GB/s read-and-decryption bandwidth and 25.1–55.1 TOPS/W 8b MAC for AI operations. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 178–180 (IEEE, 2022).

Hung, J.-M. et al. A four-megabit compute-in-memory macro with eight-bit precision based on CMOS and resistive random-access memory for AI edge devices. Nat. Electron. 4, 921–930 (2021).

Narayanan, P. et al. Fully on-chip MAC at 14 nm enabled by accurate row-wise programming of PCM-based weights and parallel vector-transport in duration-format. IEEE Trans. Electron Devices 68, 6629–6636 (2021).

Liu, C. et al. A spiking neuromorphic design with resistive crossbar. In Design Automation Conference (DAC) 1–6 (IEEE, 2015).

Liu, C. et al. A memristor crossbar based computing engine optimized for high speed and accuracy. In IEEE Computer Society Annual Symposium on VLSI (ISVLSI) 110–115 (IEEE, 2016).

Yan, B. et al. RRAM-based spiking nonvolatile computing-in-memory processing engine with precision-configurable in situ nonlinear activation. In Symposium on VLSI Technology T86–T87 (IEEE, 2019).

Elshazly, A., Rao, S., Young, B. & Hanumolu, P. K. A noise-shaping time-to-digital converter using switched-ring oscillators—analysis, design, and measurement techniques. IEEE J. Solid State Circuits 49, 1184–1197 (2014).

Chen, W.-H. et al. A 65nm 1Mb nonvolatile computing-in-memory ReRAM macro with sub-16ns multiply-and-accumulate for binary DNN AI edge processors. In International Solid-State Circuits Conference (ISSCC) 494–496 (IEEE, 2018).

Chen, W.-H. et al. CMOS-integrated memristive non-volatile computing-in-memory for AI edge processors. Nat. Electron. 2, 420–428 (2019).

Antolini, A. et al. Controlled acceleration of PCM cells time drift through on-chip current-induced annealing for AIMC multilevel MVM computation. IEEE Trans. Electron Devices 72, 215–221 (2025).

Büchel, J. et al. Programming weights to analog in-memory computing cores by direct minimization of the matrix-vector multiplication error. IEEE J. Emerg. Sel. Top. Circuits Syst. 13, 1052-1061 (2023).

Wang, D. et al. DIMC: 2219TOPS/W 2569F2/b digital in-memory computing macro in 28nm based on approximate arithmetic hardware. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 266–268 (IEEE, 2022).

Fujiwara, H. et al. A 5-nm 254-TOPS/W 221-TOPS/mm2 fully-digital computing-in-memory macro supporting wide-range dynamic-voltage-frequency scaling and simultaneous MAC and write operations. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 1–3 (IEEE, 2022).

Biswas, A. & Chandrakasan, A. P. CONV-SRAM: an energy-efficient SRAM with in-memory dot-product computation for low-power convolutional neural networks. IEEE J. Solid State Circuits 54, 217–230 (2018).

Khwa, W.-S. et al. A 65nm 4Kb algorithm-dependent computing-in-memory SRAM unit-macro with 2.3 ns and 55.8 TOPS/W fully parallel product–sum operation for binary DNN edge processors. In 2018 IEEE International Solid-State Circuits Conference (ISSCC) 496–498 (IEEE, 2018).

Si, X. et al. A twin-8T SRAM computation-in-memory macro for multiple-bit CNN-based machine learning. In International Solid-State Circuits Conference (ISSCC) 396–398 (IEEE, 2019).

Wu, P.-C. et al. A 28nm 1Mb time-domain computing-in-memory 6T-SRAM macro with a 6.6 ns latency, 1241GOPS and 37.01 TOPS/W for 8b-MAC operations for edge-AI devices. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 1–3 (IEEE, 2022).

Khaddam-Aljameh, R., Francese, P.-A., Benini, L. & Eleftheriou, E. An SRAM-based multibit in-memory matrix-vector multiplier with a precision that scales linearly in area, time, and power. IEEE Trans. Very Large Scale Integr. VLSI Syst. 29, 372–385 (2020).

Lee, C.-F. et al. A 12nm 121-TOPS/W 41.6-TOPS/mm2 all digital full precision SRAM-based compute-in-memory with configurable bit-width for AI edge applications. In Symposium on VLSI Technology and Circuits 24–25 (IEEE, 2022).

Wang, H. et al. A charge domain SRAM compute-in-memory macro with C-2C ladder-based 8-bit MAC unit in 22-nm FinFET process for edge inference. IEEE J. Solid State Circuits 58, 1037–1050 (2023).

Fujiwara, H. et al. A 3nm, 32.5 TOPS/W, 55.0 TOPS/mm2 and 3.78 Mb/mm2 fully-digital compute-in-memory macro supporting INT12 × INT12 with a parallel-MAC architecture and foundry 6T-SRAM bit cell. In IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67, 572–574 (IEEE, 2024).

Wong, H. On the CMOS device downsizing, more Moore, more than Moore, and more-than-Moore for more Moore. In International Conference on Microelectronics (MIEL) 9–15 (IEEE, 2021).

Das, U. K. & Bhattacharyya, T. K. Opportunities in device scaling for 3-nm node and beyond: FinFET versus GAA-FET versus UFET. IEEE Trans. Electron Devices 67, 2633–2638 (2020).

Bavandpour, M., Sahay, S., Mahmoodi, M. R. & Strukov, D. B. 3D-aCortex: an ultra-compact energy-efficient neurocomputing platform based on commercial 3D-NAND flash memories. Neuromorphic Comput. Eng. 1, 014001 (2021).

Hu, H.-W. et al. A 512Gb in-memory-computing 3D-NAND flash supporting similar-vector-matching operations on edge-AI devices. In International Solid-State Circuits Conference (ISSCC) Vol. 65, 138–140 (IEEE, 2022).

Wei, M.-L. et al. Analog computing in memory (CIM) technique for general matrix multiplication (GEMM) to support deep neural network (DNN) and cosine similarity search computing using 3D AND-type NOR flash devices. In International Electron Devices Meeting (IEDM) 33.3.1–33.3.4 (IEEE, 2022).

Du, Y. et al. Monolithic 3D integration of FeFET, hybrid CMOS logic and analog RRAM array for energy-efficient reconfigurable computing-in-memory architecture. In Symposium on VLSI Technology and Circuits 1–2 (IEEE, 2023).

Carletti, F. et al. Low-energy, high-accuracy convolutional network inference in 3D crosspoint (3DXP) arrays. In European Solid-State Electronics Research Conference (ESSERC) 412–415 (IEEE, 2024).

Yu, S. et al. Compute-in-memory: from device innovation to 3D system integration. In European Solid-State Device Research Conference (ESSDERC) 21–28 (IEEE, 2021).

Agrawal, A. et al. A switched-capacitor integer compute unit with decoupled storage and arithmetic for Cloud AI inference in 5nm CMOS. In Symposium on VLSI Technology and Circuits 1–2 (IEEE, 2023).

Wen, T.-H. et al. Fusion of memristor and digital compute-in-memory processing for energy-efficient edge computing. Science 384, 325–332 (2024).

Acknowledgements

We thank P. A. Francese, S. Tsai, V. Narayanan and J. Burns for technical discussions and management support.

Author information

Authors and Affiliations

Contributions

A. Singh, M.L.G. and A. Sebastian conceived of the overall research idea and coordinated the project. The manuscript was initially drafted by A. Singh, with substantial input through comments, revisions and structural guidance from A.V., M.L.G. and A. Sebastian. J.L., P.N. and G.W.B. provided critical reviews focused on the technical content and paper structure. P.N. contributed specifically to refining and streamlining the technical content, while G.W.B. offered detailed feedback on the overall presentation of the key contributions, especially in the Introduction and figures. All authors reviewed the final paper and contributed to its revision and approval.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Electronics thanks Hongyang Jia and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information (download PDF )

Supplementary Notes 1–4 and Figs. 1–3.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Singh, A., Le Gallo, M., Vasilopoulos, A. et al. The design of analogue in-memory computing tiles. Nat Electron 8, 1156–1169 (2025). https://doi.org/10.1038/s41928-025-01537-5

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41928-025-01537-5