Abstract

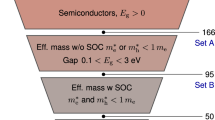

As semiconductor-based electronic technologies continue downscaling, there is an urgent need to overcome the limitations of interconnect architectures and materials that are driving an unsustainable increase in energy consumption and jeopardizing performance. In this Review, we investigate the primary causes of prolonged signal delays in interconnect systems, providing an overview of the development of key interconnect components: metals, diffusion barriers and intermetal dielectrics. We define the essential requirements and technological hurdles for next-generation materials to be industrialized within damascene processes, including topological semi-metals such as molybdenum phosphide (MoP) and 2D materials such as graphene and amorphous boron nitride (a-BN). Integrating new materials into advanced device systems offers opportunities for the advancement of interconnect technologies and highly integrated semiconductor devices.

Key points

-

As semiconductor devices relentlessly scale down, mitigating critical signal delay in interconnects requires cutting-edge materials with a low metal resistance, robust thin diffusion barrier and low intermetal dielectric (IMD) capacitance.

-

Topological semi-metals such as molybdenum phosphide (MoP) and MoTe2 for metals, 2D materials such as graphene and MoS2 for diffusion barriers, and transformed 2D materials such as amorphous boron nitride (a-BN) for IMDs hold immense potential to surpass these constraints.

-

The successful industrialization of these novel materials requires breakthroughs in the basic science to achieve ideal properties and engineering solutions to ensure seamless integration with current damascene processes.

-

The discovery of novel materials, coupled with advances in process engineering, will create interconnect technologies that offer more efficient and sustainable performance.

This is a preview of subscription content, access via your institution

Access options

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Harvey, F. Energy demands from AI datacentres to quadruple by 2030, says report. The Guardian https://www.theguardian.com/technology/2025/apr/10/energy-demands-from-ai-datacentres-to-quadruple-by-2030-says-report (2025).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Wheeler, A. What raw materials are used to make hardware in computing devices? engineering.com https://www.engineering.com/what-raw-materials-are-used-to-make-hardware-in-computing-devices/ (2018).

IEEE. International Roadmap for Devices and Systems: 2022 edition. IEEE.org https://irds.ieee.org/editions/2022 (2022).

IEEE. International Roadmap for Devices and Systems: 2024 edition. IEEE.org https://irds.ieee.org/editions/2024 (2024).

Yeap, G. Smart mobile SoCs driving the semiconductor industry: technology trend, challenges and opportunities. In IEEE Int. Electron Devices Meeting (IEDM) 1.3.1–1.3.8 (IEEE, 2013).

Gilbert, M. J. Topological electronics. Commun. Phys. 4, 70 (2021).

Zhai, E. et al. The rise of semi-metal electronics. Nat. Rev. Electr. Eng. 1, 1–19 (2024).

Wang, L. et al. Excellent catalytic performance toward the hydrogen evolution reaction in topological semimetals. EcoMat 5, e12316 (2023).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6, 183–191 (2007).

Manzeli, S., Ovchinnikov, D., Pasquier, D., Yazyev, O. V. & Kis, A. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2, 17033 (2017).

Chen, S.-H., Magyari-Kope, B., Hsu, C.-H., Woon, W.-Y. & Liao, S. S. Boron nitride for applications in microelectronics. Nat. Rev. Electr. Eng. 2, 1–10 (2025).

Edelstein, D. et al. Full copper wiring in a sub-0.25 μm CMOS ULSI technology. In IEEE Int. Electron Devices Meeting (IEDM) 773–776 (IEEE, 1997).

Venkatesan, S. et al. A high performance 1.8 V, 0.20 μm CMOS technology with copper metallization. In IEEE Int. Electron Devices Meeting (IEDM) 769–772 (IEEE, 1997).

International Technology Roadmap for Semiconductors, 2001 edition. SIA https://www.semiconductors.org/wp-content/uploads/2018/08/2001PIDS.pdf (2001).

Gall, D. The search for the most conductive metal for narrow interconnect lines. J. Appl. Phys. 127, 050901 (2020).

Josell, D., Brongersma, S. H. & Tőkei, Z. Size-dependent resistivity in nanoscale interconnects. Annu. Rev. Mater. Res. 39, 231–254 (2009).

Milosevic, E. et al. Resistivity size effect in epitaxial Ru(0001) layers. J. Appl. Phys. 124, 165105 (2018).

Kotsugi, Y. et al. Atomic layer deposition of Ru for replacing Cu interconnects. Chem. Mater. 33, 5639–5651 (2021).

Kim, J. et al. Electromigration reliability of barrierless ruthenium and molybdenum for sub-10 nm interconnection. ACS Appl. Electron. Mater. 5, 2447–2453 (2023).

Kim, Y. H. et al. Atomic layer deposited RuO₂ diffusion barrier for next-generation Ru interconnects. Adv. Funct. Mater. 32, 2206667 (2022).

Murdoch, G. et al. Semidamascene interconnects for 2 nm node and beyond. In 2020 IEEE Int. Interconnect Technol. Conf. (IITC) 4–6 (IEEE, 2020).

Jog, A. & Gall, D. Resistivity size effect in epitaxial iridium layers. J. Appl. Phys. 130, 115103 (2021).

Lanzillo, N. A. & Edelstein, D. C. Reliability and resistance projections for rhodium and iridium interconnects from first-principles. J. Vac. Sci. Technol. B 40, 052801 (2022).

Jog, A. & Gall, D. Resistivity scaling of epitaxial iridium layers. IEEE Trans. Electron. Devices 69, 3854–3860 (2022).

Gall, D. Electron mean free path in elemental metals. J. Appl. Phys. 119, 085101 (2016).

Bohr, M. T. Interconnect scaling—the real limiter to high-performance ULSI. In IEEE Int. Electron Devices Meeting (IEDM) 241–244 (IEEE, 1995).

Edelstein, D. et al. A high performance liner for copper Damascene interconnects. In IEEE Int. Interconnect Technol. Conf. (IITC) 9–11 (IEEE, 2001).

Hübner, J. et al. Electron scattering at surfaces and grain boundaries in Cu thin films. Thin Solid. Films 437, 248–256 (2003).

Jung, H. K. et al. Formation of highly reliable Cu/low-k interconnects by using CVD Co barrier in dual-damascene structures. In IEEE Int. Rel. Phys. Symp. (IRPS) 3E.2.1–3E.2.5 (IEEE, 2011).

Yang, C.-C. et al. Characterization of “Ultrathin-Cu”/Ru(Ta)/TaN liner stack for copper interconnects. IEEE Electron. Device Lett. 31, 722–724 (2010).

Chen, J. H.-C., Standaert, T. E., Alptekin, E., Spooner, T. A. & Paruchuri, V. Interconnect performance and scaling strategy at 7 nm node. In IEEE Int. Interconnect Technol. Conf. (IITC) 93–96 (IEEE, 2014).

Ravi. S. 2003 International Technology Roadmap for Semiconductors (ITRS). SIA https://www.semiconductors.org/resources/2003-international-technology-roadmap-for-semiconductors-itrs/ (2003).

IEEE. International Roadmap for Devices and Systems. 2022 update: More Moore. IEEE.org https://irds.ieee.org/editions/2022/more-moore (2022).

Witt, C. et al. Testing the limits of TaN barrier scaling. In IEEE Int. Interconnect Technol. Conf. (IITC) 54–56 (IEEE, 2018).

Xu, H. et al. Effect of thickness scaling on the permeability and thermal stability of Ta(N) diffusion barrier. Appl. Surf. Sci. 498, 143887 (2019).

Yeoh, A. et al. Interconnect stack using self-aligned quad and double patterning for 10 nm high volume manufacturing. In IEEE Int. Interconnect Technol. Conf. (IITC) 144–147 (IEEE, 2018).

Wen, L. G. et al. Ruthenium metallization for advanced interconnects. In IEEE Int. Interconnect Technol. Conf./Advanced Metallization Conf. (IITC/AMC) 34–36 (IEEE, 2016).

Hosseini, M. et al. ALD Mo for advanced MOL local interconnects. In IEEE Int. Interconnect Technol. Conf. (IITC) 145–147 (IEEE, 2022).

Croes, K. et al. Interconnect metals beyond copper: reliability challenges and opportunities. In Proc. IEEE Int. Electron Devices Meeting (IEDM) 5.3.1–5.3.4 (IEEE, 2018).

Hatton, B. D. et al. Materials chemistry for low-k materials. Mater. Today 9, 22–31 (2006).

Volksen, W., Miller, R. D. & Dubois, G. Low dielectric constant materials. Chem. Rev. 110, 56–110 (2010).

Shamiryan, D., Abell, T., Iacopi, F. & Maex, K. Low-k dielectric materials. Mater. Today 7, 34–39 (2004).

Shwartz, G. C. Handbook of Semiconductor Interconnection Technology (CRC, 2006).

Maex, K. et al. Low dielectric constant materials for microelectronics. J. Appl. Phys. 93, 8793–8841 (2003).

Grill, A. et al. Optimization of SiCOH dielectrics for integration in a 90 nm CMOS technology. In IEEE Int. Interconnect Technol. Conf. (IITC) 54–56 (IEEE, 2004).

Havemann, R. H. & Hutchby, J. A. High-performance interconnects: an integration overview. Proc. IEEE 89, 586–601 (2001).

Leduc, P. et al. Understanding CMP-induced delamination in ultra low-k/Cu integration. In IEEE Int. Interconnect Technol. Conf. (IITC) 209–211 (IEEE, 2005).

Si, L., Guo, D., Xie, G. & Luo, J. Mechanical properties and interface characteristics of nanoporous low-k materials. ACS Appl. Mater. Interfaces 6, 13850–13858 (2014).

Fischer, K. et al. Low-k interconnect stack with multi-layer air gap and tri-metal–insulator–metal capacitors for 14 nm high volume manufacturing. In IEEE Int. Interconnect Technol. Conf./Materials for Advanced Metallization Conf. (IITC/MAM) 5–8 (IEEE, 2015).

Usman, M., Mendiratta, S. & Lu, K. L. Metal-organic frameworks: new interlayer dielectric materials. ChemElectroChem 2, 786–788 (2015).

Krishtab, M. et al. Vapor-deposited zeolitic imidazolate frameworks as gap-filling ultra-low-k dielectrics. Nat. Commun. 10, 3729 (2019).

Shao, P. et al. Flexible films of covalent organic frameworks with ultralow dielectric constants under high humidity. Angew. Chem. Int. Ed. 57, 16501–16505 (2018).

Evans, A. M. et al. Thermally conductive ultra-low-k dielectric layers based on two-dimensional covalent organic frameworks. Nat. Mater. 20, 1142–1148 (2021).

Miller, D. A. Device requirements for optical interconnects to silicon chips. Proc. IEEE 97, 1166–1185 (2009).

Liu, P., Williams, J. R. & Cha, J. J. Topological nanomaterials. Nat. Rev. Mater. 4, 479–496 (2019).

Nagaosa, N., Morimoto, T. & Tokura, Y. Transport, magnetic and optical properties of Weyl materials. Nat. Rev. Mater. 5, 621–636 (2020).

Krishnamoorthy, H. N., Dubrovkin, A. M., Adamo, G. & Soci, C. Topological insulator metamaterials. Chem. Rev. 123, 4416–4442 (2023).

Kumar, N., Guin, S. N., Manna, K., Shekhar, C. & Felser, C. Topological quantum materials from the viewpoint of chemistry. Chem. Rev. 121, 2780–2815 (2020).

Sato, M. & Ando, Y. Topological superconductors: a review. Rep. Prog. Phys. 80, 076501 (2017).

Giustino, F. et al. The 2021 quantum materials roadmap. J. Phys. Mater. 3, 042006 (2021).

Kumar, N. et al. Extremely high magnetoresistance and conductivity in the type-II Weyl semimetals WP2 and MoP2. Nat. Commun. 8, 1642 (2017).

Kumar, N. et al. Extremely high conductivity observed in the triple point topological metal MoP. Nat. Commun. 10, 2475 (2019).

Shekhar, C. et al. Extremely large magnetoresistance and ultrahigh mobility in the topological Weyl semimetal candidate NbP. Nat. Phys. 11, 645–649 (2015).

Zhang, C. et al. Ultrahigh conductivity in Weyl semimetal NbAs nanobelts. Nat. Mater. 18, 482–488 (2019).

Brumme, T., Calandra, M. & Mauri, F. Determination of scattering time and of valley occupation in transition-metal dichalcogenides doped by field effect. Phys. Rev. B 93, 081407 (2016).

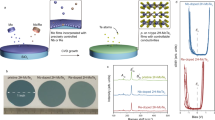

Han, H. J. et al. Topological metal MoP nanowire for interconnect. Adv. Mater. 35, 2208965 (2023).

Khan, A. I. et al. Surface conduction and reduced electrical resistivity in ultrathin noncrystalline NbP semimetal. Science 387, 62–67 (2025).

Scott, E. F. et al. Doping as a tuning mechanism for magnetothermoelectric effects to improve zT in polycrystalline NbP. Phys. Rev. B 107, 115108 (2023).

Kumar, S. et al. Surface-dominated conductance scaling in Weyl semimetal NbAs. NPJ Comput. Mater. 10, 84 (2024).

Lien, S.-W. et al. Unconventional resistivity scaling in topological semimetal CoSi. NPJ Quantum Mater. 8, 3 (2023).

Tsai, C.-I. et al. Cobalt silicide nanostructures: synthesis, electron transport, and field emission properties. Cryst. Growth Des. 9, 4514–4518 (2009).

Jin, G. et al. Vapor phase synthesis of topological semimetal MoP2 nanowires and their resistivity. Appl. Phys. Lett. 121, 113105 (2022).

Lin, T. et al. Ultrafast carrier relaxation dynamics in a nodal-line semimetal PtSn4. Nano Lett. 24, 6278–6285 (2024).

Oudah, M. et al. Discovery of superconductivity and electron–phonon drag in the non-centrosymmetric Weyl semimetal LaRhGe3. NPJ Quantum Mater. 9, 88 (2024).

Anemone, G. et al. Electron–phonon coupling in superconducting 1T-PdTe2. NPJ 2D Mater. Appl. 5, 25 (2021).

Lo, C.-L. et al. Opportunities and challenges of 2D materials in back-end-of-line interconnect scaling. J. Appl. Phys. 128, 080903 (2020).

Berry, V. Impermeability of graphene and its applications. Carbon 62, 1–10 (2013).

Li, L. et al. Vertical and lateral copper transport through graphene layers. ACS Nano 9, 8361–8367 (2015).

Hong, J. et al. Graphene as an atomically thin barrier to Cu diffusion into Si. Nanoscale 6, 7503–7511 (2014).

Nguyen, B.-S., Lin, J.-F. & Perng, D.-C. 1-nm-Thick graphene tri-layer as the ultimate copper diffusion barrier. Appl. Phys. Lett. 104, 082105 (2014).

Kuo, C.-Y. et al. Graphene-all-around cobalt interconnect with a back-end-of-line compatible process. Nano Lett. 24, 2102–2109 (2024).

Lo, C.-L. et al. Large-area, single-layer molybdenum disulfide synthesized at BEOL compatible temperature as Cu diffusion barrier. IEEE Electron. Device Lett. 39, 873–876 (2018).

Shen, T. et al. MoS2 for enhanced electrical performance of ultrathin copper films. ACS Appl. Mater. Interfaces 11, 28345–28351 (2019).

Zhao, R. et al. Incorporating niobium in MoS2 at BEOL-compatible temperatures and its impact on copper diffusion barrier performance. Adv. Mater. Interfaces 6, 1901055 (2019).

Kuo, C.-Y. et al. MoS2 as an effective Cu diffusion barrier with a back-end compatible process. ACS Appl. Mater. Interfaces 15, 47845–47854 (2023).

Deijkers, J. H. et al. MoS2 synthesized by atomic layer deposition as Cu diffusion barrier. Adv. Mater. Interfaces 10, 2202426 (2023).

El Kazzi, S. et al. Assessing ultrathin wafer-scale WS2 as a diffusion barrier for Cu interconnects. ACS Appl. Electron. Mater. 5, 5074–5081 (2023).

Lo, C.-L. et al. Enhancing interconnect reliability and performance by converting tantalum to 2D layered tantalum sulfide at low temperature. Adv. Mater. 31, 1902397 (2019).

Lo, C.-L. et al. Studies of two-dimensional h-BN and MoS2 for potential diffusion barrier application in copper interconnect technology. NPJ 2D Mater. Appl. 1, 42 (2017).

Rahman, M. H., Biswas, M. & Mannodi-Kanakkithodi, A. Understanding defect-mediated ion migration in semiconductors using atomistic simulations and machine learning. ACS Mater. Au 4, 557–573 (2024).

Ahmed, M., Li, Y., Chen, W. & Li, E.-P. First-principles investigation of copper diffusion barrier performance in defective 2D layered materials. Nanotechnol 33, 165201 (2022).

Galvani, T. et al. Exploring dielectric properties in atomistic models of amorphous boron nitride. J. Phys. Mater. 7, 035003 (2024).

Hong, S. et al. Ultralow-dielectric-constant amorphous boron nitride. Nature 582, 511–514 (2020).

Hong, S. et al. Reply to: On the measured dielectric constant of amorphous boron nitride. Nature 590, E8–E10 (2021).

Nguyen, S., Nguyen, T., Treichel, H. & Spindler, O. Plasma-assisted chemical vapor deposition and characterization of boron nitride films. J. Electrochem. Soc. 141, 1633 (1994).

Lin, C. M. et al. Ultralow-k amorphous boron nitride based on hexagonal ring stacking framework for 300 mm silicon technology platform. Adv. Mater. Technol. 7, 2200022 (2022).

Lu, C.-M. V., Fenouillet-Beranger, C., Bout, C. & Roule, A. Integration of low temperature 480 °C SiOCN as offset spacer in view of 3D sequential integration. In Ext. Abstr. 2016 Int. Conf. Solid State Devices Mater. (SSDM) 657–658 (Jpn. Soc. Appl. Phys., 2016).

Chen, C. Y. et al. Tailoring amorphous boron nitride for high-performance two-dimensional electronics. Nat. Commun. 15, 4016 (2024).

Kim, K. et al. Ultralow-k amorphous boron nitride film for copper interconnect capping layer. IEEE Trans. Electron. Devices 70, 2588–2593 (2023).

Kaya, O., Colombo, L., Antidormi, A., Lanza, M. & Roche, S. Revealing the improved stability of amorphous boron-nitride upon carbon doping. Nanoscale Horiz. 8, 361–367 (2023).

Kaya, O. et al. Amorphous boron nitride as a diffusion barrier to Cu atoms. Preprint at https://arxiv.org/html/2402.01251v1 (2024).

Kaya, O. et al. Impact of hydrogenation on the stability and mechanical properties of amorphous boron nitride. J. Phys. Mater. 7, 025010 (2024).

Baklanov, M. R. et al. Plasma processing of low-k dielectrics. J. Appl. Phys. 113, 041101 (2013).

Lionti, K., Volksen, W., Magbitang, T., Darnon, M. & Dubois, G. Toward successful integration of porous low-k materials: strategies addressing plasma damage. ECS J. Solid. State Sci. Technol. 4, N3071 (2014).

Kim, C. et al. A study on the interfacial adhesion energy between capping layer and dielectric for Cu interconnects. Microelectron. Reliab. 116, 114020 (2021).

Lee, C. S. et al. Fabrication of metal/graphene hybrid interconnects by direct graphene growth and their integration properties. Adv. Electron. Mater. 4, 1700624 (2018).

Nguyen, V. L. et al. Wafer-scale integration of transition metal dichalcogenide field-effect transistors using adhesion lithography. Nat. Electron. 6, 146–153 (2023).

Han, H. J. et al. Synthesis and resistivity of topological metal MoP nanostructures. APL. Mater. 8, 011103 (2020).

Ciofi, I. et al. Impact of wire geometry on interconnect RC and circuit delay. IEEE Trans. Electron. Devices 63, 2488–2496 (2016).

Bansal, A., Paul, B. C. & Roy, K. An analytical fringe capacitance model for interconnects using conformal mapping. IEEE Trans. Comput. -Aided Des. Integr. Circuits Syst. 25, 2765–2774 (2006).

Zhou, T., Lanzillo, N. A., Bhosale, P., Gall, D. & Quon, R. A first-principles analysis of ballistic conductance, grain boundary scattering and vertical resistance in aluminum interconnects. AIP Adv. 8, 055127 (2018).

Valencia, D. et al. Grain-boundary resistance in copper interconnects: from an atomistic model to a neural network. Phys. Rev. Appl. 9, 044005 (2018).

Gall, D. et al. Materials for interconnects. MRS Bull. 46, 959–966 (2021).

Qi, Y. et al. Superconductivity in Weyl semimetal candidate MoTe2. Nat. Commun. 7, 11038 (2016).

Lahourpour, F., Boochani, A., Parhizgar, S. & Elahi, S. Structural, electronic and optical properties of graphene-like nano-layers MoX2 (X = S, Se, Te): DFT study. J. Theor. Appl. Phys. 13, 191–201 (2019).

Zhang, X. et al. Ruthenium interconnect resistivity and reliability at 48 nm pitch. In 2016 IEEE Int. Interconnect Technol. Conf./Advanced Metallization Conf. (IITC/AMC) 31–33 (IEEE, 2016).

Steeves, M., Deniz, D. & Lad, R. Charge transport in flat and nanorod structured ruthenium thin films. Appl. Phys. Lett. 96, 142103 (2010).

Meindl, J. D. Beyond Moore’s law: the interconnect era. Comput. Sci. Eng. 5, 20–24 (2003).

Magen, N., Kolodny, A., Weiser, U. & Shamir, N. Interconnect-power dissipation in a microprocessor. In Proc. Int. Workshop Syst. Level Interconnect Predict. 7–13 (ACM, 2004).

Banerjee, K. & Mehrotra, A. Power dissipation issues in interconnect performance optimization for sub-180 nm designs. In Symp. VLSI Circuits, Dig. Tech. Pap. 12–15 (IEEE, 2002).

Borkar, S. Design challenges of technology scaling. IEEE Micro 19, 23–29 (1999).

Ceyhan, A. & Naeemi, A. Cu/low-k interconnect technology design and benchmarking for future technology nodes. IEEE Trans. Electron. Devices 60, 4041–4047 (2013).

Wong, S.-C., Lee, G.-Y. & Ma, D.-J. Modeling of interconnect capacitance, delay, and crosstalk in VLSI. IEEE Trans. Semicond. Manuf. 13, 108–111 (2000).

Morgen, M. et al. Low dielectric constant materials for ULSI interconnects. Annu. Rev. Mater. Sci. 30, 645–680 (2000).

Acknowledgements

H.-J.S. acknowledges support from the National Research Foundation of Korea (NRF) grant funded by the Korean Government Ministry of Science and ICT (MSIT) (grant no. RS-2024-00352458), the GIST research fund (Future-leading Specialized Research Project, 2025) and the InnoCORE programme of the MSIT (GIST InnoCORE KH0830). H.S.S acknowledges support from the Institute for Basic Science (IBS-R036-D1), Republic of Korea. M.C. acknowledges support from the European Research Council (ERC) Advanced Grant (grant agreement GA 101019828-2D-LOTTO) and EPSRC (EP/ T026200/1, EP/T001038/1). J.J.C. acknowledges support from the US National Science Foundation Division of Materials Research (FUSE 2328907). O.K. acknowledges REDI Program funding and a Marie Skłodowska-Curie Grant (no. 101034328). S.R. acknowledges 2021 SGR 00997, CERCA Programme of the Generalitat de Catalunya, Severo Ochoa Centres of Excellence Programme (grant no. CEX2021-001214-S) and MCIN/AEI/10.13039.501100011033.

Author information

Authors and Affiliations

Contributions

H.-J.S. conceptualized this work. H.K., S.O., S.A. and H.-J.S. researched data for the article and wrote the manuscript. J.K., T.K. J.J.C., M.C. and H.S.S. contributed substantially to discussion of the content, and reviewed and edited the manuscript. S.J., O.K., T.G. and S.R. reviewed and edited the manuscript. J.J.C., M.C., H.S.S. and H.-J.S. supervised this project.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Reviews Electrical Engineering thanks Wenzhong Bao, Yang Chai, Shengxi Huang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, H., Oh, S., An, S. et al. Future interconnect materials for highly integrated semiconductor devices. Nat Rev Electr Eng 2, 835–845 (2025). https://doi.org/10.1038/s44287-025-00233-y

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s44287-025-00233-y