Abstract

Sharing the hardware platform between diverse information systems to establish full cooperation among different functionalities has attracted substantial attention. However, broadband multifunctional integrated systems with large operating frequency ranges are challenging due to the bandwidth and computing speed restrictions of electronic circuitry. Here, we report an analog parallel processor (APP) based on the silicon photonic platform that directly discretizes and parallelizes the broadband signal in the analog domain. The APP first discretizes the signal with the optical frequency comb and then adopts optical dynamic phase interference to reassign the analog signal into 2N parallel sequences. Via photonic analog parallelism, data rate and data volume in each sequence are simultaneously compressed, which mitigates the requirement on each parallel computing core. Moreover, the fusion of the outputs from each computing core is equivalent to directly processing broadband signals. In the proof-of-concept experiment, two-channel analog parallel processing of broadband radar signals and high-speed communication signals is implemented on the single photonic integrated circuit. The bandwidth of broadband radar signal is 6 GHz and the range resolution of 2.69 cm is achieved. The wireless communication rate of 8 Gbit/s is also validated. Breaking the bandwidth and speed limitations of the single-computing core along with further exploring the multichannel potential of this architecture, we anticipate that the proposed APP will accelerate the development of powerful opto-electronic processors as critical support for applications such as satellite networks and intelligent driving.

Similar content being viewed by others

Introduction

The effective acquisition and utilization of massive, diversified, and multifunctional information is crucial for intelligent sensing systems, such as unmanned vehicles and the Internet of Things1,2,3. To achieve this capability, the type and number of radio-frequency (RF) sensors are continuously expanding, resulting in quality and volume that exceed the affordable limit of mobile or distributed sensing platforms. Multifunctional integrated systems, which share the hardware platform among different functionalities, break the constraints of traditional resource division technologies and share resources efficiently4. Benefitting from technologies such as digital array antenna5, waveform multiplexing6, and resource scheduling7, multifunctional integrated systems achieve a higher degree of fusion and collaborative efficiency. All these strengths are in compliance with the development trends of intelligent sensing systems, especially airborne, vehicle, and other mobile platforms8. Future generations of multifunctional integrated systems will propel broader bandwidth to achieve increased data rate and finer sensing resolution, as well as require wider range of operating frequencies for more flexible scheduling of frequencies and functions9,10,11,12,13. However, the bandwidth and computing speed restrictions of electronic circuitry have hindered the evolution of multifunctional integrated systems towards efficient information acquisition and interaction across a wider spectrum14.

Microwave photonics (MWP) can access a broader bandwidth compared with electrical technologies, harnessing the processing bandwidth obtained from upconverting radio-frequencies (RF) to optical frequencies15,16. Broadband solutions include MWP receivers based on de-chirping for broadband linear frequency-modulated (LFM) radar echo signals17, integrated MWP filters for large-capacity wireless communication systems18,19, and MWP receivers capable of microwave signals measurement20,21. These solutions pursue broad acquisition bandwidth and flexible RF response tailoring capability. However, as they are designed and implemented to optimally perform a particular functionality, there is a lack of universality and reconfigurability for multifunctional applications16. Meanwhile, fully digital solutions that use analog-to-digital converters (ADC) along with digital signal processors (DSP) to implement multifunctional receiving and processing can guarantee universality and reconfigurability. Nevertheless, to process signals with broad bandwidth, the fully digital solution will produce a great deal of data, occupying a significant amount of memory and processing resources. This puts undue stress on high-performance signal processors14. Although emerging photonic signal processors excel in terms of clock rate, throughput, and power efficiency22,23,24,25,26,27,28,29,30. Their wide deployment is impeded by two challenges: access to high-speed memory to prevent a memory bottleneck31,32, and the total insertion loss when scaling up network dimensions26. In this case, how to advance broadband photonic signal processing capacity with mature electrical circuits without putting additional pressure on memories is an urgent problem to be solved.

Here, we demonstrate a silicon photonic platform-based analog parallel processor (APP) for broadband multifunctional integrated systems, which directly discretizes and parallelizes the broadband signal in the analog domain. Thus, computing cores with reduced clock rate and data volume are capable of processing diverse broadband signals. High-speed memories are also significantly omitted, which are usually configured to complete serial-parallel conversion in traditional electrical digital processors. The APP utilizes the optical frequency comb to discretize broadband analog signal, and then reassign temporal discrete signal into 2N parallel sequences through optical dynamic phase interference. For each sequence, the data is demultiplexed in time-domain and processed independently through low-speed computing cores in each channel. It is verified that the fusion of outputs from each computing core is equivalent to processing broadband signals directly. In the proof-of-concept experiment, a two-channel APP chip is fabricated. The universality of APP for multifunctional applications is validated through processing broadband radar signals and high-speed communication signals on the single photonic integrated circuit. Its high-resolution-ranging capability is experimentally demonstrated with a resolution up to 2.69 cm. The accurate detection of communication signals with complex modulation format guarantees a communication rate of 8 Gbit/s.

The signal processing for multifunctional integrated systems usually includes down-conversion, filtering, pulse compression, spectrum analysis, signal accumulation, etc33,34. We can decompose such operations into linear multiplication and summation with a specific order, and then implement decomposed processing onto the temporal signal sequence. As digital processing remains the mainstream, multifunctional integrated tasks usually convert the input analog signals into digital signals by ADCs. And store digital signals in memories for subsequent digital signal processing (Fig. 1a). However, for broadband multifunctional integrated systems, high-speed ADCs, and large-capacity memories are essential according to Shannon’s theorem32. Moreover, as the amount of data increases, the requirement of multiplications and summations also grows, thus demanding more computing resources. In the process of the APP (shown in Fig. 1b), the input analog signals are temporally discretized by the optical frequency comb. The optical frequency comb with a high repetition rate realizes high-speed optical discretization. Optical discretization is the pre-processing for parallelization. After the optical discretization, the signals are parallelized through the periodic optical switching window. Temporal discrete signals are routed into 2N parallel sub-sequences, thereby reducing the effective data rate and volume in each computing core. To match the parallel sub-sequences, the coefficients of multipliers are decomposed in the same order and spatially divided into 2 N channels. Multiplication of signal and coefficients in each channel is performed respectively, with the output results from each channel added in pairs to achieve the complete processing result. The clock rate and data volume of each computing core are therefore 2N-time reduced. Memory access rate is also significantly compressed, with the elimination of serial-parallel conversion in traditional electrical parallel processors. Here we take pulse compression in radar signal processing as an example, which is calculated by the convolution of echo analog signal s(t) and the conjugate function of transmitting signal h(t). The computation of pulse compression is represented by:

where h(n) denotes the conjugate function of transmitting signal, s(n) denotes the echo analog signal, and y(n) denotes pulse compression output. The equivalent computation in APP is expressed as:

where hi and sj represent the ith sub-sequence of h(n) and the jth sub-sequence of s(n), respectively. y(n) is the final fused pulse compression output. K stands for the number of hi or sj. sj is generated through the APP chip in the optical domain without memories and controllers for serial-parallel conversion. Detailed descriptions of other calculation decomposing procedure can be found in Supplementary Note 1.

a The workflow of traditional digital processing for multifunctional integrated systems, including high-speed ADCs, large-capacity memories, and high-performance computing cores. b The workflow of APP. The input analog signals are temporally discretized and routed into 2 N parallel sub-sequences in the APP chip. The data rate and volume in each sub-sequence are reduced exponentially. The coefficients of multipliers are decomposed in the same order into 2N channels. Multiplication of signal and coefficients in each channel is performed respectively. The output results from each channel are added in pairs to achieve the complete processing result. c Schematic of the APP chip. MZM mach-zehnder modulator, TDL time delay line, DO-MZM dual-output modulator, PD photodetector. The optical pulses and MZM perform temporal discretization in the optical domain. The DO-MZM is driven by a microwave driving signal to parallelize the temporal discrete signal. Tunable TDL allows adjacent optical pulses to enter corresponding sub-channels without residual components

Following the APP concept, the schematic of the photonic integrated chip is illustrated in Fig. 1c. The optical pulses at the repetition interval of TS are generated by a mode-locked Er-fiber optical frequency comb and coupled to the chip by an on-chip edge coupler. The analog signal is modulated on the optical pulses through the Mach-Zehnder modulator (MZM) biased at its quadrature point, which is temporally discretized for parallelization in the optical domain. Here, the dual-output Mach-Zehnder modulators (DO-MZM) is employed to parallelize the temporal discrete signal35. Two outputs of the DO-MZM correspond to two sub-sequences after each stage parallelization. The principle of optical dynamic phase interference in Supplementary Note 2 reveals a fixed phase difference π between envelopes of optical pulses from each sub-sequence, indicating analog parallelizing based on DO-MZM is inherently phase uniform. Uniform parallelizing without RF phase offset between sub-sequences is critical for the accuracy of analog processing36, and is difficult to be accomplished in electrical domain due to the wiring error, especially when bandwidth increases. Specifically, the tunable optical delay line (TDL) is added before the DO-MZM to allow two adjacent optical pulses to pass through the DO-MZM at the maximal and the minimal intensity transmission levels, respectively37. The DO-MZM is driven by a driving signal at the frequency of fd (fd = 1/2TS) to achieve optical dynamic phase interference. Subsequently, two sub-sequences are aligned via a fixed delay line for synchronization. Photodetectors (PDs) convert the signal in each sub-sequence to electrical signals. Low-speed ADCs and DSPs in each channel perform decomposed computation, subsequently, the complete processing result is achieved through fusing outputs from each channel. The schematic output sequence of each step on our chip is illustrated in Fig. 1c.

Results

The fabricated analog parallel processor chip

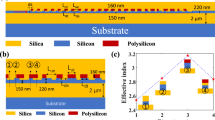

Figure 2a shows the photograph of the APP chip, which is fabricated with a standard Silicon-on-Insulator (SOI) integration process. We implement most of the required optical components onto the chip, including modulator, tunable TDL, fixed TDL, and DO-MZM. The fabricated chip conducts two-channel parallel processing with a discrete data rate of 40 GHz. Duplicating the same structure can expand the number of sub-channels and thus increase the total data rate and data volume. Optical signals enter and leave the chip through the waveguide-fiber edge coupler. Figure 2b depicts the layout of the fabricated APP chip, comprising a modulator, a tunable TDL and a DO-MZM. Figure 2c presents the measured electro-optic (EO) modulation responses of the packaged MZM and the DO-MZM. The EO bandwidth of the MZM ultimately determines the analog input bandwidth of the whole processor. The bandwidth of the DO-MZM determines the frequency range of the driving signal for optical dynamic phase interference and further affects the total data rate38.

As shown in Fig. 2c, the measured 3 dB EO bandwidth is 16.5 GHz and 9.1 GHz for MZM and DO-MZM, respectively. This difference is the result of different reverse-bias voltages applied to PN junctions, which are independently adjusted to match the amplitude of analog input signal onto the MZM and driving signal onto the DO-MZM35. Figure 2d illustrates the characterization result of tunable TDL showing the measured time delay tuning range of 28.99 ps. The discrete data rate of this APP chip is 40 GHz and the repetition interval of optical discrete points is 25 ps, Thus, the on-chip delay tuning range is sufficient. Here, the orange curves are the reference optical output waveforms passing through the corresponding straight waveguide. The light blue, dark blue and purple curves in Fig. 2d are optical output waveforms passing through one waveguide spiral with a designed time delay of 10 ps, one waveguide spiral with a designed time delay of 20 ps, and two waveguide spirals with a total designed time delay of 30 ps, respectively. The difference between the measured value and the designed value is mainly due to the fabrication error. Detailed information on photonic device design and characterization can be found in Supplementary notes 3–4.

a Photograph of the packaged APP chip. Optical signals enter and leave the chip via the edge-coupled fiber. b Layout of the APP chip. The analog signal is temporally discretized through the MZM. The temporal discrete signal is parallelized into two parallel sub-channels by the DO-MZM, with the aid of tunable TDL. c Normalized measured EO modulation responses of the packaged MZM and DO-MZM. d Measured optical output waveforms with a time delay of 8.66 ps (light blue curve), 18.58 ps (dark blue curve), and 28.99 ps (purple curve). Here the orange curve is the measured reference optical output waveform passing through the corresponding straight waveguide

Optical discretization and parallelization

Figure 3a illustrates the experimental setup for validating the optical discretization and parallelization capability of the APP chip (see the “Materials and methods” section for details of the experimental setup). The single-tone signal provided by an analog signal generator is launched to the chip. Figure 3b shows the temporal outputs from two sub-channels, where the frequency of the input single-tone signal is 8.1 GHz. The orange and blue curves represent sub-channel 1 and 2, respectively. After discretization and parallelization, the analog input signal is uniformly converted into two parallel discrete sequences. From the zoom-in plot, the delay between adjacent data points is 50 ps in each sub-channel, corresponding to the data rate of 20 GHz. The delay difference between the two sub-channels is depicted as 25 ps. It means the original discretized signal is temporally divided and reshaped into 2 channels.

a Experimental setup to measure the optical discretization and parallelization capability of the APP chip. PD photodetector, Sync synchronization. b Temporal outputs from two sub-channels when the input single-tone signal is 8.1 GHz. c Measured amplitude ratio response of two sub-channels. d Measured phase difference frequency response between two sub-channels. e Measurement of the SNR over 1 h continuous operation

Since the discrete points in each sub-channel are processed independently and then fused to achieve the results, it is necessary to ensure the amplitude and phase uniformity between the two sub-channels. We measure the amplitude ratio and phase difference of two sub-channels under different input frequencies by gradually tuning the frequency of analog input signal. The output amplitude ratio response of two sub-channels is depicted in Fig. 3c. The measured amplitude ratio is under 0.36 dB within the measured frequency band, which demonstrates great consistency. Taking sub-channel 1 as a reference, the phase difference frequency response is measured and displayed in Fig. 3d. The experimental results (orange dot) are in good agreement with the theoretical phase difference frequency curve for a time delay of 25 ps (blue line). The phase-frequency curve is slightly fluctuant due to some practical limitations such as the nonlinear phase response of off-chip PDs39. The measured amplitude ratio response and phase difference response indicate that these two sub-channels match well in both amplitude and phase. This benefits efficient parallel processing and avoids complex inter-channel calibrations, which are more cumbersome for broadband signals.

The long-term stability of our chip is also evaluated by monitoring the real-time signal-to-noise ratio (SNR) over a 1-hour experiment. The SNR is calculated by the ratio of signal power to integrated noise power in full Nyquist bandwidth. As presented in Fig. 3e, the calculated SNR shows acceptable fluctuations (<0.9 dB), which reveals that photonic integration of main optical components leads to great advances on the robustness of environmental perturbations20.

Broadband multifunctional integrated demonstration using the APP chip

Based on the successful validation of optical discretization and parallelization, we move on to process multiple-waveform broadband signals for different functions, such as radar and communication40,41. To validate the broadband signal processing capacity of our APP chip, we apply it to process broadband LFM radar signals and communication signals in complex modulation formats. Figure 4a displays the structure of the broadband signal parallel processing and the experimental setup is similar to Fig. 3a (details are provided in “Materials and methods”). The input analog signals are temporally discretized and parallelized into sub-sequences with lower data rates in the APP chip. The algorithm and coefficients of multipliers are decomposed in the same order. Output results from each channel are combined in pairs to reconstruct the complete processing result. The instantaneous bandwidth of LFM signals is the determining factor for range resolution in radar function. We generate LFM signals with 6 GHz bandwidth as simulated radar echo signals. The temporal waveforms of LFM signals from each sub-channel and reconstruction result are shown in Fig. 4b. It is observed from the zoom-in plot that the delay between adjacent data points is 50 ps, in each sub-channel. Moreover, the reconstructed waveform is reassembled by rearranging the data from two sub-channels one by one. The range resolution is usually used to characterize the radar detection ability, which is calculated by pulse compression. Here, we conduct the pulse compression by calculating the autocorrelations of obtained temporal waveforms. The pulse compression results are depicted in Fig. 4c. As shown in the zoom-in insets, the experimental resolution is 2.69 cm, which agrees well with theoretical values (2.5 cm for 6 GHz bandwidth LFM signal). The result reveals that the fusion of pulse compression outputs from each sub-channel (blue solid line in Fig. 4c bottom) is consistent with directly processing broadband LFM signal (red dashed line in Fig. 4c bottom). The APP chip owns a flexible processing capability in the range of 2–8 GHz (covering the whole S-band and C-band). Also, we demonstrate the ability to detect multiple targets at multiple distances, Supplementary note S7 describes the details and results of this demonstration. It verifies the feasibility of our APP chip for acquiring high-resolution range profiles. Moreover, it is expected to serve as a processor in inverse synthetic aperture radars for precise target imaging, by employing the coherent accumulation of radar echo signals42.

a Structure of the broadband signal parallel processing. The input analog signals are temporally discretized and parallelized in the APP chip. The algorithm and coefficients of multipliers are decomposed in the same order. Output results from each channel are combined in pairs to reconstruct the complete processing result. b The temporal waveforms from each sub-channel and reconstruction result. The data rate of each sub-channel is 20 GHz and the data rate of reconstructed waveform is 40 GHz. c Pulse compression results of each sub-channel; fusion result of two sub-channels (blue solid line in the bottom); direct processing result (red dashed line in bottom). d Temporal waveforms and constellation diagrams of sub-channel 1 (orange lines) and sub-channel 2 (blue lines). e Fused constellation diagram of two sub-channels (blue dots); direct processing result (red cross dots)

The APP chip further shows flexible processing capability in terms of complex communication signals. The 16-quadrature amplitude modulation (16QAM) signal based on orthogonal frequency division multiplexing (OFDM) is fed into the chip. The bandwidth of the 16QAM signal is 2 GHz, for which the frequency spacing of adjacent subcarriers is 1 MHz and the number of orthogonal subcarriers is 2000. The net communication rate of the 16QAM signal is 8 Gbit/s. The temporal waveforms of sub-channel 1 (orange lines) and sub-channel 2 (blue lines) are recorded in Fig. 4d. Based on temporal waveforms from the two sub-channels, the constellation diagrams after demodulation for each sub-channel are plotted in Fig. 4d. The calculated BER is 1.375 × 10^-2 for sub-channel 1 and 1.35 × 10^-2 for sub-channel 2, no extra error correction adopted. We then combine the demodulation results from sub-channels and plot the fused constellation diagram in Fig. 4e (blue dots). The direct processing result is also plotted in Fig. 4e (red cross dots). The comparison in Fig. 4e shows excellent equivalence of our chip in analog parallel processing. The calculated BER of the combined result is 1.375 × 10^-2. Overall, for advanced communication scenarios, our chip exhibits its broadband and high-speed processing capability.

Discussion

In multifunctional integrated systems, universal processors with ultrabroad bandwidth and high computational accuracy are the common pursuit. We note that the proposed APP chip has the potential to be upgraded toward an ultrabroad one. Recent breakthroughs in electro-optic integrated modulators, on conventional SOI platforms or thin-film lithium niobate platform43,44,45,46,47,48,49, pave the way for a broad modulation bandwidth. Replacing the modulators used in the proposed chip can greatly enhance the analog input bandwidth. On the other hand, to increase the total data rate, cascaded DO-MZMs for constituting more sub-channels are inevitable. In Supplementary material, potential scalability, and total data rate enhancement of APP chip are discussed. As the number of sub-channels goes to 2 N, the total number of tunable TDLs and DO-MZMs both increases to 2N-1, and the insertion loss becomes the primary limitation of chip implementation with the current silicon photonic platform. More critically, the accumulated insertion loss leads to the deterioration of SNR and computational accuracy, which adversely affects the sensitivity in radar systems and the order of modulation format in communication systems. Therefore, in future engineering, the insertion loss of the APP chip should be refined significantly from the following aspects: using advanced fiber-chip coupling50; using low-loss components; using loss compensated modulators based on heterogeneous platform51; using on-chip amplifier52; using on-chip PD to avoid chip-fiber coupling. The whole parallel processing system is supposed to be integrated on the chip towards real-world application scenes, including the optical pulses, optical amplifiers, PDs, and processing cores. With the recent development of heterogeneous or hybrid integration technologies, combining strengths from diverse material platforms and being compatible with CMOS electronics have proven to be a viable paradigm20,53,54,55,56,57,58,59,60. Moreover, cavity-less ultra-short optical pulses based on cascaded modulators, which can produce high-speed optical pulse trains, would also be used to generate optical pulses for temporal discretization. Integrated modulators based on thin-film lithium niobate platforms are beneficial for reducing the size and power consumption of cavity-less optical pulses. It is foreseeable that the SWaP and robustness of the APP chip will be further optimized.

The range resolution is usually used to characterize the radar detection ability, which depends on the bandwidth of LFM radar signals. The relation is Δr = c/2B, where ∆r denotes the range resolution and B is the signal bandwidth. To further improve the range resolution, the analog input bandwidth of the APP chip can be upgraded by expanding the electro-optic bandwidth of the MZM. Besides, our APP chip is capable of processing analog echo signals directly, transforming the analog input signals into parallel sequences with reduced data rate and data volume. These characteristics allow for the processing of larger bandwidth signals to achieve finer resolution, without putting stress on high-speed ADCs and large-capacity memories. Moreover, the signal processing for multifunctional integrated systems can be divided into the combination of dot product, convolution, and basic vector operation as derived in Supplementary notes 1. Thus, although our proof-of-concept experiment was validated for radar and communication signals, the APP chip would be effective for more kinds of signals and improve the collaborative efficiency in multifunctional integrated systems. The direction of arrival estimation, which is a critical technology for multifunctional integrated systems, also needs to develop more effective computing paradigms beyond conventional array signal processing methods61,62.

In conclusion, we propose an integrated analog parallel processor for multifunctional integrated systems. Compared with mainstream digital processors, it is capable of processing broadband signals without extra digital data parallelization and memory use. The optical frequency comb temporally discretizes broadband analog signal and the DO-MZM reshapes discrete signal into 2 N parallel sequences through optical dynamic phase interference. After optical discretization and parallelization, the signal in each sequence is processed by computing cores with reduced clock rate and data volume. The limitation of memory in traditional digital serial-parallel conversion is thus eliminated. In the proof-of-concept experiment, an APP chip based on the silicon photonic platform is fabricated. It performs two-channel parallel processing, exhibiting good amplitude and phase uniformity between two sub-channels. The multifunctional integrated processing is carried out with a ranging resolution of 2.69 cm and a communication rate of 8 Gbit/s. Since the cooperation and mutual promotion of multiple functions have become the main trend, our APP chip will become an effective solution for advanced information systems such as electronic warfare, autonomous driving, and the Internet of Things.

Materials and methods

Experimental setup

The schematic of the experimental setup for optical discretization and parallelization is illustrated in Fig. S5. In the experiment, the optical pulses are generated by the mode-locked Er-fiber optical frequency comb (Calmar PSL-40-TT) with a repetition rate of 40 GHz. The single-tone signal provided by an analog signal generator (Rohde&Schwarz SMA100B) is launched to the on-chip MZM with the aid of an RF balun (Marki BAL-0026). The microwave driving signal (Keysight Technologies, N5183B) for driving the DO-MZM is at 20 GHz and strictly synchronized with the mode-locked Er-fiber optical frequency comb. An RF balun (Marki BAL-0026) is also used to differentially drive the two EO phase shifters of the DO-MZM. Both the MZM and the DO-MZM are biased at the quadrature point. Their desired bias voltages are provided by a home-made multi-channel voltage source and combined with RF signals using bias-tees (Marki BT-0025). For on-chip tunable TDL, the thermal controlling of MZ switches and spiral lines is also supplied by the home-made multi-channel voltage source. The parallel pulses in each sub-channel are amplified by erbium-doped optical fiber amplifiers (EDFA, ASPMEDFA-C-BA-20) and subsequently detected into electrical sequences by PDs (EOT ET-3500F). The gain of the EDFA is 30 dB. The bandwidth and responsivity of PDs is 10 GHz and 0.9 A/W @1550 nm, respectively. A real-time oscilloscope (Keysight Technologies, MSOS804A) is used as EADCs to quantize two electrical sequences, where the oscilloscope has a quantizing rate of 20 GSa/s and an input analog bandwidth of 8.4 GHz.

The process for conceptual multifunctional integrated processing is shown in Fig. 4a, and the experimental setup is similar to that in Fig. S5. In the broadband signal emulator, an arbitrary waveform generator (AWG, Keysight Technologies, M8195A, 65GSa/s) is employed to generate broadband LFM radar signals and complex modulated communication signals. The generated signals are first amplified by a power amplifier (CONNPHY CLN-0.1G20G-3040-S), and then fed into the on-chip MZM. After optical discretization and parallelization, parallel pulses in both sub-channels are amplified by EDFAs (ASPMEDFA-C-BA-20) and converted into electrical sequences by PDs (EOT ET-3500F). Afterwards, the electrical sequences are quantized by the real-time OSC (Keysight Technologies, MSOS804A). The pulse compression and demodulation for each sub-channel as well as the reconstruction for fusion results are implemented by our computer.

Package

The packaged APP chip is shown in Fig. 2a. For optical packaging, customized tapered fiber is employed to match the input fiber waveguide and silicon waveguide mode field, and they are fixed by using ultraviolet curing adhesive. For electrical connections, the RF and DC pads on the chip are wire-bonded to a custom-designed print circuit board (PCB). As the wire bonding for RF connections is critical to the behavior of our chip at high frequencies, we maintain the length of gold wire as short as possible and suppress the crosstalk between adjacent RF channels.

Insertion loss of the APP chip

The insertion loss of the APP chip is mainly composed of several parts: fiber-chip edge coupling, MZM, tunable TDL, DO-MZM, and the waveguide loss from the input to the output of the chip. The insertion loss of fiber-chip edge coupling is around 6.5 dB/facet. It is ~8 dB for the MZM and DO-MZM operating at the quadrature bias point. In the proof-of-concept experiment, the optical power injected into the APP chip is about 13 dBm, and the average output power from each sub-channel is about -22 dBm. In summary, the measured insertion loss of the current version of the APP chip is ~35 dB for each sub-channel, including the coupling loss.

Time delay measurement of tunable TDL

To experimentally characterize the tunable TDL, a pulse generated by a mode-locked Er-fiber optical frequency comb (Calmar PSL-40-TT) at 1550 nm is launched to the tunable TDL and received by a wide-bandwidth oscilloscope (Keysight Technologies, Infiniium DCA-X 86100D). The time interval resolution of this oscilloscope is ≤ 62.5 fs63. The MZ switches in the tunable TDL are switched thermally by heating micro-heaters controlled by a home-made multi-channel voltage source64. Here, we measure optical output waveforms passing through the corresponding straight waveguide as reference (orange curve in Fig. 2d). Optical output waveforms, passing through one waveguide spiral with the designed time delay of 10 ps, one waveguide spiral with the designed time delay of 20 ps and two waveguide spirals with total designed time delay of 30 ps, are also measured and recorded (represented by light blue, dark blue, and purple curves in Fig. 2d). The time delay can be calculated through recorded waveforms.

Amplitude ratio and phase difference measurement of two sub-channels

We quantitatively evaluate the amplitude and phase uniformity between two sub-channels. Optical discretization and parallelization on the APP chip have been regulated to the proper state35. The gain of two off-chip EDFAs and the length of tail fibers are consistent. We input the single-tone signal to the APP chip. The frequency range of the test single-tone signal is 0.1 GHz-7.9 GHz, with a step of 200 MHz. At each frequency, the electrical sequences after quantization in each sub-channel are collected. Fourier transform is then performed and digital spectra for both channels are obtained. We extract amplitude and phase from the digital spectra at each frequency. The amplitude ratio and phase difference of two sub-channels under different input frequencies are calculated and plotted in Fig. 3c and d.

Parallel processing of LFM and 16QAM signal

LFM signals are used in most radar systems to achieve wide operating bandwidth. As a method for improving the range resolution of pulse radar, pulse compression performs a correlation between the received echo signal and the transmitting reference signal, which looks for a strong correlation between them. Traditional pulse compression is calculated by the convolution of the echo signal and the conjugate function of the transmitting signal. With our APP chip, the pulse compression is accomplished by the following steps: (1) obtaining two parallel discrete sequences from our chip; (2) performing the Hilbert transform on the data of two sub-channels independently, and removing the carrier frequency to get s1 and s2; (3) generating the reference signal according to the pulse duration and operating frequency range of echo signal; (4) conjugating the reference signal and separating it into two sequences r1 and r2; (5) obtaining four sets of convolution results between two echo sequences and two reference sequences: Cr1s1, Cr2s2, Cr1s2, and Cr2s1. To achieve the fused pulse compression, we sum up four sets of convolution results according to Eq.2.

QAM signal transmits information by changing both the amplitude and phase of carrier waves, thereby doubling the effective bandwidth. It is thus essential to demodulate 16QAM signals through Fourier transform to obtain symbol information. With our APP chip, the original Fourier transform is deformed and disassembled into two smaller Fourier transforms. Perform Fourier transform on two sub-sequences respectively. According to the basic properties of the Fourier series, the Fourier transform of original 16QAM signals is equivalent to the sum of the Fourier transforms of two sub-sequences, where the Fourier transform of one sub-sequence is multiplied by the phase rotation factor65. Map the demodulated symbol information (including amplitude and phase information) to polar coordinates. Constellation diagrams represent two-dimensional QAM modulation information, the distance from the point to the origin (0,0) representing the amplitude after modulation, and the angle of the point representing the phase after modulation.

Data availability

All data used in this study are available from the corresponding authors upon reasonable request.

References

Liu, F. et al. Joint radar and communication design: applications, state-of-the-art, and the road ahead. IEEE Trans. Commun. 68, 3834–3862 (2020).

Paul, B., Chiriyath, A. R. & Bliss, D. W. Survey of RF communications and sensing convergence research. IEEE Access 5, 252–270 (2017).

Zou, X. H. et al. Multifunctional photonic integrated circuit for diverse microwave signal generation, transmission, and processing. Laser Photonics Rev. 13, 1800240 (2019).

Wang, C. X. et al. On the road to 6G: visions, requirements, key technologies, and testbeds. IEEE Commun. Surv. Tutor. 25, 905–974 (2023).

Hu, Y. et al. An orthogonal hybrid analog–digital multibeam antenna array for millimeter-wave massive MIMO systems. IEEE Trans. Antennas Propag. 69, 1393–1403 (2021).

Zhou, W. X. et al. Integrated sensing and communication waveform design: a survey. IEEE Open J. Commun. Soc. 3, 1930–1949 (2022).

Yan, M. et al. Intelligent resource scheduling for 5G radio access network slicing. IEEE Trans. Vehic. Technol. 68, 7691–7703 (2019).

Wei, J. et al. Highly integrated multifunctional antenna for global navigation satellite system. IEEE Trans. Antennas Propag. 70, 12305–12310 (2022).

Liu, F. et al. Integrated sensing and communications: toward dual-functional wireless networks for 6G and beyond. IEEE J. Sel. Areas Commun. 40, 1728–1767 (2022).

Pérez-López, D. et al. General-purpose programmable photonic processor for advanced radiofrequency applications. Nat. Commun. 15, 1563 (2024).

Ghelfi, P. et al. A fully photonics-based coherent radar system. Nature 507, 341–345 (2014).

Kürner, T., Mittleman, D. M. & Nagatsuma, T. THz Communications: Paving the Way Towards Wireless Tbps. (Cham: Springer, 2022).

Qian, N. et al. Signal-to-noise ratio improvement of photonic time-stretch coherent radar enabling high-sensitivity ultrabroad W-band operation. Opt. Lett. 43, 5869–5872 (2018).

Xu, S. F. et al. Analog spatiotemporal feature extraction for cognitive radio-frequency sensing with integrated photonics. Light Sci. Appl. 13, 50 (2024).

Capmany, J. & Novak, D. Microwave photonics combines two worlds. Nat. Photonics 1, 319–330 (2007).

Marpaung, D., Yao, J. P. & Capmany, J. Integrated microwave photonics. Nat. Photonics 13, 80–90 (2019).

Li, S. M. et al. Chip-based microwave-photonic radar for high-resolution imaging. Laser Photonics Rev. 14, 1900239 (2020).

Shu, H. W. et al. Microcomb-driven silicon photonic systems. Nature 605, 457–463 (2022).

Tao, Z. H. et al. Highly reconfigurable silicon integrated microwave photonic filter towards next-generation wireless communication. Photonics Res. 11, 682–694 (2023).

Tao, Y. S. et al. Fully on-chip microwave photonic instantaneous frequency measurement system. Laser Photonics Rev. 16, 2200158 (2022).

Yao, Y. H. et al. Highly integrated dual-modality microwave frequency identification system. Laser Photonics Rev. 16, 2200006 (2022).

Xu, X. Y. et al. 11 TOPS photonic convolutional accelerator for optical neural networks. Nature 589, 44–51 (2021).

Shastri, B. J. et al. Photonics for artificial intelligence and neuromorphic computing. Nat. Photonics 15, 102–114 (2021).

Xu, S. F. et al. High-order tensor flow processing using integrated photonic circuits. Nat. Commun. 13, 7970 (2022).

Feldmann, J. et al. Parallel convolutional processing using an integrated photonic tensor core. Nature 589, 52–58 (2021).

Zhuang, L. M. et al. Programmable photonic signal processor chip for radiofrequency applications. Optica 2, 854–859 (2015).

Capmany, J., Gasulla, I. & Pérez, D. The programmable processor. Nat. Photonics 10, 6–8 (2016).

Liu, W. L. et al. A fully reconfigurable photonic integrated signal processor. Nat. Photonics 10, 190–195 (2016).

Pérez, D. et al. Multipurpose silicon photonics signal processor core. Nat. Commun. 8, 636 (2017).

Hu, J. Q. et al. Reconfigurable radiofrequency filters based on versatile soliton microcombs. Nat. Commun. 11, 4377 (2020).

Efnusheva, D., Cholakoska, A. & Tentov, A. A survey of different approaches for overcoming the processor - memory bottleneck. Int. J. Comput. Sci. Inf. Technol. 9, 151–163 (2017).

Schmidt, C. et al. Data converter interleaving: current trends and future perspectives. IEEE Commun. Mag. 58, 19–25 (2020).

Chen, V. C. & Martorella, M. Inverse Synthetic Aperture Radar Imaging: Principles, Algorithms and Applications. (Edison: IET, 2014).

Zhang, J. A. et al. An overview of signal processing techniques for joint communication and radar sensing. IEEE J. Sel. Top. Signal Process. 15, 1295–1315 (2021).

Qian, N. et al. Influence of the demultiplexer on channel-interleaved photonic analog-to-digital converters. IEEE Photonics J. 12, 5502110 (2020).

Flatt, H. P. & Kennedy, K. Performance of parallel processors. Parallel Comput. 12, 1–20 (1989).

Scotti, F. et al. High precision photonic ADC with four time-domain-demultiplexed interleaved channels. Proceedings of 2013 18th OptoElectronics and Communications Conference Held Jointly with 2013 International Conference on Photonics in Switching. Kyoto, Japan: IEEE, 2013, 1-2.

Xu, S. F. et al. Deep-learning-powered photonic analog-to-digital conversion. Light Sci. Appl. 8, 66 (2019).

Qin, R. H. et al. Decoupling and one-time elimination of the timing skew in a time-demultiplexing photonic analog-to-digital converter for high-resolution wideband signal acquisition. Opt. Lett. 48, 5324–5327 (2023).

Tavik, G. C. et al. The advanced multifunction RF concept. IEEE Trans. Microw. Theory Tech. 53, 1009–1020 (2005).

Nie, H. J. et al. Photonics-based integrated communication and radar system. Proceedings of 2019 International Topical Meeting on Microwave Photonics. Ottawa, ON, Canada: IEEE, 2019, 1-4.

Deng, A. Y. et al. High-resolution ISAR imaging based on photonic receiving for high-accuracy automatic target recognition. Opt. Express 30, 20580–20588 (2022).

Han, C. H. et al. Ultra-compact silicon modulator with 110 GHz bandwidth. Proceedings of 2022 Optical Fiber Communications Conference and Exhibition. San Diego, CA, USA: IEEE, 2022, 1-3.

Rahim, A. et al. Taking silicon photonics modulators to a higher performance level: state-of-the-art and a review of new technologies. Adv. Photonics 3, 024003 (2021).

Li, K. et al. Electronic–photonic convergence for silicon photonics transmitters beyond 100 Gbps on-off keying. Optica 7, 1514–1516 (2020).

Weigel, P. O. et al. Bonded thin film lithium niobate modulator on a silicon photonics platform exceeding 100 GHz 3-dB electrical modulation bandwidth. Opt. Express 26, 23728–23739 (2018).

Wang, C. et al. Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages. Nature 562, 101–104 (2018).

Zhang, Y. W. et al. Systematic investigation of millimeter-wave optic modulation performance in thin-film lithium niobate. Photonics Res. 10, 2380–2387 (2022).

Wang, J. et al. Engineering a sandwiched Si/I/LNOI structure for 180-GHz-bandwidth electro-optic modulator with fabrication tolerances. Opt. Express 30, 35398–35408 (2022).

Billah, M. R. et al. Hybrid integration of silicon photonics circuits and InP lasers by photonic wire bonding. Optica 5, 876–883 (2018).

Wang, J., Xiong, N. N. & Zou, W. W. Loss compensation of an ultra-wideband electro-optic modulator in heterogeneous silicon/erbium-doped lithium niobate. Opt. Lett. 48, 3399–3402 (2023).

Liu, Y. et al. A photonic integrated circuit–based erbium-doped amplifier. Science 376, 1309–1313 (2022).

Wan, Y. T. et al. High speed evanescent quantum-dot lasers on Si. Laser Photonics Rev. 15, 2100057 (2021).

Xiang, C. et al. Laser soliton microcombs heterogeneously integrated on silicon. Science 373, 99–103 (2021).

Xiang, C. et al. High-performance lasers for fully integrated silicon nitride photonics. Nat. Commun. 12, 6650 (2021).

Zhang, J. et al. III-V-on-Si photonic integrated circuits realized using micro-transfer-printing. APL Photonics 4, 110803 (2019).

Haq, B. et al. Micro-transfer-printed III-V-on-silicon C-band semiconductor optical amplifiers. Laser Photonics Rev. 14, 1900364 (2020).

Theurer, M. et al. Flip-chip integration of InP to SiN photonic integrated circuits. J. Lightw. Technol. 38, 2630–2636 (2020).

Lin, S. Y. et al. Efficient, tunable flip-chip-integrated III-V/Si hybrid external-cavity laser array. Opt. Express 24, 21454–21462 (2016).

Wang, J. et al. Toward photonic–electronic convergence based on heterogeneous platform of merging lithium niobate into silicon. J. Opt.Soc. Am. B 40, 1573–1590 (2023).

Gao, S. et al. Super-resolution diffractive neural network for all-optical direction of arrival estimation beyond diffraction limits. Light Sci. Appl. 13, 161 (2024).

Gao, S., Wu, C. & Lin, X. Demixing microwave signals using system-on-chip photonic processor. Light Sci. Appl. 13, 58 (2024).

KEYSIGHT. 86100D DCA-X. at https://www.keysight.com/us/en/assets/7018-02546/data-sheets-archived/5990-5824.pdf URL.

Hong, S. H. et al. Ultralow-loss compact silicon photonic waveguide spirals and delay lines. Photonics Res. 10, 1–7 (2022).

Oppenheim A. V. & Schafer, R. W. Digital Signal Processing. (Englewood: Prentice Hall, 1975).

Acknowledgements

This work is supported in part by the National Natural Science Foundation of China (T2225023, 62205202); and the Shanghai Sailing Program (No. 22YF1420200). We thank Prof. J. Liu and Dr. Z. Zhang for their help in packaging.

Author information

Authors and Affiliations

Contributions

W.Z. and N.Q. conceptualized this study. N.Q. and D.Z. came up with the methods. H.S. and M.Z. designed the chip layout. N.Q. and D.Z. carried out experiments and obtained data. N.Q. and D.Z. visualized the data. W.Z., X.W., D.D., and X.D. supervised the work. N.Q. wrote the original manuscript. N.Q. and W.Z. revised and edited the manuscript. W.Z. funded this study.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Supplementary information

41377_2025_1753_MOESM1_ESM.docx

Supplementary Information for Analog parallel processor for broadband multifunctional integrated system based on silicon photonic platform

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Qian, N., Zhou, D., Shu, H. et al. Analog parallel processor for broadband multifunctional integrated system based on silicon photonic platform. Light Sci Appl 14, 71 (2025). https://doi.org/10.1038/s41377-025-01753-w

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41377-025-01753-w

This article is cited by

-

High-performance analog signal processing with photonic integrated circuits

Light: Science & Applications (2025)

-

Silicon integrated microwave photonics

Science China Information Sciences (2025)