Abstract

Two-dimensional (2D) semiconductors hold great promise for future electronics, yet the fabrication of clean ohmic electrical contacts remains a key challenge. Traditional lithography and metallization processes often introduce interfacial disorder, and recently developed electrode-transfer-based techniques are difficult to implement without contaminating the interfaces between 2D crystals and metals. Here, we demonstrate a low-temperature chemical vapor deposition (CVD)-based van der Waals (vdW) epitaxy method to grow 2D metal (Cd) electrodes, eliminating lithography, deposition, or transfer processes and enabling the damage-free integration of 2D semiconductors. This thermodynamic integration strategy significantly mitigates the interfacial disorder and metal-induced gap states (MIGS), leading to low contact resistance (RC) and near-zero barrier ohmic contacts. Cd-MoS2 field-effect transistors (FETs) exhibit RC down to 70–100 Ω·μm, on-state current densities up to 942 μA/μm, on/off ratios exceeding 108, and mobilities up to 160 cm2 V−1 s−1. These results position vdW epitaxially grown 2D metals as a promising contact technology for next-generation electronics beyond silicon.

Similar content being viewed by others

Introduction

Silicon transistor technology has reached a critical point after experiencing significant advancement according to the Moore’s law1. 2D semiconductors exhibit electrical transport properties superior to silicon in extreme miniaturization and remarkable hetero-integration ability, thus becoming the most promising candidate for the electronics beyond silicon2,3,4. The issue of RC at the metal-2D semiconductor interface has become increasingly crucial, hindering the further downsizing of electronic devices and limiting the performance improvements of next-generation electronics1,5,6. The electronic contact problem roots in a high Schottky barrier. This barrier arises from strong Fermi level pinning (FLP), which occurs due to the formation of two types of gap states: MIGS7 and defect-induced gap states (DIGS)8. MIGS result from the rehybridization of the metal’s extended wavefunction with that of the semiconductor, while DIGS are created during traditional deposition and doping methods9,10.

Both the academic and industrial communities have made substantial efforts to address the electronic contact issue, primarily through two approaches. The first approach focuses on the contact electrodes, involving techniques such as electrode transfer8, low-energy deposition of materials like indium11, deposition of semimetals like bismuth and antimony7,12, growth or conversion of semimetal nanosheets particularly transition metal dichalcogenides (TMDs) as electrodes13, and the insertion of buffer layers to decouple the interactions between metal and semiconductor14. The second approach targets the material itself, aiming to heavily dope the semiconductor to reduce the width of the Schottky barrier, thereby encouraging tunneling current to exceed the thermionic emission current across the barrier15,16. However, despite these efforts, problems persist. The deposited semimetal electrodes still suffer from thermal instability or surface roughness (Supplementary Fig. 1a, b). Besides, these methods require conventional lithography, evaporation and lift-off process in the contact formation with photoresist residues which probably affects device performance. Evaporation deposition can easily create interfacial disorder and DIGS due to the high energy cluster implantation. Lift-off process can also damage the materials. Moreover, growth or phase conversion of semimetal TMDs or metal nanosheets for contacts usually requires high temperature1,10,13,17,18,19,20,21, which can deteriorate existing materials and are not compatible with the back-end-of-line (BEOL) integration temperatures (<400 °C) in microelectronics. Furthermore, the transfer electrode method for creating interfaces between metals and 2D semiconductors inevitably introduces contamination (adsorbed water or hydrocarbon), wrinkles and bubbles22, and the yield is low. Therefore, it is impossible to obtain a perfect interface with the most thermodynamic stability. Moreover, the heavy doping for monolayer 2D semiconductors remains highly challenging and brings about defects, degrading the transport properties23,24,25,26. Hence, there is a pressing need to explore more favorable vdW contact interface that can further improve contact performance, posing a significant scientific and technological research question5.

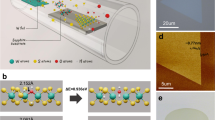

In this study, we present a method of vdW epitaxy for 2D metal, which constructs an atomically thin and perfect vdW interface. The epitaxy is through CVD which is widely employed in industrial settings. It eliminates the need for lithography techniques in the contact formation. This approach facilitates formation of the ohmic contacts with a suitable work function that matches the electron affinity of the MoS2 channel, and effectively reduces the interfacial disorder and RC. The MIGS is effectively suppressed. We successfully prepared vertically epitaxial vdW Cd contacts at BEOL friendly temperatures below 400 °C27, which is essential to prevent damage to the 2D materials. Monolayer MoS2 transistors with channel length (LCH) under 100 nm were fabricated. The Cd (001) face grows parallel to the MoS2 (001) crystal plane. By precisely controlling growth time and temperature, we varied the LCH ranging from 48 to 300 nm, without relying on conventional photolithography and metallization process. Cd-MoS2 FETs exhibit high overall performance, including a low RC of 70–100 Ω·µm, a high on-state current density of 788 μA/μm (LCH = 100 nm), 942 μA/μm (LCH = 50 nm), an on/off ratio exceeding 108, a small hysteresis window of 112 mV/(MV cm⁻¹), along with a high mobility of up to 160 cm2 V−1 s−1.

Results

Material growth, characterizations and theoretical analysis

The low work function metal Cd is selected as the contact material for the following considerations. First, the Schottky barrier height between a metal and n-type semiconductor is defined as ΦB = ΦM − χ, where ΦB is the Schottky barrier height, ΦM is the work function of the metal and χ is the electron affinity of the semiconductor. Since the Fermi level (EF) of Cd metal is close to the conduction band minimum of MoS2 and the difference between the work function of the metal Cd (4.34 eV, measured from Kelvin probe force microscopy, KPFM) and the electron affinity of the semiconductor MoS2 (4.35 eV from ref. 21) is small (Fig. 1a). Second, first-principles calculations using density functional theory (DFT) were carried out for the Cd metal epitaxially grown on the MoS2 surface (Fig. 1b). The tunneling barrier of Cd has a smaller height and width (height, Φt = 3.14 eV; width, wt = 1.61 Å), compared to the Bi semimetal (Φt = 3.6 eV; wt = 1.66 Å)7. The calculated tunneling-specific resistivity (ρt) ≈ 1.7 × 10−9 Ω cm2 for Cd-MoS2 contact, lower than 1.81 × 10−9 Ω cm2 of Bi-MoS2 contact (Methods)7. The calculations show that the 2D Cd tends to grow along the (001) plane on 2H-MoS2 (001) crystallographic plane, in which the free energy increase is the lowest, meaning that the Cd-MoS2 heterostructure grows in a parallel manner until Cd fully covers MoS2. We also calculated the projected density of states (DOS) of MoS₂ before (Fig. 1c i) and after (Fig. 1c ii) contact with Cd (001). When MoS₂ is in contact with Cd, the EF of MoS₂ moves from within the band gap to the conduction band minimum at the interface7,28. The small amount of MIGS distributed within the band gap will be filled by electrons below EF, resulting in the saturation of the gap states and making MIGS negligible (Fig. 1d i). The projected DOS of some common electrode metals were also calculated (Supplementary Fig. 2a-f), revealing that the DOS of Cd (001) is smaller than that of other metals. In this scenario, the semiconductor at the metal-semiconductor contact will be in a degenerate doped state, the FLP will be significantly alleviated, and the Schottky barrier will be significantly reduced, favoring ohmic contact (Fig. 1d ii). Third, the melting point of Cd is relatively low (321.07 °C), enabling epitaxially growing 2D metal Cd on MoS2 through vapor deposition at a BEOL friendly temperature (~108 °C on downstream growth substrate). Figure 1e shows the comparison of the growth temperature of this work with previous reports of using grown or phase-converted semimetal TMDs or metal nanosheets as contacts1,10,13,17,18,19,20,21 (Supplementary Table 1). The vdW epitaxy in a low-energy, damage-free manner is expected to prevent damage to the 2D material and result in a perfect interface29.

a The band alignment of monolayer MoS2 with metals (Cd, Au). Evac, Ec, Ev and Eg represent the vacuum level, the conduction band minimum, the valence band maximum, and the band gap, respectively. b The corresponding electrostatic potential distribution for Cd (001)-MoS2 (001) along the vertical direction. The electron tunneling barrier of Cd (height, Φt = 3.14 eV; width, wt = 1.61 Å) c The density of states (DOS) distribution before (i) and after (ii) the contact between Cd metal and the semiconductor. The valence band (VB) is shaded in light red, while the conduction band (CB) is shaded in light blue. The Fermi level (EF), indicated by the dash-line moves from within the gap (before Cd contact) to above the conduction band minimum (after Cd contact). d The schematic illustrations of the energy band structures and the interface interactions of the metal-semiconductor Au-MoS2 and Cd-MoS2 contacts. The gap states pinning in Au-MoS2 forms a Schottky barrier with a height (ΦSB), while the suppressed gap states in Cd-MoS2 contacts facilitate the formation of ohmic contacts. Metal-induced gap states (MIGS) and defect-induced gap states (DIGS) are located within the band gap. e Comparison of the growth temperatures of 11 reported grown or phase-converted semimetal transition metal dichalcogenides (TMDs) or metal nanosheets1,10,13,17,18,19,20,21. The back-end-of-line (BEOL) temperature limit is indicated by the dash-line. The specific parameters are listed in Supplementary Table 1.

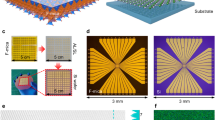

Under the theoretical guidance, we employed a two-step method to grow the 2D Cd electrode via vdW epitaxy (the growth schematic illustration is in Supplementary Fig. 3a–c, and the growth details are in Methods). The monolayer MoS2 was used as a substrate for the vdW epitaxial growth of 2D metal Cd nanosheets. The epitaxially grown Cd nanosheets exhibited a clear vdW epitaxial relationship, maintaining the triangular or hexagonal geometries aligned with that of MoS2 flake (Supplementary Fig. 4a–c). During the growth process, by controlling the growth time and the reaction temperature, the lateral dimensions of the 2D Cd metal can be adjusted and neighboring hexagonal Cd nanosheets gradually adjoined together to form nanosheet pairs. After the reaction, the furnace was opened to rapidly cool to room temperature, revealing that the adjacent hexagonal Cd domains had not fully merged at the grain edges. The in-between gap provides a material basis for achieving atomically thin MoS2 transistor channel without the need for conventional techniques of lithography and metal deposition1. Supplementary Fig. 4d displays an optical microscopy (OM) image of large-size 2D Cd. Supplementary Fig. 4e presents scanning electron microscopy (SEM) images of the gaps between pairs of hexagonal Cd on MoS2 varying from 303 nm down to 48 nm. Supplementary Fig. 4f shows that the two vibrational Raman modes at 385.3 cm−1 (\({E}_{2{{\rm{g}}}}^{1}\)) and 402.2 cm−1 (\({A}_{1{{\rm{g}}}}\)) are pronounced, suggesting the intactness of underlying monolayer MoS2. Photoluminescence (PL) spectra and mapping in Supplementary Fig. 4g, h show that there is no defect-related emission after the deposition of Cd. At the heterostructure region, the PL is totally quenched. Figure 2a, b shows the atomic force microscopy (AFM) and KPFM characterization of the thickness and work function of the grown 2D Cd-MoS2 heterostructure. The synthesized 2D metal Cd thickness ranges from 13 nm to 100 nm, and the potential difference between Cd and MoS2 is 120 mV, allowing us to calculate the work function of Cd as 4.34 eV and that of MoS2 as 4.52 eV.

a Atomic force microscopy (AFM) characterization of Cd-MoS2. b Kelvin probe force microscopy (KPFM) characterization of Cd-MoS2. c Energy-dispersive X-ray spectroscopy (EDS) elemental mapping of Cd nanosheets with the corresponding high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image. Inset: scale bar, 500 nm. d The selected-area electron diffraction (SAED) pattern of the epitaxial Cd-MoS₂. e HAADF-STEM image of the Cd nanosheets, with the corresponding atomic-model illustration highlighted in purple. f HAADF-STEM image of the Cd (001)-MoS2 (001) contact. g Atomic resolution image obtained from the white frame in (f). Mo, S, and Cd atoms are marked, with the interplanar distance of the Cd (001) plane labeled as 2.62 Å. The interatomic distance between Mo and Cd is labeled as 4.84 Å. The vdW gap distance of Cd-S is 1.06 Å. EDS elemental mapping images of Cd (h), S (i), Mo (j), and Si (k) on a 300 nm SiO2 substrate.

The crystal structure of the Cd nanosheets was studied using high-angle annular dark field scanning transmission electron microscopy (HAADF-STEM). The HAADF-STEM image and the corresponding transmission electron energy dispersive spectroscopy (TEM-EDS) mapping (Fig. 2c) indicate a uniform distribution of Cd. The DFT calculations results show the A-A stacking manner of Cd plane exactly parallel to the MoS2 (001) crystal plane is most favorable (Supplementary Fig. 5a). The two sets of hexagonal spot patterns in selected area electron diffraction (SAED) of MoS2-Cd heterostructure (Fig. 2d) confirm the above-mentioned epitaxy relationship and the SAED pattern of merely 2D Cd shows one set hexagonal spot pattern (Supplementary Fig. 5b). The corresponding HAADF-STEM image (Fig. 2e) show that the lattice spacing of the nanosheets is 0.26 nm, consistent with the lattice spacing in the Cd (001) crystal plane.

Cross-sectional HAADF-STEM was also performed to further evaluate the interface characteristics of monolayer MoS2 and vertically synthesized Cd in vdW contact30. Figure 2f presents a typical HAADF-STEM cross-sectional image of the Cd-MoS2 heterostructure on a 300 nm SiO2 substrate. The STEM imaging reveals a perfect close interfacing between the crystalline Cd and MoS2, with no metal-induced defects observed. Additionally, the enlarged STEM image (Fig. 2g) shows an interface at the Cd-MoS2 junction with atomic sharpness and cleanliness, without significant impurities or atomic mixing between the two materials. The distance between Cd atomic planes parallel to MoS2, measured in HAADF-STEM image, is 2.62 Å, further confirming the (001) crystal plane. Theoretically, the vdW gap distance between the S atoms and Cd atoms can be calculated using the formula14:

where \({D}_{{{\rm{Mo}}}-{{\rm{Cd}}}}\) is the distance between the Mo atom and the Cd atom in the interface, \({D}_{{{\rm{Mo}}}-{{\rm{S}}}}\) is the distance between the Mo atom plane and S atom plane in MoS2, \({R}_{{{\rm{Cd}}}}^{{{\rm{vdw}}}}\), \({R}_{{{\rm{S}}}}^{{{\rm{vdw}}}}\) are the vdW radius of Cd and S respectively31. The vdW gap \({g}_{{{\rm{vdw}}}}\) is the distance between S and Cd. The measured \({D}_{{{\rm{Mo}}}-{{\rm{Cd}}}}\) ≈ 4.84 Å. Given that \({R}_{{{\rm{Cd}}}}^{{{\rm{vdw}}}}\) and \({R}_{{{\rm{S}}}}^{{{\rm{vdw}}}}\) are 1.58 Å and 1.80 Å respectively32, and \({D}_{{{\rm{Mo}}}-{{\rm{S}}}}+{R}_{{{\rm{S}}}}^{{{\rm{vdw}}}}\) is 2.2 Å33, the calculated \({g}_{{{\rm{vdw}}}}\) is approximately 1.06 Å, which is smaller than those of MoS2-Sb (01\(\bar{1}\)2)12 and MoS2-Bi (0001)7, confirming the formation of an ideal vdW contact (Supplementary Table 2). Furthermore, Supplementary Table 2 also shows that this \({g}_{{{\rm{vdw}}}}\) distance is smaller than the vdW gap distance of the transferred electrode interface MoS2-Au8, ReSe2-Au34, the distance of transferred gate dielectric interfaces17,35, PPC-transferred vdW metal electrode interface36, and near-ideal vdW interfaces by the deposition process (Pt, Pd, In)11,37, implying a smaller tunneling barrier in MoS2-Cd case. Moreover, Fig. 2h–k indicate the corresponding elemental distribution maps of Cd, Mo, S and Si respectively, further revealing a clear spatially resolved element distribution at the Cd-MoS2 interface. The Raman spectrum of the Cd-MoS2 heterostructure (Supplementary Fig. 4f) shows no peaks associated with nonstoichiometric MoxSy38.

Besides, X-ray diffraction (XRD) characterization (Supplementary Fig. 6a) indicates that Cd grows parallel to the (001) crystal plane on MoS2, confirming the vdW epitaxial crystallographic alignment with the theoretical calculations and the HAADF-STEM results. X-ray photoelectron spectroscopy (XPS) was also conducted to investigate the chemical states of the Cd-MoS2 interface. The spectra obtained from Cd-MoS2 (Supplementary Fig. 6b) show features almost identical to those of pristine MoS2, suggesting that Cd-MoS2 does not introduce any chemical reactions, defects, or strains at the interface or within the MoS238. In addition, the blue shift of the Mo 3d and S 2s peaks in the XPS spectra reveals that the EF increases upon contact of MoS2 with Cd, indicating electron doping7,39, in agreement with the band alignment shown in Fig. 1.

These characterizations indicate that Cd grows on MoS2 in a vdW manner without causing damage to the underlying MoS2, with its intrinsic lattice structure and physical properties remaining largely unchanged, definitely superior than the interface created by conventional metal deposition reported in previous literatures8,33. In addition, this thermodynamically stable hetero-integration strategy should be preferable to other means such as manually mechanical vdW stacking, offering an interface free of contaminations, wrinkles, bubbles and with a minimal vdW gap distance. Such a clean interface of 2D metal/2D semiconductor contacts would offer a nearly ideal ΦSB dictated by the metal work function/semiconductor electron affinity and translate into high performances of devices.

Electrical performance of sub-100-nm monolayer MoS2 transistors

Cd-MoS2 back-gated FETs were fabricated on a 300 nm SiO2 substrate, where adjacent vdW epitaxial Cd nanosheets on MoS2 served as the source and drain contacts. Figure 3a illustrates the device structure schematics of the two-dimensional FETs with a monolayer MoS2 channel and Cd contacts. Figure 3b presents the typical transfer characteristics of monolayer MoS2 FETs with Cd contacts (drain-to-source current, IDS, versus gate-to-source voltage, VGS). The Cd-MoS2 FETs exhibit clearly n polarity with a high on/off ratio greater than 108. Figure 3c presents the output characteristics of monolayer MoS2 FETs with Cd contacts (drain-to-source current IDS, versus drain-to-source voltage VDS), where the current saturation occurs at VDS larger than 2 V. At VDS = 3 V and VGS = 70 V, the on-state current density reaches 788 μA/μm. The inset displays linear output characteristics at room temperature, indicating ohmic contact properties. The RC is as low as 70 Ω⋅μm (Fig. 3f) at a carrier density (n2D) of 5.58 × 1012 cm−2 using transfer length method (TLM).

a Schematic illustration of a 2D FET with a monolayer MoS2 channel and Cd contacts. The electrodes consist of 40-nm-thick Cd capped with 30-nm-thick Au. b Room temperature transfer characteristics curve (IDS-VGS) for Cd-MoS2 FETs on a 300 nm thick SiO2 dielectric. The inset shows a scanning electron microscopy (SEM) image of the device, where LCH indicates the channel length. c Typical output characteristic curves (IDS-VDS) for Cd-MoS2 FETs at room temperature, with the inset showing the IDS-VDS for (VGS changes from –60 V to 60 V, VDS = 1 V). d RC of Cd-MoS2 FETs extracted using the transfer length method (TLM) on a 300 nm thick SiO2 dielectrics. Blue squares, circles, and triangles represent the relationship between total resistance (RTotal) and LCH at carrier densities of 4.13 × 1012, 4.85 × 1012, and 5.58 × 1012 cm–2, respectively. The dash-line represents the linear fitting. e, f Comparison of the IDS-VGS and IDS-VDS characteristics for typical monolayer MoS2 FETs with Cd and Cr/Au contacts respectively at 300 K.

Figure 3e, f compares the transfer and output characteristics of MoS₂ FETs with conventional evaporated Cr/Au contacts and epitaxially grown Cd electrodes. Under VDS = 1 V and VGS = 60 V, the Cd-MoS₂ FET exhibits an on/off ratio of approximately 108 (3 orders of magnitude higher than that of the Cr/Au-MoS₂ FET), with an on-state current density that is 30 times higher than that of the Cr/Au-MoS₂ FET. The monolayer MoS₂ FET with Cr/Au contacts shows distinct Schottky contact characteristics at room temperature. When the LCH of the Cd-MoS2 FET reaches down to 50 nm, the electrical characterization curves show well-defined transfer curve and Ohmic output curve, with on/off ratio of 106 (VDS = 0.2 V), on-current density of 942 μA/μm (Supplementary Fig. 7a–c).

Furthermore, recently, transferred metal electrodes are also reported as a possible route to enhance the contact quality40, and we employed transferred metal electrodes and thermally deposited semimetal Bi electrodes for comparison with our 2D metal contact. Supplementary Fig. 8a–c compare the transfer and output characteristics of the same channel-length MoS2 FETs with contacts made from transferred Au electrodes, deposited semi-metallic Bi electrodes, and epitaxially grown Cd electrodes. All these three show good ohmic contact properties in output characteristics (Supplementary Fig. 8a1, b1, c1). However, at the same voltage, both the on-state current density and the on-off ratio decrease in the order of Cd-MoS₂, Bi-MoS₂, and transferred Au-MoS₂ FETs.

Figure 4a and Supplementary Fig. 9a display temperature-dependent transfer characteristic curves for the Cd and Cr/Au contacts. Each ΦSB at the Cd-MoS2 and Cr/Au-MoS2 interfaces was extracted from the slope of the Arrhenius plot ln (IDS/T1.5) ~ q/kT at varying gate voltages (Fig. 4b, Supplementary Fig. 9b). The ΦSB for Cd-MoS2 approaches zero in the flat-band regime in Fig. 4c, while that for Cr/Au-MoS2 is 90 meV (Supplementary Fig. 9c). In comparison, the barrier height at the Cd-MoS2 interface can be modulated more effectively than that at the Cr/Au-MoS2 interface. When VGS = -5 V, the Cd contact achieves ohmic contact, with the barrier height approaching zero.

a Temperature-dependent IDS-VGS for Cd-MoS2 FETs. b Arrhenius plots for varying gate voltages in the same Cd-MoS2 device (VGS from –25 V to 40 V). The dash-line represents the linear fitting. c Extracted ΦSB at flat-band regime for Cd-MoS₂ FETs, which corresponds to the onset of deviation from linear behavior (black dash-line). The magnitude of the extracted contact barrier can almost be neglected. The inset illustrates the linear output characteristics at low temperature. d Temperature dependence of the field effect mobility of Cd-MoS2 FETs (μ\(\propto\)T-γ). Comparison of hysteresis windows in MoS2 FETs with Cd (e) and Cr/Au (f) contacts at 300 K.

Figure 4d displays the temperature dependence of the mobility. With increasing temperature, the field effect mobility of the Cd-MoS2 FET initially varies not largely (rises in small magnitude) then decreases. The temperature dependence of the mobility is fitted with the power law relation μ ∝ T-γ in the range of 180 K to 300 K, yielding a small negative power index (γ = 0.59), which is superior to the –1.5 power law from the conventional lattice scattering theory41, indicating that carrier scattering effects are diminished in this case and electronic transport performance is improved. In the temperature range of 30–180 K, the observed mobility shows a nearly saturating behavior with temperature, suggesting that the carrier scattering influence is alleviated by good crystallinity and interface quality. Note these mobilities surpass ultrathin silicon (<2 nm) and germanium (<4 nm) on insulator devices42.

To evaluate the thermal stability of the Cd-MoS2 contacts, the devices were heated from 290 K to 423 K in vacuum and maintained at the temperature for 12 h. The morphology of Cd remains intact and smooth (Supplementary Fig. 10a), compared to the semimetals in Supplementary Fig. 1. Supplementary Fig. 10b-e show the transfer and output characteristics before and after the thermal stress test, which remain almost unchanged. The linear slope in the output curve exhibits that contact remains perfectly ohmic. To explore the temperature tolerance of the Cd-MoS₂ contacts, we gradually increased the temperature from 373 K to 590 K and precisely tested the electrical characteristic curves every 30 K to observe the degradation of performance. We found that the device performance did not show obvious degradation until 570 K (VDS = 0.5 V) (Supplementary Fig. 10f–h). Meanwhile, we conducted a time stability test on the Cd-MoS₂ FET. As shown in Supplementary Fig. 11a–c, the electrical properties of this Cd-MoS₂ FET remained nearly unchanged after 60 days, exhibiting good time stability. In addition, to probe the electric field endurance of the epitaxially grown Cd electrodes, an electric field stress test was performed on the Au/2D Cd/Au junction as shown in Supplementary Fig. 12a. Supplementary Fig. 12b shows the electrical curve of the device, confirming the metallic nature of 2D Cd. Supplementary Fig. 12c shows the breakdown electric field is 0.35 MV/cm, more than 10 times higher than that of the air43. Figure 4e, f compares the hysteresis windows of MoS2 FETs with Cd and Cr/Au contacts. The hysteresis window of the Cd-MoS2 device (~1 V) is much smaller than that of Cr/Au-MoS2 device (15 V), due to the significantly lower interface states and thereby less carrier trapping/detrapping44.

Supplementary Fig. 13 compares the results of the gate leakage current tests of MoS2 FETs with Cd and Cr/Au contacts. The gate leakage current density with Cr/Au contact is one order of magnitude higher than that with Cd contact, showing a steeper slope (5 × 10−3 vs. 4.4 × 10−3 A·V−1 cm−2). This is likely due to the direct electrode metal-substrate contact caused by diffusion, metal cluster permeation, and MoS2 layer damage during traditional PVD of Cr/Au8,33. In addition, chromium has very strong adhesion ability to SiO245. These factors increase the leakage current. Gate leakage current density J of the Cd-MoS2 device is smaller than 1.5 × 10−2 A cm−2, meeting the IRDS requirements for low-power devices46.

In summary, we provide three pieces of evidence indicating the absence of a Schottky barrier in Cd-MoS2 FETs. First, the RC in Cd-MoS2 FETs is almost independent of n2D, indicating an almost negligible barrier at the Cd-MoS2 interface. Second, the flat-band Schottky barrier extracted from the temperature-dependent IDS measurements for Cd-MoS2 FETs is close to zero. Third, a regime resembling saturation appears at lower temperatures (<200 K), suggesting a negligible contact barrier height for electron transport, and the IDS-VDS curve of the Cd-MoS2 FETs remains linear at low temperatures (Fig. 4c inset)7.

Comprehensive evaluations of 2D Cd-MoS2 FETs’ performance metrics

Next, we evaluate the uniformity of electronic characteristics of locally back-gated MoS2 devices with vdW Cd contacts. First, monolayer MoS2 transistors with six different short-channel lengths exhibit an on-state current density above 300 μA/μm at relatively low VDS (Supplementary Fig. 14a–f), indicating good electrical performance in 2D TMD transistors. For example, in a device with LCH = 75 nm, the transfer characteristics of this device reveal an on/off ratio as high as 108 when VDS ≤ 1.0 V; an on-state current density of 771 μA/μm was achieved at VDS = 3.0 (Supplementary Fig. 14a). Additionally, when LCH = 600 nm, an on-state current density of 400 μA/μm was realized at VDS = 2.5 V. (Supplementary Fig. 14f2). The output curves show a linear feature at low bias, indicating good contact qualities.

In order to clarify the origin of high performance, Fig. 5a, b and Supplementary Fig. 15 compare the electric field distribution inside short-channel (LCH = 100 nm) MoS2 FETs with Cd, Cr/Au and Bi contacts simulated by technology computer-aided design (TCAD). In short-channel FETs, the relatively small size of the channel means that the electric field gradient significantly affects carrier movement. In the electric field gradient diagrams, it can be seen that the uniformity of the electric field in the channel with Cd electrode is better than that with Bi contacts, which in turn is better than that with Cr/Au contacts (Fig. 5a, Supplementary Fig. 15, Fig. 5b). Note the color-scale limit of Cr/Au contacts case is much larger than that of Cd contact case, and actually its electrical field difference between the contact part and the in-between channel part is larger than Cr/Au case. Benefit by the lower Schottky barriers of Cd contacts, the electric field distributes more uniformly in the channel, reducing local electric field intensity peaks at the contact area. This enhances the linear response of the current, resulting in better on-state performance. In contrast, in Cr/Au contacts case, larger electric field strength concentrates at the contact area (Fig. 5b) and also larger electric field gradients are present especially at the interface with enormous interface states, leading to larger electric potential drop at contacts, greater energy loss and more scattering for carriers during transport. Thus, current output reduces.

a, b The electric field distribution inside short-channel MoS2 FETs with Cd and Cr/Au contacts is compared via technology computer-aided design (TCAD) simulations (LCH = 100 nm) with a positive voltage of 5 V applied to the drain. The colorscale limit of the right Cr/Au contacts case is much larger than that of the left Cd contact. The red dashed boxes denote the zoom-in parts shown in the bottom. c, d The channel length modulation effects of vdW contact Cd-MoS2 FETs versus traditional evaporated Cr/Au-MoS2 FETs. The statistical distribution of mobility (e), hysteresis width (f), threshold voltage (VTH) (g), and on/off ratios (Ion/Ioff) (h) for 85 randomly selected vdW epitaxially grown Cd contacts and 85 randomly selected evaporated Cr/Au MoS2 FETs measured at room temperature. The LCH ranges from 0.1 to 10 μm. i, j A comparison of the mobility degradation between vdW epitaxial Cd-MoS2 FETs and traditional evaporated Cr/Au-MoS2 FETs. The dash-lines indicate the asymptotic linear behavior. k Comparison of the normalized gate hysteresis of our MoS2 FETs with other 2D semiconductor transistors reported in the literatures10,37,60,61,62,63,64,65,66,67,68,69. The references are listed in Supplementary Table 3. l A radar chart comparing the electrical performance of our MoS2 FETs with other reported short-channel TMD-FETs-(It should be noted that the on-state current and on/off ratio were compared only for the 100 nm channel length in the Bi/Sb/Cd cases). The red symbols represent our FETs, while the light blue, light yellow, light green, and light purple areas represent other reported high-performance TMD FETs (See Supplementary Table 4 for the device dimensions in our measurements of on-current density, on/off ratio, mobility and Rc). Since the channel width is significantly larger than the length, fringe current effects can be neglected. The dark blue dash-line indicates the RC limit for the ITRS 2024 vision of 2D semiconductor transistors, and the dark purple dash-line represents the mobility limit in the IRDS 2028 target.

Figure 5c, d and Supplementary Fig. 16 compare the channel length modulation effects of vdW contact Cd-MoS2 FETs and conventional evaporated Cr/Au-contacted-MoS2 FETs. Ideally, the output characteristics of a FET remain constant after entering the saturation region (once VDS reaches gate overdrive voltage threshold of VGS-VTH). However, in practice, as VDS continues to increase, the alteration in carrier density beyond pinch-off in the channel leads to a reduction in effective channel length, thereby giving rise to a continued increase in drain current15,47. In the output curves, Cd-MoS2 FET exhibits a stable current after saturation with a larger saturation curvature (Curvature = 3.2, reflecting sharper turning-on behavior) and also displays a small drift slope (Slope = 0.083). In contrast, the Cr/Au-MoS2 FET shows a larger upward drift slope after saturation (Slope = 0.16) and smaller saturation curvature (Curvature = 0.28). The parameter comparison is shown for clarity in Supplementary Fig. 16a, b. Under short-channel conditions, channel length modulation effects significantly impact the saturation current characteristics of the device, leading to current output fluctuations, increased power consumption and instability. Therefore, Cd-MoS2 contact is advantageous over conventional Cr/Au contact in this aspect.

We further statistically analyzed and compared other key parameters. Figure 5e–h compares the mobility, hysteresis window, threshold voltage, on/off ratio distribution of devices with conventional photolithography/metallization techniques and vdW contacts. The devices with vdW Cd contacts exhibit higher average mobility (≈ 90 cm² V⁻¹ s⁻¹), relatively small hysteresis window (≈ 3.7 V), smaller threshold voltage (≈ 4.5 V), and moreover a higher Ion/Ioff ratio (≈ 10⁸). In contrast, the devices with deposited metal contacts show significantly lower average mobility (≈ 11 cm² V⁻¹ s⁻¹), a smaller Ion/Ioff ratio (≈ 6 × 106), a larger threshold voltage (≈ 28 V), as well as a larger hysteresis window (≈ 14 V).

The uncontrolled damage during the conventional process can give rise to a considerable number of DIGS at the contact interface, leading to degraded performance and significant differences among the devices. Instead, the vdW epitaxially grown 2D Cd contacts are thermodynamically most stable, offering a high-quality interface, which can avoid the above-mentioned DIGS and assist the corresponding devices to prevail in performance. Moreover, interface-state-assisted tunneling can lead to a substantial increase in reverse-biased leakage current in the metal-semiconductor junction during the off state, resulting in a high Ioff and thus a lower Ion/Ioff ratio48. Furthermore, the additional parasitic capacitance from the interface states increases the hysteresis window49. In contrast, devices with vdW contacts reduce these, resulting in high uniformity, low Ioff, large Ion/Ioff ratio, alongside a small hysteresis window in the devices. Besides, during the conventional lithography and lift-off process, TMDs under the contact area can be more likely to degrade50,51.

Additionally, Fig. 5i, j and Supplementary Fig. 17 compare the degree of mobility attenuation between vdW contact Cd-MoS2 FETs, evaporated Cr/Au-MoS2 FETs and Bi-MoS2 FETs. The effective field-effect mobility (μeff) decreases with increasing gate overdrive voltage due to factors including the vertical electric-field in the channel and the horizontal resistance52. While the vertical gate bias range remains exactly the same, the main factor contributing to the mobility attenuation involves the horizontal resistance. The effective mobility can be described by the equation52:

\({\mu }_{0}\) is the low-field mobility limit extracted by extrapolation, the field-effect mobility is strongly influenced by the contacts; and the mobility attenuation factor θ (slope) is related to the horizontal resistance53,54. When other parameters are kept constant, if RC is larger, the slope \(\theta\) would be larger52 and mobility attenuation will be more pronounced.

It is evident that the Cr/Au contact has a largest slope and a smallest μ0 when interfacing with MoS2 (Supplementary Fig. 18a–c), indicating that the RC of Cr/Au is higher and the mobility attenuation is more severe. In the higher overdrive voltage VGS-VTH, Cd contact device displays smaller instability than the Cr/Au contact device. This is also in line with fewer interface states in 2D Cd-MoS2 contact. In contrast, the Cd-MoS2 contact exhibits the smallest slope (also smaller than those of Cr/Au-MoS2 FET, Bi-MoS2 FET) and thus the lowest RC, the largest μ0 (higher than those of Cr/Au-MoS2 FET, Bi-MoS2 FET), due to higher quality contact.

Moreover, the switch cycle hysteresis window is also an important parameter for the stability of the transistor’s switching functionality and relates to switching power consumption. The increase in interface states at the contact can significantly enlarge the hysteresis window49. The device performance is assessed by comparing the gate hysteresis with that of other 2D FETs with SiO2 dielectrics (Fig. 5k, Supplementary Table 3). For a more accurate comparison, the gate hysteresis has been normalized to the insulator field factor ΔVg/dins, where dins is the oxide thickness and ΔVg is the sweep range of the gate voltage (ΔVg = Vg(max) - Vg(min))17. As shown in Supplementary Fig. 19, at a voltage of VDS = 1 V, the normalized gate hysteresis can be as small as 112 mV/ (MV cm⁻¹). The Cd-MoS2 transistors exhibit one of the lowest normalized gate hysteresis values among 2D FETs with SiO2 gate dielectrics (Fig. 5k).

Figure 5l shows a radar chart comparing the electrical performance of our Cd-MoS2 FETs with some other reported short-channel TMD FETs. The RC extracted from the Cd-MoS₂ FETs is in the range of 70-100 Ω·μm. The maximum saturation current density in output characteristic reaches 788 μA/μm (LCH = 100 nm). The ΦSB is nearly zero. The maximum room temperature mobility reaches 160 cm² V⁻¹ s⁻¹ with an on/off ratio greater than 108 (Supplementary Fig. 14e), indicating high overall performance in vdW contact devices, even more superb than the state-of-the-art contact techniques7,12. The RC of Cd-MoS2 exceeds limit for 2D semiconductor transistors in the International Technology Roadmap for Semiconductors (ITRS) 2024 vision (the blue dash-line in Fig. 5l), and the mobility surpasses the target in the International Roadmap for Devices and Systems (IRDS) 2028 vision (the purple dash-line in Fig. 5l). Supplementary Table 5 lists some key performance indicators of the devices, together with those of other literatures.

Our vdW metal epitaxial growth and contact strategy is also suitable for other TMD materials, such as WS2. The structural information of the as-grown Cd-WS2 is systematically characterized by using OM, AFM, Raman and PL spectroscopy, XRD and XPS (Supplementary Fig. 20a–f, 21a, b). Supplementary Fig. 22a–f characterizes its electrical properties. The back-gate Cd-WS₂ FETs on a 300 nm SiO₂ dielectrics present a switching ratio greater than 10⁸ vs. 4 × 105 of conventional deposited electrodes, and additionally a smaller threshold voltage (10.3 V vs. 47.2 V). The on-state current density of Cd-WS2 FETs is two orders of magnitude greater than that of the Cr/Au-WS2 FETs under the same channel conditions. Overall performance is noticeably improved, displaying the universal applicability of Cd contact on 2D TMDs.

Discussions

In conclusion, 2D metal Cd-MoS2-based FETs exhibit notable performance advantages, exceeding conventional fabrication techniques and even some state-of-art contact methods. They achieve a ΦSB close to zero, a remarkably low RC of 70–100 Ω·µm, a high on-state current density of 788 μA/μm (LCH = 100 nm), 942 μA/μm (LCH = 50 nm), an on/off ratio greater than 108, a small hysteresis window of 112 mV/(MV cm−¹) and a high mobility of approximately 160 cm2 V−1 s−1. These performance advantages result from the use of vdW epitaxial 2D metal Cd contacts, which offer atomically pristine interfaces and minimal damage to the underlying MoS2 through contamination-free vdW epitaxy at low temperatures. The resulting suppression of MIGS and DIGS further enhances device performance. This thermodynamically stable hetero-integration strategy provides a promising pathway towards 2D transistors that could complement, compete with, or even surpass silicon electronics1.

Methods

Growth of monolayer TMD materials

The growth of monolayer MoS₂ nanosheets was conducted in a three-zone tube furnace. MoO₃ array patterns were deposited onto a silicon dioxide substrate using a thermal evaporation system with a metal mask. The patterned substrate was placed in the middle zone of the furnace as the precursor, with a small amount of salt added to lower the melting point. Sulfur powder (99.99% purity) was used as the other precursor and placed upstream in the quartz tube. Before heating, the CVD system was purged with 500 sccm Ar (99.999% purity) for 10 min. The temperature of the middle zone was then ramped to 760 °C over 35 min and held at 760 °C for 8 min for monolayer MoS₂ growth, with 100 sccm of argon as the carrier gas55.

Monolayer WS₂ was grown using a similar process, with the main difference being that the center zone temperature was set to 900 °C and maintained for 5 min. After the reaction, the system was allowed to cool to room temperature.

The growth of van der Waals epitaxial Cd nanosheets

For the vdW epitaxial growth of Cd nanoplates on MoS2 (WS2), a single temperature zone tube furnace was used as an experimental instrument. Cd powder (1 mg, purity 99.99%) and BiOCl (0.25 mg, purity 99.99%) powder were mixed uniformly and put into a quartz boat1. The MoS2 (WS2) substrate was placed downstream, while the quartz boat was positioned at the center of the heating zone. During the growth process, a constant flow of 35 sccm Ar and 15 sccm H2 was used as the carrier gas. Then, the furnace center for precursors was heated to 390 °C under ambient atmospheric pressure. The growth substrate downstream was around 108 °C. After reaching the desired growth temperature, the temperature was maintained for 15 min. After the growth process terminated, the furnace was naturally cooled to room temperature, and the sample was removed.

DFT calculations

The Vienna ab initio software package (VASP) was used to perform DFT calculations under the Perdew–Burke–Ernzerh of generalized gradient approximation (PBE-GGA) and the projected augmented wave method. A slab model stacked with monolayer MoS2 and four-layer semi-metal (Cd) (001) plane was used to simulate the MoS2-Cd contact. In all calculations, the K-point mesh to sample the 2D Brillouin Zone was 6 × 6 × 1 by Monkhorst-Pack method. The cutoff energy of the plane-wave was 450 eV. In the structural relaxation and other calculations, the convergence criterion of the electronic self-consistent iteration and force were <10−5 eV and 0.02 eV Å−1, respectively. A vacuum zone of 15 Å was used to prevent interactions between the adjacent images.

Calculation of the tunneling-specific resistivity for Cd–MoS2 contact

The tunneling current density (Jt) across the vdW barrier can be calculated using Simmon’s model56:

where wt stands for the tunneling gap width, Φt stands for the tunneling potential barrier, α is an empirical parameter associated with the barrier shape for an ideal square barrier, (α = 1), V is the bias voltage, q is the electron charge, ħ is the reduced Planck’s constant, and me stands for the free-electron mass. At low bias (qV ≪ Φt), the tunneling-specific resistivity is formula is simplified to

According to our DFT calculation results, wt ≈ 1.61 Å and Φt ≈ 3.14 eV. We therefore estimate that ρt ≈ 1.7 × 10−9 Ω cm2 for our Cd-MoS2 contact.

Material characterizations

The morphology of the synthesized Cd/MoS₂ (WS₂) heterostructures was studied using OM (DSX1000, Olympus), scanning electron microscopy (Nova 200 NanoSEM), and atomic force microscopy (Bruker, Dimension Icon). The crystal structure, phase, optical absorption, and composition were further analyzed using XRD (Bruker, D8-Advance), XPS (ULVAC-PHI, PHI 5000 VersaProbe III), a microscope-based Raman spectrometer (inVia Reflex, Renishaw, with a 532 nm excitation laser), and TEM (FEI, Titan Cubed Themis G2 300, equipped with an EDS system). All characterizations were conducted at room temperature.

Device fabrication and electrical measurements

The monolayer MoS2 with synthetic Cd vdW contacts were grown by CVD on a doped silicon substrate, where 300 nm SiO2 was served as the bottom gate dielectric. Cr/Au electrodes were deposited on top of adjacent Cd nanosheets as the electrical leads for source and drain probing pads, while TMDs under the contact area are protected by Cd nanosheets. The evaporation of 5 nm Cr was under a well-controlled deposition rate of 0.5 Å s−1, followed by an Au capping layer (30–50 nm at 0.1 Å s−1) at ~10−6 torr.

For the fabrication process of transferred metal electrode. First, we prepared 80-nm-thick Au electrode arrays on the sacrificial silicon substrate (with an atomically flat surface) using standard photolithography followed by thermal evaporation under vacuum (pressure ~10−6 torr). After the lift-off process, the silicon substrate was immersed in a sealed hexamethyldisilazane (HMDS) chamber at 100 °C to functionalize the surface of SiO2. Au electrodes were mechanically peeled and laminated to the target substrate via the mechanical aligner under an optical microscope. All the electrical transport measurements were conducted in vacuum with an Agilent B1500A semiconductor analyzer at 30 K-300 K temperature.

Extraction of Schottky barrier height

To quantitatively estimate the ΦSB, we performed temperature-dependent IDS-VGS measurements on the aforementioned devices. The device was tested in vacuum. The effective barrier height (ΦB) can be calculated from the slope of the linear fit to ln(IDS/T3/2) versus 1/T using thermionic emission:

where A is the area of the Schottky junction, A* is the Richardson constant, IDS is the total current, kB is the Boltzmann constant, and T is the absolute temperature. Plots of ΦB versus VGS for the different contacts are presented in Fig. 3h. The ΦSB of each MoS2 device was determined in the flat-band zone (VGS = VFB), which corresponds to the deviation from VGS linear dependence of the thermionic emission model.

Contact resistance extraction through transfer-length method (TLM)

The TLM is employed to determine the RC for metal contacts on semiconductors57. In this method, multiple devices are fabricated with a TLM geometry, where the channel lengths (denoted as L1, L2, etc.) are varied between different contacts. The RTotal, normalized by channel width (W), between any two contacts can be expressed as a linear combination of the RC and the length-dependent channel resistance (RCH) of the semiconductor situated between the contacts.

Where RSH is the sheet resistance of the semiconductor channel and LCH is the channel length7.

Equation (6) is the fundamental relationship that is used to extract width-normalized RC in TLM. Multiple two-probe resistance measurements were made between an adjacent pair of contacts with different channel lengths and RTotal were plotted as a function of channel length. which RC can be extracted by finding the y-intercept using a linear fit58.

Carrier density estimation from current–voltage characterization

The n2D of a semiconductor can be modulated by electrostatic gating in a FET configuration. In this configuration, the two metal electrodes (source and drain, S/D) are used to monitor its conductivity, while the third electrode (gate, G) induces free carriers in the channel material across a gate dielectric material. Here, the n2D above VTH can be estimated by where Cox is the oxide gate capacitance per area (for example, 11.5 nF cm-2 with 300 nm SiO2)59. For a channel-dominated MoS2 device which is not operated in a quantum-capacitance dominated regime VTH, the n2D induced by electrostatic gating can be estimated by assuming a simple linear charge dependence on the gate overdrive voltage:

MOSFET field-effect mobility extraction

Field-effect mobility is derived from the transconductance \({g}_{{{\rm{m}}}}=\frac{\partial {I}_{{{\rm{D}}}}}{\partial {V}_{{{\rm{GS}}}}}\) (constant VDS) of a MOSFET, the tangent of the transfer characteristics curve. The field-effect mobility is given by

where LCH is the channel length, W is the channel width, VDS is the source–drain voltage, Cox is the capacitance of the back-gate oxide. The back-gate voltage (VGS) of the devices in our study was applied through an SiO2 (300 nm) (Cox = 11.5 nF cm−2) dielectric stack.

TCAD simulation

The device simulation was conducted using the Atlas simulator in Silvaco TCAD. To facilitate the observation of the electric field potential variation near MoS2, a denser grid (0.018 μm × 0.0004 μm) was established in that region. The parameters for molybdenum disulfide were selected from the literature, including electron affinity, bandgap, conduction band electron density, valence band electron density, dielectric constant, low-field electron and hole mobilities, and the work function was defined near the electrodes with experimentally measured value. The Lombardi concentration-voltage-temperature (CVT) mobility model was used along with the Shockley-Read-Hall (SRH) recombination model. The iterative method employed was the Newton-Raphson method, and the default carrier statistics model used was the Boltzmann statistics model.

Data availability

The source data underlying the figures of this study are available at https://doi.org/10.6084/m9.figshare.28766570. All raw data supporting the conclusions of this study are available from the corresponding author upon request.

References

Wu, R. et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat. Electron. 5, 497–504 (2022).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Wang, P., Yang, D. & Pi, X. Toward Wafer-scale production of 2D transition metal chalcogenides. Adv. Electron. Mater. 7, 2100278 (2021).

Pan, B. et al. General synthesis strategy of 2D transition metal dichalcogenide gradient alloys for high-performance optoelectronic synapses. Adv. Funct. Mater. 2421337, 1–13 (2025).

Aslam, M. A. et al. All van der Waals semiconducting PtSe2 field effect transistors with low contact resistance graphite electrodes. Nano Lett. 24, 6529–6537 (2024).

Chee, S.-S. et al. Lowering the Schottky barrier height by graphene Ag electrodes for high-mobility MoS2. Adv. Mater. 31, 1804422 (2019).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Liu, Y. et al. Approaching the Schottky-Mott limit in van der Waals metal-semiconductor junctions. Nature 557, 696–700 (2018).

Song, S. et al. Fabrication of p-type 2D single-crystalline transistor arrays with Fermi-level-tuned van der Waals semimetal electrodes. Nat. Commun. 14, 4747 (2023).

Li, X. et al. Two-dimensional metallic alloy contacts with composition-tunable work functions. Nat. Electron. 6, 842–851 (2023).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Liang, J. et al. Laser patterning for 2D lateral and vertical VS2/MoS2 metal semiconducting. Adv. Funct. Mater. 34, 2407636 (2024).

Kwon, G. et al. Interaction-and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices. (John Wiley & Sons, Inc, 2006).

Ho, P.-H. et al. Hysteresis-free contact doping for highperformance two-dimensional electronics. ACS Nano 17, 2653–2660 (2023).

Zhang, L. et al. Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses. Nat. Electron. 7, 662–670 (2024).

Liu, X. et al. High-performance asymmetric electrodes photodiode based on Sb/WSe2 heterostructure. Nano Res. 12, 339–344 (2018).

Ma, H. et al. In‐plane epitaxial growth of 2D CoSe‐WSe2 metal‐semiconductor lateral heterostructures with improved WSe2 transistors performance. InfoMat 3, 222–228 (2020).

Yang, S. et al. Large-scale vertical 1T’/2H MoTe2 nanosheet-based heterostructures for low contact resistance transistors. ACS Appl. Nano Mater. 3, 10411–10417 (2020).

Zhang, X. et al. Low contact barrier in 2H/1T’ MoTe2 in-plane heterostructure synthesized by chemical vapor deposition. ACS Appl. Mater. Interfaces 11, 12777–12785 (2019).

Kim, C. et al. A review on transfer process of two-dimensional materials. Tribol. Lubric. 36, 1–10 (2020).

Komsa, H.-P. et al. Two-dimensional transition metal dichalcogenides under electron irradiation: Defect production and doping. Phys. Rev. Lett. 109, 035503 (2012).

Sun, T. et al. Defect chemistry in 2D materials for electrocatalysis. Mater. Today Energy 12, 215–238 (2019).

Khossossi, N. et al. Recent progress of defect chemistry on 2D materials for advanced battery anodes. Chem.- Asian J. 15, 3390–3404 (2020).

Prucnal, S. et al. Chlorine doping of MoSe2 flakes by ion implantation. Nanoscale 13, 5834 (2021).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Jiang, J. et al. Yttrium-doping-induced metallization of molybdenum disulfide for ohmic contacts in two-dimensional transistors. Nat. Electron. 7, 545–556 (2024).

Lei, M. et al. Low-temperature chemical vapor deposition growth of 2D materials. Electron. e43, https://doi.org/10.1002/elt1002.1043 (2024).

Qin, B. et al. General low-temperature growth of two-dimensional nanosheets from layered and nonlayered materials. Nat. Commun. 14, 304 (2023).

Bondi, A. van der Waals Volumes and Radii. Phys. Chem. 68, 441–451 (1964).

Batsanov, S. S. Van der Waals Radii of elements. Inorg. Mater. 37, 871–885 (2001).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Wu, G. et al. Efficient suppression of charge recombination in self-powered photodetectors with band-aligned transferred van der Waals metal electrodes. ACS Appl. Mater. Interfaces 13, 61799–61808 (2021).

Luo, P. et al. Molybdenum disulfide transistors with enlarged van der Waals gaps at their dielectric interface via oxygen accumulation. Nat. Electron. 5, 849–858 (2022).

Kong, L. et al. Wafer-scale and universal van der Waals metal semiconductor contact. Nat. Commun. 14, 1014 (2023).

Wang, Y. et al. P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61–66 (2022).

Jang, J. et al. Fermi-level pinning-free WSe2 transistors via 2D Van der Waals metal contacts and their circuits. Adv. Mater. 34, 2109899 (2022).

Wang, P. et al. Bidirectional electronic tuning of single-layer MoS₂ with conjugated organochalcogens. J. Phys. Chem. C. 123, 1506–1511 (2019).

Liu, L. et al. Transferred van der Waals metal electrodes for sub−1-nm MoS2 vertical transistors. Nat. Electron. 4, 342–347 (2021).

Cui, X. et al. Low-temperature Ohmic contact to monolayer MoS by van der Waals bonded Co/h-BN electrodes. Nano Lett. 17, 4781–4786 (2017).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Hong, A. Dielectric Strength of Air. The Physics Factbook (2000).

Esqueda, I. S. et al. Charge trapping in aligned single-walled carbon nanotube arrays induced by ionizing radiation exposure. J. Appl. Phys. 115, 054506 (2014).

Le-The, H. et al. Postdeposition UV-ozone treatment: An enabling technique to enhance the direct adhesion of gold thin films to oxidized silicon. ACS Nano 13, 6782–6789 (2019).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2020).

Neamen, D. A. Semiconductor Physics and Devices: Basic Principles.4th ed. (McGraw-Hill, 2012).

Yang, X. et al. Highly reproducible van der Waals integration of two-dimensional electronics on the wafer scale. Nat. Nanotechnol. 18, 471–478 (2023).

Sun, Y. et al. Characterization of interface trap dynamics responsible for hysteresis in organic thin-film transistors. Org. Electron. 27, 92–196 (2015).

Jumbert, G. et al. Electron beam lithography for direct patterning of MoS2 on PDMS substrates. RSC Adv. 11, 19908 (2021).

Wang, P. et al. High-fidelity transfer of chemical vapor deposition grown 2D transition metal dichalcogenides via substrate decoupling and polymer/small molecule composite. ACS Nano 14, 7370–7379 (2020).

Schroder, D. K. Semiconductor Material and Device Characterization. (Wiley, 2017).

Islam, A., Lee, J. & Feng, P. X.-L. All-dry transferred single- and few-layer MoS2 field effect transistor with enhanced performance by thermal annealing. J. Appl. Phys. 123, 025701 (2018).

Kim, T.-Y. et al. Electrical properties of synthesized large-area MoS2 field-effect transistors fabricated with Inkjet-printed contacts. ACS Nano 10, 2819–2826 (2016).

Lan, S. et al. Judicious selection of precursors with suitable chemical valence state for controlled growth of transition metal chalcogenides. Adv. Mater. Interfaces 10, 2300713 (2023).

Simmons, J. G. Generalized formula for the electric tunnel effect between similar electrodes separated by a thin insulating film. J. Appl. Phys. 34, 1793–1803 (1963).

Berger, H. H. Contact resistance and contact resistivity. J. Electrochem. Soc. 119, 507 (1972).

Mitta, S. B. et al. Electrical characterization of 2D materials-based field-effect transistors. 2D Mater. 8, 012002 (2020).

Mukherjee, R. et al. Substitutional electron and hole doping of WSe2: Synthesis, electrical characterization, and observation of band-to-band tunneling. Phys. Rev. Appl. 7, 034011 (2017).

Qi, D. et al. Graphene-enhanced metal transfer printing for strong van der Waals contacts between 3D metals and 2D semiconductors. Adv. Funct. Mater. 33, 2301704 (2023).

Bartolomeo, A. D. et al. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 5, 015014 (2017).

Wang, H. et al. Hysteresis of electronic transport in graphene transistors. ACS Nano 4, 7221–7228 (2010).

Giannazzo, F. et al. Effect of temperature-bias annealing on the hysteresis and subthreshold behavior of multilayer MoS2 transistors. Phys. Status Solidi-Rapid Res. Lett. 10, 797–801 (2016).

Kaushik, N. et al. Reversible hysteresis inversion in MoS2 field effect transistors. npj 2. D. Mater. Appl. 1, 34 (2017).

Late, D. J. et al. Hysteresis in single-layer MoS2 field effect transistors. ACS Nano 6, 5635–5641 (2012).

Lan, C. et al. The origin of gate bias stress instability and hysteresis in monolayer WS2 transistors. Nano Res. 13, 3278–3285 (2020).

Li, T. et al. Scaling behavior of hysteresis in multilayer MoS2 field effect transistors. Appl. Phys. Lett. 105, 093107 (2014).

Lan, C. et al. Gate bias stress instability and hysteresis characteristics of InAs nanowire field-effect transistors. ACS Appl. Mater. Interfaces 12, 56330–56337 (2020).

Shu, J. et al. The intrinsic origin of hysteresis in MoS2 field effect transistors. Nanoscale 8, 3049–3056 (2016).

Acknowledgements

We acknowledge the support from National Natural Science Foundation of China (Nos. 52072272 (L.Z.), 52331009 (S.W.), 62304157 (M.Z.), 51902061 (P.W.)), Wenzhou Fundamental Scientific Research Projects (Grant No. G20240021 (P.W.), G20240037 (M.Z.)), Zhejiang Provincial Natural Science Foundation of China, Grant No. LMS25E020003 (P.W.).

Author information

Authors and Affiliations

Contributions

L.Z., P.W., M.Z., S.W. coordinated the work. M.Y., M.Z., J.L., Y.W., P.W. participated in materials growth as well as TEM and HAADF-STEM characterizations. P. W., M.Z., provide concrete guidance on the device measurements as well as material characterizations. M.Y. prepared and measured all devices. Y.W., D.L., M.Z., J.L., and B.Z. assisted in device fabrication. C.Z. provided accessories of thermal evaporation setup and instructed the handling of the setup. P.W. conducted the first-principle calculations and provided theoretical analysis method for device data. P.W., M.Y., M.Z., contributed to the discussions, data analysis and plotted the drawings. P.W. and M.Y. wrote the manuscript with inputs from all the authors. S.W., Y.Y., D.L, and K.Z. made revision suggestions. P.W., L.Z. and Y.Y. revised the manuscript. All the authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Ki Seok Kim, Junyoung Kwon, and the other, anonymous, reviewer for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Yue, M., Zhang, K., Zhao, M. et al. 2D Cd metal contacts via low-temperature van der Waals epitaxy towards high-performance 2D transistors. Nat Commun 16, 4018 (2025). https://doi.org/10.1038/s41467-025-59174-7

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-59174-7

This article is cited by

-

2D computational photodetectors enabling multidimensional optical information perception

Nature Communications (2025)