Abstract

The integration of two-dimensional (2D) semiconductors with high-κ dielectrics is critical for the development of post-silicon electronics. The key challenge lies in developing an ultra-thin high-κ dielectric with damage-free interface and sub-1 nm equivalent oxide thickness (EOT) for further continuation of Moore’s law. Here we report the thickness-controlled free-standing growth of layered MoO3 dielectrics with EOT down to 0.9 nm and high permittivity beyond 40, and their application in 2D electronic devices. The MoS2 transistors with MoO3 as high-κ gate dielectric exhibit a high on/off ratio close to 108, low subthreshold swing of 78 mV/dec and low leakage current below 10−4 A/cm2. By further vertically stacking n-MoS2 with p-WSe2 transistors, the complementary metal-oxide-semiconductor (CMOS) inverters are achieved, demonstrating its application potential in high-density digital logical circuits. This work develops the controllable growth of high-κ MoO3 dielectrics with ultra-thin EOT, advancing the development of high-performance, size-shrinking and low-power 2D electronics.

Similar content being viewed by others

Introduction

To align with the Moore’s law, the continued scaling of silicon-based field-effect transistors (FETs) has driven the development of advanced device architectures such as Fin-FETs and vertical gate-all-around (VGAA) transistors1,2,3,4. Despite these innovations, silicon-based FETs encounter significant challenges when they approach sub-nanometer scales, including gate leakage current and diminished gate controllability5,6. These issues underscore the need of alternative materials and technologies. Two-dimensional (2D) semiconductors such as MoS2 and WSe2 offer promising electronic properties for next-generation transistors7,8,9,10,11. However, integrating these channel materials with suitable gate dielectrics for achieving efficient gate control and low leakage currents remains problematic12,13,14.

For post-silicon electronics, it is of great importance to develop an ultra-thin high-κ dielectric with damage-free interface and sub-1 nm equivalent oxide thickness (EOT). In theory, EOT = \({{t}_{{{{\rm{ox}}}}}\varepsilon }_{{{{{\rm{SiO}}}}}_{2}}/{\varepsilon }_{{{{\rm{ox}}}}}\), where \({t}_{{{{\rm{ox}}}}}\) is the thickness of the oxide layer, \({\varepsilon }_{{{{{\rm{SiO}}}}}_{2}}\) and \({\varepsilon }_{{{{\rm{ox}}}}}\) are the dielectric constants of the SiO2 and oxide layer, respectively. Traditional high-κ dielectrics such as Al2O3 and HfO2 were usually deposited via atomic layer deposition (ALD) technique, that can degrade the interface between dielectrics and semiconductor channels12,15, particularly when a sub-1 nm EOT is needed. This degradation occurs due to the non-uniform nucleation and additional defect formation, which compromises device performance and causes leakage current.

There is a pressing need for an alternative approach that maintains interfacial integrity while providing high-quality dielectric properties. Benefiting from the atomically thin thickness and dangling-bond-free surfaces, the 2D dielectrics can be stacked with 2D channels via a van der Waals interaction, allowing for atomic-level gate thinning and circumvention of lattice mismatch issues16,17,18. In widely reports, the 2D hexagonal boron nitride (h-BN) has been regarded as a universal insulator in FETs19. However, h-BN has a low dielectric constant of ~5 and inapposite band offsets with most 2D semiconductors. As size scaling technologies require EOT below 1 nm (corresponding to a physical thickness below 1.3 nm in h-BN), the few-layer h-BN often results in excessive thermionic and tunneling leakage currents20. So far, there is still a lack of van der Waals (vdW) layered dielectrics with high dielectric constant and ultrathin EOT as alternatives to h-BN.

In response to this challenge, 2D layered high-κ materials have been recently developed as promising dielectrics for high performance FETs21,22. As typical transition metal oxides, MoO3 demonstrates great application potential as a high-κ gate dielectric in 2D semiconductor transistors23. In order to further leverage its advantages and potentials, we herein developed a physical vapor deposition (PVD) method for the thickness-controllable growth of large-area single-crystal MoO3 nanoflakes, that can serve as a high-κ vdW dielectric layer for FETs. The layered MoO3 can be free-standing grown in an out-of-plane direction and transferred onto target substrates to stack with 2D channels via a polymer-free technique21,24, achieving atomically smooth and damage-free surface and interface, thus preserving the high dielectric characteristic of MoO3 and the intrinsic electrical properties of the 2D semiconductor channels. Through the thickness dependent capacitance measurement at room temperature, the dielectric constant of vertically grown MoO3 can reach up to ~40 at thickness of ~15.9 nm, enabling a high breakdown field exceeding 7.65 MV/cm and an ultra-thin EOT of 0.9 nm in FETs with MoO3 thickness of 9.31 nm. By incorporating PVD-grown MoO3 as the top gate dielectric, the MoS2 FETs exhibit a high on/off current ratio up to 7 × 107, a subthreshold swing as low as 78 mV/dec, a leakage current below 10−4 A/cm2 and a zero gate operating voltage. The vertically stacked complementary metal-oxide-semiconductor (CMOS) inverters are further demonstrated by integrating the n-MoS2 and p-WSe2 transistors stacked in out-of-plane direction, showing a great application potential in high-density digital logic circuit. This work develops a vdW high-κ MoO3 dielectric that is much superior to h-BN and traditional oxide insulators, realizing high performance transistors with ultra-thin EOT and vertically stacked CMOS inverter, contributing to the continued progress of “More Moore” scaling in semiconductor devices.

Results and discussion

Free-standing growth of MoO3 dielectrics

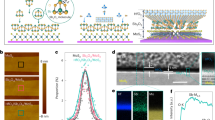

The physical vapor deposition (PVD) technique was employed to grow layered MoO3 on SiO2/Si substrates (see Methods for details). From the scanning electron microscopy (SEM) images as shown in Fig. 1a, b, the MoO3 nanoflakes were vertically grown with lateral side standing on the substrate. This can protect the MoO3 surface from the substrate during the high temperature growth, in favor of its atomically smooth and damage-free surface. Additionally, the out-of-plane growth can also enable an easy transfer onto targeted substrates via a polymer-free mechanical pressing method as shown in Fig. 1c, preventing damage and contamination during the vdW stack with 2D semiconductor channels21. Supplementary Fig. 1 shows the optical microscopy (OM) images of the transferred MoO3 nanoflakes on flexible PDMS, mica and silicon substrates, respectively. Figure 1e shows the atomic force microscopy (AFM) images of the MoO3 on mica, revealing the uniform thickness and clean surface after the transfer process. The surface roughness of the samples with different thickness are also shown in Supplementary Table 1, further revealing clean and smooth surface. Overall, the free-standing layered MoO3 grown by our PVD technique demonstrates its advantages of high-quality surface and interface, thus ensuring the high dielectric characteristic of MoO3 and the intrinsic electrical properties of the 2D channels.

a Scanning electron microscopy (SEM) image of vertically standing MoO3 nanoflakes grown on silicon substrates at 740 °C. b SEM image of MoO3 nanoflakes grown on silicon substrates at 790 °C. c Schematic of the polymer-free transfer method for transferring vertically grown MoO3 on target substrate. d Optical microscopy (OM) images of layered MoO3 with varying thicknesses on SiO2/Si substrates grown at different temperatures. e Atomic force microscopy (AFM) image showing the uniform thickness and clean surface of the as-grown MoO3 nanoflakes. f Raman spectra of MoO3 with varying thicknesses, three vertical dashed lines indicate the dominant Raman peaks at 666 cm−1, 817 cm−1 and 995 cm−1. g Ultraviolet–visible (UV–vis) absorption spectra of MoO3 with the corresponding plots of the Kubelka–Munk function, where λ, α, h and ʋ are wavelength, absorption coefficient, Planck’s constant and frequency of the incident light. Inset: the calculation of band gap, dashed line indicates Tauc’s equation result. h X-ray diffraction (XRD) pattern of the synthesized MoO3. i X-ray photoelectron spectroscopy (XPS) spectra of Mo 3 d core level.

By precisely controlling the growth conditions including temperature and holding time, the thickness and lateral dimension of the MoO3 nanoflakes can be gradually tuned (see more details in Supplementary Figs. 2, 3). The morphology evolution as growth temperature changes from 740 °C to 790 °C has been characterized by OM and SEM techniques, as shown in Fig. 1d and Supplementary Fig. 4, respectively. Determined from AFM measurement, the thicknesses of PVD-grown MoO3 are tuned from few nanometers to tens of nanometers, alongside with increased lateral size up to millimeter scale. Figure 1f shows the Raman spectra of MoO3 nanoflakes with varying thicknesses, the dominant Raman peaks at 666 cm−1, 817 cm−1 and 995 cm−1 are corresponding to the phonon stretching mode of Mo-O3, Mo-O2 and Mo = O, respectively25,26, that remain unchanged with increasing thickness.

The ultraviolet-visible (UV-vis) absorption measurement was performed to investigate electronic band structure of MoO3 with Tauc’s equation, (αhν)1/2 = A(hν − Eg), where α, hν, A, and Eg are absorption coefficient, photon energy, constant, and optical band gap, respectively25,27. As shown in Fig. 1g, the band gap (Eg) of our sample is measured to be around 3.3 eV. In order to confirm the crystal structure of MoO3, the X-ray diffraction (XRD) measurement was conducted as shown in Fig. 1h. The main diffraction peaks are indexed as (020), (040), (060) and (080) planes, which typically correspond to the orthorhombic structure of MoO3 phase28. To analyze the elements in single crystals MoO3, the X-ray photoelectron spectroscopy (XPS) was performed to confirm Mo 3 d core level in Fig. 1i. The spectrum consists Mo6+ and Mo5+ oxidation states with the binding energies of Mo 3d5/2 at 232.6 eV for Mo6+ and 231.6 eV for Mo5+. The ratio of Mo6+: Mo5+ is 95: 5, which indicates the most presence of +6 oxidation state in molybdenum29,30. Transmission electron microscopy (TEM) and selected area electron diffraction (SAED) experiments were also measured to analyze atomic arrangement (Supplementary Fig. 5). The TEM lattice images revealed the spacing between the two sets of parallel fringes was 0.433 nm and 0.415 nm, corresponding to the two vertical planes (100) and (001) of α-MoO3, respectively25,28.

Dielectric and breakdown characteristics of MoO3 dielectrics

By constructing metal-insulator-metal (MIM) capacitors as shown in Fig. 2a, we further evaluated the out-of-plane dielectric constant of the as-grown MoO3 nanoflakes with varying thickness. The OM and AFM images of the MIM devices with different thickness are shown in Supplementary Fig. 6 for more details. To exclude the influence of parasite capacitance, the MIM devices were fabricated on sapphire substrate. As shown in Fig. 2b, the capacitance-voltage (C–V) measurements were conducted to extract the dielectric constant of MoO3 layers with thicknesses ranging from 15.9 to 95.1 nm at 10 kHz frequency. Due to its high dielectric quality, the MoO3 nanoflake with a thickness of 15.9 nm exhibits a stable capacitance density of 2.2 μF/cm². Figure 2c shows the C-V measurements for the device with different area, indicating negligible variation in capacitance. The dielectric constants were calculated using the formula31: C = Aε0εr/d, where C is the measured capacitance, ε0 is the vacuum permittivity, εr is the relative permittivity, A is the overlapping area of the electrodes and d is the thickness of the MoO3. The calculated relative permittivity (εr) varies from 39.8 to 54.1 as thickness increases from 15.9 nm to 95.1 nm (Supplementary Fig. 6f). To further benchmark the performance of MoO3 as a gate dielectric, we compared its dielectric constant and band gap with those of other representative high-κ materials, as shown in Fig. 2d. With a dielectric constant of ~40 and a band gap of 3.3 eV, our MoO3 resides in a favorable region of this parameter space, striking a balance between strong gate coupling and effective leakage suppression.

a Schematic diagram of the metal-insulator-metal (MIM) device configuration using MoO3 as the dielectrics. b Capacitance-voltage (C–V) characteristics of the MIM devices with varied thickness. c Capacitance-voltage (C–V) measurement of the device with different areas. d Dielectric constant versus energy band gap of advanced dielectric materials in literature21,34,35,38,39,40. e Breakdown field strength of the MoO3 dielectric of different device pixel. Inset: MIM device array for breakdown voltage measurement. f I–V characteristic of a typical MoO3-based in-plane device, demonstrating its insulating behavior. Inset: Schematic illustration of the horizontal transport device.

A high dielectric constant (κ) of gate insulator in FETs provides two key advantages: i) higher gate capacitance can enhance the control ability on the channel charges, improving modulation of conductivity within a small gate voltage range, which in turn lowers the threshold voltage and reduces power consumption; and ii) the physical thickness of the gate insulator can be increased without compromising the gate capacitance, which reduces direct electron tunneling through the gate oxide, thereby minimizing gate leakage current14,17,32,33. To assess its endurance under high electric fields, we further measured the breakdown field strength (EBD) of the layered MoO3. As shown in Fig. 2e, the average EBD, determined from the MIM device arrays based on one MoO3 nanoflake (inset of Fig. 2e), is calculated to be 7.65 MV/cm, indicating strong tolerance to vertical electric fields. In addition, the layered MoO3 also exhibits a low in-plane current below 10−12 A as shown in Fig. 2f, which can ensure the negligible leakage current through MoO3 between source and drain in the transistor.

MoS2 FETs with MoO3 top-gate dielectrics

Using the polymer-free mechanical pressing method as discussed above (Fig. 1b), the PVD-grown MoO3 layers were transferred and stacked on top of 2D semiconductors to construct the FETs with MoO3 as high-κ dielectric and MoS2 as channel. Figure 3a, b illustrate the schematic diagram and SEM image of top-gated MoS₂ FETs, respectively. To examine the interfacial quality, the cross-sectional TEM image was conducted as shown in Fig. 3c. Both the MoO3 gate dielectric and MoS2 channel display typical layered structures with clear lattice fringes and atomically-flat surfaces. The clean and flat surface of MoO3 layer facilitates a close vdW interaction with the MoS2 channel, guaranteeing a high gate controllability and device performance24,34,35,36. Furthermore, the cross-sectional high-angle annular dark-field (HAADF) imaging and EDX elemental mapping (Fig. 3d) confirm the uniform distribution of Mo, O, and S elements across the layers, corresponding to the expected compositions in device structure. Additionally, the C elements were not detected at the MoO3/MoS2 interface, implying no polymer contamination during the vdW integration process, that indicates the advantage of our polymer-free transfer method.

a Schematic illustration of the top-gate field effect transistor (FET) with as-grown MoO3 as gate dielectric and MoS2 as channel, the TG, S and D are represented as top-gate, source and drain, respectively. b Scanning electron microscopy (SEM) image of the device with MoO3 thickness of 9.31 nm, blue and orange dashed lines represent MoO3 and MoS2 respectively. c Cross-sectional transmission electron microscopy (TEM) image of the MoO3 layer stacked on MoS₂ channel, showing a clean and damage-free interface. d High-angle annular dark-field (HAADF) and corresponding energy-dispersive X-ray (EDX) mapping images for the Mo, O, S, and C elements, confirming the anticipated MoO3/MoS2 structure with distinct elemental distributions. e Transfer characteristics for channel current (IDS) and top-gate voltage (VTG) of the devices with MoO3 thickness from 9.31 nm to 210 nm at drain voltage (VDS) = 1 V. f Transfer characteristics (IDS–VTG) of the transistor with MoO3 thickness of 9.31 nm and the channel length/width of 4.2/2.2 μm measured at different VDS. g Comparison of gate leakage current (LC) density and subthreshold sweep across devices with varying dielectric thicknesses after 2 months.

In the top-gated MoS₂ FETs, the MoO3 dielectric thickness is varied from 9.31 nm to 208 nm (Supplementary Fig. 7), and the corresponding transfer characteristics are shown in Fig. 3e. It is observed that the thinner MoO3 dielectric can lead to smaller threshold voltage and steeper subthreshold swing (SS). Figure 3f shows the transfer curves of the transistor with 9.31 nm thick MoO3 dielectric, corresponding to an ultrathin EOT of 0.9 nm. At different VDS, the drive current (IDS) can reach saturation state at gate operating voltage (VTG) of 0 V, indicating a promising potential for low-power electronic application37. The device also exhibits switching performance with high on/off ratio of 7 × 107, low SS of 78 mV/dec, and low leakage current below 10−4 A/cm², that outperforms the reported 2D transistors with conventional high-κ dielectrics and meets the requirements of the International Roadmap for Devices and Systems (IRDS)1.

To evaluate the air-stability of the device over time, we compared the gate leakage current (LC) density and subthreshold swing of different transistors with varying dielectric thicknesses before and after two months (Fig. 3g). There were no significant changes in the performance even for the devices with thinner dielectrics (<30 nm), that can be attributed to the protection of high-κ MoO3 dielectrics on MoS2 channel. Long-term air-stability of single MoO3 without any protection was also demonstrated by AFM and Raman characterization as shown in Supplementary Fig. 8. Overall, the high-κ MoO3 dielectrics allow for an ultrathin EOT transistor with steep subthreshold swing, low leakage current and zero gate operating voltages, making these transistors as promising candidates for future energy-efficient electronics.

Vertical CMOS inverter and benchmark of high-κ transistor

By vertically stacking the n-MoS2 and p-WSe2 transistors based on MoO3 as high-κ gate dielectrics, we further achieved a complementary metal–oxide–semiconductor (CMOS) inverter. Figure 4a shows the OM and schematics of the vertically stacked CMOS inverter, where the MoS2, MoO3 and WSe2 are stacked layer-by-layer from bottom to top, with the MoO3 dielectrics and gate electrodes sandwiching between MoS₂ and WSe2 channel. The supply voltage (VDD) is applied to one side of top WSe2, while the output voltage (VOUT) electrode is connected with bottom MoS2 and the other side of WSe2 as shown in Fig. 4b. The voltage transfer characteristic of the inverter at VDD of 1 V and 2 V is shown in Fig. 4c, as the input voltage (VIN) ranges from −2 V to −0.5 V, the output voltage (VOUT) is switched from high to low level, showing a typical NOT logic operation. At VDD of 1 V and 2 V, the inverter exhibits a voltage gain of 6.2 and 10.1, respectively, demonstrating the feasibility of vertically stacked logic circuits using the transistors with MoO3 as gate dielectrics.

a OM image of the vertically stacked CMOS inverter with input voltage (VIN), output voltage (VOUT) and supply voltage (VDD). The blue, green and white dashed lines represent MoO3, MoS2 and WSe2 respectively. b The schematic representation of the CMOS inverter configuration. c Output voltage and voltage gain characteristics of the inverter at supply voltages (VDD) of 1 V and 2 V. d Comparison of equivalent oxide thickness (EOT) and subthreshold swing (SS) values with state-of-the-art 2D FETs integrated with high-κ dielectrics reported in the literature21,22,31,34,38,39,40,41,42,43. e Comparison of operating voltage and on/off ratio of our FETs with other high-k dielectrics based 2D FETs21,22,31,34,35,38,39,40,41,42,43.

To benchmark the performance of our FETs against state-of-the-art 2D FETs, we compared their performances of the transistors with various high-κ dielectrics. Figure 4d and e show the performance comparisons of SS versus EOT and on/off ratio versus operating voltage, respectively. Our MoS2 FETs with MoO3 dielectrics demonstrate an ultra-thin EOT of 0.9 nm, while remaining a low SS of 78 mV/dec (Fig. 4d). Due to the high dielectric constant and ultra-thin EOT, our transistors also achieve a high on/off ratio close to 108 at zero gate operating voltage (Fig. 4e). It is noted that the “operating voltage” here is defined as the top-gate voltage required to reach the target on/off ratio.

In summary, the free-standing growth of MoO3 nanoflakes as high-κ dielectrics has made a significant advance for next-generation ultra-scaled FETs. The vertically grown MoO3 can enable an atomically smooth and damage-free surface, preserving the high dielectric feature of MoO3 and intrinsic electric property of 2D channel. As a result of capacitance measurement, the atomically thin MoO3 layer exhibits a high dielectric constant beyond 40 and an ultra-thin EOT down to 0.9 nm. The MoS2 FETs with MoO3 as gate dielectrics exhibit superior performance with current on/off ratio up to 7 × 107, SS of 78 mV/dec, and leakage current below 10-4 A/cm2, accounting a high level among state-of-the-art 2D FETs with other high-κ dielectrics. By integrating n-MoS2 with p-WSe2 transistors using MoO3 as gate dielectrics, the vertically stacked CMOS inverters are also demonstrated for future high-density digital logical circuits. This work addresses the critical challenges of scaling FETs by developing a high-κ dielectrics, aligning with the “More Moore” principle for future semiconductor technology.

Methods

PVD growth of MoO3 single crystal nanoflakes

The layered MoO3 nanoflakes were grown by physical vapor deposition (PVD) method in a one-inch horizontal tube furnace. 300 mg MoO3 powder (purity 99.999%, Macklin) was placed in the center of the hot zone and spread in 10 cm length on a ceramic boat. Clean SiO2/Si substrates were faced down to the ceramic boat. The reaction was carried out at atmospheric pressure and pure Ar was used as carrier gas. Typical growth conditions were as follows. The central temperature was heated up to 740–790 °C within 30–35 min in vacuum. After reaching set temperature, the system was filled with Ar gas and then keeping flow rate around 100 sccm. The growth time was ranged from 10 to 30 min. Finally, the whole system was cooled to room temperature naturally.

Fabrication of MoO3 capacitor and MoS2 FETs

The MoO3-based metal-insulator-metal (MIM) capacitors were fabricated on sapphire substrates. First, the thick graphite was exfoliated onto the substrate as bottom electrodes. Next, the vertically grown MoO3 nanoflakes were directly picked up from the SiO2/Si substrates by a polydimethylsiloxane (PDMS) stamp (purchased from Taizhou SUNANO New Energy Co., Ltd.), followed by aligned transfer onto the specific graphite bottom electrode using a transfer platform (Shanghai OnWay Technology Co., Ltd). Finally, the electrodes were fabricated via an Ultraviolet Maskless Lithography machine (TuoTuo Technology, UV Litho-ACA) with the help of an ARP-5350 positive photoresist (purchased from Taizhou SUNANO New Energy Co., Ltd.), AR 300-26 developing solution (ALLRESIST GmbH, purchased from Taizhou SUNANO New Energy Co., Ltd.), the thermal evaporation was used to deposit the 50 nm Au electrode.

For top-gated MoS2 FET, the few-layer MoS2 flakes (purchased from Taizhou SUNANO New Energy Co., Ltd.) were mechanically exfoliated onto the 300 nm Si/SiO2 substrate. Then, the standard ultraviolet maskless lithography and thermal evaporation process were used to pattern the Source/Drain electrodes (Cr/Au, 10/40 nm). With the help of the polymer-free transfer method, the selected MoO3 nanoflake was directly picked up from growth substrate, and then stacked onto MoS2. After that, the pre-fabricated Au electrode (50 nm) was transfer as top-gate electrode through classical dry transfer. Transferring top-gate electrode can eliminate the possible physical damage and organic contamination to the ultrathin dielectrics and 2D semiconductor channel.

Material characterization and device measurements

Raman spectrum measurements were performed with confocal microscopy (Thermo DXR2xi) with an excitation wavelength of 532 nm in the ambient atmosphere. The morphology and diameter of MoO3 nanoflakes were further confirmed by optical microscopy, scanning electron microscopy (SEM) (Phenom Pharos G2) and atomic force microscopy (AFM) (Bruker Dimension Icon). The crystal structure of MoO3 were performed by X-ray diffraction (XRD) (Bruker D8 Advance), X-ray photoelectron spectroscopy (XPS) (Thermo escalab 250XI) and ultraviolet-visible (UV-vis) absorption (MStarter ABS DUV-NIR Microscopic Absorption Spectroscopy System, Nanjing Metatest Optoelectronics Co., Ltd.) measurement. The C–V and C–f measurements were carried out on a semiconductor analyzer (FS-Pro) and the E4990A Impedance Analyzer. The cross-sectional TEM lamella was prepared by a focused ion beam microscope (FEI-Scios 2 Hivac) and was characterized by a Talos F200i transmission electron microscope. The electrical properties were measured with a three-probe station equipped with Keithley 2636B and 2611B Source Meter (PSAICPB6A, Precision Systems Industrial Co., Ltd). All measurements were conducted at room temperature.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request. Source data are provided with this paper.

References

Badaroglu, M. International Roadmap for Devices and Systems 2021 (IEEE, 2021). https://irds.ieee.org/editions/2021/more-moore.

Zeng, S., Liu, C. & Zhou, P. Transistor engineering based on 2D materials in the post-silicon era. Nat. Rev. Electr. Eng. 1, 335–348 (2024).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-κ gate oxide. Nature 616, 66–72 (2023).

Shen, Y. et al. The trend of 2D transistors toward integrated circuits: scaling down and new mechanisms. Adv. Mater. 34, 2201916 (2022).

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Vexler, M. I. et al. A general simulation procedure for the electrical characteristics of metal-insulator-semiconductor tunnel structures. Semiconductors 47, 686–694 (2013).

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Liu, C. S. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Kim, K. S. et al. The future of two-dimensional semiconductors beyond Moore’s law. Nat. Nanotechnol. 19, 895–906 (2024).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Kim, H. G. & Leek, H. B. R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron 5, 356–366 (2022).

Robertson, J. High dielectric constant oxides. Eur. Phys. J.-Appl. Phys. 28, 265–291 (2004).

Lin, Y. C. et al. Dielectric material technologies for 2-D semiconductor transistor scaling. Ieee T Electron Dev. 70, 1454–1473 (2023).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Hui, F. et al. On the use of two dimensional hexagonal boron nitride as dielectric. Microelectron. Eng. 163, 119–133 (2016).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Chen, J. et al. Vertically grown ultrathin Bi2SiO5 as high-κ single-crystalline gate dielectric. Nat. Commun. 14, 4406 (2023).

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023).

Holler, B. A., Crowley, K., Berger, M. H. & Gao, X. P. A. 2D semiconductor transistors with van der Waals oxide MoO3 as integrated high-κ gate dielectric. Adv. Electron. Mater. 6, 2000635 (2020).

Zhang, L. et al. Vertically grown metal nanosheets integrated with atomic-layer-deposited dielectrics for transistors with subnanometre capacitance-equivalent thicknesses. Nat. Electron. 7, 662–670 (2024).

Kim, J. H. et al. van der Waals epitaxial growth of single crystal α-MoO3 layers on layered materials growth templates. 2D Mater. 6, 015016 (2018).

Wang, Y., He, R. H., Su, M. Z. & Xie, W. G. Synthesis of the few layered two-dimensional molybdenum oxide atomic crystal. Iop. Conf. Ser.-Mat. Sci. 167, 012020 (2017).

Greiner, M. T., Chai, L., Helander, M. G., Tang, W. M. & Lu, Z. H. Metal/Metal-Oxide Interfaces: How Metal Contacts Affect the Work Function and Band Structure of MoO3. Adv. Funct. Mater. 23, 215–226 (2012).

Hou, X. et al. Single-Crystal MoO3 Micrometer and Millimeter Belts Prepared from Discarded Molybdenum Disilicide Heating Elements. Sci. Rep. 8, 34849 (2018).

Kumar et al. Synthesis of α-MoO3 nanofibers for enhanced field-emission properties. Adv. Mater. Lett. 9, 585–589 (2018).

Zhu, Y. et al. Synthesis of Large-Sized van der Waals Layered MoO3 Single Crystals with Improved Dielectric Performance. Precis Chem. 2, 406–413 (2024).

Huang, J. K. et al. high-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Yang, S. J. et al. Gate dielectrics integration for 2D electronics: challenges, advances, and outlook. Adv. Mater. 35, 2207901 (2023).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Li, S., Liu, X., Yang, H., Zhu, H. & Fang, X. Two-dimensional perovskite oxide as a photoactive high-κ gate dielectric. Nat. Electron. 7, 216–224 (2024).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Mitta, S. B. et al. Electrical characterization of 2D materials-based field-effect transistors. 2D Mater. 8, 012002 (2021).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Cheng, L. et al. Sub-10 nm tunable hybrid dielectric engineering on MoS2 for two-dimensional material-based devices. Acs Nano 11, 10243–10252 (2017).

Park, J. H. et al. Atomic layer deposition of Al2O3 on WSe2 functionalized by titanyl phthalocyanine. Acs Nano 10, 6888–6896 (2016).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Acknowledgements

N.H. acknowledges financial support from Guangdong Basic and Applied Basic Research Foundation (No. 2024A1515030107) and the National Natural Science Foundation of China (No.11904108), Y.Y. thanks financial support from the Guangzhou Basic and Applied Basic Research Foundation (No. 2023A04J1710).

Author information

Authors and Affiliations

Contributions

N.H. conceived the idea and supervised the work. X.L. designed the experiments and performed the measurement. S.X. and Z.Z. helped with the analysis and discussion. Z.Y., X.L., Z. P. and Y.Y. supported the characterization of materials and device. X.L. and N.H. co-wrote the manuscript. All authors contributed to the discussion and revision of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Xuan Gao and the other, anonymous, reviewers for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Source data

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Li, X., Xu, S., Zhang, Z. et al. Controllable growth of MoO3 dielectrics with sub-1 nm equivalent oxide thickness for 2D electronics. Nat Commun 16, 6758 (2025). https://doi.org/10.1038/s41467-025-61972-y

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-61972-y

This article is cited by

-

Bottom–up-synthesized graphene nanoribbons for nanoelectronics

Nature Reviews Materials (2026)