Abstract

Recently the quest for post-silicon semiconductors has escalated owing to the inherent limitations of conventional bulk semiconductors, which are plagued by issues such as drain-induced barrier lowering, interfacial-scattering-induced mobility degradation and a constrained current on/off ratio determined by semiconductor bandwidth. These challenges have prompted the search for more advanced materials, with atomic-layer-thick two-dimensional (2D) semiconductors emerging as a potential solution. Following over a decade of research advances, recent developments1,2,3 in wafer-scale growth and device fabrication have led to breakthroughs in 2D semiconductor electronics. However, the level of integration remains constrained to a few hundred transistors. We describe a reduced instruction set computing architecture (RISC-V) microprocessor capable of executing standard 32-bit instructions on 5,900 MoS2 transistors and a complete standard cell library based on 2D semiconductor technology. The library contains 25 types of logic units. In alignment with advances in silicon integrated circuits, we also co-optimized the process flow and design of the 2D logic circuits. Our combined manufacturing and design methodology has overcome the significant challenges associated with wafer-scale integration of 2D circuits and enabled a pioneering prototype of an MoS2 microprocessor that exemplifies the potential of 2D integrated-circuit technology beyond silicon.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

All data from this study are included in the paper and are available from the corresponding authors upon request. Source data are provided with this paper.

Code availability

All codes used in this study are included in the paper and are available from the corresponding authors upon request.

References

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Illarionov, Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022).

Xia, Y. et al. 12-inch growth of uniform MoS2 monolayer for integrated circuit manufacture. Nat. Mater. 22, 1324–1331 (2023).

Xue, G. et al. Modularized batch production of 12-inch transition metal dichalcogenides by local element supply. Sci. Bull. 68, 1514–1521 (2023).

Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

O’Brien, K. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In Proc. 2021 IEEE International Electron Devices Meeting 7.1.1–7.1.4 (IEEE, 2021).

Chou, A. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In Proc. 2021 IEEE International Electron Devices Meeting 7.2.1–7.2.4 (IEEE, 2021).

Kumar, A. et al. Sub-200 Ω·µm alloyed contacts to synthetic monolayer MoS2. In Proc. 2021 IEEE International Electron Devices Meeting 7.3.1–7.3.4 (IEEE, 2021).

Chou, A. et al. High-performance monolayer WSe2 p/n FETs via antimony–platinum modulated contact technology towards 2D CMOS electronics. In Proc. 2022 IEEE International Electron Devices Meeting 7.2.1-7.2.4 (IEEE, 2022).

Yang, A. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Huang, J. K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Zhang, Y. et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat. Electron. 5, 643–649 (2022).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature 616, 66–72 (2023).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Liu, K. et al. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 4, 906–913 (2021).

IRDS. International Roadmap for Devices and Systems (IRDS™) 2022 Edition: More Moore (IEEE, 2022).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Radisavljevic, B., Whitwick, B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934–9938 (2021).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Yu, L. et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Wachter, S. et al. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Chen, X. et al. Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning. Nat. Commun. 12, 5953 (2021).

Fan, D. et al. Two-dimensional semiconductor integrated circuits operating at gigahertz frequencies. Nat. Electron. 6, 879–887 (2023).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Rhodes, D. et al. Disorder in van der Waals heterostructures of 2D semiconductors. Nat. Mater. 18, 541–549 (2019).

Wang, S. et al. Two-dimensional devices and integration towards the silicon lines. Nat. Mater. 21, 1225–1239 (2022).

Mennel, L. et al. Ultrafast machine vision with 2D material neural network image sensors. Nature 579, 62–66 (2020).

Ning, H. et al. An in-memory computing architecture based on a duplex two-dimensional material structure for in situ machine learning. Nat. Nanotechnol. 18, 493–500 (2023).

Luo, Y. et al. Technology roadmap for flexible sensors. ACS Nano 17, 5211–5295 (2023).

Ma, J. et al. Engineering top gate stack for wafer-scale integrated circuit fabrication based on two-dimensional semiconductors. ACS Appl. Mater. Interfaces 14, 11610–11618 (2022).

Kong, L. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Lee, D. et al. Remote modulation doping in van der Waals heterostructure transistors. Nat. Electron. 4, 664–670 (2021).

Jiang, J. et al. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Kindgren, O. et al. SERV – The SErial RISC-V CPU. GitHub http://github.com/olofk/serv (2020).

Feng, X. et al. Self-selective multi-terminal memtransistor crossbar array for in-memory computing. ACS Nano 15, 1764–1774 (2021).

Hong, S. L. et al. Dual‐gated MoS2 memtransistor crossbar array. Adv. Funct. Mater. 30, 2003683 (2020).

Migliato, M. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

Meng, W. et al. Three-dimensional monolithic micro-LED display driven by atomically thin transistor matrix. Nat. Nanotechnol. 16, 1231–1236 (2021).

Huang, B. et al. MoS2-thin film transistor based flexible 2T1C driving circuits for active-matrix displays. Nano Lett. 23, 9333–9339 (2023).

Peng, Y. et al. Gate‐last MoS2 transistors for active‐matrix display driving circuits. Adv. Funct. Mater. 33, 2304879 (2023).

Heekyeong, P. et al. A wafer-scale nanoporous 2D active pixel image sensor matrix with high uniformity, high sensitivity, and rapid switching. Adv. Mater. 35, 2210715 (2023).

Tang, J. et al. Low power flexible monolayer MoS2 integrated circuits. Nat. Commun. 14, 3633 (2023).

Xinyu, W. et al. Pass-transistor logic circuits based on wafer-scale 2D semiconductors. Adv. Mater. 34, 2202472 (2022).

Yeh, C.-H. et al. Graphene–transition metal dichalcogenide heterojunctions for scalable and low-power complementary integrated circuits. ACS Nano 14, 985–992 (2020).

Acknowledgements

This work was supported by the National Natural Science Foundation of China (Grant Nos. 61925402, 62090032, 62004040 and 62334011), the National Key Research and Development Program (Grant No. 2021YFA1200500), the Innovation Program of Shanghai Municipal Education Commission (Grant No. 2021-01-07-00-07-E00077), the New Cornerstone Science Foundation through the XPLORER PRIZE, the Science and Technology Commission of Shanghai Municipality (Grant No. 23JC1401100) and the Shanghai Pilot Program for Basic Research at Fudan University (Program 21TQ1400100 and Grant No. 23TQ008).

Author information

Authors and Affiliations

Contributions

P.Z. and W.B. proposed this work. W.B. and M.A. directed the fabrication aspects of this project. W.B., S.G., X.D., Y.Z., Q.S., Z.Z., Y.H., J.Z. and C.S. contributed to the development of the FEOL fabrication process. M.A. and Q.Z. contributed to the development of the BEOL fabrication process. S.C. led the short-channel device fabrication. X.Z. performed VLSI design aspects of this project including the creation of the MoS2 FET process design kit and all standard cells in the MoS2 FET library. X.Z. also performed the RV32-WUJI physical design and led experimental calibration and testing. J.H. and X.K. led the architectural definition of RV32I-WUJI, including Firrtl, the Verilog hardware description language and the instruction set architecture, and they also wrote the test programs. K.W. contributed to project management. S.W. and J.W. contributed to manuscript preparation. W.B. and P.Z. were in charge, advised and led on all aspects of the project.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks Saptarshi Das, Michael Waltl and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data figures and tables

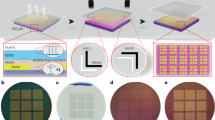

Extended Data Fig. 1 The impact of process steps on transistor performance and the complete fabrication process flow for RV32-WUJI.

a,We divided the process steps for wafer-level circuits into nine main modules and utilized machine learning to analyze the transistor performance under thousands of different process conditions, thereby studying in detail the impact of each process step on transistor performance. This approach effectively helped us determine the optimal wafer-level process flow.b,The integration at the wafer level involves four metal layers (M0-M3) and can be divided into three main parts: (1-2), synthesis of MoS2 on a rigid substrate; (3-7), preparation of the MoS2 transistors; and (8-13), back-end-of-line process. The diagram illustrates the interconnection of a full adder with an inverter.

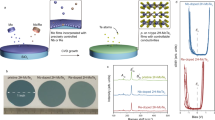

Extended Data Fig. 2 The stability control of the logic circuits in the back-end of line integration.

An example is provided using the voltage transfer characteristic of the inverter unit. After completion of the front-end of line process (a-c), the average switching voltage (VM) of the inverter is 2.065 V. After the subsequent deposition of the inter-layer dielectric (ILD) isolation layer (d-f), VM experiences a slight negative shift and becomes 1.889 V. After completing the integration process (g-i), the VM stabilizes at 1.817 V. Throughout the back-end of line process, the VM shift remains within 6.2% of Vdd, which is well within the range of the tolerable noise margin.

Extended Data Fig. 3 Combined noise margin of 24 typical logic units.

(a-b), The noise margin was tested by adding an input inverter before the logic unit and an output inverter after the logic unit. a represents the results for NOR1 to NOR4 and b for NAND1 to NAND4. If the noise margin is less than 5% of Vdd (0.2 V), the logic unit is considered unsuitable for circuit composition. c, we summarized the full input-output margin maps for various single-stage logic gates and conducted an in-depth analysis of the specific impact of process variations on these margin maps. We have collated the minimum margin values for 16 combinations of single-stage logic gates operating at a voltage of 4 V. Among these, 11 logic gates have been selected as the practical PDK modeling units for application.

Extended Data Fig. 4 MoS2 standard cell library.

A complete table containing a total of 25 types of MoS2 logic unit modules for our “2D_NMOS_lib” standard cell library, along with their corresponding brief description, microscopy image, the schematic of each cell, a typical measured waveform of each fabricated cell, and a truth table.

Extended Data Fig. 5 The circuit schematics of four core functional modules in RX32-WUJI, and the typical measured waveforms from a core module of a 32-bit register.

a, A 1-bit controlled adder module that includes an adder and a control logic, consisting of a total of 27 MoS2 transistors. b, A selection module with four input signals and a total of 27 MoS2 transistors, and its function is to select the appropriate signal output for the next stage by means of a coded selection. c, A 4-bit ring counter and a 3-bit synchronous counter, constructed using 156 MoS2 transistors. It can perform both cyclic counting for a 4-bit signal and sequential counting up to 8. d, A 32-bit data register divided into four 8-bit register blocks, comprising a total of 576 MoS2 transistors. This module can realize the storage and synchronous shift of data.e, The 32-bit register is divided into four 8-bit synchronous register blocks. Four sets of signals, 01000110, 01000100, 01001101, and 01000101, are input into the registers using a clock signal shifting input method. These signals correspond to the letters ‘F’, ‘D’, ‘M’, and ‘E’, respectively, according to the ASCII code.

Extended Data Fig. 6 Main modules used in RV32-WUJI.

This table lists the general function, core units, and schematic of each module separately. The majority of modules contain a multi-bit register as the core unit for data storage. The core units in ALU, Regfile_IF, and State are respectively the adder, multiplexer, and counter, used to implement data operations, i/o management, and count-based timing control.

Extended Data Fig. 7 The result of digital computation by the 2D RV32 processor.

In the first instruction, an operand stored in the register file, “1946” (the year ENIAC was manufactured), and another operand in the instruction as the immediate number, “25”, are added together. On the first clock cycle of this instruction, the valid 32-bit PC is sent to the ibus with the pc_valid flag. The instruction is then sent to RV32-WUJI in the next clock cycle with the inst_valid flag. After several clock cycles for decoding, the counter starts counting while the computation begins: First, the lowest bits of “1946” (“0”) and “25” (“1”) are entered separately into the ALU as rs1 and imm, whose names represent the data from the 1st source register and the immediate numbers. After the addition between the lowest bits is finished, the result bit is written back to the register file as rd, representing the destination register, and the carry is stored in the ALU. Then the second lowest bits are entered and added in the next clock cycle, while the carry stored in the ALU in the last clock cycle is included in the addition this time. The calculation continues until the counter reaches 32 and all 32-bit calculations are complete. A similar calculation is performed in the second instruction, except that both input operands, “1971” and “53”, are from the register file. The final result is 2024, which is 1971 plus 53.

Supplementary information

Supplementary Information

Supplementary Figs. 1–12, Supplementary Tables 1 and 2 and Supplementary References.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Ao, M., Zhou, X., Kong, X. et al. A RISC-V 32-bit microprocessor based on two-dimensional semiconductors. Nature 640, 654–661 (2025). https://doi.org/10.1038/s41586-025-08759-9

Received:

Accepted:

Published:

Issue date:

DOI: https://doi.org/10.1038/s41586-025-08759-9

This article is cited by

-

Bioinspired high-order in-sensor spatiotemporal enhancement in van der Waals optoelectronic neuromorphic electronics

Nature Communications (2025)

-

Computer processors built from 2D materials

Nature (2025)