Abstract

With the growing awareness of energy savings and consumption for a sustainable ecosystem, the concept of iontronics, that is, controlling electronic devices with ions, has become critically important. Composite devices made of ions and solid materials have been investigated for diverse applications, ranging from energy storage to power generation, memory, biomimetics, and neuromorphic devices. In these studies, three terminal transistor configurations with liquid electrolytes have often been utilized because of their simple device structures and relatively easy fabrication processes. To date, oxide semiconductors and layered materials have mainly been used as active materials. However, inorganic compound semiconductors, which have a long history of basic and applied research, hardly function as channel materials in ion-gated transistors, partly because of the Schottky barrier at the electrode interface. Herein, we show that a typical group III–V compound semiconductor, InP, is available as a high-performance channel for ion-gated transistors with an on/off current ratio of ≈ 105 and a subthreshold swing as small as 93 mV/dec at room temperature. We fabricated AuGe/Ni contact electrodes via annealing to obtain the Ohmic contacts over a wide temperature range. The electrical resistance of InP was drastically decreased by the ionic liquid gating, which led to an electrically induced insulator-to-metal transition. Bulk compound semiconductors are well characterized and have relatively high carrier mobilities; thus, devices combined with electrolytes should prompt the development of iontronics research for novel device functionalities.

Similar content being viewed by others

Introduction

Recent progress in iontronics, in which ions play an important role in the device architecture, has attracted significant attention from various research areas1,2,3,4. For example, along with conventional Li-ion batteries, all-solid-state batteries are expected to become key devices for achieving sustainable systems for human activities. In addition, in recent studies on unused energy, energy harvesting from waste heat via the ionic thermoelectric effect5,6,7,8,9 and from mechanical vibration with polarized ions10,11,12,13 have been studied as possible small power sources in self-powered systems. Nano scale interfaces between ions and electronic materials are ideal for the exploration of novel device functionalities.

In the study of iontronic devices, ion-gated field-effect transistors (FETs) are recognized as important research platforms4,14,15. This is because the physical and chemical properties of channel materials can be modified by the alignment of ions on the surface, which is controlled by an external voltage. For example, various electronic phase transitions have been realized in functional materials with FET structures4,15 by accumulating high-density charge carriers at the solid–liquid interface. Moreover, beyond the typical scheme of electrostatic FETs, ion intercalations16,17,18, redox reactions15, and neuromorphic synaptic devices19,20 have been demonstrated. On the other hand, however, the available channel materials for ion-gated FET configurations have been limited mostly to oxides, organic semiconductors, and two-dimensional layered materials; thus, expanding the range of these materials is crucial to accelerating the development of basic ionotronics research.

One of the target materials for the transistor channels is group III-V compound semiconductors, which have played the central roles in modern high-speed circuits by utilizing modulation-doped FET structures21. These compound semiconductors have moderate band gaps ranging from 0.3 eV to 1.5 eV and relatively high electron mobilities, forming sharp hetero interfaces to construct defect-free two-dimensional electron gases21. As a result, a high-speed switching operation, low energy consumption, and a large on/off ratio of the drain-source current ID are realized. Thus, the application of bulk compound semiconductors to the channel materials of ion-gated FETs is utmost importance for the pursuit of high-performance iontornic devices.

The fabrication of ion-gated FETs based on III-V semiconductors has been difficult, partly because of the high contact resistance at the interface between the electrodes and channels. This problem is typically encountered when fabricating devices based on insulating materials with low Fermi levels. For example, in the case of oxide insulators such as SrTiO3 and KTaO3, Ar ion bombardment was performed to etch the underlayer of the electrodes22,23 and selectively remove oxygen ions. This oxygen deficiency induced thin conductive layers, which resulted in the Ohmic contact at the electrode interfaces24,25,26. As for the compound semiconductors, it was reported that the contact resistance at room temperature was reduced by employing AuGe/Ni electrodes with high-temperature annealing treatments27,28,29,30,31. This suggests that achieving low contact resistance in ion-gated devices based on III-V semiconductors over a wide temperature range can be done by finding an appropriate annealing condition through a systematic investigation of the annealing process.

In this study, we present the fabrication of ion-gated FETs based on semi-insulating InP and gate control of the electrical transport properties (see the “Methods” for details of the device fabrication process and measurements). A small amount of ionic liquid was applied to the surface of an InP single crystal to form an electric double layer transistor structure, as shown schematically in Fig. 1a. AuGe/Ni electrodes with a thickness of approximately 140/35 nm were deposited by resistance heating and electron beam evaporations and subjected to a high-temperature annealing to obtain a good Ohmic contact. We systematically investigated the annealing time tA dependences of the transfer curves (the change in ID as a function of the gate voltage VG) and of the electrical transport at temperatures as low as 10 K. Finally, it is revealed that metallic transport was induced in the initially insulating InP by an ionic-liquid gating, which provides a further research arena for the development of iontronics using high-carrier-mobility materials.

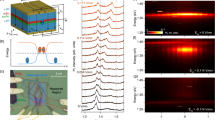

Structure of ion-gated InP device and annealing effect on contact electrodes. (a) Schematic device structure of ion-gated InP with electric double layers. When a positive gate voltage VG is applied to the gate electrode, the cations (DEME+) and anions (FTSI−) are aligned on the channel and the gate electrode, respectively, to form the electric double layers. Here, S and D represents the source and drain electrodes, respectively. See the “Methods” for details of the device fabrication. (b) Annealing effect on contact electrodes. After annealing, Ni in the topmost layer diffuses toward the InP surface. (c) Typical transfer characteristics (drain-source current ID versus gate voltage VG) at 295 K for different annealing times tA. The annealing temperature was 420 °C for all the measurements. The values of ID increases with increasing VG, showing that the electron carriers are doped under positive VG for annealed devices. The drain voltage VD was 0.1 V. (d) Two terminal resistance R2 as a function of tA. The values of R2 at 295 K were evaluated as the resistance between the drain and source electrodes.

Results and discussion

Details of the device structure and the concept behind its fabrication are summarized in Fig. 1. Figure 1a schematically shows the device structure of the ion-gated InP, where the ionic liquid between the gate electrode and channel acts as a gate dielectric. When VG is applied to the gate electrode, electric double layers are formed on the surface of InP and the gate electrode, inducing a strong electric field at the interfaces. The drain and source electrodes were fabricated by depositing AuGe and Ni, respectively, as shown in Fig. 1b. According to previous reports27,28,29,30,31, the contact resistance of n-type InP can be reduced using AuGe/Ni electrodes via additional annealing procedures. Ni in the topmost layer diffuses toward the InP surface through AuGe during annealing. Consequently, an intermediate semiconductor layer, possibly an alloy of Ni and P, is formed to suppress the contact resistance30. Figure 1c shows the transfer characteristics at 295 K for the ion-gated InP devices A (tA = 0 min), B (tA = 5 min), C (tA = 10 min), and D (tA = 20 min). The annealing temperature was set at 420 °C throughout the present study based on the discussions on making an Ohmic contact in previous studies27,28,29,30,31. When tA was 0 min, ID did not increase under positive VG. In contrast, ID showed an upturn at approximately VG = 1.0 V and increased further with increasing VG in the annealed devices. Here, both the forward and reverse scans were plotted and mostly overlapped. This shows that the charge carriers were induced in a reversible manner against sweeping VG. Moreover, the negligible hysteresis suggests that the electrochemical reaction was unlikely. Figure 1d shows the room-temperature values of the two-terminal resistances R2 of devices A, B, C, D, and E (tA = 30 min) for VG = 1.8 V. The values of R2 consist of the contact resistance and channel resistance; therefore, a comparison of R2 can be a good measure for qualitatively evaluating the modulation of the contact resistance. With increasing tA, R2 significantly decreased from 3 MW to 4 kW for several minutes of annealing. This strongly suggests that the contact resistance was suppressed owing to the formation of an Ohmic contact at the interface between electrode and InP. Notably, the typical tA value needed to obtain Ohmic electrodes in InP only ranged from several seconds to minutes in previous reports27,28,29,30. These recipes seem reasonable because R2 at 295 K hardly varied for longer tA, as shown in Fig. 1d.

At low temperatures, however, R2 exhibited a drastic contrast. To evaluate the tA dependence of the contact resistance, we systematically measured R2 of the ion-gated InP with varying VG and temperatures. Figure 2 shows the temperature dependence of R2 at VG = 1.8 V for devices B, C, D, and E. When tA = 5 min, R2 exhibited insulating behavior, even though the room-temperature value of R2 was suppressed to the order of 10 kW by gating. When we annealed the device for 10 min, R2 was measurable down to the lowest temperature of the present experiments, 10 K. For further expansion of tA, the low-temperature values of R2 were much more suppressed but did not show a drastic change when tA was extended from 20 to 30 min. This suggests that the formation of the intermediate semiconductor layer at the electrode interface is almost saturated at around 20 min. See Supplementary Figure S1 for the temperature dependence of R2 on other VG values.

Comparison of temperature T dependence of two-terminal resistance R2 for different annealing times tA. The gate voltage VG was maintained at 1.8 V for all the devices. With increasing tA from 5 min for device B to 10 min for device C and 20 min for device D, R2 at low temperatures decreased. When tA was further extended to 30 min for device E, the T dependence of R2 moderately changed, suggesting that the annealing effect was saturated at approximately tA = 20 min.

Atomic force microscopy (AFM) analyses of AuGe/Ni electrodes. (a)-(d) AFM topography image of boundary of InP and AuGe/Ni electrode. The four devices, F, G, H, and I, were prepared with the annealing times of tA = 0, 10, 20, and 30 min, respectively. (e) Height profile along red lines in (a) and (c). The height of the AuGe/Ni electrode remained almost constant in device F with tA = 0 min. The unevenness in the height of AuGe/Ni layers was confirmed in devices H, which was due to the atom migration through the high-temperature annealing process. See Supplementary Figure S2 for the height profiles of other devices.

The effect of annealing on the electrodes was also confirmed through the analysis with atomic force microscopy (AFM). For the AFM measurements, we prepared four devices: F (tA = 0 min), G (tA = 10 min), H (tA = 20 min), and I (tA = 30 min). Figure 3 shows the development of the surface morphology of the electrodes with increasing tA. At tA = 0 min, the AFM topography image in Fig. 3a demonstrated a sharp boundary between the electrode and InP. With increasing tA up to 30 min, we found that the surface and edges of the electrodes became uneven, as shown in Fig. 3b-d. We also investigated the height profile along the red lines in Fig. 3a-d and plotted them in Fig. 3e and Supplementary Fig. S2, where the origin of the x-axis was set at the edge of the electrodes. Figure 3e shows the data only for devices F and H for clarity. The height of the AuGe/Ni electrode was almost constant in device F with tA = 0 min; in contrast, the heights of the AuGe/Ni layers exhibited unevenness in device H, which was more pronounced for devices with longer tA (see Supplementary Fig. S2). This indicates that atom migration and the formation of the intermediate semiconductor layer continuously developed with tA in this time scale. From the results in Figs. 2 and 3, we conclude that at least 20 min of annealing are required to obtain the low contact resistance that is valid for wide temperature regions. This value of tA is much longer than those in previous studies, where the typical tA ranged from several seconds to minutes27,28,29,30,31. Although the low temperature electrical transport measurement was enabled, the mechanism for reducing the contact resistance with long annealing time is unclear. Further investigations such as composition and structural analyses of the intermediate semiconductor layer is necessary, which will be conducted using a high energy X-ray bean in a synchrotron radiation facility and reported in a future work.

After determining tA = 20 min at 420 °C as an appropriate annealing condition, we fabricated another InP device with tA = 20 min (device J) and systematically investigated the transistor characteristics. Figure 4a shows the transfer curves of device J at 295 K when the drain-source voltage VD was 0.5 V. A negligibly small hysteresis was observed, where the forward and reverse scans overlapped. The threshold voltage VTH was estimated to be approximately 1.25 V from the slope of the transfer curve, as indicated by the dashed line. As seen in the transfer curve plotted with a log scale, the subthreshold swing was found to be 93 mV/dec at VG = 0.7 V, suggesting a potential for high-performance transistor operation. The ratio of the on- and off-currents was as large as 105, indicating the large tunability of the carrier densities in the InP channel by the gate electric field. The FET properties were also confirmed by observing the output curves, as shown in Fig. 4b. Figure 4c shows the temperature dependence of the sheet channel resistance RS, which was estimated by normalizing the four-terminal resistance to the length and width of the channel (see Supplementary Fig. S3). The temperature dependence of RS demonstrated insulating behavior when VG was less than 1.2 V. With increasing VG, RS was suppressed and finally showed a metallic behavior when VG = 2.0 V was applied, achieving an electrically induced insulator-to-metal transition.

The insulator-to-metal transition shown in Fig. 4c is consistent with the transfer curve shown in Fig. 4a. As shown in Fig. 4c, the increase in RS at low temperatures was suppressed by applying VG. The values of RS showed divergence-like temperature dependencies below VG = 1.2 V and shifted to nearly temperature independent behavior above VG = 1.2 V. Meanwhile, in Fig. 4a, VTH was about 1.25 V, above which ID steeply increased in proportion to VG. Therefore, the insulator-to-metal transition in ion-gated InP would have occurred at VG ≈ VTH. The reason that RS versus temperature curves showed the insulating behaviors in the subthreshold regime, where VG is lower than VTH, would be that the carrier density is not sufficient to maintain the electrical conduction at low temperatures32,33,34. In other words, percolative carrier doping is realized below VTH. It is suggested that the electrically induced carriers can be inhomogeneously doped because of the imperfect ordering of cations and anions32,35 and also the Coulomb potential induced by ions near the interface36, which makes mobile carriers localize at low temperatures. When VG becomes larger than VTH, the chemical potential rises into the conduction band, and the electrons are accumulated according to the relationship between the sheet carrier density N and VG, eN = CEDL(VG-VTH). Here, e and CEDL are the elementary charge and the capacitance of the electric double layer, respectively. Therefore, when a typical value of CEDL, 10 µF/cm2 37,38,39,40,41, is tentatively assumed, N at VG = 2 V is 5 × 1013 cm−2. High-density electrons are induced in the FET channel in this VG region; thus, the randomness of the carrier distribution is less dominant in the electrical conduction. Consequently, the gated surface electrons exhibited metallic conduction from room temperature to the lowest temperature as shown in Fig. 4c.

Insulator-to-metal transition in ion-gated InP. (a) Transfer curve (gate voltage VG dependence of drain-source current ID) of device J at 295 K. The annealing time tA of device J was 20 min. The drain-source voltage VD was 0.5 V. The threshold voltage VTH was estimated to be approximately 1.25 V from the slope of the curve. (b) Output characteristics (VD dependence of ID) at 295 K of device J. A typical n-type field effect transistor operation was observed. (c) Temperature T dependence of sheet resistance RS of device J. The values of RS at low temperatures were suppressed with increasing VG, and an almost flat T dependences was observed when VG was larger than 1.2 V.

Conclusions

We revealed the systematic evolution of the electrical transport properties of ion-gated InP against electrostatic carrier doping. With recent advancements in iontronics, it is highly required to expand the material variety of channels for ion-gated FETs. In particular, the application of III-V compound semiconductors to iontronic devices is promising because of their relatively high carrier mobilities and well characterized material properties. We fabricated the electric double layer transistors based on the semi-insulating InP single crystals. The n-type transistor operations were successfully observed by reducing the contact resistance at the electrode interface with AuGe/Ni Ohmic contacts through the annealing procedure. Ion gating is a versatile technique for carrier doping and continuous modulation of the carrier density at the surface of the InP single crystal, resulting in achieving the electrically-induced insulator-to-metal transition, which has been difficult to realize in ion-gated FETs based on bulk compound semiconductors. The present approach is applicable to other compound semiconductors, which would lead to the emergence of novel electronic properties and the development of the iontoronic devices.

Methods

Device fabrication

To control the electron carrier density in InP, an electric double layer transistor structure was fabricated on the (111) surface of Fe-doped semi-insulating InP. An optical image of the device is presented in Supplementary Fig. S3. The single crystals of InP that we used in this study were doped with Fe to increase resistivity. We purchased the single crystals with electrical resistivity larger than 107 Ωcm at room temperature from MO Sangyo Co., Ltd. The electrodes and channels were formed using standard photolithography and a metal evaporation process. We first evaporated the AuGe layer by resistance heating evaporation and then the Ni layer by electron beam evaporation, whose thicknesses were approximately 140 and 35 nm, respectively. To reduce the contact resistance, the devices were annealed after the lift-off process, as discussed in detail in the main text (see Supplementary Figure S4 for the comment on the contact resistance in Device J). A small amount of an ionic liquid, N,N-dimethyl-N-(2-methoxyethyl)-N-methylammonium bis-(trifluoromethylsulfonyl)-imide (DEME-TFSI), was deposited to cover both the channel and gate electrodes and perform gating experiments with a side gate configuration. When VG is applied, an electric double layer is formed on the surface of the InP channel. The thickness of the electric double layer is order of 1 nm and works as a nano-gap capacitor in the transistor configuration. It has been reported that the capacitance of the electric double layer is as large as 10 µF/cm2 37,38,39,40,41 or larger. Here, it is noted that the strong electric field induced in the electric double layer can cause an unexpected chemical reaction on the channel surface. That is often accompanied by an irreversible modulation of electrical conductivity in channels. In Figs. 1c and 4a, the transfer curves were shown for both the forward and reverse scans. The reversibility of ID and the negligible hysteresis suggest that the chemical reaction was unlikely to have occurred.

Electrical measurements

To evaluate the transfer characteristics (the gate voltage VG dependence of the drain-source current ID) of the ion-gated InP, ID was measured under the application of VG and the drain-source voltage VD with a semiconductor parameter analyzer (E5270, Agilent). The temperature dependence of the sheet resistance RS was measured from 295 K to 10 K using a conventional Gifford-McMahon type refrigerator (PASCAL CO., LTD.) and a temperature controller (model 335, Lake Shore Cryotronics). In the ion-gated device structures, ID can flow through the InP channel and the ionic liquid. See Supplementary Figure S5 for the evaluation of the resistance of the ionic liquid.

Data availability

The authors confirm that the data supporting the findings of this study are available within the article and the supplementary information.

References

Li, T. & Xiao, K. Solid-state iontronic devices: mechanisms and applications. Adv. Mater. Technol. 7, 2200205 (2022).

Wei, D., Yang, F., Jiang, Z. & Wang, Z. Flexible iontronics based on 2D nanofluidic material. Nat. Commun. 13, 4965 (2022).

Chun, H. & Chung, T. D. Iontronics Annual Rev. Anal. Chem. 8, 441–462 (2015).

Bisri, S. Z., Shimizu, S., Nakano, M. & Iwasa, Y. Endeavor of iontronics: from fundamentals to applications of ion-controlled electronics. Adv. Mater. 29, 1607054 (2017).

Pu, S. et al. Thermogalvanic hydrogel for synchronous evaporative cooling and low-grade heat energy harvesting. Nano Lett. 20, 3791–3797 (2020).

Li, T. et al. Cellulose ionic conductors with high differential thermal voltage for low-grade heat harvesting. Nat. Mater. 18, 608–613 (2019).

Han, C. G. et al. Giant thermopower of ionic gelatin near room temperature. Science 368, 1091–1098 (2020).

Massetti, M. et al. Unconventional thermoelectric materials for energy harvesting and sensing applications. Chem. Rev. 121, 12465–12547 (2021).

Inoue, D., Niwa, H., Nitani, H. & Moritomo, Y. Scaling relation between electrochemical seebeck coefficient for Fe2+/Fe3+ in organic solvent and its viscosity. J. Phys. Soc. Jpn. 90, 033602 (2021).

Moon, J. K., Jeong, J., Lee, D. & Pak, H. K. Electrical power generation by mechanically modulating electrical double layers. Nat. Commun. 4, 1487 (2013).

Helseth, L. E. & Guo, X. D. Contact electrification and energy harvesting using periodically contacted and squeezed water droplets. Langmuir 31, 3269–3276 (2015).

Biutty, M. N. et al. Ion transport through layered hydrogels for low-frequency energy harvesting toward self-powered chemical systems. J. Mater. Chem. Mater. 10, 11881–11892 (2022).

Ono, S. Recent advanced application of ionic liquid for future iontronics. Chem. Record. 23, e202300045 (2023).

Wang, D. et al. Recent advanced applications of ion-gel in ionic-gated transistor. npj Flex. Electron. 5, 13 (2021).

Zhang, L. et al. Redox gating for colossal carrier modulation and unique phase control. Adv. Mater. 36, 2308871 (2024).

Rajapakse, M. et al. Intercalation as a versatile tool for fabrication, property tuning, and phase transitions in 2D materials. npj 2D Materials and Applications 5, 30 (2021).

Yue, Z. Ionic gating for ion intercalation. Nat. Reviews Phys. 3, 42254 (2021).

Chen, H. et al. Protonation-induced colossal chemical expansion and property tuning in NdNiO3 revealed by proton concentration gradient thin films. Nano Lett. 22, 8983–8990 (2022).

López, A. et al. Electrolyte gated synaptic transistor based on an ultra-thin film of La0.7Sr0.3MnO3. Adv. Electron. Mater. 9, 2300007 (2023).

Miao, T. et al. Gate--tunable anisotropic oxygen ion migration in SrCoOx: toward emerging oxide-based artificial synapses. Adv. Intell. Syst. 5, 2200287 (2023).

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices (Wiley, 2006).

Reagor, D. W. & Butko, V. Y. Highly conductive nanolayers on strontium titanate produced by preferential ion-beam etching. Nat. Mater. 4, 593–596 (2005).

Harashima, S. et al. Coexistence of two-dimensional and three-dimensional Shubnikov–De Haas oscillations in Ar+-irradiated KTaO3. Phys. Rev. B. 88, 085102 (2013).

Chang, J. W., Lee, J. S., Lee, T. H., Kim, J. & Doh, Y. J. Controlled formation of high-mobility shallow electron gases in SrTiO3 single crystal. Appl. Phys. Express. 8, 055701 (2015).

Bruno, F. Y. et al. Anisotropic magnetotransport in SrTiO3 surface electron gases generated by Ar+ irradiation. Phys. Rev. B. 83, 245120 (2011).

Ngai, J. H. et al. Electric field tuned crossover from classical to weakly localized quantum transport in electron doped SrTiO3. Phys. Rev. B. 81, 241307(R) (2010).

Erickson, L. P., Waseem, A. & Robinson, G. Y. Characterization of ohmic contacts to InP. Thin Solid Films. 64, 421–426 (1979).

Del Alamo, J. A. & Mizutani, T. AuGeNi ohmic contacts to n-InP for FET applications. Solid State Electron. 31, 1635–1639 (1988).

Kuphal, E. Low resistance ohmic contacts to n- and p-InP. Solid State Electron. 24, 69–78 (1981).

Morais, J., Fazan, T. A., Landers, R. & Sato, E. A. S. Ohmic contacts formation on n-InP. J. Appl. Phys. 79, 7058–7061 (1996).

Murakami, M. & Koide, Y. Ohmic contacts for compound semiconductors. Crit. Rev. Solid State Mater. Sci. 23, 1–60 (1998).

Xia, Y., Xie, W., Ruden, P. P. & Frisbie, C. D. Carrier localization on surfaces of organic semiconductors gated with electrolytes. Phys. Rev. Lett. 105, 036802 (2010).

Li, M., Graf, T., Schladt, T. D., Jiang, X. & Parkin, S. S. P. Role of percolation in the conductance of electrolyte-gated SrTiO3. Phys. Rev. Lett. 109, 196803 (2012).

Sasama, Y., Yamaguchi, T., Tanaka, M., Takeya, H. & Takano, Y. Low-temperature carrier transport in ionic-liquid-gated hydrogen-terminated silicon. J. Phys. Soc. Jpn. 86, 114703 (2017).

Mezger, M. et al. Molecular layering of fluorinated. Science. 322, 424–428 (2008).

Petach, T. A. et al. Disorder from the bulk ionic liquid in electric double layer transistors. ACS Nano. 11, 8395–8400 (2017).

Zhou, Y. & Ramanathan, S. Relaxation dynamics of ionic liquid-VO2 interfaces and influence in electric double-layer transistors. J. Appl. Phys. 111, 084508 (2012).

Saito, Y. & Iwasa, Y. Ambipolar insulator-to-metal transition in black phosphorus by ionic-liquid gating. ACS nano. 9, 3192–3198 (2015).

Yoshida, M. et al. Gate-optimized thermoelectric power factor in ultrathin WSe2 single crystals. Nano Lett. 16, 2061–2065 (2016).

Ono, S., Miwa, K., Seki, S. & Takeya, J. A comparative study of organic single-crystal transistors gated with various ionic-liquid electrolytes. Appl. Phys. Lett. 94, 063301 (2009).

Shimotani, H. et al. Insulator-to-metal transition in ZnO by electric double layer gating. Appl. Phys. Lett. 91, 082106 (2007).

Acknowledgements

This work was supported by JSPS KAKENHI Grant Numbers JP20H02830, JP20KK0318, JP21H05016 and JP23K20278 and by FIRSTBANK OF TOYAMA SCHOLARSHIP FOUNDATION.

Author information

Authors and Affiliations

Contributions

S.S., H.S., A.O., and K.M. fabricated the devices. S.S. and S.O. developed the measurement system. S.S., H.S., T.H., and S.O. planned the study and performed electrical measurements. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Below is the link to the electronic supplementary material.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Shimizu, S., Shioya, H., Hatano, T. et al. Electrically induced insulator-to-metal transition in InP-based ion-gated transistor. Sci Rep 14, 30364 (2024). https://doi.org/10.1038/s41598-024-81685-4

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-024-81685-4