Abstract

Quantum-dot Cellular Automata (QCA) is a new nanoscale computing architecture that has ultra-low power, high device density, and possible applicability to future nano-communication systems. In this paper, we present optimized QCA-based even parity generator and parity checker circuits with efficient XOR logic. The proposed designs reduce area and cell count significantly while maintaining stable logical operation. The circuits were drawn and simulated in QCADesigner-E and analyzed using QCAPro for energy dissipation and polarization error. Results show that the proposed parity generator reduces 57% cell count and 20% area over existing designs, whereas the parity checker reduces 67% cell count and 12.5% area. These improvements indicate the potential of the proposed circuits for low-power and small-area error detection mechanisms in nanoscale communication systems.

Similar content being viewed by others

Introduction

From transparent connectivity to coherent Internet of Things (IoT), data management, and cloud computing merge to revolutionize how one connects with technology1. On-demand self-service provisioning gives access to scalable resources for storing, processing, and analyzing data in real-time. IoT will physically bring devices onto the internet to collect and exchange data, driving innovation in smart systems and industrial automation2,3. These technologies will help improve decision-making at all levels and operational efficiencies in most sectors with remote monitoring, predictive maintenance, and integration with intelligent systems4. Quantum Cellular Automata (QCA) computing science involves complex mathematical equations performed at incredible rates using quantum mechanics. The QCA method represents and manipulates quantum states instead of the conventional binary computing interpretations5. Their computer systems are, therefore, very effective and always achieve parallel computation using the least energy. Greater integration of QCA due to cloud computing and the IoT will increase their processing power, thus allowing faster, more secure, and more efficient data management methods. One can also conceive of formulating it in such a way that links improvements in machine learning and encryption, among others, to having the availability of computing capability to take on more complex tasks. This would be coupled with error detection techniques; the parity generator and parity checker circuits are important in ensuring that an extra bit shall be added to the binary message during fault finding at transmission and ensure the integrity of the data. These circuits do not allow the loss and corruption of data in cloud computing, where huge volumes of information are being transferred, and in every type of IoT system where sensors provide continuous data. Hence, parity circuits’ overall reliability, safety, and utility in cloud computing and the IoT are guaranteed.

After years of rigorous progress, the current transistor-based technology has achieved near saturation regarding size optimization, power efficiency, and computational progress6,7. The emerging QCA technology allows researchers to consider it a CMOS replacement because of its less energy utilization8,9. Current research into the basic circuit’s efficiency in QCA technology is also generating interest. During signal transition and propagation, current flows in the CMOS circuit but not in the QCA circuit10. Instead, in QCA technology, the Quantum-dot interacts with each other by Coulombic repulsion11. The majority and inverter gates make up any QCA circuit. Quantum-dot arrays and Quantum-dot cross-wires, in addition to these two fundamental units, are essential components of any QCA circuit12,13. Thus, decreasing the number of gates, which has a notable effect on the price of a QCA circuit, has been the primary emphasis while constructing area and cost-efficient QCA circuits14,15.

The design of the parity-generating circuit, on the other hand, is critical with this technology. It generates the parity bit in the transmitter circuits16. In digital systems, a hybrid circuit or devices comprising parity checkers and generators are frequently used to identify 1-bit defects in the transferred information expression. Also, identifying a mistake in a received message is a critical topic in numerical communication17,18. The parity bit is used to detect such flaws. An additional bit is padded with the information during the transmission of a binary message via the network to recognize the fault inside the message19. The parity bit is the name for this extra bit. It is padded to make the overall number of 1 s in a message even or odd (including the parity bit). The article presents a novel QCA-based even parity checker and generator circuits with low latency and a low number of cells. The recommended circuits are modeled in this study using the QCADesigner-E in coherence vector engine and bistable vector engine mode to compute average energy dissipation and quantum cost. The simulations show that the circuits work correctly. In summary, the investigation’s objectives are:

-

Designing efficient even parity checker and generator circuits using a small quantity of cells;

-

Designing short latency even parity generator and checker in quantum technology;

-

Demonstrating nano communication architecture using proposed circuits;

-

Using QCADesigner-E to simulate the suggested circuits in coherence vector engine and bistable vector engine modes to compute average energy dissipation and quantum cost.

Aside from its theoretical value, the proposed QCA-based checker and generator circuits find industrially appealing implementations in a number of application areas. In particular, such energy-efficient and compact implementations are pivotal to making real-time fault detection feasible in resource-constrained nano communication systems, e.g., implantable medical implants, aerospace control systems, and autonomous sensor networks. These application fields require highly dependable and low-power error detecting units that can sustain data integrity under space, energy, or environmental constraints. The compact size of the suggested circuits and low-level energy dissipation render them especially suitable for next-generation hardware security modules, on-chip data validation, and energy-constrained nanoscale processors, where CMOS cannot meet demands. This research, therefore, not only enriches the fundamental QCA circuit design but also presents a scalable and application-ready building block towards next-generation nanoelectronic systems for safety-critical and energy-constrained applications.

The following is an overview of the rest of the article. The second section delves into the basics of quantum skill and interconnected works. The proposed work is presented in Sect. “Proposed circuits”, which includes a full overview of the even parity checker and generator circuits. Section “Simulation tools and results” summarizes all of our general observations from our intended work and briefly summarizes all of the important research achievements that have been obtained throughout this project. Finally, Sect. “Conclusions” represents the paper’s conclusion.

QCA fundamentals

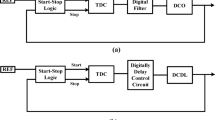

The cell is a critical part of QCA technology. Each QCA cell contains four quantum dots and two electrons20. A pair of electrons are contained in two diagonal neighboring dots, and two pairs of quantum dots are situated in the cell’s vertices. Polarity P = + 1 (logic 1) and P=−1 (logic 0) are two modes inserted in any diagonal antagonistic Quantum-dot pair placement, as demonstrated in Fig. 1. (a). Unlike CMOS design, which utilizes AND/OR logic, QCA’s majority gate is OUT (IN1, IN2, IN3) = IN1×IN2 + IN3×IN2 + IN1×IN3 (Fig. 1 (b))21. By altering an input to continuous polarity, this majority constituent might effectively be adapted near a two-input OR, or AND gate22. The majority gate works as an AND gate whenever three inputs are regulated to P = −1 (logic 0), and as an OR gate whenever P = + 1 (logic 1). Figure 1(c) depicts an inverter with a pair of distinct configurations that can be likened to NOT logic in CMOS architecture23,24.

Dissimilar to the CMOS field, the clock is QCA’s important feature. One important benefit of using clocking in QCA is the ability to restore signals with loss and attenuation25. These clocking methods are often created using an electric field26. Establishing a robust QCA is significantly hampered by the open problem of QCA array switching. Although QCA benefits from the physical ground mode, the logical solution must be mapped to the system’s issue27. A meta-stable state emerges and there is a delay in reaching ground state stability when a QCA system is abruptly turned on because it defaults to a polarization mode of P = + 1 or P=−1, or their polarization combination. Four modes are essential for an adiabatic pipe-lining cycle clocking technique: Switch, Hold, Release, and Relax. Hold keeps the inter-dot barrier potential high so that no outside source may affect the QCA cell, while switching overcomes it28. The kernel refers to the clocking technology used in a QCA circuit29. The adiabatic switching principle looks to be the most efficient for a QCA system. The QCA clock is the only source of synchronization that delivers data from one end to the other. The clock region is the area where two or more QCA cells are positioned under a certain clock signal30.

(a) QCA cell deferent polarization, (b) Majority gate, and (c) Inverter gate31.

Related works

We examine the most recent papers on the subject in this area.

A QCA-based error detection circuit for nano communication networks has been proposed by Das, et al.32. An even parity checker circuit using QCA and an even parity-generating circuit with low power consumption have been described in this study. The suggested parity generator and even parity checker were developed using a novel XOR gate arrangement. The suggested parity checker and generator have surpassed the current design because to its lower latency, area, and cell count. The comparison shows that the circuits are denser and faster than the ones currently in use. Using the proposed circuits and nano communication architecture, the efficacy of this design has also been demonstrated. The proposed designs that validate the enhanced processing speed at the nano-scale have been evaluated using a variety of measures, such as density, latency, and a logic gate. Although the limited number of cells in this architecture is one of its primary advantages, its extremely poor speed is a significant drawback.

Additionally, effective QCA-based logical circuits with power dissipation analysis have been proposed by Sheikhfaal, et al.33. The structural and power problems of the previously published 5-input majority gates have been thoroughly investigated. The average leakage and switching power dissipations in these architectures have been investigated using an accurate QCA power dissipation model. A unique low-complexity, low-power circuit that transforms an inefficient five-input majority gate into an efficient two-input XOR gate has been designed and put into use by scientists in response to the limitations. In the following phase, we used the suggested XOR gate to design and implement various length parity generating circuits up to 32 bits. A thorough power consumption comparison between the suggested circuits and earlier models has also been carried out by researchers. These circuits have a high voltage. In other words, the product takes a long time to create, and the quantity of cells and their consumption area are regarded as major drawbacks.

Based on QCA, Santra and Roy34 have suggested parity generator and checker architectures. A QCA circuit requires less hardware thanks to the XOR gate, which also makes the circuits easier to comprehend in terms of level, latency, and cell count. This article has given a low-tech way to make a special XOR gate that can be used to make a number of complex QCA circuits. Despite its simple form, the proposed XOR gate has a strong capacity to construct digital circuits. To verify that the proposed design works, several complex implementations of parity generator and parity checker circuits have been proposed and simulated using the QCA Designer tool. Some of the most recent designs have been compared to these outcomes. The effectiveness of this method in implementing different digital circuits has been validated by the simulation results and physical relationships. The provided circuit is slow and takes a long time to generate the desired output, even with all of the positive situations mentioned.

A design for cell configurations in QCA has been proposed by Hashemi, et al.35. In order to construct arbitrary functionalities at the nanoscale, QCA has developed as a revolutionary nanotechnology that promises extra low power and an incredibly dense and fast structure. A shift between 90 and 45 QCA cells has been noted in earlier designs, indicating the necessity of properly arranging QCA cells in QCA circuits. However, new configurations for QCA cells have been presented in this article. These new configurations have been used to demonstrate a basic even parity generator with varying word sizes. This parity generator is designed from the bottom up using a thick and robust QCA XOR gate as the foundation. This work uses QCA Designer to model and implement the QCA circuits. According to the simulation results, these novel designs are more complex and have a larger area than the usual designs. However, as time passes and new and modern circuits are developed, it becomes increasingly apparent that these designs use a large number of cells and need an excessive amount of time to create output.

Circuits for a parity generator and checker have been proposed by Mustafa and Beigh36. The XOR gate implementations presented in this paper give the lowest possible complexity and cell count compared to the previously proposed designs. QCA implementations of combinational circuits, such as checkers and parity generators, have been given based on the proposed XOR gate designs. The proposed designs have been validated by researchers using simulations from the QCA designer tool. These simulations and techniques are important for constructing increasingly intricate circuits with QCA as the basis. However, in spite of all these benefits, the circuits offered are incredibly slow.

Finally, Singh, et al.37 recently provided energy dissipation analysis and suggested a novel robust realization of an XOR gate in QCA nanotechnology. Compared to earlier designs, the novel implementation of a two-input XOR gate in quantum-dot cellular automaton nanotechnology uses less space and power. Without the need for coplanar or multi-layer cross-over wiring, the recently suggested XOR gate can be implemented in a single layer. This makes it possible to create dense and incredibly resilient QCA circuits. The effectiveness of the suggested design has been examined using circuits for 4, 8, 16, and 32-bit even parity generators in a complicated array of QCA structures. Compared to the previously given designs, the suggested 4-bit even parity design has reduced area and latency. Compared to the best-reported previous architecture, the 32-bit even parity design takes up less space. The suggested design significantly improves area, latency, energy dissipation, and structural implementation requirements, according to the simulation results. Results of energy dissipation have been calculated with a precise QCAPro. This circuit is slower and contains more cells than the newly presented circuits, according to the comparisons.

Proposed circuits

The circuits linked to the even parity checker and generator are presented first in this section, followed by the circuit related to nano-communications, which is based on the even parity checker and generator circuits.

Even parity generator and checker circuits

A check bit, also known as a parity bit, is a bit added to a binary coding string. A simple type of error-detection coding is parity bits. Parity bits are typically used to represent the smallest components of a communication protocol. However, they can be used to represent a full message string of bits separately. The parity bit decides if the overall 1-bits in the string are even or odd. Hence, parity bits are divided into even and odd parity bits. Because XOR gates produce what is comparable to a check bit that creates an even parity, data transcoding with parity can be very efficient in electronics. XOR logic design is simply scalable to any number of inputs. The majority of parity-generating circuitry is made up of XOR structures. The XOR gate performs a logic operation on two inputs, producing logic ‘1’ if one of the inputs has logic ‘1’ and logic ‘0’ otherwise. Figure 2 shows the QCA-based XOR gate circuit that was employed. The XOR gate QCA layout has nine cells, a 0.01 µm2 area, and a latency of 0.25. All of the values of output bit OUT correspond to the values of inputs IN1 and IN2. The result matches the theoretical XOR gate values, indicating that the design is accurate38.

The used XOR gate38.

The sender node is where the parity generator is used. Consider a 3-bit message with message bits IN1, IN2, and IN3. Say the parity bit is OUT P once more. If all three bits of the message have an odd number of ones, OUT P is 1; otherwise, OUT P is 0. The XOR value between the inputs IN1, IN2, and IN3 is interpreted to be OUT P. For a better understanding of circuit performance, Fig. 3 shows the 3-bit even parity QCA configuration. Two XOR gates, 23 cells, 0.04 µm2 area, and 0.75 latency make up the QCA architecture.

By scanning the parity bit at the receiver premises, a combinational logic circuit known as a parity checker can identify errors. The received message is checked for even numbers of 1 s by an even parity checker. Imagine a 4-bit received a message with IN1, IN2, IN3, and IN4 (OUT P) message bits and OUT Pc error check bit. If the received message contains an odd number of ones, OUT Pc is ‘1’; otherwise, OUT Pc is ‘0’. As a result, if and only if OUT Pc is ‘1’, the received message contains an error. Figure 4 depicts the QCA architecture of a 4-bit even parity checker. This QCA layout consists of three XOR gates, 31 cells, 0.07 µm2 area, and a latency of 0.75.

Nano communication with suggested circuits in QCA technology

Figure 5 shows a schematic of a nano communication circuit with the recommended even parity generator and even-parity checker. The architecture is divided into three parts: the sender, the communication channel, and the receiver. Input and parity generator blocks are found in the sender section. The receiver section includes a parity checker and an output block. The inputs to the parity-generating block are IN1, IN2, and IN3. Figure 6 shows the implementation in QCA for the nano communication circuit. This QCA layout has 152 cells, a 0.26 µm2 size, and a 1.75 latency.

The procedure for communicating is as follows:

-

1.

The parity generator block on the sender side receives the three-bit text message, IN1, IN2, and IN3, as input and generates the parity bit.

-

2.

These three bits, IN1, IN2, IN3, and the created parity bit, are transmitted to their respective receivers over the communication channel.

-

3.

Finally, in the receiver section, the parity checker block processes the received four bits (IN1, IN2, IN3, and the created parity bit). To identify an error, the parity checker block validates the padded bit Pb across the obtained text message.

Simulation tools and results

The QCADesigner-E was created at the University of Bremen to expand the QCADesigner. The tool implements the estimation of QCA circuits’ power dissipation. The extension is dependent on the Coherence Vector Simulation Engine and is implemented as an additional simulation module. Furthermore, the QCADesigner-E is entirely compatible with QCA designs created with version 2.0.3 of the QCADesigner39. To model QCA circuits, this tool employs two different simulation engines. With default values, Coherence and Bistable Vector simulation approaches are used. As a result of using both engines in this experiment, the outcomes are comparable. To ensure accurate and consistent simulation results, both the Bistable Approximation Engine and Coherence Vector Engine were configured with optimized settings. Table 1 summarizes the key parameters used during simulation, including cell size, clock energy, and layer separation.

The suggested 3-bit even parity generator’s modeling findings are shown in Fig. 7. The yellow color represents the output in this diagram, while the blue hue represents the inputs. Figure 7 shows that when IN1 = 0, IN2 = 0 and IN3 = 0, the output is OUT P = 0. The output will be OUT P = 1 when IN1 = 0, IN2 = 0, and IN3 = 1. Thus, all output bit OUT P values correspond to the inputs IN1, IN2, and IN3. This outcome matches the parity generator circuit’s theoretical numbers, suggesting that the architecture is correct.

Figure 8 shows the modeling outcome of a 4-bit even parity checker. The yellow color indicates the output, while the blue color represents the inputs in this diagram. Figure 8 illustrates that when IN1 = 0, IN2 = 0, IN3 = 0, and IN4 = 0, the output will be OUT Pc = 0. When IN1 = 0, IN2 = 0, IN3 = 0, and IN4 = 1, the output will be OUT Pc = 1. When IN1 = 0, IN2 = 0, IN3 = 1, and IN4 = 0, the output will be OUT Pc = 1. As a result, all of the output bit OUT Pc values correspond to the inputs IN1, IN2, IN3, and IN4. This outcome matches the parity checker circuit’s theoretical numbers, proving the architecture’s correctness.

Finally, Fig. 9 exhibits the input waveforms IN1, IN2, and IN3, which have been carefully researched, and the simulation result of the suggested nano communication circuit in QCA technology. OUT PC is one of the comparator circuit’s outputs. In this setup, the output is produced after 1.75 clock phases.

Additionally, the QCAPro program was used to assess the suggested design40. Researchers at the University of South Florida created QCAPro, a probabilistic modeling tool, to examine QCA circuits, a nanotechnology paradigm for high-speed, low-power computing that goes beyond conventional CMOS. It provides information on circuit reliability and energy efficiency by estimating polarization errors and power dissipation in QCA circuits. QCAPro is an expert in error-power estimates, detecting extremely erroneous cells and estimating power loss during non-adiabatic switching operations, in contrast to QCADesigner, which concentrates on circuit design and simple simulation. It needs input files from QCADesigner to work and only runs in a Linux environment. To provide energy dissipation metrics, such as average, maximum, and minimum power loss, users create a QCA circuit in QCADesigner, prepare input combinations, and then execute QCAPro.

Though the QCA-based parity generator and checker circuits suggested in this paper have promising results in area, cell count, and energy consumption, one should not forget that the simulation environment is limited. The designs were simulated and verified with QCADesigner-E and QCAPro, which were both under idealized conditions. These tools accept ideal cell placement, but not fixed clocking, and do not precisely model fabrication imperfections, defects, or quantum-level variation. Thermal effects such as temperature variation and thermal noise are not simulated in QCADesigner-E simulations. Even though QCAPro provides rough energy dissipation and polarization error estimation, it accepts operation at a constant cryogenic temperature (e.g., 2 K), whereas in real situations, temperatures vary. Thus, published performance measurements will vary in actual implementations. This restriction identifies the need for future work to involve fault modeling, defect tolerance simulation, and experimental proof of correctness for a more thorough performance evaluation.

Table 2 compares QCA-based circuits regarding cell number, clock phases, area, and quantum cost (area × latency2). Also, in Table 2, the percentage of improvement of the presented plans compared to the best previous plans in the use of cells has been calculated. This paper uses Coplanar technology to create all proposed designs and circuits. Investigators utilize the QCADesigner-E tool to create circuits and quantify power loss for diverse crossings. Hence, QCADesigner-E is used to calculate the power loss of the preferred circuit. Figure 10 shows the mean and overall power loss of the suggested circuits.

We used the 4-bit even parity checker and 3-bit even parity generator in QCA from the QCAPro application to examine power loss. These displays each cell’s power loss. The power loss increases with the tone’s depth. For each of the three kinetic energy inputs, we follow these steps. The power loss map findings for 1.5 Ek energies of the proposed 3-bit even parity generator and the proposed 4-bit even parity checker in QCA are displayed in Fig. 11 (a) and (b), respectively.

Conclusions

QCA nanotechnology stands as one of the promising alternatives to replace CMOS technology. In the domain of nano communication circuits, the even parity checker and generator play crucial roles. This study focuses on harnessing the potential of QCA to develop a revolutionary, low-power even parity checker and generator. Leveraging the significantly faster and denser XOR gate, the proposed design offers substantial improvements over previous versions. The suggested architecture boasts reduced cell usage, a smaller footprint, and lower latency compared to existing systems. Moreover, a groundbreaking nano communication block design is introduced in QCA technology, enabling even denser and faster parity generators and checks. Future works in this area involve integrating the proposed design as a foundational element in the development of QCA-centered nano communication transmitters and receivers. This cutting-edge technology has the potential to revolutionize the field of nano-scale communication and enable advanced applications. However, while the presented plan offers numerous advantages, it also exhibits some disadvantages that must be addressed. One significant concern lies in the 67% decrease in cell count for the suggested parity checker compared to the current design. Such a drastic reduction may lead to potential reliability issues or a decrease in fault tolerance. Additionally, the 12.5% decrease in area might impact the overall robustness and manufacturability of the checker. Furthermore, while the suggested XOR gate is faster and denser, its performance might be susceptible to certain noise or error rates, demanding rigorous testing and validation to ensure reliable operation. Also, the QCAPro program was used to assess the power consumption for QCA based on the 4-bit even parity checker and 3-bit even parity generator. The potential challenges related to scaling up the design and addressing any emerging technological limitations should also be carefully examined in future endeavors. By tackling these disadvantages, the proposed QCA-based even parity checker and generator can reach their full potential in nano communication systems.

Data availability

No datasets were generated or analyzed during the current study.

References

Burgin, M., Eberbach, E. & Mikkilineni, R. Cloud computing and cloud automata as A new paradigm for computation. Comput. Reviews J. 4, 113–134 (2019).

Gao, H. & Lei, J. Grouping analysis of QCA for international ecotourism destinations in cloud computing era of Geo-ecology. EAI Endorsed Trans. Energy Web, 10, 1, (2023).

Chen, H., Abnoosian, K. & Salih Mohammed, A. An efficient design of a Three-Layer magnitude comparator for Nano-Scale IoT applications based on QCA technology. J. Nanoelectronics Optoelectron. 19 (5), 459–464 (2024).

Santhiya Devi, R., Balaguru, R. J. B., Amirtharajan, R., & Praveenkumar, P. A novel quantum encryption and authentication framework integrated with IoT. In Security, privacy and trust in the IoT environment (eds Khan, M. K. et al) 123–150 (Springer, 2019). https://doi.org/10.1007/978-3-030-26176-4_6.

Khan, A., Bahar, A. N. & Arya, R. Quad-functioning parity layout for nanocomputing: A QCA design. Nano Commun. Netw. 41, 100525 (2024).

Chang, K. T., Chang, Y. J., Chen, C. L. & Wang, Y. N. Multichannel lens-free CMOS sensors for real‐time monitoring of cell growth, Electrophoresis, vol. 36, no. 3, pp. 413–419, (2015).

Darbandi, M., Seyedi, S. & Al-Khafaji, H. M. R. An efficient new design of nano-scale comparator circuits using quantum-dot technology, Heliyon, vol. 10, no. 18, (2024).

Sheykholeslami-Nasab, P., Davoudi-Darareh, M. & Yousefi, M. H. Modeling and numerical simulation of electrical and optical characteristics of a quantum Dot light-emitting diode based on the hopping mobility model: influence of quantum Dot concentration. Chin. Phys. B. 31 (6), 068504 (2022).

Seyedi, S. & Navimipour, N. J. A fault-tolerant image processor for executing the morphology operations based on a nanoscale technology. Multimedia Tools Appl. 82 (2), 2489–2502 (2023).

Kumar, A. et al. Bioinspired quantum Dots for cancer therapy: A mini-review. Mater. Lett. 313, 131742. https://doi.org/10.1016/j.matlet.2021.131742 (2022).

Nishitani, D. et al. Loop-gap microwave resonator for millimeter-scale diamond quantum sensor. Mater. Today Commun. 31, 103488 (2022).

Pal, J., Goswami, M., Saha, A. K. & Sen, B. Toward the realization of Conservative full adder in QCA with enhanced reliability. J. Circuits Syst. Computers. 30 (10), 2150172 (2021).

Seyedi, S. & Navimipour, N. J. A fault-tolerance nanoscale design for binary-to-gray converter based on QCA. IETE J. Res. 69 (5), 2991–2998 (2023).

Han, M. et al. Cytoplasmic delivery of quantum dots via microelectrophoresis technique, Electrophoresis, vol. 42, no. 11, pp. 1247–1254, (2021).

Seyedi, S. & Navimipour, N. J. A space-efficient universal and multi-operative reversible gate design based on quantum-dots. J. Circuits Syst. Computers. 32 (10), 2350166 (2023).

Graziano, M. et al. Characterisation of a bis-ferrocene molecular QCA wire on a non-ideal gold surface. Micro Nano Lett. 14 (1), 22–27 (2019).

Das, K., De, D. & De, M. Realisation of semiconductor ternary quantum Dot cellular automata. Micro Nano Lett. 8 (5), 258–263 (2013).

Zohaib, M., Navimipour, N. J., Aydemir, M. T. & Ahmadpour, S. S. A nano-scale design of arithmetic and logic unit for energy-efficient signal processing devices based on a quantum-based technology. Cluster Comput. 28 (5), 1–25 (2025).

Hall, M. N., Foerster, K. T., Schmid, S. & Durairajan, R. A survey of reconfigurable optical networks. Opt. Switch. Netw. 41, 100621 (2021).

Gudivada, A. A. & Sudha, G. F. STQCA-FFT: A fast fourier transform architecture using stack-type QCA approach with power and delay reduction. J. Comput. Sci. 60, 101594 (2022).

Khan, A., Safoev, N. & Arya, R. Modeling of Excess-3 to BCD code converter for nano system using quantum‐dot cellular automata technology. Int. J. Numer. Modelling: Electron. Networks. 36 (2), e3055 (2023). Devices and Fields.

Sharma, V. K. Optimal design for digital comparator using QCA nanotechnology with energy Estimation. Int. J. Numer. Modelling: Electron. Networks. 34 (2), e2822 (2021). Devices and Fields.

Ahmadpour, S. S., Navimipour, N. J., Mosleh, M., Bahar, A. N. & Yalcin, S. A nano-scale n-bit ripple carry adder using an optimized XOR gate and quantum-dots technology with diminished cells and power dissipation. Nano Commun. Netw. 36, 100442 (2023).

Tang, L., Kong, T. & Seyedi, S. A new design of an efficient configurable circuit based on quantum-dot technology for digital image processing. Analog Integr. Circuits Signal Process. 122 (3), 36 (2025).

Ahmadpour, S. S., Heidari, A., Navimpour, N. J., Asadi, M. A. & Yalcin, S. An efficient design of multiplier for using in Nano-Scale IoT systems using atomic silicon. IEEE Internet Things J. 10(16), 14908–14909.https://doi.org/10.1109/JIOT.2023.3245344 (2023).

Seyedi, S. & Abdoli, H. A fault tolerant CSA in QCA technology for IoT devices. Sci. Rep. 15 (1), 3396 (2025).

Ahmadpour, S. S., Navimipour, N. J., Bahar, A. N., Mosleh, M. & Yalcin, S. An Energy-Aware Nano-Scale design of reversible atomic silicon based on miller algorithm. IEEE Des. Test 40(5), 62–69. https://doi.org/10.1109/MDAT.2023.3282470 (2023).

Pramanik, A. K., Mahalat, M. H., Pal, J., Ahmadpour, S. S. & Sen, B. Cost-effective synthesis of QCA logic circuit using genetic algorithm. J. Supercomputing. 79 (4), 3850–3877 (2023).

Seyedi, S. & Abdoli, H. Efficient design and implementation of approximate FA, FS, and FA/S circuits for nanocomputing in QCA. PloS One. 19 (9), e0310050 (2024).

D. De and J. C. Das, Design of novel carry save adder using quantum dot-cellular automata. Journal Comput. Science, 22, pp. 54–68, (2017).

Sen, B., Nag, A., De, A. & Sikdar, B. K. Towards the hierarchical design of multilayer QCA logic circuit. J. Comput. Sci. 11, 233–244 (2015).

Das, J. C. et al. QCA based error detection circuit for nano communication network. IEEE Access. 7, 67355–67366 (2019).

Sheikhfaal, S., Angizi, S., Sarmadi, S., Moaiyeri, M. H. & Sayedsalehi, S. Designing efficient QCA logical circuits with power dissipation analysis. Microelectron. J. 46 (6), 462–471 (2015).

Santra, S. & Roy, U. Design and optimization of parity generator and parity checker based on quantum-dot cellular automata. Int. J. Nuclear Quantum Eng. 8 (3), 491–497 (2014).

Hashemi, S., Farazkish, R. & Navi, K. New quantum Dot cellular automata cell arrangements. J. Comput. Theor. Nanosci. 10 (4), 798–809 (2013).

Mustafa, M. & Beigh, M. Design and implementation of quantum cellular automata based novel parity generator and checker circuits with minimum complexity and cell count. J. Comput. Theor. Nanosci. 10(12), 2787–2794. https://doi.org/10.1166/jctn.2013.3319 (2013).

Singh, G., Sarin, R. & Raj, B. A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis. J. Comput. Electron. 15, 455–465 (2016).

Ahmed, S. & Naz, S. F. Notice of violation of IEEE publication principles: design of cost efficient modular digital QCA circuits using optimized XOR gate. IEEE Trans. Circuits Syst. II: Express Briefs 67(3), 568.https://doi.org/10.1109/TCSII.2019.2940951 (2020).

Walus, K., Dysart, T. J., Jullien, G. A. & Budiman, R. A. QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3 (1), 26–31 (2004).

Srivastava, S., Asthana, A., Bhanja, S. & Sarkar, S. QCAPro-an error-power estimation tool for QCA circuit design, in 2011 IEEE international symposium of circuits and systems (ISCAS), : IEEE, pp. 2377–2380. (2011).

Angizi, S., Alkaldy, E., Bagherzadeh, N. & Navi, K. Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10 (2), 259–271 (2014).

Poorhosseini, M. & Hejazi, A. R. A fault-tolerant and efficient XOR structure for modular design of complex QCA circuits. J. Circuits Syst. Computers. 27 (07), 1850115 (2018).

Singh, G., Sarin, R. & Raj, B. A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis. J. Comput. Electron. 15 (2), 455–465 (2016).

Agrawal, P., Sinha, S., Misra, N. K. & Wairya, S. Design of quantum Dot cellular automata based parity generator and checker with minimum clocks and latency. Int. J. Mod. Educ. Comput. Sci. 8 (8), 11 (2016).

Author information

Authors and Affiliations

Contributions

Saeid Seyedi simulated the design, analyzed the results, wrote the main manuscript text, and prepared the figures. Hatam Abdoli developed the idea, supervised the research, analyzed the results, reviewed and proofread the manuscript text.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Seyedi, S., Abdoli, H. Design and assessment of even parity generator and checker circuits for nanoscale communication networks using quantum dots. Sci Rep 15, 26022 (2025). https://doi.org/10.1038/s41598-025-10868-4

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-10868-4