Abstract

This paper proposes a unity-gain active-neutral-point-clamped (ANPC) multilevel inverter topology utilizing two DC sources, ten switches, and four DC-link capacitors. The proposed inverter generates 17 and 25 output voltage levels by leveraging input voltage ratios of V2 = 3V1 (triple) and V2 = 5V1 (quintuple), respectively. Unlike conventional designs, the topology eliminates the need for an H-bridge to produce bipolar voltage waveforms, thereby reducing the number of switches exposed to the maximum output voltage from four (in H-bridge-based structures) to two. Additionally, the inverter supports diverse load types across a wide range of power factors. Comparative analysis demonstrates that the proposed topology achieves the lowest number of conducting switches (only three) to generate any output voltage level, minimizing voltage drop, device losses, and conduction losses while enhancing overall efficiency and output voltage quality. Furthermore, it requires fewer DC sources and switches compared to existing 25-level inverters. Experimental results from a laboratory-scale prototype validate the effective operation of the proposed ANPC inverter in both 17- and 25-level configurations.

Similar content being viewed by others

1. Introduction

The growing demand for high-efficiency, high-quality power conversion in renewable energy systems, electric vehicles, and industrial drives has propelled the advancement of multilevel inverter (MLI) technologies1,2. Multilevel inverters are distinguished by their ability to synthesize staircase voltage waveforms, significantly reducing total harmonic distortion (THD) and electromagnetic interference compared to conventional two-level inverters. Traditional MLI topologies—such as neutral-point clamped (NPC), flying capacitor (FC), and cascaded H-bridge (CHB) designs—have laid the foundation for high-power applications. However, these architectures often suffer from high component counts, complex voltage balancing requirements, and elevated voltage stress on switching devices, which escalate costs, control complexity, and reliability concerns3.

Recent researches have focused on improved MLI configurations to mitigate these challenges by optimizing the trade-off between part count, voltage stress, and output quality. Innovations such as switched-capacitor networks, asymmetric DC source arrangements, and advanced modulation strategies have demonstrated promising results in reducing component numbers and improving efficiency4,5,6. Nevertheless, many existing solutions still face limitations in scalability, device stress, or dependency on numerous isolated DC sources, which constrain their practicality in cost-sensitive applications7. The switched-capacitor based MLIs suffer from impulsive charging/discharging current of capacitors, which may damage the on-path semiconductors and reduce the lifespan of capacitors. The soft-charging cells are usually adopted to overcome this issue8,9. Using DC-link capacitors in MLIs can simultaneously reduce the number of DC sources and increase the number of levels, but in expense of losing voltage boosting ability. An asymmetric MLI with four DC sources, four DC-link capacitors, ten switches, and 14 MOSFETs is presented in10 that provides 35 voltage levels, where two switches are exposed to a voltage stress higher than peak output voltage (Vo, max). Furthermore, another two switches have to withstand a voltage stress equal to Vo, max, which leads to a high total voltage stress. The total summation of input sources is less than the maximum output voltage, which means that the converter operates as a step-down converter. A unity-gain 17-level inverter is presented in11 that is consisted of three DC sources, two DC-link capacitors, nine switches and ten MOSFETs, where the voltage stress of all switches is less than the Vo, max. An asymmetric unity-gain dual source 11-level inverter is presented in12 that is composed of two DC sources, two DC-link capacitors, seven switches, and eight MOSFETs, where only two switches have to block a voltage stress of equal Vo, max. In13, a generalized DC-link capacitors based multilevel inverter topology is proposed, which in its basic form utilizes four switches to create the desired voltage levels. In this structure, two half-bridges have been used for bipolar voltage waveform generation, where none of the switches has to withstand the voltage stress of Vo, max. In14, a 13-level inverter topology is presented, in which three DC-link capacitors and a switched-capacitor have been utilized. The voltage balancing between the three DC-link capacitors is the main challenge of this topology that requires complicated control techniques. In15,16 two similar unity-gain 9-level inverter topologies are presented that differ only at realization of bidirectional switches. Both topologies combine two DC-link capacitors with two switched-capacitors, where only two switches are exposed to a voltage stress of equal to Vo, max. Two 7-level inverter topologies are presented in17,18 that use two DC-link capacitors with two switched-capacitors to provide a voltage boosting factor of 1.5, while none of the semiconductors has to block the voltage stress of Vo, max. Another 7-level inverter topology composed of nine switches, two DC-link capacitors and a switched-capacitor is presented in19 that provides a voltage gain of 1.5. The voltage stress of all switches is less than the Vo, max. The detailed comparative analysis on similar existed 17- and 25-level ANPC topologies (presented in20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35 has been provided in Sect. 4. Another ANPC structure is presented in36 that employs two DC sources, ten switches, four diodes and two switched-capacitors to provide nine output voltage levels with unity gain. In37 a five-level ANPC is presented that utilizes single DC source, nine switches, two diodes, two DC-link capacitors, a single switched-capacitor and an impulsive charging current limitter inductor. While suppressing capacitor’s impulsive charging current, it provides 1.5 boosting factor. A seven-level ANPC is presented in38, which utilizes single DC source, seven switches, six diodes, two DC-link capacitor and two switched-capcitors to provide boosting factor of 1.5. Despite the extensive progress on dual-source and capacitor-based multilevel inverters, most existing topologies still suffer from one or more limitations, including the requirement of a high number of isolated DC sources, reliance on an H-bridge that increases device stress, a large number of conducting switches per level, and the inability to naturally balance capacitor voltages. These challenges increase the overall cost, complexity, and reduce the efficiency of the system, particularly in renewable and hybrid energy applications where compactness and reliability are critical.

To address these issues, this paper proposes a dual-source multi-level inverter architecture that can provide 17- or 25-level output voltages, depending on the magnitude of input DC sources. It requires only three conducting switches per voltage level, and ensures natural capacitor voltage balancing. The significance of generating up to 25 levels lies in achieving superior waveform quality, lower THD, reduced EMI, and higher efficiency, which are critical for demanding high-performance power conversion applications. The operation of the proposed inverter relies on asymmetric input voltage ratios: V2 = 3V1 for 17-level and V2 = 5V1 for 25-level operation. These ratios are essential because they ensure that all voltage steps are unique and equally spaced. If the input voltages deviate from the designed ratios, the inverter will still function, but some output levels may merge or become unevenly spaced, leading to fewer distinct voltage levels and slightly degraded harmonic performance.The proposed inverter has H-bridge free structure, where only two (instead of four) switches have to tolerate a voltage stress of Vo, max. This reduction in voltage stress not only enhances efficiency and thermal performance but also permits the use of lower-rated, cost-effective semiconductor devices. Furthermore, another key advantage is that only three switches is required to be on to generate any desired voltage level, which leads to lower voltage drop on devices and higher achievable output voltage on the load. The combination of H-bridge elimination, reduced conduction path, dual-level scalability without additional devices, and verified high efficiency distinguishes the proposed topology from previously reported dual-source inverters. The proposed design can flexibly generate both 17 and 25 output levels with unity gain using the same hardware, achieving high efficiency with fewer components compared to conventional approaches. 17 level version may be chosen when a small filter is acceptable and overall bill-of-materials/efficiency are prioritized. Also, when filter minimization and power-quality/EMI margins dominate, 25 level version is chosen. Since the proposed desin supports both 17 and 25 levels without adding parts, the level selection can be made at deployment to minimize total cost (inverter + filter) for the same THD and rated power.

The remainder of this paper is organized as follows: Sect. 2 details the configuration and operational principles of the proposed dual-source inverter. Section 3 presents the Nearest Level modulation strategy. Section 4 provides the results of comparative analysis. Section 5 validates the topology through experimental results, including efficiency analysis and THD performance. Finally, Sect. 6 concludes the study.

2. Proposed multilevel inverter

2.1 Configuration

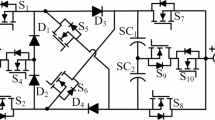

Figure 1 shows the proposed double-input active neutral-point clamped multilevel inverter, which utilizes two DC supplies, ten power switches (6 unidirectional and 4 bidirectional) and four DC-link capacitors, as (1).

Based on the magnitude of DC sources, the proposed inverter can generate 17 or 25 voltage levels. For ternary-ordered magnitude of DC sources (V2 = 3V1), the proposed inverter can provide 17 voltage levels, while for quinary-ordered inputs (V2 = 5V1) it can produce 25 voltage levels. The proposed inverter does not require any diode, which enables it to supply variety of load types from zero to unity power factors. Regardless of the number of generated levels, there exists only three conducting semiconductors on current flow path.

2.2 Operational modes and switching schemes

2.2.1 17-Level version

In order to generate 17 voltage levels at the output, the magnitude of DC sources should be selected as (2).

Since two DC-link capacitors are paralleled with each input, the voltage of each capacitor is naturally balanced to half of the input voltage, as shown in (3).

Table 1 shows the switching scheme of proposed 17-level inverter, where “1” and “0” denotes the “on” and “off” states, respectively.

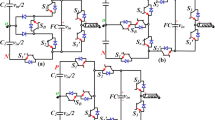

For clear understanding, the equivalent circuits of proposed 17-level inverter at different operational states has been shown in Fig. 2. As seen from Table 1; Fig. 2, the proposed inverter successfully generates 8 positive, 8 negative and a zero voltage-level (0, ±Vdc, ±2Vdc, ±3Vdc, ±4Vdc, ±5Vdc, ±6Vdc, ±7Vdc, ±8Vdc,), with maximum output voltage of 8Vdc, while V2 = 3V1 = 6Vdc. Also, it is observed that at each state, there exists a path for both the positive and negative load current, which enables the proposed converter to feed the variety of loads from zero to unity power factor.

Table 2 shows the voltage stress (in per-unit) of switches in proposed 17-level inverter. As seen, only two switches (T2, T3) have to tolerate the voltage stress of equal to maximum output voltage (Vo, max), while the voltage stress of other switches is much lower than the Vo, max. The total voltage stress of proposed 17-level inverter is 48Vdc (6 per-unit).

2.2.1 25-Level version

The number of voltage levels in proposed inverter can be enhanced to 25 voltage-levels, without any additional part, only by choosing the magnitude of input DC sources as (4).

Accordingly, the voltage of C1-C4 capacitors is naturally regulated as (5).

Table 3 shows the switching pattern of proposed inverter at its 25-level version. The equivalent circuits have also been presented in Fig. 3. As seen, the proposed inverter can produce 25 voltage levels, including 12 positive, 12 negative and one zero level, with peak value of Vo, max=12Vdc, where V2 = 5V1 = 10Vdc. Table 4 shows the voltage stress of switches at proposed 25-level inverter.

At 25-level version, similar to 17-level version, only two switches (T2, T3) have to withstand the voltage stress of equal to peak output voltage. The total voltage stress on switches is equal to 74Vdc (6.167 per-unit).

3. Nearest-level modulation method

In this study, the Nearest-Level Method (NLM) has been used for generating switching pulses of switches. The NLM has been chosen because it offers the best balance of simplicity, low switching loss, and excellent THD performance for a high-level inverter. In contrast, other techniques like Selective Harmonic Elimination (SHE) and SPWM are more suited for low-level converters where harmonic elimination or carrier-based shaping is critical. For theproposed 17/25-level inverter, NLM achieves near-optimal output quality with minimal control complexity and maximum efficiency. The NLM technique operates by selecting the nearest available voltage level to the reference waveform at each sampling instant. In this technique, a sinusoidal reference waveform (vRef) is generated with the desired amplitude (VRef) and frequency (fRef=50 Hz), as shown in (6).

The valid range for VRef is [0−(Ma×Vo, max)], where the modulation index (Ma) is defined as (7).

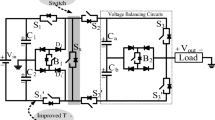

At each sampling instant, the reference value is compared with the available voltage levels, and the nearest level is selected, which is translated into appropriate switching signals for the inverter’s switching devices. The simplicity of NLM lies in its straightforward level selection process, which eliminates the need for complex calculations or carrier-based modulation schemes. Furthermore, the NLM technique demonstrates lower switching losses compared to PWM based modulation techniques. Figure 4 depicts the implemented of NLM on the proposed 17-level ANPC inverter through logic circuits. The logic circuit shown in Fig. 4 can be further extended to accommodate the 25-level configuration.

4. Comparative analysis

In this section, comparative analysis is performed between the proposed 17/25-level inverter and its similar counterparts presented in20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35, from viewpoints of number of levels (NL), DC sources (NDC), switches (NS), MOSFETs (NM), capacitors (NC), diodes (ND), gain, maximum number of conducting semiconductors (NCS), total voltage stress (TVS), maximum voltage stress (MVS), number of semiconductors tolerating maximum output voltage (NSMOV), cost factor (CF), and the capability of feeding the inductive loads (ILFC).

Table 5 summarizes the comparison results. The mathematical definition of TVSpu, MVSpu and gain have been shown in (8).

Also, in literature, different definitions have been proposed for the Cost Function (CF). In this study, the commonly used definition, shown in (9) has been employed, which is the most comprehensive definition, containing as much as possible effective parameters.

Figures 5 and 6 serve as graphical evidence of the comparative analysis. While Table 5 provides numerical values, Figs. 5 and 6 make the contribution of the work more transparent and accessible.

4.1 17-Level topologies

According to Table 5; Fig. 5(a), the proposed 17-level topology and28 require only 2 DC sources, while all other converters utilize 4 DC sources. The reduced count of sources dramatically reduces the total size, mass and cost of converter. The number of switches employed in the proposed topology is 10, which is equal to or fewer than that of20,23,24,26. None of the converters use the diodes. The proposed topology and26,28 use 4 capacitor, while the other converters are capacitor-free structures. The proposed converter and all the considered 17-level converters provide unity voltage gain, where the maximum output voltage is equal to the summation of input voltage sources. As seen from Fig. 5(b), the proposed converter and21,22,25,28 employ minimum number of switches (only 3 switches) to generate each voltage level, which may lead to lower voltage drop and losses. According to Fig. 5(c), the TVS in proposed converter is higher than the others. Also, the two switches in proposed topology and20,21,22,23,25 have to withstand a voltage stress of Vo,max. The maximum voltage stress on semiconductors of24,26,27,28 is less than the Vo,max. In this study, the cost analysis has been repeated for two different weighting factors of TVS, α = 0.5 and α = 1.5. According to Fig. 5(d), for both α = 0.5 and α = 1.5, the proposed topology provides the second least CF value. All the considered converters are able to successfully feed the inductive loads with variety of power factors. The proposed topology is superior to20 in terms of reduced DC source requirement, fewer conduction switches, H-bridge elimination, and scalability to 25 levels, making it more efficient, cost-effective, and versatile for practical high-performance power conversion.

4.1 25-Level topologies

According to Fig. 6(a), the proposed topology and29,30 utilize only 2 DC sources to provide 25 voltage levels at the output, which is fewer than the other structures. Furthermore, the proposed topology requires only 10 switches, which is equal to or fewer than that of other topologies. The number of MOSFETs in proposed topology is 14, which is fewer than that of33,35. Based on Fig. 6(b), the proposed topology and29,30 require 4 capacitors to generate 25 voltage levels, while this amount for33 is 8. The other converters are capacitor-free structures. The topologies presented in29 and30 respectively use 8 and 16 diodes, while the proposed topology and the other ones are diode-free structures. Among considered structures, the converter presented in35 operates as a step-down converter (the maximum output voltage is less than the summation of all input sources), while the proposed topology and the other structures provide unity-gain. During generation of any voltage level in proposed topology, only 3 semiconductors are in conducting state, which is equal to or fewer than that of other structures.

According to Fig. 6(c), the two switches in proposed topology have to tolerate a voltage stress of Vo,max. The topology presented in35 has the highest total voltage stress (in per-unit). The second highest TVS belongs to the proposed topology, which is considered as its main drawback. According to Fig. 6(d), the proposed topology provides the least CF for both weighting factors of α = 0.5 and α = 1.5. Here again, all the considered topologies are capable of feeding inductive loads with variety of power factors. The28 is limited to 17 levels only, while the proposed design can flexibly operate at both 17- and 25-level configurations using the same hardware, simply by changing the input DC voltage ratio. This scalability is not possible in28. Furthermore, the proposed 25-level inverter achieves a significantly higher ratio of number of levels to the number of DC sources, switches, MOSFETs and capacitors, meaning it generates more levels per device. This indicates a more efficient utilization of components and highlights the practicality of the proposed design for high-quality power conversion with reduced part count. Although30 has a slightly lower TVS, the proposed topology eliminates 16 diodes, reduces total device count by almost 50%, requires fewer conduction devices per level, and achieves the lowest CF values. Moreover, the proposed design has been experimentally validated, confirming its practical feasibility and efficiency advantages.

5. Experimental and simulation validations

The laboratory-scaled prototype of proposed topology has been implemented with output power of 270W (shown in Fig. 7).

Table 6 summarizes the parameter values employed during experimental validations.

Figure 8(a)–(b) present the output voltage and load current waveforms of proposed topology, respectively at 17- and 25-level versions. At 17-level version (shown in Fig. 8(a)), where V1 = 45V and V2 = 135V, the proposed topology has successfully produced 17 voltage levels including 0, ± 22.5V, ± 45V, ± 67.5V, ∙∙∙, ± 157.5V, ± 180V. The peak output voltage is about 180V (with small voltage drop on devices), which provides a unity voltage gain. Considering ZL=48.8 + j0.077ɷ (where ɷ = 2πf) as the load, a sinusoidal current with the magnitude of about 3.3A passes through the load. Due to the resistive-inductive nature of the load, there exists a phase difference of about Δφ = 26° between the load current and voltage waveforms. Also, at 25-level version (shown in Fig. 8(b)), where V1 = 30V and V2 = 150V, the proposed topology can effectively generate 25 voltage steps including 0, ± 15V, ± 30V, ± 45V, ∙∙∙, ± 165V, ± 180V. The maximum output voltage is about 180V. Since a load of ZL = 49.3 + j0.077 ɷ is supplied by the proposed inverter, a sinusoidal current with the peak value of 3.2A flows through the load. Here again, a phase difference of about Δφ = 26° is seen between the load voltage and current waveforms.

Figure 9 (a)–(b) show the dynamic performance of proposed inverter during sudden load step change conditions at both 17- and 25-level versions.

As seen, at both 17- and 25-level scenarios, the proposed inverter can effectively produce desired output voltage waveform during full-load and no-load conditions. During full-load condition, the output voltage magnitude experiences a very small reduction compared to the no-load condition, which is due to the voltage drop on the conducting devices. Figures 10 and 11 show the voltage and current waveforms of C1-C4 capacitors respectively at 17- and 25-level versions.

As seen from Fig. 10, at 17-level version, the voltage on C1-C4 is regulated respectively on 22.5V, 22.5V, 67.5V, and 67.5V. According to Fig. 11, at 25-level version, the voltage on C1-C4 capacitors is regulated respectively on 15V, 15V, 75V, and 75V. As seen, the proper sizing of capacitors has restricted their voltage ripple. Unlike switched-capacitor inverters, the proposed topology uses DC-link capacitors that are continuously connected to their input sources and naturally balanced to half of the source voltage. Therefore, aside from the short startup transient, no significant inrush current occurs during operation. This structural difference explains why the capacitor current waveforms in Figs. 10 and 11 are nearly equal to the load current rather than several times higher.

The voltage waveforms of switches at 17-level version have been shown in Fig. 12. According to experimental results, the peak voltage stress among semiconductors is about 180V (Vo, max), which belongs to T2 and T3 switches (verified by Table II). The voltage stress of other switches is much less than the peak output voltage.

Figure 13 shows the efficiency of proposed topology. As seen, the efficiency of 17-level and 25-levelversions of the proposed inverter are respectively about 97.7% and 97.6%, which have been obtained at the output powers of 270 W and 268 W, respectively. As shown in Fig. 13, the efficiency of the 25-level version is slightly lower (~ 97.6%) compared to the 17-level version (~ 97.7%). This small difference can be explained as follows:

-

Increased Switching Events: In the 25-level mode, more output voltage steps are generated within one fundamental cycle. Although the nearest-level modulation (NLM) minimizes switching frequency, the total number of commutations per cycle is higher in the 25-level case compared to the 17-level case. This leads to slightly higher switching and conduction losses.

-

Higher Total Voltage Stress (TVS): The 25-level configuration has a higher total standing voltage (6.167 p.u. vs. 6.0 p.u. for the 17-level). This results in slightly higher device stress and marginally increased losses across semiconductors.

-

Capacitor Current Ripple: In the 25-level mode, the DC-link capacitors handle smaller voltage steps but more frequent charging/discharging cycles, which contributes to additional (though small) ESR-related power loss.

The reduction in efficiency in 25-level version is very minor (only ≈ 0.1%), and both versions achieve quite high efficiency (> 97.5%), which confirms that the proposed topology maintains proper performance in both 17-level and 25-level versions, with the small difference being inherent to the higher-level operation.

The total power loss on semiconductors of 17 and 25-level versions are respectively about 6.24 W and 6.48 W. Also, the total power loss on ESR of capacitors of 17 and 25-level versions are respectively about 0.068 W and 0.073 W. Thus, according to Fig. 14, the 99% of total power losses of the proposed inverter belongs to the semiconductors at both 17 and 25-level versions.

Figure 15 displays the power loss of semiconductors in proposed inverter. Furthermore, Fig. 16 shows the power loss distribution between the semiconductors at both 17 and 25-level versions of the proposed inverter.

As seen from Figs. 15 and 16, the highest power loss occurs on switch K1, which is 17% and 19% of total switch losses, respectively at 17 and 25-level versions. Owing to usage of nearest level as the modulation technique, the semiconductors operate at quite low frequencies, which accordingly leads to quite small switching and rather high conduction losses. The total power losses on semiconductors (switching + conduction) in 17- and 25-level versions are about 6.24W and 6.48W respectively.

Figure 17 illustrates the share of each capacitor on total capacitor losses. At both 17 and 25-level versions, the share of capacitors on first DC-link (C1 and C2) is higher than that of those on second DC-link (C3 and C4). As seen, the percentage share of losses in capacitors C1 and C2 is higher in the 25-level case due to their more frequent charge/discharge cycles. However, it should be emphasized that the absolute value of total capacitor losses remains very small in both cases compared to semiconductor losses.

Additional simulations of the proposed 17- and 25-level inverter using PSCAD/EMTDC has been performed and the results have been shown Fig. 18 shows. The study considered step changes in the resistive part of the load while monitoring the output voltage, load current, and capacitor voltages to validate the natural voltage balancing mechanism. At both 17- and 25-level versions, from t = 0 s to t = 0.2 s, the inverter operates with the base load Z1 (R1 = 48.8Ω, L1 = 77mH), producing the expected 17-level or 25-level output voltage waveform along with balanced capacitor voltages. At t = 0.2 s, the resistive load is suddenly reduced from 48.8Ω to 12.2Ω (75% reduction, equal to 0.25R1), resulting in a sharp increase in load current. At t = 0.3 s, the resistance is increased from 12.2Ω to 73.2Ω (600% increase, equal to 1.5R1). At t = 0.4 s, the resistance is decreased to 36.6Ω (50% reduction, equal to 0.75R1). Finally, at t = 0.5 s, the resistance is increased to 61Ω (166% increase, equal to 1.25R1). At both versions, throughout all aforementioned transitions, the proposed inverter consistently maintains the output voltage waveform with nearly constant peak amplitude, aside from negligible variations caused by parasitic elements. Importantly, the DC-link capacitors automatically balance at their intended voltages: capacitors C1 and C2 stabilize at half of the first input source, and capacitors C3 and C4 stabilize at half of the second input source. These results confirm that the proposed topology in its both 17-level and 25-level versions is capable of withstanding significant load fluctuations while preserving both the desired multilevel output waveform and the natural voltage balance of the DC-link capacitors.

6. Conclusions

In this paper, a double-input active neutral point clamped inverter topology has been proposed that is capable of producing unity voltage gain with 17 and/or 25 voltage levels at the output port, based on the magnitude of input DC voltage sources. The proposed inverter requires 4 DC-link capacitors and 10 switches, 4 of which are bidirectional ones. Since the proposed inverter doesn’t require an H-bridge to generate the bipolar voltage waveform, only two switches (instead of four) is exposed to a voltage stress of equal to maximum output voltage. The proposed inverter is capable of feeding any load type with variety of power factors. Compared to similar 17/25-level inverters, the proposed topology requires fewer number of DC sources, which leads to fewer size and cost. Also, it provides lower CF values than its similar counterparts. The results of experimental analysis confirm the correct operation of the proposed inverter.

Data availability

The datasets used and/or analyzed during the current study available from the corresponding author on reasonable request.

References

Hosseinpour, M., Derakhshandeh, M., Seifi, A. & Shahparasti, M. A 17-level quadruple boost switched-capacitor inverter with reduced devices and limited charge current. Sci. Rep. 14 (1), 6233 (2024).

Seifi, A., Hosseini, S. H., Tarafdar Hagh, M. & Hosseinpour, M. Capacitor based topology of cross-square-switched T-type multi-level inverter. Sci. Rep. 14 (1), 3166 (2024).

Wang, D. et al. Multilevel inverters for electric aircraft applications: current status and future trends. IEEE Trans. Transp. Electrification. 10 (2), 3258–3282 (2023).

Barzegarkhoo, R., Forouzesh, M., Lee, S. S., Blaabjerg, F. & Siwakoti, Y. Switched-capacitor multilevel inverters: a comprehensive review. IEEE Trans. Power Electronics, (2022).

Vijeh, M., Rezanejad, M., Samadaei, E. & Bertilsson, K. A general review of multilevel inverters based on main submodules: structural point of view. IEEE Trans. Power Electron. 34 (10), 9479–9502 (2019).

Kumari, M. et al. Recent trends and review on switched-capacitor‐based single‐stage boost multilevel inverter. Int. Trans. Electr. Energy Syst. 31 (3), e12730 (2021).

Karimi, M., Kargar, P. & Varesi, K. An extendable asymmetric boost multi-level inverter with self‐balanced capacitors. Int. J. Circuit Theory Appl. 50 (4), 1297–1316 (2022).

Ghelichi, A., Varesi, K. & Khoubrooy Eslamloo, M. Reliability assessment of an improved Single-Input Switched‐Capacitor boost 7/9‐Level inverter suitable for renewable energies. Eng. Rep. 7 (1), e13098 (2025).

Deliri, S., Varesi, K. & Padmanaban, S. An extendable single-input reduced‐switch 11‐level switched‐capacitor inverter with quintuple boosting factor. IET Generation Transmission Distribution. 17 (3), 621–631 (2023).

Esmaeili, F. & Varesi, K. An asymmetric multi-level inverter structure with increased steps per devices, in 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), : IEEE, pp. 1–5. (2020).

Asl, R. I. & Varesi, K. 17-Level Asymmetric DC-Link Capacitor Based Inverter, in 9th International Conference on Technology and Energy Management (ICTEM), 2024: IEEE, pp. 1–5. (2024).

Asl, R. I., Varesi, K., Akbari, M. & Prabhakar, M. An Asymmetric Double-Source DC-Link Capacitors Based 11-Level Inverter with Reduced Components, in 2025 16th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), : IEEE, pp. 1–4. (2025).

Majumdar, S., Mahato, B. & Jana, K. C. Implementation of an optimum reduced components multicell multilevel inverter (MC-MLI) for lower standing voltage. IEEE Trans. Industr. Electron. 67 (4), 2765–2775 (2019).

Almakhles, D. J., Ali, J. S. M., Selvam, S., Bhaskar, M. S. & Sandeep, N. Switched capacitor-based 13L inverter topology for high-frequency AC power distribution system. IEEE J. Emerg. Sel. Top. Power Electron. 9 (5), 5883–5894 (2020).

Sathik, M. J., Almakhles, D. J., Sandeep, N. & Siddique, M. D. Experimental validation of new self-voltage balanced 9L-ANPC inverter for photovoltaic applications. Sci. Rep. 11 (1), 5067 (2021).

Siddique, M. D., Iqbal, A., Sathik Mohamed Ali, J., Mekhilef, S. & Almakhles, D. J. Design and implementation of a new unity gain nine-level active neutral point clamped multilevel inverter topology. IET Power Electron. 13 (14), 3204–3208 (2020).

Lee, S. S., Bak, Y., Kim, S. M., Joseph, A. & Lee, K. B. New family of boost switched-capacitor seven-level inverters (BSC7LI). IEEE Trans. Power Electron. 34 (11), 10471–10479 (2019).

Jagabar Sathik, M. et al. Seven-level boosting active neutral point clamped inverter using cross‐connected switched capacitor cells. IET Power Electron. 13 (9), 1919–1924 (2020).

Lee, S. S., Lim, C. S., Siwakoti, Y. P. & Lee, K. B. Hybrid 7-level boost active-neutral-point-clamped (H-7L-BANPC) inverter. IEEE Trans. Circuits Syst. II Express Briefs. 67 (10), 2044–2048 (2019).

Ali, J. S. M. et al. A new generalized multilevel converter topology based on cascaded connection of basic units. IEEE J. Emerg. Sel. Top. Power Electron. 7 (4), 2498–2512 (2018).

Samadaei, E., Sheikholeslami, A., Gholamian, S. A. & Adabi, J. A square T-type (ST-type) module for asymmetrical multilevel inverters. IEEE Trans. Power Electron. 33 (2), 987–996 (2017).

Alishah, R. S., Hosseini, S. H., Babaei, E. & Sabahi, M. A new single-phase multilevel converter topology with reduced power electronic devices, voltage rating on switches, and power losses. Int. J. Circuit Theory Appl. 46 (7), 1372–1391 (2018).

Alishah, R. S. et al. A new Switched-Ladder multilevel converter structure with reduced power electronic components. J. Circuits Syst. Computers. 30 (12), 2150217. https://doi.org/10.1142/s0218126621502170 (2021).

Siddique, M. D., Mekhilef, S., Shah, N. M., Sarwar, A. & Memon, M. A. A new single-phase cascaded multilevel inverter topology with reduced number of switches and voltage stress. Int. Trans. Electr. Energy Syst. 30 (2), e12191 (2020).

Meraj, S. T., Hasan, K. & Masaoud, A. A novel configuration of cross-switched T-type (CT-type) multilevel inverter. IEEE Trans. Power Electron. 35 (4), 3688–3696 (2019).

Dhanamjayulu, C. et al. Design and implementation of seventeen level inverter with reduced components. IEEE Access. 9, 16746–16760 (2021).

Kakar, S. et al. New asymmetrical modular multilevel inverter topology with reduced number of switches. IEEe Access. 9, 27627–27637 (2021).

Arif, M. S. B. et al. Asymmetrical 17-level inverter topology with reduced total standing voltage and device count. IEEE Access. 9, 69710–69723 (2021).

Saeedian, M., Adabi, J. & Hosseini, S. M. Cascaded multilevel inverter based on symmetric–asymmetric DC sources with reduced number of components. IET Power Electron. 10 (12), 1468–1478 (2017).

Taheri, A., Rasulkhani, A. & Ren, H. P. An asymmetric switched capacitor multilevel inverter with component reduction. IEEE Access. 7, 127166–127176 (2019).

Siddique, M. D. et al. A new multilevel inverter topology with reduce switch count. IEEE Access. 7, 58584–58594 (2019).

Prem, P. et al. A novel cross-connected multilevel inverter topology for higher number of voltage levels with reduced switch count. Int. Trans. Electr. Energy Syst. 30 (6), e12381 (2020).

Samadaei, E., Gholamian, S. A., Sheikholeslami, A. & Adabi, J. An envelope type (E-Type) module: asymmetric multilevel inverters with reduced components. IEEE Trans. Industr. Electron. 63 (11), 7148–7156 (2016).

Chittathuru, D., Padmanaban, S. & Prasad, R. Design and implementation of asymmetric cascaded multilevel inverter with optimal components. Electr. Power Compon. Syst. 49, 4–5 (2021).

Shalchi Alishah, R. et al. A new generalized cascade multilevel converter topology and its improved modulation technique. Int. J. Circuit Theory Appl. 49 (4), 1103–1120 (2021).

Alaas, Z. A new active neutral point clamped (ANPC) nine-level inverter topology with low energy storage switched capacitors. Sci. Rep. 15 (1), 7031 (2025).

Surapu, P. R., Sandeep, N. & Verma, A. K. Five-level Anpc inverter with full dc-bus utilization. IEEE Trans. Power Electron. 39 (1), 83–87 (2023).

Saif, B. et al. A single-phase seven-level ANPC inverter with hybrid modulation for enhanced efficiency and harmonic performance, Scientific reports, vol. 15, no. 1, p. 9551, (2025).

Funding

The authors received no funding for this work.

Author information

Authors and Affiliations

Contributions

Conceptualization, M. A. and K. V.; methodology, M. A. and K. V.; software, M. A. and K. V.; validation, M. A., K. V. and M. K.; investigation, M. A., K. V., M. K. and M. A. J. S.; resources, M. A., K. V., and M. K.; data curation, M. A., K. V., and M. K.; writing—original draft preparation, M. A., K. V., and M. K.; supervision, K. V. and M. A. J. S.; Funding acquisition: K. V.; Visualization: K. V.; writing—review and editing: M. A., K. V., and M. A. J. S.; project administration, K. V.; Formal analysis: M. A., and K. V., All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Varesi, K., Akhgari, M., Karimi, M. et al. Dual-source 17/25-Level ANPC inverter with low stress on devices and reduced part count suitable for hybrid energy systems. Sci Rep 15, 35661 (2025). https://doi.org/10.1038/s41598-025-19530-5

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-19530-5