Abstract

This paper introduces a quadratic-based DC-DC converter with high voltage gain, specifically optimized for DC microgrid applications. The proposed topology offers several key merits, including enhanced voltage gain, reduced voltage stress on switching components, continuous input current, a common ground between the input and output, high efficiency, and synchronized switch operation. A detailed analysis is provided on its operational principles, steady-state characteristics, design considerations, and efficiency evaluation, along with dynamic modeling and control assessment. To emphasize its benefits, the proposed converter is compared with existing topologies. The effectiveness of the design is validated through experimental testing on a 200W prototype, operating with an input voltage of 20V and delivering an output voltage of 200V.

Similar content being viewed by others

Introduction

With the increasing integration of distributed generation sources, DC microgrid technology continues to advance. Since DC power generators typically produce low output voltages, high efficiency and high-gain DC-DC converters are essential to meet the voltage requirements of DC loads [1]. In addition to their crucial role in renewable energy systems, these high-gain converters are widely employed in various applications, including battery backup solutions for uninterruptible power supplies, high-intensity discharge lamp ballasts for automotive headlamps, electric traction systems, and certain medical devices [2].

Traditionally, conventional DC-DC boost converters have been utilized for voltage step-up applications. However, one major drawback is that the voltage stress on the switching device is equivalent to the output voltage. As a result, high-voltage-rated switches must be chosen, leading to increased conduction losses. Furthermore, achieving a high voltage gain requires operating at large duty cycles, which not only amplifies conduction losses and voltage spikes but also intensifies the diode reverse recovery issue, potentially affecting overall system performance [3].

Various advanced DC-DC circuit topologies have been developed to achieve high voltage gain by converting low-voltage sources into elevated DC output voltages. These designs incorporate multiple voltage-boosting techniques, such as switched inductor and switched capacitor (SC) methods, cascading structures, interleaved configurations, voltage multiplier cells, and hybrid approaches that integrate these methods [4,5,6,7,8,9,10,11]. While these strategies effectively enhance voltage gain, many suffer from inherent drawbacks, including the use of multiple components and hard-switching operations, which compromise their efficiency and suitability for high-gain applications.

To overcome these challenges, multi-stage or multi-level strategies have been introduced, generally categorized into three main sections: cascading, interleaving, and multilevel configurations. Despite their potential to improve voltage gain, these converters often encounter issues such as complex control requirements, an increased number of components, and higher system costs. Interleaved structures, as proposed in [12] and [13], have gained attention for photovoltaic applications due to their capability to reduce input current ripple, making them particularly beneficial in such scenarios. However, their practical implementation is prevented, by the intricacy of the control mechanism and elevated costs.

Among various voltage-boosting techniques, the SC approach, which operates on the charge pump principle, is a commonly employed method for achieving high voltage gain, as demonstrated in [14,15,16]. Nevertheless, SC-based topologies present a significant limitation: they generate high peak currents through capacitors, which can result in substantial power losses and increased electromagnetic interference. Despite this drawback, the voltage multiplier technique has emerged as a more cost-effective and efficient solution. Comprising diodes and capacitors, voltage multiplier circuits enable significant voltage gain while maintaining a relatively simple structure [17,18,19]. However, although studies in [20] and [21] highlight the capability of voltage multipliers to achieve high voltage levels, their dependence on a large number of components escalates both cost and system size. Furthermore, a major limitation of voltage multiplier circuits is the excessive voltage stress imposed on the circuit components.

Another widely implemented method for increasing input voltage and achieving high voltage gain in DC-DC converters is the voltage lift technique [22,23,24]. This approach relies on charging a capacitor to a predefined voltage level before utilizing the stored charge to elevate the output voltage. By continuously applying this principle and incorporating additional capacitors, higher voltage levels can be attained through extended configurations such as re-lift, triple-lift, and quadruple-lift techniques.

The switched inductor technique operates using two distinct configurations: the passive switched-inductor unit (PSL) and the active switched-inductor unit (ASL). In ASL-based designs, the circuit comprises active switches and inductors, whereas PSL units utilize diodes in combination with inductors [25, 26]. The ASL approach significantly enhances the voltage boost capability by first charging the inductors in parallel through two power switches. When the switches are turned off, the stored energy is then released in series, effectively increasing the output voltage, as outlined in [27, 28].

Motivated by the advantages and limitations of existing high step-up converters, this paper introduces an innovative DC-DC topology tailored for DC microgrid applications. The proposed design offers several key benefits, enhancing performance and efficiency in high step-up voltage conversion. Main contributions and features of this paper are classified as follows:

-

The proposed topology, enables high voltage gain without being limited by the duty cycle, allowing it to operate across the full range from 0 to 1

-

Imposing low voltage stress on the switches, allowing the use of low-voltage-rated switches with minimal on-resistance. This reduction in resistance decreases conduction losses and improves overall efficiency.

-

Providing a continuous input current with minimal ripple

-

Utilizing two power switches operating in synchronization.

-

The input and output sides share a common ground.

The rest sections of this work are titled as follows:

Section "Proposed Step up DC-DC Converter" includes theoretical study to reach converter’s boosting gain, dynamic study and compassion study. In Sect. 3 experimental results are studied in detail. Section 4 includes work conclusion.

Proposed step up DC-DC converter

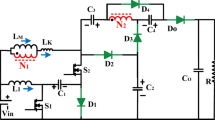

Figure 1 illustrates the basic structure of the proposed boost converter. The proposed converter includes: two switches (S1, S2), three inductors (L1, L2, L3), three diodes (D1, D2, D3) and capacitors (C1, C2, C3, Co). This converter operates in two modes, continues and discontinues conduction mode (CCM, DCM). Some assumption is considered to have a comprehensive study, as follows:

-

Equivalent series resistance (ESR) of all semiconductors are ignored.

-

Voltage of all capacitors is considered in the constant value (due to its large magnitude)

-

The transient intervals are not considered in the operational modes, because of its shorter time than switching period of time.

Both of CCM and DCM operation modes are described in the following sections.

Analysis of CCM mode

CCM operation mode of the proposed converter consists of two-time intervals. S1 and S2 are turned on in the same time, or S1 and S2 are turned off in the same time. The idealized waveform of the proposed non-isolated boost converter is depicted in the Fig. 2.

First operation mode

In this time interval, S1 and S2 are turned on. This time interval endures (1-D) T. D1 and D3 are off and D2 is on. The blocking voltage of D1and D3 are, VC1 andVC3-Vo, respectively. Inductors L1, L2 and L3 are in the charging position. Figure 3 shows the converter’s condition in this time interval. Inductors voltages are obtained via Eqs. (1–4):

Second operation mode

Figure 4 illustrates the proposed boost converter’s elements condition in the second time interval. In this mode, S1 is in on state and S2 is in off state. D1 and D2 are blocked via voltage VC1 and VC2-VO, respectively. Diode D3 is in forward bias. Inductors L1, L2 and L3 are in charge, charge and discharge position, respectively. Equations (4–6) gives voltage of the inductors:

Volt–second law

Average voltage of inductors in the period of time is equal to zero [29]. By employing volt-second law, capacitors voltage is obtained as follows:

By using capacitor voltages, the voltage gain has been calculated as follows:

The blocking voltage of diodes and switches could be calculated as follows:

Analyze of DCM mode

DCM Condition.

The first two DCM operating modes exhibit similar behavior; therefore, this section focuses exclusively on Mode II of DCM. In this mode, all switches and diodes are turned off, and the corresponding relationship derived using Kirchhoff’s Voltage Law (KVL) is as follows:

Utilizing the volt-second balance principle on the input inductors, accompanied by several derivations, enables the determination of the voltages across capacitors C1, C2, C3, as well as the output voltage.

Additionally, through the application of the charge balance principle to the capacitors, followed by a sequence of derivations, it becomes possible to calculate the current flowing through the inductors.

Assuming IL1 = IL1(peak) /2, then IL1(peak) can be obtained, as follows:

Furthermore, the following equation can be formulated for the inductor, as below:

Time duration of the mode III can be calculated as:

where, τ is a dimensionless variable, and it is defined, as follows:

Boundary conduction mode (BCM)

A. Boundary condition

To ensure CCM operation in the proposed circuit, the minimum current through the L1 must remain above zero. The minimum current of the L1 and \(\Delta I_{L1}\) can be determined as:

The minimum required values of the L1 to maintain CCM, as illustrated in Fig. 5, are as given.

Current calculation

Mode I: During this time interval, Kirchhoff’s Current Law (KCL) govern the relationships in the circuit.

Mode II: Using KCL, the corresponding equations for this mode can be derived as:

Current stress of the components

The currents through the semiconductor components during the first and second switching subintervals can be expressed as follows:

Additionally, the currents flowing through the capacitors during the first and second switching subintervals can be expressed as:

Assuming ripple-free currents for inductors during CCM operation, the average currents can be calculated as shown below:

Additionally, the average currents for the converter’s switches and diodes can be approximated as follows:

Calculating the root-mean-square (RMS) currents is essential for assessing the overall power efficiency of the power converter. Hence, the RMS currents for each component are determined as:

Design and efficiency

Design approach

The high-performance design is resulted by considering all of voltage and current constraints [30,31,32]. To this aim, inductance and capacitor values are calculated by considering current and voltage ripple equations as follows:

Calculating efficiency of the proposed converter

The real form of proposed converter with considering parasitic resistance of elements is used to calculate its efficiency [33, 34]. RDS-ON, R (D1, D2, D3), R (L1, L2, L3), R (C1, C2, C3) are resistance of power switch, ESR of diodes, ESR of inductors, and ESR of capacitors, respectively.

By implementing Eqs. (81–87) numerical power loss values of each component are calculated as follows:

Figure 6 illustrates the portion of each component in total power loss of the proposed converter. As it could be seen clearly, Diodes total loss are more than other elements. To have a comprehensive study, change of converter’s efficiency versus output power change is depicted as Fig. 7.

To have a calculation approximately near to the real, inductor core losses are considered in all of calculations as follows:

Comparison Study

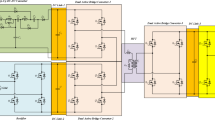

To assess the effectiveness of the proposed high-gain DC–DC converter, an extensive benchmark study was carried out against several existing topologies. Table 1 summarizes the main attributes of the suggested design and compares them with converters reported in [15,16,17,18,19,20,21,22,23,24,25,26,27]. The comparison considers aspects such as the number of components, overall device count, voltage gain, peak stress across switches and diodes, nominal power capacity, and input current ripple. In the voltage gain expressions of converters that utilize a coupled inductor, the parameter N denotes the turns ratio between the secondary and primary windings. This factor significantly impacts voltage gain performance. By contrast, the proposed topology is transformerless and does not rely on N, thereby avoiding leakage inductance, EMI, and additional losses typically associated with coupled-inductor-based converters. Figure 8a presents the voltage gain profile of the proposed topology in relation to other boost converters. The results indicate that the proposed design delivers a substantially higher voltage gain. This characteristic is particularly advantageous, as it enables the converter to achieve the required output at relatively low duty cycles. Operating at lower duty ratios reduces conduction losses and, consequently, enhances efficiency. Figure 8b compares the maximum voltage stress on the switches. The proposed converter demonstrates lower stress levels compared to its counterparts, allowing the use of more affordable power switches. Furthermore, minimizing switch stress directly contributes to reducing power dissipation, thereby improving overall performance. Similarly, Fig. 8c examines the voltage stress imposed on diodes. The proposed design again exhibits considerably lower stress, ensuring both cost reduction and efficiency improvement by lowering conduction and switching losses. Another critical factor considered is the input current ripple. A low input ripple is vital for renewable energy systems and other sensitive applications, as it ensures stable and reliable operation. Converters in [15,16,17,18,19, 25], and [27], listed in the comparison table, exhibit relatively high ripple levels, which restricts their suitability for such applications. The results confirm that the proposed converter delivers superior efficiency in comparison to most of the existing designs, with the exception of the configurations in [19, 23], and [26], which demonstrate slightly higher performance. In conclusion, the comparative analysis demonstrates that the proposed converter outperforms conventional designs by offering higher voltage gain, reduced stress on switching devices, and lower input current ripple. These features establish it as a strong candidate for high step-up power conversion applications.

Dynamic performance

In this section, average-state- space method has been used to give the transfer function. By employing Kirchhoff’s voltage and current law, the function includes: state, input and control variable are formulated as an equation of the output and state variables. All assumptions to write state-space equations are listed as follows:

-

The value of input voltage source of the proposed converter is adjusted in the constant value.

-

All of utilized inductors and series resistance of them are considered equal to L1=L2=L3=L and rl, respectively

-

All of utilized capacitors and series resistance of them are considered equal to C1=C2=C3=C and rc

By considering these conditions, there are 6 independent state variables. Equation (79) show the state-space form of the output variables.

Equations (79) illustrates the state variables and input variables vectors.

Steady state equations in intervals \((0\le t\le \left(D\right)T)\) which both of S1 and S2 are on, are written as follows:

The mentioned equations in interval \((DT\le t\le T)\) which G2 is on, is written as follows:

by considering Eq. (84), transfer function of the proposed converter is achieved as;

Figure 9 illustrates the phase and gain margin of Eq. (84).

To make a stability discussion, close-loop model and diagram are figured as Fig. 10.

To improve stability of close-loop model, by PID controller is used. Pole placement technique is used to equivalent model poles. To adjust PID controller, Ziegler and Nichols, tuning technique is used as follows [29]:

where: \({T}_{i}=4\times {T}_{d}\)

To improve phase margin with utilizing PID controller, the new transfer function is achieved as follows:

Figure 11 illustrates the bode diagram of close loop model with adjusted PID controller.

Experimental results

To validate the theoretical analysis and demonstrate the practical applicability of the proposed high-gain converter, a 200 W experimental prototype was developed. The key design specifications are provided in Table 2. Figure 12 presents the gating signals applied to switches S1 and S2. The measured inductor currents, displayed in Fig. 13a–c, closely follow the values derived from Eqs. (63–65), confirming the accuracy of the analytical model. Experimental results also verify the current and voltage stresses on the diodes. As shown in Fig. 14a, diode D1 conducts 13 A at 37 V. Diode D2 sustains 38 V and 9 A [Fig. 14b], while D3 operates at 38 V and 5 A [Fig. 14c]. Capacitor voltages are consistent with theoretical predictions as well: Fig. 15 records 37 V across C1 compared to the calculated 40 V from Eq. (11), and around 19 V across C2 and C3, which is close to the expected values from Eqs. (13) and (15). The prototype also delivers an output voltage of 195 V with a current of 1 A, as indicated in Fig. 16. These values are in strong agreement with the predicted 200 V from Eq. (16). Switching device stresses were further examined: Fig. 17a shows that S1 is subjected to a maximum of 36 V and 10 A, while Fig. 17b indicates that S2 withstands 75 V and 14 A. Both sets of measurements are consistent with the calculated results. In summary, the strong correlation between the analytical expectations and the experimental observations across Figs. 13–17 confirms the correctness of the theoretical analysis and validates the high performance of the proposed converter.

The proposed converter was tested under various load conditions and input values. In Fig. 18a, the output voltage of the converter initially registers around 96 V with a power output of about 200 W. When the load is suddenly altered and the output power is adjusted to 300 W, the output voltage remains relatively stable after brief transient fluctuations. The output voltage deviates only slightly from the reference value, demonstrating the stability of the closed-loop system in maintaining the output voltage close to the target. Figure 18b depicts the output voltage response when the input voltage suddenly drops from 20 to 15 V. It is evident from Fig. 18b that the output voltage shows minimal variation in response to the input change. Figure 19 illustrates the prototype of the proposed step-up converter.

Conclusion

This paper introduces a quadratic high step-up topology designed to minimize input current ripple, specifically tailored for DC microgrid applications. Low-power and low-voltage implementations of this topology typically support output ranges from a few watts to several tens of watts, with voltage levels spanning from 12 to 100V. The proposed converter is particularly well-suited for powering small-scale systems, including sensors, communication devices, and low-power appliances such as LED lighting. Additionally, it plays a major role in regulating the output of residential fuel cells (typically between 24 and 100V) to align with the operating voltage requirements of the microgrid. The suggested topology provides several notable advantages, such as increased voltage gains, lower voltage stress on switching components, continuous input current, a shared ground between the input and output, high efficiency, and synchronized switch operation. The adaptability of this topology makes it ideal for a wide range of applications, including robotics and switch-mode power supplies. In industrial environments, it effectively regulates DC motor speeds in assembly lines by controlling the DC link voltage.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Jia, P. & Yuan, Y. Analysis and design of an isolated high step-up converter based on the secondary side quasi-resonant loops. IET Power Electr. 13, 1129–1143 (2020).

Jia, P. et al. An isolated high step-up converter based on the active secondary-side Quasi-resonant loops. IEEE Trans. Power Electr. 37, 659–673 (2021).

Jin, T. et al. A New Three-Winding Coupled Inductor High Step-Up DC-DC Converter Integrating with Switched-Capacitor Technique. IEEE Transactions on Power Electronics, 2023.

Alghaythi, M. L. et al. A high step-up interleaved DC-DC converter with voltage multiplier and coupled inductors for renewable energy systems. IEEE Access 8, 123165–123174 (2020).

Seo, S.-W., Lim, D.-K. & Choi, H. H. High step-up interleaved converter mixed with magnetic coupling and voltage lift. IEEE Access 8, 72768–72780 (2020).

Mohammadi, F. Khorsandi, A. Dual‐input single‐output high step‐up DC–DC converter for renewable energy applications. IET Power Electronics, 2024.

Kumar, C. & Raj, T. D. A new non-isolated high-step-up DC–DC converter topology with high voltage gain using voltage multiplier cell circuit for solar photovoltaic system applications. J. Circuits Syst. Comput. 30, 2150014 (2021).

Nadermohammadi, A. et al. Cost-effective soft-switching ultra-high step-up DC–DC converter with high power density for DC microgrid application. Sci Rep 14, 20407. https://doi.org/10.1038/s41598-024-71436-w (2024).

Xu, P. et al. non-isolated switching-capacitor-integrated three-port converters with seamless PWM/PFM modulation. Sol. Energy 224, 160–174 (2021).

Paramasivam, SK, et al. Solar photovoltaic based dynamic voltage restorer with DC-DC boost converter for mitigating power quality issues in single phase grid. Energy Sources, Part A: Recovery, Utilization, and Environmental Effects, 2021, 1–25.

Lagudu, J. V. & Vulasala, G. Maximum energy harvesting in solar photovoltaic system using fuzzy logic technique. Int. J. Ambient Energy 42, 131–139 (2021).

Banaei, M. R. & Bonab, H. A. F. A high efficiency nonisolated buck–boost converter based on ZETA converter. IEEE Trans. Industrial Electr. 67, 1991–1998 (2019).

Nanda, H., Sharma, H., Yadav, A. Design and Implementation of a High-gain Switched-capacitor Step-up Multi-level Inverter with Reduced Components Count. Electric Power Components and Systems, 2024, 1–12.

Kariyat, V. K. P. & Janardhanan, J. J. Design and development of modified highly efficient high gain DC-DC converter for SPV standalone systems. Int. J. Power Electr. Drive Syst. (IJPEDS) 14, 1562–1576 (2023).

Radmanesh, H., Jashnani, H., Pourjafar, S. & Maalandish, M. A dual-output single-input non-isolated DC-DC converter with reduced semiconductors stress. Int J. Circ. Theor Appl. 51(2), 594–610 (2023).

Jalilzadeh, TBE. Maalandish, M, “Generalized Non-isolated High Step-Up DC-DC Converter with ReducedVoltage Stress on Devices”, International Journal of Circuit TheoryandApplications. https://doi.org/10.1002/cta.2506.

Zhang, Y., Zhou, L., Sumner, M. & Wang, P. Single-switch, wide voltage-gain range, boost DC–DC converter for fuel cell vehicles. IEEE Trans. Veh. Technol. 67(1), 134–145. https://doi.org/10.1109/TVT.2017.2772087 (2018).

Zhu, B., Wang, H., Vilathgamuwa, M. “Single Switch High Step-up Boost Converter Based on a Novel Voltage Multiplier,” IET Power Electronics. https://doi.org/10.1049/iet-pel.2019.0567.

Banaei, M. R. & Bonab, H. A. F. A Novel Structure for SingleSwitch Nonisolated Transformerless Buck-Boost DC-DC converter. IEEE Trans. Industr. Electron. 64(1), 198–205. https://doi.org/10.1109/TIE.2016.2608321 (2017).

Elsayad, N., Moradisizkoohi, H. & Mohammed, O. A. A SingleSwitch Transformerless DC–DC Converter With Universal Input Voltage for Fuel Cell Vehicles: Analysis and Design. IEEE Trans. Veh. Technol. 68(5), 4537–4549. https://doi.org/10.1109/TVT.2019.2905583 (2019).

Tang, Y., Fu, D., Wang, T. & Xu, Z. Hybrid switched-inductor converters for high step-up conversion. IEEE Trans. Industr. Electron. 62(3), 1480–1490 (2014).

Tang, Y., Wang, T. & He, Y. A switched-capacitor-based activenetwork converter with high voltage gain. IEEE Trans. Power Electron. 29(6), 2959–2968 (2013).

Sharifiyana, O. et al. Presenting a new high gain boost converter with inductive coupling energy recovery snubber for renewable energy systems-simulation, design and construction. J. Solar Energy Res. 8, 1417–1436 (2023).

Hu, R. et al. A non-isolated bidirectional DC–DC converter with high voltage conversion ratio based on coupled inductor and switched capacitor. IEEE Trans. Industrial Electr. 68, 1155–1165 (2020).

Sanjeevikumar, P. et al. non-isolated sextuple output hybrid triad converter configurations for high step-up renewable energy applications. In: Advances in Power Systems and Energy Management. Springer, Singapore, 2018. p. 1–12.

Spiazzi, G. et al. non-isolated high-step-up DC–DC converter with minimum switch voltage stress. IEEE Transactions on Power Electronics, 2018, 34.2: 1470–1480.

Kurdkandi, N. V. & Nouri, T. Analysis of an efficient interleaved ultra-large gain DC–DC converter for DC microgrid applications. IET Power Electronics 13(10), 2008–2018 (2020).

Zaoskoufis, K. & Tatakis, E. C. Isolated ZVS-ZCS DC–DC High Step-Up Converter With Low-Ripple Input Current. IEEE Journal of Emerging and Selected Topics in Industrial Electronics 2(4), 464–480 (2021).

Nouri, T. & Shaneh, M. A new interleaved ultra-large gain converter for sustainable energy systems. IET Power Electronics 14(1), 90–105 (2021).

Tarzamni, H. et al. non-isolated high step-up dc-dc converters: comparative review and metrics applicability. IEEE Transactions on Power Electronics, 2023.

Farahani, H. J., Rezvanyvardom, M. & Mirzaei, A. Non-isolated high step-up DC–DC converter based on switched-inductor switched-capacitor network for photovoltaic application. IET Generation, Trans. Distribution 17, 716–729 (2023).

Zamani, M. et al. Design and Implementation of Non-isolated High Step-Up DC-DC Converter. International Transactions on Electrical Energy Systems, 2023.

Rajabi, A. et al. A non-isolated high step-up DC-DC converter using voltage lift technique: analysis, design, and implementation. IEEE Access 10, 6338–6347 (2022).

Karimi Hajiabadi, M. et al. Non-isolated high step-up DC/DC converter for low-voltage distributed power systems based on the quadratic boost converter. Int. J. Circuit Theory Appl. 50(6), 1946–1964 (2022).

Dastgiri, A., Hosseinpour, M. & Poulad, A. A high step-up non-isolated DC-DC converter with active switched-inductor and switched-capacitor networks. Int. J. Model. Simulation 43(4), 462–473 (2023).

Nadermohammadi, A. et al. A non-isolated single-switch ultra-high step-up DC–DC converter with coupled inductor and low-voltage stress on switch. IET Power Electron. 17, 251–265 (2024).

Taheri, D., Shahgholian, G. & Mirtalaei, M. M. Analysis, design and implementation of a high step-up multi-port non-isolated converter with coupled inductor and soft switching for photovoltaic applications. IET Generation, Trans. Distrib. 16(17), 3473–3497 (2022).

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing interests

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Rostami, R., Hosseini, S.H. & Sharifian, M.B.B. High gain non-isolated step-up DC-DC converter proper for renewable energy applications. Sci Rep 15, 43608 (2025). https://doi.org/10.1038/s41598-025-26770-y

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-26770-y