Abstract

This paper proposes a non-isolated quadratic high-step-up DC-DC converter. A coupled inductor and a switched capacitor cell are implemented in its structure to increase voltage gain. Balancing the capacitor and the coupled inductor plays the role of the resonant tank, which solves the problem of reverse recovery losses of its diodes. In this structure, soft switching conditions are established for some diodes and MOSFET, which reduces the switching losses of the converter. With a low number of components, the proposed converter achieves a high voltage gain. The diode-capacitor clamp circuit is utilized to reduce the negative effects caused by the leakage inductance and recover the energy stored in it. The performance of the proposed converter is analyzed in the continuous and discontinuous conduction modes. An analysis of design considerations, including inductors and capacitors, is presented. In addition, an analysis of the efficiency of the proposed topology is provided. The proposed topology is compared in terms of voltage gain, voltage/current stress across semiconductor components, and converter efficiency with related topologies. Finally, a 210 W (20 V/420 V) laboratory prototype is presented to verify the proposed converter's mathematical analysis and performance.

Similar content being viewed by others

Introduction

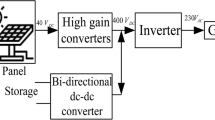

The issue of energy conversion has been one of the main challenges in the last decade, and engineers are always looking for new ways to provide the required energy. The most important sources are fossil fuels and renewable energy sources. Unlike renewable energy sources, fossil fuels are limited and produce much pollution1,2. As the output voltage of renewable energy systems is limited, power electronic converters are needed to provide high voltage gain. In the design of these converters, the output voltage gain, the voltage stress across the semiconductor elements, the number of elements, and the efficiency are considered3,4,5. In order to increase the output voltage gain, a switched capacitor cell and a coupled inductor can be used. In these types of converters, the capacitors of switched capacitor cells are charged in parallel and discharged in series, which increases the voltage gain of the converter. Of course, in this case, the coupled inductor can be used in the mentioned cell structure to improve the diode reverse recovery problem6,7. Also, the coupled inductor gives the converter higher degrees of freedom to increase output voltage gain and reduce voltage stress across the semiconductor elements8. In9,10,11, a transformer has been used as an isolation technique in those structures. The presence of voltage spikes across semiconductor elements is the main disadvantage of these converters, which is caused by the leakage inductance of the transformer. The number of components used in the structure of the converter is another significant issue for DC-DC converters. The presence of a substantial quantity of components increases the circuit's volume and the construction cost. In addition, each of the elements also includes losses12.

In13,14, two symmetrical switched capacitor cells are implemented in order to increase the output voltage gain. In addition, a passive clamp circuit was used to recover the leakage energy and improve the voltage spike across the switch. In15, a SEPIC DC-DC converter is presented. The structure of this converter includes voltage multiplier cells to increase the output voltage gain. Besides, the passive clamp structure has been used to recover the leakage energy of the coupled inductor. High diode counts and hard switching conditions have reduced converter efficiency.

In16,17, a diode-capacitor cell and two coupled inductors have been used to increase the output voltage gain. Also, in order to have soft switching conditions, the snubber capacitor is placed parallel to the main power switches. A large number of switches and the presence of a snubber capacitor and two coupled inductors increase the size of the structure of these converters. The DC–DC converter suggested in18 is based on the conventional boost converter. A switched capacitor cell has been used to increase its voltage gain in this structure; however, it has a low voltage gain. One of the methods to improve the efficiency is the quasi-resonant operation, which is utilized by the converters presented in19,20. Also, two passive clamp circuits are used in their structure. In21,22,23,24, the voltage lift technique was utilized to increase voltage gain. In this technique, energy storage elements such as capacitors and inductors are implemented in order to increase the output voltage gain and overcome the parasitic effects of the components. In25,26,27, the input source and the output terminal do not have a common ground. This method makes these converters unsuitable for PV applications. In some converters, a three-coil coupled inductor has been used to increase the output voltage gain, which has a sizeable magnetic core27,28,29. In the interleaved DC–DC converter presented in29, two pairs of three-coil inductors and a voltage multiplier cell are utilized to increase the output voltage gain in a cascade structure. Despite the hard switching conditions, the large number of semiconductor elements in this converter has caused an increase in losses and, as a result, a decrease in the converter efficiency.

In this paper, a non-isolated high-step-up DC-DC converter is presented. In order to increase the voltage gain, a coupled inductor and the switched capacitor cell are used in its structure. Due to the presence of the clamp circuit, there is a low voltage stress across the semiconductor components, which increases efficiency and reduces construction costs. The clamp circuit in the proposed structure recovers the leakage energy of the coupled inductor and increases the voltage gain. Additionally, soft switching conditions are established, and the current waveforms flowing through some diodes and MOSFETs are quasi-resonant, which leads to reduced switching losses.

Proposed converter operation principles

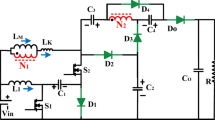

Figure 1 shows the structure of the suggested converter. In order to increase the output voltage gain, the coupled inductor and the switched capacitor technique are used. This structure contains two power switches (S1, S2), an inductor (L1), a coupled inductor, four diodes (D1, D2, D3 and DO) and four capacitors (C1, C2, C3 and CO). The input source is Vin, and the output port is VO. To simplify the steady-state analysis calculations, the following assumptions are considered:

-

1) All components of the converter are considered ideal.

-

2) The coupled inductor is modeled as a leakage inductor (LK) and a magnetizing inductor (Lm) at the primary side with a coupling coefficient k = Lm/(Lm + Lk) and its turn ratio is n = n2/n1.

The key waveform of the suggested converter in Continues Conduction Mode (CCM) is shown in Fig. 2. In the CCM condition, the proposed converter has four operation modes, as shown in Fig. 3a–d. Both power switches are turned on and off simultaneously. So, the control structure of the proposed converter is simple.

Mode I (t0 < t < t1): Regarding Fig. 3a, at the beginning of this time interval, switches S1 and S2 are simultaneously turned on, such that the power switch S2 is turned on under ZCS (Zero Current Switching) conditions. In this transient mode, the output diode DO is forward bias. Because of the influence of the reflected leakage inductance on the secondary side of the coupled inductor, the current passing through diode DO drops to zero at the end of this time interval, resulting in a low reverse recovery issue.

Mode II (t1 < t < t2): In this operation mode, MOSFETs S1 and S2 remain in on state from the previous operating mode. Diodes D2, and D3 are turned on at ZCS conditions and D1 and DO are reversed bias in this mode. The input source charges L1, and its current level increases linearly. Also, the current of L11 is energized by the input source and C1, and its current increases. C2 and C3 are charged through the secondary side of the coupled inductor. This operation mode ends when D2 and D3 are turned off at ZCS conditions. A schematic of the converter in this operational mode is illustrated in Fig. 3b. In this operation mode, the following equations are obtained:

In order to eliminate the reverse recovery loss of D2 and D3 as well as reduce the switch turn-off loss, it is mandatory that the resonant time (TR) be shorter than the turn-on time of the switching period (TR < D × Ts) as illustrated in Fig. 2.

Mode III (t2 < t < t3): In this transient operation mode, the power switches are in the on state, and all the diodes are reversed bias. Similar to operation mode II, L1 is charged by Vin, and L11 is charged by Vin and C1. In addition, the voltages of C2 and C3 remain constant. This operation mode ends when the power switches turn off. A schematic of the converter in this operational mode is shown in Fig. 3c. In this operation mode, the following equations are expressed:

Mode IV (t3 < t < t4): Regarding Fig. 3d, in this operation mode, D2, D3, and the power switches are in off state, and D1 and DO are forward biased. C1 is charged by Vin and L1. L11, C2, and C3 are discharged, and the current passing through L11 decreases. In addition, the input source, L11, C2, and C3 charge CO and supply the power to the output load. In this operation mode, the following equations are obtained:

Mode V (t4 < t < t5): This operation mode corresponds to the DCM condition as shows in Figs. 3e and 4. In this case, D1 is forward bias, and the rest of the semiconductor elements are in off state. C1 is charged through the input source and L1. CO supplies the output load power. For this operation mode, the following equations are expressed:

Steady state analysis

Voltage gain in CCM

By applying the volt-second balance principle for L1 and substituting (1) and (13) into it, the following equation is expressed:

According to (2) and (19), the following equation is achieved for the voltage across Lm in operation mode II:

Using (3) and (20), the following equation is obtained:

By applying the volt-second balance low for Lm and according to (20), the voltage across Lm in operation mode IV is obtained as follows:

By substituting (21) and (22) into (12), the following equation for the voltage gain of the converter in CCM condition is calculated:

In the ideal case, assuming k = 1, the output voltage gain of the converter is expressed as follows:

According to (24), the output current can be derived as:

Voltage stress across power semiconductors

Using mode II, the following equations are obtained:

According to operation mode IV, the following equations are expressed:

According to (19), (22), (26), (28), and (29), the following equations are achieved:

According to (19), (21), (22), (27), and (30), the following equations can be derived:

Current stress of power semiconductors

By applying the ampere-second balance low for CO, the following equation for the current passing through C3 in operation mode IV is achieved:

Using (15) and (35), the following equation can be written:

According to (4) and (5), the current passing through C2 in operation mode II is as follows:

By applying the ampere-second balance low for C2 and according to (35) and (37), the following equation for the current passing through the capacitor C1 in operation mode II can be obtained as:

Now, by substituting (36) into (38), the current passing through capacitor C1 in operation mode II is achieved as follows:

Using (39), the current of C1 in operation mode IV can be derived as follows:

According to (36), (37), and (39), the current passing through C2 in operation mode II is obtained as follows:

Using (14) and (40), inductor current L1 is expressed as:

According to operation mode II, it can be written:

According to operation mode IV, it can be written:

Using (39) and (42) into (43), the current stress of S1 can be obtained as follows:

Using (39) and (44), current stress of S2 can be obtained as:

According to (35), (40), (41), (45-47), the following equations are obtained for the current stress of the diodes:

Voltage gain in DCM

Discontinuous Conduction Mode (DCM) analysis is considered for the condition where the coupled inductor enters the DCM condition. The converter has five operation modes in DCM condition. These operation modes are shown in Fig. 3a-e. Figure 4 shows the key waveform of the suggested converter in DCM condition. According to this figure, by applying the volt-second balance low for Lm, the following equation is achieved:

According to (13), (20) and (53), the voltage gain in DCM condition is obtained as:

According to Fig. 4, the average value of the current passing through Lm is expressed as:

According to (20) and (55), the average current passing through Lm is achieved as follows:

By applying the ampere-second balance low for CO, the following equation is obtained:

According to (6), (16), (18) and (57), the following equation can be written for C3 in operating mode IV:

According to (15) and (58), the following equation for the average current through Lm is achieved:

By substituting (56) into (59), the following equation for Δ1 can be obtained:

According to (54) and (60), the output voltage gain of the converter in DCM condition is achieved as:

Using (23), (61), and assuming that the normalized input inductor time constant equals τ = fsLm/R, where R represents the load resistance, the boundary conditions between CCM and DCM are as follows:

According to this equation, the boundary conduction mode (BCM), CCM, and DCM regions for n = 2 can be plotted as shown in Fig. 5.

Non-ideal voltage gain in CCM

The deviation of the non-ideal voltage gain of the proposed converter is influenced by parasitic parameters and leakage inductance. In this analysis, the resistances of the components are considered as follows: inductor and coupled inductor (rL1, rL11, rL12); capacitors (rC1, rC2, rC3, rCO); switches (rDS(on)1, rDS(on)2); diodes (rD1, rD2, rD3, rDO), along with their forward voltage drops (VF1, VF2, VF3, VFO). By applying KVL in the loops containing L1 and Lm the following equations are derived in the operating mode II:

By substituting (65) into (64), it can be written:

By applying KVL in the loops including inductors L1 and Lm, the following equations are obtained in the operating mode IV:

By applying the volt-second balance for L1, the following equation for the voltage across the capacitor C1 is obtained:

By applying the volt-second balance for Lm, the following equation is obtained:

By substituting (66) into (70), it can be written:

By substituting (69) into (71), the following equation is obtained:

By simplifying Eq. (72), it can be written:

According to (36), (39), and (42), the following equations are expressed:

By substituting (74-76) into (73), it can be written:

By simplifying (77), the following equation is obtained:

By simplifying (78), the non-ideal output voltage of the proposed converter with the influence of leakage inductance and parasitic resistances of the elements is obtained as follows:

Considering (79) and according to Table 2, the non-ideal voltage gain versus duty cycle D is illustrated in Fig. 6. This figure shows how voltage gain changes with the duty cycle (D) for both an ideal and a non-ideal power converter. The solid red line represents the ideal theoretical case, while the blue dashed line accounts for non-ideal model, assuming an output power of 210 W. Figure 6 is plotted in k = 0.985 and R = 840 Ω. As can be seen, the effect of leakage inductance and parasitic resistances is less at lower duty cycles leading to a comparatively higher efficiency.

The small inset zooms in on a specific range (around D = 0.5) to highlight the gap between the two models. As expected, the non-ideal case results in a lower voltage gain due to practical factors like parasitic resistances and switching losses. Interestingly, the non-ideal gain peaks sharply at high duty cycles before dropping, indicating potential instability or inefficiency in that region.

Design considerations

Inductor design

The voltage across the inductor is proportional to the current that passes through the inductor per unit of time. So, it can be written as:

By considering the maximum acceptable current ripple of 20% for inductors L1 and Lm and according to operation mode II and substituting (1) and (20) into (80), the minimum inductor inductance of L1 and Lm are obtained from the following equation:

Capacitor design

The current passing through the capacitor is proportional to the voltage changes across the capacitor per unit of time. So, it can be written as:

By considering the maximum acceptable ripple of voltage for capacitors usually 1% of the voltage across capacitor C1) and according to operation mode II and using (39) and (83), the following equation is obtained:

According to (5), the current passing through C1 and C2 is equal in operation mode II. By taking into consideration the maximum acceptable voltage ripple for capacitors (usually 1% of the voltage across capacitor C2, C3, and CO).

And by substituting (6) and (41) into (83), the following equations can be written:

Efficiency analysis

In this section, the converter efficiency is investigated by considering the presence of parasitic resistances of the elements. Table 1 shows the RMS values of the current passing through the elements by considering n = 2, D = 0.5, and output resistance R = 840 Ω. Table 2 displays the power loss breakdown across different proposed converter components. In this table, VF denotes the forward voltage drop of the diode. Rds and rD are the on-state resistance of the switch and the diode, respectively. Internal resistances of the capacitor and the inductor are represented by rC and rL, respectively. In addition, the power semiconductors specification and their part numbers are provided. Figure 7 shows the power loss distributions of the constituent elements of the suggested converter. According to this figure, the highest share of power losses is related to diode losses, and the lowest is related to capacitor losses. The efficiency and voltage gain curves of the converter versus the duty cycle and for n = 2 are shown in Fig. 8. As shown in this figure, although the voltage gain of the converter increases with the increase of the duty cycle, the efficiency of the converter is acceptable up to a certain range and then decreases. As can be seen, at high-duty cycle ranges, conduction losses increase, and efficiency is reduced.

Inductor losses: The conduction losses of the inductor and coupled inductor are calculated as following equations:

The core power losses related to the inductors is calculated as30:

The power loss (PC) is expressed in unit W/kg. The parameters α, β and k known as the Steinmetz coefficients, are typically specified by manufacturers for various core materials. For ferrite materials, the values of α can vary from 1 to 2, (1 ≤ α ≤ 2). Based on Faraday's Law, it can be written:

The parameter Ac represents the core area as specified by manufacturers for various types of magnetic cores. N is the turns of inductor's windings. Hence, the peak flux density of ΔB for the inductor and the coupled inductor, can be determined as follows:

The core loss in both inductor and coupled inductor can be expressed as PCore = PCM, where M represents the mass of the core. Therefore, considering Bm = ΔB/2, the core loss of inductor and coupled inductor is calculated as:

The parameters utilized for the calculation of the core losses are as:

k = 5.597 × 10−4, α = 1.43, β = 2.85, ML1 = 0.089 kg, MCL = 0.215, AC_L1 = 178mm2, Ac_CL = 353mm2 fs = 50 kHz.

The total power loss of inductors is obtained as follows:

Switch losses: The power losses of the switches are determined as:

COSS is the parasitic capacitor of the switch. PCoss is obtained as follows31:

The total power loss of the switches is obtained from the following equation:

Diode losses: The power losses of the diodes are determined as:

The total power loss of the diodes is obtained from the following equation:

Capacitor losses: Losses of the capacitors are determined as follows:

The total power loss of the capacitors is obtained as the following equation:

Therefore, the total power losses PLoss is written as:

Consequently, the total efficiency of the proposed converter can be calculated as:

Dynamic model and control method

The proposed topology consists of six storage elements, where the voltage and current of the components can be derived as follows:

First stage:

Second stage:

To derived state space vectors, these equations can be rewritten as follows:

Therefore, the achieved equations can be stated as follows:

Dynamic modeling of the proposed converter

For dynamic response analysis, independent storage elements are considered as state variables vector (x). Given that the voltage equations for capacitors C₂ and C₃ are identical, one of them can be excluded to simplify the analysis. In this converter, L1 , Lm, C1, C2, and Co are selected as state variables. The state variables vector (x), input vector (u), and output vector (y) are considered as follows:

The average state space of the overall system can be displayed as follows

Equation (124) can be expressed as:

In this case, A, B, C, and D can be written as:

According to the small signal modeling method, state variables, duty cycles, input and output voltages consist of two segments, a DC (\(\mathop X\limits^{\_\_} , \, \mathop Y\limits^{\_\_} , \, \mathop U\limits^{\_\_} , \, \mathop D\limits^{\_\_}\)) part and an AC (\(\tilde{x}, \, \tilde{y}, \, \tilde{u}, \, \tilde{d}\)) part.

It is supposed that the AC values are significantly smaller than the DC values (\(\mathop X\limits^{\_\_} > > \tilde{x}, \, \mathop Y\limits^{\_\_} > > \tilde{y}, \, \mathop U\limits^{\_\_} > > \tilde{u}, \, \mathop D\limits^{\_\_} > > \tilde{d}\)) and do not change considerably during one period. Therefore, the small signal model can be displayed as follows:

In the small signal analysis, input voltage is short circuited. In (132), \(\mathop x\limits^{ \cdot }\), \(\widetilde{{\text{u}}}\) and \(\mathop y\limits^{ \cdot }\) are the state variables vector, control signals, and output signals, respectively. The new state space vector based on these definitions can be rewrite as follows:

where \({\text{A}}{\prime}\)(n × n fixed matrix), \({\text{E}}{\prime}\)(n × n fixed matrix), and \({\text{C}}{\prime}\)(m × n fixed matrix) are calculated as follows:

Transfer function of this state-space vector can be expressed as:

For this system, by using parameters' values from Table 3, the step response can be modeled in MATLAB. The step-response is shown in Fig. 9. The step response shown in the figure indicates that the system is highly unstable. Initially, the output remains close to zero, but as time progresses, it exhibits an exponential divergence, rapidly growing to an extremely large value (on the order of 1023). This behavior suggests that the system has at least one unstable pole with a positive real part, leading to an unbounded response. Such instability can arise from inherently unstable open-loop system. To address this issue, a stability analysis should be conducted by examining the system's poles and adjusting the controller parameters potentially through modifying the pole placement strategy to ensure all poles have negative real parts, leading to a stable response.

Pole placement control description

Since the proposed topology is unstable it is required to apply pole-placement strategy, in this case, control diagram is illustrated in Fig. 10. This block diagram represents a state-space control system designed to regulate the output voltage VCO. The reference input VCO,ref is processed through an integrator to eliminate steady-state error, with feedback gains kq and kx adjusting the control input. Matrices A', C', D, and E' define the system dynamics, ensuring stability and desired performance. The control law combines integral and state feedback to achieve accurate voltage regulation. This structure suggests a pole placement control approach for enhanced system response.

Based on Fig. 10, the following equations can be written:

where q is the integrator output and r is the reference signals vector for the output variable. The vector r can be expressed as:

It can be simplified as follows:

In this method, if the control system is complete state controllable, it can be located the closed-loop poles to any suitable location with proper design of the state feedback gain matrix. The controllability matrix of this system is defined as follows:

For this system, if the rank of the controllability matrix Øc is complete, then the system is completely controllable.

Using Fig. 10 and Eqs. (135), (136), and (137), the open-loop state matrixes change to the matrixes \(\tilde{A}^{\prime}\) and \(\tilde{E}^{\prime}\) as follows:

Now, the new controllability matrix \(\overline{{\Phi_{c} }}\) is assumed as follows:

Then, the \(\overline{{{\Phi }_{{\text{c}}} }}\) can be written as follows:

If the following matrix rank is equal to n + m, the defined system will be completely state controlled.

The fourth eigenvalues of the matrix \(\tilde{A}^{\prime}\) are obtained as follows:

As can be seen, two eigenvalues have positive real part. These eigenvalues should be sufficiently shifted to the left side of the jw axis in order to reach the desired location of the converter closed-loop eigenvalues and achieve desired phase margin (PM ≥ 80) and gain margin (GM ≥ 10). The new eigenvalues are determined as follows:

Using the formula in MATLAB for placing the eigenvalues by importing the matrixes (\(\tilde{A}^{\prime}\) and \(\tilde{E}^{\prime}\)), and considering the designed places for the closed-loop eigenvalues, this relation can be written:

The control coefficients matrixes kx and kq are obtained as follows:

Also, after this control method, the transfer functions are obtained as follows:

By importing (21) and (22) in (28), the state equations of the control system are written as follows

The bode diagram illustrates the frequency response of the system before and after applying the control strategy in Fig. 11. The magnitude plot (top) shows how the system gain varies with frequency, while the phase plot (bottom) depicts the phase shift across different frequencies. Before control (blue line), the phase response and the phase margin was negative (-4.99°), confirming that the system was unstable. The gain margin was infinite, suggesting no gain crossover point, further emphasizing instability. After applying control (red line), the magnitude response was significantly improved, leading to a more stable frequency response. The phase response also became smoother, reducing abrupt shifts. The phase margin increased to 122.92°, and the gain margin became 33.21 dB, ensuring system stability and robustness. Overall, the applied control strategy effectively stabilizes the system by improving margins, leading to a well-conditioned and reliable design.

Furthermore, the step response of the utilized control strategy is depicted at Fig. 12. This figure shows the step response of the system, which represents how the system's output VO(s) responds to a step input in D(s). The output starts at zero and rises quickly, indicating a fast transient response. The system overshoots above the final steady-state value (around 1.2 before settling back to 1). Overshoot occurs due to the system's dynamics and can indicate underdamping. The system stabilizes at around 1.5 ms. This suggests a fast response time, which is ideal in many control applications. After the transient response, the output remains close to 1, indicating no steady-state error.

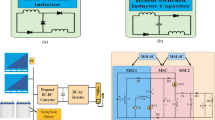

Comprehensive comparison

In this section, the proposed converter is compared with some other converters. In Table 4, the voltage gain, the number of elements, normalized voltage stress (NVS) across the main power switch, input and output common ground feature, and the efficiency of the converters at 210 W are gathered and tabulated. In order to make a fair comparison, the value of n = 2 is considered for the turn ratio of all converters. Figure 13a shows the curves of the output voltage gain versus the duty cycle of the suggested structure and other compared converters. Based on this figure, the voltage gain of the suggested converter is higher than the voltage gain of other compared converters for all duty cycle values. Therefore, it can be said that the suggested topology is an high-step-up converter. Figure 13b shows the output voltage gain per the number of elements (Gain/TCC) versus the duty cycle. According to this figure, the output voltage gain of the proposed converter is higher than other converters. Therefore, it can be said that the proposed converter provides a high output voltage gain for a low number of components compared to other references. On the other hand, it can be concluded that the proposed topology components are structured better than the other topologies to provide higher voltage gains. Figure 13c shows the normalized voltage stress across the main power switch. As shown in this figure, the normalized voltage stress across the main power switch of the proposed converter has the lowest value compared to other structures for all duty cycle values.

Comparison of the proposed converter with converters mentioned in {R2-6} Table 4 in terms of (a) output voltage gain, (b) Gain/TCC, (c) normalized voltage stress (NVS) across the main power switch, (d) normalized total voltage standing (NTVS).

Furthermore, with an increase in the duty cycle, the normalized voltage stress across the main power switch of the suggested converter decreases. This highlights the superiority of the proposed converter, as the reduction in voltage stress is evident when the duty cycle is raised in relation to the output voltage. As a result, a power switch with low power specifications and low Rds(on) can be used, which reduces the cost and increases the efficiency. The total normalized voltage stress across the semiconductor elements is shown in Fig. 13d. According to this figure, the total normalized voltage stress of the proposed converter is lower than the structures in14,16,17,19,27,28 for all duty cycle values. Furthermore, for D < 0.65, the total normalized voltage stress of the proposed converter is lower than the structures in24,29. It should be noted that when D > 0.65, conduction losses increase. Moreover, the converter presented in18 has the lowest total normalized voltage stress compared to the other converters. According to {R2-6} Table 4, the number of components of the proposed converter is equal to the number of components of the structures presented in13,18,19. Other compared structures have more components than the proposed converter. Another notable advantage of the proposed topology is the establishment of a common ground for both input and output, resulting in reduced electromagnetic interference (EMI) issues. Furthermore, the experimental efficiency of the proposed converter in the output power of 210 W is lower than the efficiency of25 and higher than the efficiency of all other compared converters.

Experimental Results

In this section, to verify the theoretical analysis, the experimental results of the prototype of the suggested converter are presented. The prototype of the proposed converter is shown in Fig. 14. The specifications of the prototype are listed in Table 2. The goal is to convert the input voltage Vin = 20 V to the output voltage Vout = 440 V until the converter delivers 210 W output power. For this purpose, by setting n = 2 and according to (24), the converter's duty cycle should be considered equal to D = 0.5. The switching frequency is considered equal to fS = 50 kHz. An 840 Ω load is placed on the output port. By considering ΔIL1 = 1 A and ΔILm = 4.25 A and according to (81) and (82), the minimum inductance values of L1 and Lm are equal to 200 µH and 140 µH, respectively. Therefore, the inductance values of L1 and Lm in the prototype are considered equal to 300 µH and 150 µH, respectively. By considering ΔVC1 = 8 V, ΔVC2 = ΔVC3 = 3 V, and ΔVCO = 0.03 V and according to (84)-(87), the minimum capacity values of C1, C2, C3, and CO are equal to 4.3 µF, 3.3 µF, 3.3 µF and 166 µF, respectively. So, the capacity values of C1, C2, and C3 are considered equal to 4.7 µF, and the capacitance value of CO is considered equal to 220 µF. Figure 15a shows the output current and voltage waveforms obtained from the laboratory prototype. It is shown in this figure that the output voltage is equal to 420 V, which proves the statement (24), and the current passing through the output load is equal to 0.5 A. 10 (b) shows the current waveform of L1. According to this figure, the average current value of L1 equals 6.96 A, which corresponds to (42). Figure 16 shows the current and voltage waveforms of S1 and S2. According to Fig. 16a, the voltage stress of S1 is equal to 38.5 V. In addition, the waveform of the current passing through it is quasi-resonant. Also, according to Fig. 16b, the voltage stress of S2 equals 78 V. In addition, as can be seen in this figure, S2 turns on under ZCS conditions, and the waveform of the current passing through this power switch is also quasi-resonant.

Figure 17 shows the voltage and current waveforms of D1, D2, D3, and DO. According to Fig. 17a, the voltage stress of D1 is equal to 38 V. As shown in Fig. 17b and c, the voltage stress of D2 and D3 is equal to 230 V. As evident from the observation, the current waveforms of these diodes reach zero before experiencing reversed or forward biases. This observation substantiates these diodes' ZCS condition. Figure 17d illustrates voltage and current stress across DO, which is 348 V, and proves the provided mathematical analysis. Figure 18 shows the voltage waveforms of C1, C2, and C3. As shown in this figure, the voltage across C1, C2, and C3 are equal to 39 V, 117 V, and 117 V, respectively.

The control strategy was successfully implemented in an experimental setup to evaluate its performance under varying conditions. Figure 19a illustrates the system's response to input voltage variations, demonstrating a rapid transient response with minimal overshoot. This confirms the controller's effectiveness in maintaining stability.

Figure 19b presents the system's dynamic response to a load variation. Initially, the load resistance is set at 840Ω, and at a certain instant, it is increased to 1000 Ω. The transient region, highlighted in the middle of the figure, shows the system's reaction to this change. The output current (iO) decreases as expected due to the reduced load current demand, while the output voltage (VO) remains stable with minimal deviation, confirming the effectiveness of the applied control strategy. The system successfully regulates the voltage despite the load variation, demonstrating the robustness of the proposed control method.

The experimental and theoretical efficiency curves of the proposed converter versus output power are shown in Fig. 20. As depicted, the prototype's efficiency in Vin = 20 V and Pout = 210 W is about 96.3%. Consequently, the proposed converter provides higher efficiency than 95.25% for different output power ranges.

Conclusion

In this paper, a non-isolated quadratic high-step-up DC-DC converter is presented. A coupled inductor and the switched capacitor cell are utilized in this structure to increase the voltage gain. The proposed converter provides high voltage gain with a low number of elements. Low voltage stress across power switches is another advantage of the presented topology, which leads to the selection of MOSFETs with low internal resistance Rds(on). A diode-capacitor clamp circuit is utilized to reduce the negative effects of leakage inductance and recover stored energy, leading to soft switching conditions for half of the diodes. The combination of these features provides a new topology with a high efficiency of 96.3%, which is recorded at 210W. Steady-state analysis, design consideration, and efficiency analysis are presented in detail. The proposed converter is compared with related structures, and it is observed that the proposed topology has higher efficiency and voltage gain compared to other structures. Finally, to verify the converter's performance qualification and mathematical analysis, a 210 W laboratory prototype is built, and its outcomes are thoroughly examined.

Data availability

All data generated or analyzed during this study are included in this published article.

References

Selvam, S., Sannasy, M. & Sridharan, M. Analysis and design of two-switch enhanced gain SEPIC converter. IEEE Trans. Ind. Appl. 59(3), 3552–3561 (2023).

Qiu, M., Sun, Z., Liu, X., Meng, H., Marzang, V., Cao, D. A 15x matrix autotransformer switched-capacitor DC-DC converter for datacenter application. 2024 IEEE APEC, Long Beach, CA, USA, 2024, pp. 88-93

Fani, R., Akhlaghi, Z. & Adib, E. High step-up DC-DC converter by integration of active switched inductors, built in transformer, and multipliers. IEEE Trans. Power Electron. 39(2), 2468–2477 (2024).

Karimi, K., Babaei, E., Karimi, M., Alizadeh, D. & Mousavi, S. M. J. An interleaved high step-up DC–DC converter based on coupled-inductor. IET Power Electron. 17, 473–485 (2024).

Nadermohammadi, A. et al. Cost-effective soft-switching ultra-high step-up DC–DC converter with high power density for DC microgrid application. Sci. Rep. 14, 20407 (2024).

Marzang, V., Babaei, E., Mehrjerdi, H., Iqbal, A. & Islam, S. A high step-up DC–DC converter based on ASL and VMC for renewable energy applications. Energy Rep. 8, 12699–12711 (2022).

Nadermohammadi, A. et al. A non-isolated single-switch ultra-high step-up DC–DC converter with coupled inductor and low-voltage stress on switch. IET Power Electron. 17, 251–265 (2024).

Hashemzadeh, S. M., Marzang, V., Pourjafar, S. & Hossein Hosseini, S. An ultra high step-up dual-input single-output DC–DC converter based on coupled inductor. IEEE Trans. Ind. Electron. 69(11), 11023–11034 (2022).

Goyal, V. K. & Shukla, A. Two-stage hybrid isolated DC–DC boost converter for high power and wide input voltage range applications. IEEE Trans. Ind. Electron. 69(7), 6751–6763 (2022).

Kiran, R. & Kalpana, R. An isolated dual-input half-bridge DC–DC boost converter with reduced circulating power between input ports. IEEE Canad. J. Electr. Comput. Eng. 45(1), 68–76 (2022).

Salehi Dobakhshari, S., Milimonfared, J., Taheri, M. & Moradisizkoohi, H. A quasi-resonant current-fed converter with minimum switching losses. IEEE Trans. Power Electron. 32(1), 353–362 (2017).

Abbasi Shahabi, M. et al. Symmetric wide-input-voltage range boost Z-source DC–DC converter with reduced current of source and active components. IEEE Trans. Power Electron. 38(8), 9961–9971 (2023).

Hassan, W., Lu, D.D.-C. & Xiao, W. Single-switch high step-up DC–DC converter with low and steady switch voltage stress. IEEE Trans. Ind. Electron. 66(12), 9326–9338 (2019).

Meier, M. B., da Silva, S. A., Badin, A. A., Romaneli, E. F. R. & Gules, R. Soft-switching high static gain DC–DC converter without auxiliary switches. IEEE Trans. Ind. Electron. 65(3), 2335–2345 (2018).

Eskandarpour Azizkandi, M., Sedaghati, F., Shayeghi, H. & Blaabjerg, F. Two-and three-winding coupled-inductor-based high step-up DC–DC converters for sustainable energy applications. IET Power Electron. 13(1), 144–156 (2020).

Alavi, P., Mohseni, P., Babaei, E. & Marzang, V. An ultra-high step-up dc–dc converter with extendable voltage gain and soft-switching capability. IEEE Trans. Ind. Electron. 67(11), 9238–9250 (2020).

Mohseni, P., Hosseini, S. H. & Maalandish, M. A new soft switching dc–dc converter with high voltage gain capability. IEEE Trans. Ind. Electron. 67(9), 7386–7398 (2020).

Sadeghpour, D. & Bauman, J. High-efficiency coupled-inductor switched-capacitor boost converter with improved input current ripple. IEEE Trans. Ind. Electron. 69(8), 7940–7951 (2022).

Hasanpour, S., Siwakoti, Y. P., Mostaan, A. & Blaabjerg, F. New semiquadratic high step-up dc/dc converter for renewable energy applications. IEEE Trans. Power Electron. 36(1), 433–446 (2021).

Hasanpour, S., Forouzesh, M., Siwakoti, Y. P. & Blaabjerg, F. A new high-gain, high-efficiency SEPIC-based DC–DC converter for renewable energy applications. IEEE J. Emerg. Sel. Top Ind. Electron. 2(4), 567–578 (2021).

Marzang, V. et al. A high step-up nonisolated DC–DC converter with flexible voltage gain. IEEE Trans. Power Electron. 35(10), 10489–10500 (2020).

Khan, S., Zaid, M., Siddique, M. D. & Iqbal, A. Ultra high gain step up DC/DC converter based on switched inductor and improved voltage lift technique for high-voltage applications. IET Power Electron. 15, 932–952 (2022).

Marzang, V. et al. A modified triple-switch triple-mode high step-up DC–DC converter. IEEE Trans. Ind. Electron. 69(8), 8015–8027 (2022).

Fani, R., Farshidi, E., Adib, E. & Kosarian, A. Analysis, design, and implementation of a ZVT high step-up DC–DC converter with continuous input current. IEEE Trans. Ind. Electron. 67(12), 10455–10463 (2020).

Hu, X., Liang, W., Liu, X. & Yu, Z. A hybrid interleaved DC–DC converter with a wide step-up regulation range and ultralow voltage stress. IEEE Trans. Ind. Electron. 67(7), 5479–5489 (2020).

Liang, T.-J., Luo, P. & Chen, K.-H. A high step-up DC–DC converter with three-winding coupled inductor for sustainable energy systems. IEEE Trans. Ind. Electron. 69(10), 10249–10258 (2022).

Akhlaghi, B., Molavi, N., Fekri, M. & Farzanehfard, H. High step-up interleaved ZVT converter with low voltage stress and automatic current sharing. IEEE Trans. Ind. Electron. 65(1), 291–299 (2018).

He, L. et al. A plug-play active resonant soft switching for current-auto-balance interleaved high step-up DC/DC converter. IEEE Trans. Power Electron. 34(8), 7603–7616 (2019).

Salehi, S. M., Dehghan, S. M. & Hasanzadeh, S. Interleaved-input series-output ultra-high voltage gain DC–DC converter. IEEE Trans. Power Electron. 34(4), 3397–3406 (2019).

Marzang, V., Islam, S., Iqbal, A., Mehrjerdi, H., Cao, D. A new quadratic high step-up DC-DC converter based on coupled inductors for renewable energy applications. IEEE J. Emerg. Sel. Topics Power Electron.

Imanlou, A., Babaei, E. and Hosseini, S. A new high voltage gain common-ground step-up DC-DC converter integrating coupled-inductors and switched-capacitors. Int. J. Circ. Theor. Appl. (2024).

Author information

Authors and Affiliations

Contributions

Conceptualization, K.K., V.M, M.K., S.H.H., and M.R.F.; methodology, K.K.; software, K.K., V.M., and M.K.; validation, K.K., S.H.H., and M.R.F.; investigation, K.K., V.M, M.K., resources, K.K., V.M., and M.K.; data curation, K.K.; writing—original draft preparation, K.K., V.M., and M.K.; supervision, S.H.H., and M.R.F.; Funding acquisition: K.K.; Visualization: K.K., V.M, and M.K.; writing—review and editing: K.K., V.M, and M.K.; project administration, K.K., S.H.H., and M.R.F.; Formal analysis: K.K. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Karimi, K., Marzang, V., Karimi, M. et al. High-step-up quadratic DC–DC converter based on switched capacitor and coupled inductor techniques. Sci Rep 15, 9487 (2025). https://doi.org/10.1038/s41598-025-94214-8

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-94214-8

This article is cited by

-

A new high voltage gain step-up converter with minimum phase characteristic

Scientific Reports (2025)

-

A novel soft-switched trans-inverse ultra-high-gain DC/DC converter with low switch voltage stress

Scientific Reports (2025)