Abstract

As Moore’s law approaches its limits, chalcogenides offer a promising route to next-generation computing and sensing, thanks to their topological, magnetoelectric, excitonic, and spintronic properties. Yet the same traits that make them appealing, e.g., exotic properties at monolayer thickness, clean van der Waals interfaces, and strong many-body effects, also heighten sensitivity to fabrication, hindering translation into scalable devices. Progress is further constrained by fragmented knowledge across synthesis, processing, and integration, and by the lack of systematic links between fabrication parameters and performance metrics. This Perspective examines key obstacles in controlling chalcogenide heterostructures and stresses the need for an integrated co-design framework, uniting materials growth, processing, and device architecture to accelerate practical technologies.

Similar content being viewed by others

Introduction

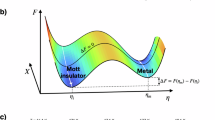

Moore’s law1, the semiconductor industry’s guiding principle for over half a century, is ending. Similar statements have been made by researchers for many years; however, improvements in material quality and innovative fabrication techniques have repeatedly delayed the law’s anticipated demise2,3,4,5. Nonetheless, physical limitations associated with shrinking device dimensions are now becoming unavoidable. Fundamentally, conventional electronics relies on shuttling charge through ever-smaller transistors, and beyond a certain scale, electrons cannot be reliably controlled without incurring unacceptable power losses and heat generation6,7,8,9,10. If computing technologies are to continue advancing, we must look beyond classical charge-based logic toward new paradigms that leverage other fundamental physical resources, such as spin or light, and reimagine how information is processed, stored, and transmitted. Quantum computing and neuromorphic architectures are prime examples of potential successors, but their realization hinges on harnessing quantum materials whose exotic quasiparticles can truly move us beyond the charge-manipulation framework. Due to the entangled nature of quantum resources and their sensitivity to local surroundings, we must also reimagine the co-design workflows to realize quantum technologies. Traditional Technology Readiness Levels (TRLs), even when applied to quantum technologies, still reflect linear trajectories from fundamental principles to practical applications11,12. However, to fully harness new quantum resources, we must recognize the intrinsic link between quantum material property and quantum device functionality and adapt a more end-to-end cyclic co-design process, as shown in Fig. 1. Current efforts are hindered by gaps in materials–process integration, a lack of comparative studies that link processing choices to performance, and reproducibility challenges across laboratories. Addressing these issues demands a co-design strategy in which materials development and device engineering evolve in concert, guided by systematic feedback.

The inherent sensitivity and coupling of quantum states preclude a simple linear trajectory from fundamental quantum principles to functional prototype devices. Material interfaces and fabrication-induced defects significantly affect device performance in the quantum realm, necessitating their careful integration at every stage of development.

Over the past decades, there has been a surge of “use-inspired” research into novel quantum materials that promise remarkable properties for next-generation technologies. These materials, exemplified by chalcogenides and other two-dimensional (2D) systems, exhibit quantum phenomena such as excitonic and many-body interactions13,14,15,16,17,18, topological order19,20,21,22, magnetoelectric and multiferroic effects23,24,25,26, and tunable bandgaps27,28,29,30. The foundational breakthroughs in isolating single-atom-thick layers of graphene spawned an avalanche of discovery across a broad family of 2D compounds31. Today, chalcogenides stand out in particular for demonstrating exotic phenomena, including superconductivity32,33,34,35,36, ferromagnetism37,38,39, and ferroelectricity40,41,42,43,44,45,46,47,48, in atomically thin layers. These properties and phenomena are not simply academic curiosities: they open the door to entirely new device concepts, including field effect and spin-based transistors49,50,51,52,53,54,55,56,57,58 and memories59,60,61,62,63,64,65,66, spintronics49,60,67,68,69,70,71,72,73,74,75,76,77,78, valleytronics74,75,79,80,81,82,83,84,85,86,87,88, high-performance optoelectronics and photonics29,62,89,90,91,92,93,94,95,96,97,98,99,100,101,102,103,104,105,106,107,108,109,110,111, neuromorphic65,112,113,114,115,116,117,118,119,120,121 and quantum computing platforms90,122,123,124,125,126,127,128,129,130,131,132,133, and many others as outlined in Fig. 2. The central question becomes how to make the use-inspired useful.

Despite these impressive demonstrations of novel physics, efforts to integrate 2D chalcogenide materials into large-scale, commercial-ready devices have remained largely proof-of-concept. The crux of the challenge lies in translating exotic quantum properties into robust, manufacturable, and scalable platforms without quenching the very effects that make these materials so compelling. Traditional semiconductor processing techniques, developed and refined over decades for silicon and CMOS-based technologies, often fail when applied to chalcogenides, either due to chemical incompatibilities, interface damage, or the introduction of parasitic defects113,134,135,136,137,138. Because 2D materials often rely on van der Waals bonding to maintain ideal, dangling-bond-free interfaces, conventional chemical etching, lithography, and thermal treatments can introduce inhomogeneities, impurities, and cracks that degrade device performance113,135,136,137,138,139,140,141,142,143,144,145. Furthermore, the inability to effectively dope 2D semiconductors in three-dimensional ways complicates forming reliable, ohmic contacts, which remain a critical bottleneck in making operational 2D circuits136,144,145.

Yet it is precisely these ultra-clean, atomically sharp interfaces that make chalcogenide materials so promising. With no dangling bonds at the surface, 2D chalcogenides can be stacked in arbitrary heterostructures with relaxed constraints of lattice matching, resulting in tunable interfaces64,94,141,146,147,148,149,150,151,152. Their extended possibilities for phase and defect engineering allow for substantial control over physical properties, ranging from band alignments and carrier densities to magnetism and excitonic interactions, by adjusting the atomic and electronic structures on demand92,113,147,153,154,155,156,157,158,159,160. The potential for low-leakage, high-mobility devices at sub-nanometer gate lengths has generated enormous excitement53,54,99,101,106,160,161,162,163,164,165,166,167,168. Additionally, the dramatic range of band gaps exhibited by these materials, encompassing metallic to semiconducting regimes, offers versatility in designing both logic elements and photonic devices for applications in data communications, sensing, and quantum information27,28,29,58,92,168,169,170,171,172,173,174,175,176.

An equally important aspect is the potential energy efficiency gained by moving to 2D chalcogenides. The atomically thin nature and absence of dangling bonds reduce charge traps and short-channel effects, which together help curb power dissipation53,58,64,92,177,178,179,180. In emergent computing paradigms, such as neuromorphic and quantum computing, device density and low-latency operation are paramount, and 2D chalcogenide materials are well-positioned to meet these requirements113. For instance, transistor and optoelectronic elements with large on/off ratios and floating-gate nonvolatile memory with extraordinary retention times have been demonstrated using ultrathin layers59,101,160,166,181,182,183. Similarly, functionalities based on ferroelectric and exciton-driven photodetection point to applications in integrated compute-sensor-memory systems capable of performing many co-located tasks in parallel113,184,185,186,187. These developments highlight how chalcogenide materials could allow complex information processing to occur directly where data is collected, fundamentally improving bandwidth, latency, and energy consumption.

Still, significant obstacles remain. The surface sensitivity of 2D materials necessitates advanced interface engineering so that gate dielectrics, metal contacts, and protective encapsulation layers do not introduce extrinsic defects or compromise their crystalline integrity. Equally pressing is the need for consistent, wafer-scale growth of chalcogenides with precisely controlled layer numbers. Although chemical vapor deposition (CVD) techniques have produced impressive monolayer crystals, controlling layer thickness across large areas remains challenging. Alternatives such as molecular beam epitaxy (MBE) and atomic layer deposition (ALD) combined with atomic layer etching (ALE) offer promising paths for achieving layer-by-layer control in a manner that integrates smoothly with existing CMOS infrastructure113,188,189,190,191,192. Recent review articles offer comprehensive assessments of chalcogenide synthesis methods, which fall outside the scope of this article139,151,165,186,192,193,194,195,196,197. Beyond wafer-scale synthesis, doping and defect engineering require a more systematic approach that correlates processing conditions with the resulting fundamental device characteristics, especially for quantum and neuromorphic applications, where localized defects can be both detrimental and potentially beneficial depending on their role in electron or spin transport.

Here, our aim is to draw attention to the critical challenges and research opportunities in bridging fundamental chalcogenide quantum material research and practical device technologies. We first examine the central hurdles in interfacial materials physics, including the formation of clean, reliable interfaces, contacts, and the management of defects. We then discuss current emerging nanofabrication strategies and the opportunities they present for scalable manufacturing, highlighting both successes and open questions in harnessing chalcogenides for spintronics, optoelectronics, and quantum information science. Our goal is not to provide an exhaustive survey, but to illustrate the breadth and novel behaviors of chalcogenide materials as they are transformed into functional devices. By illuminating these interconnected challenges, we aim to reveal research opportunities needed to accelerate the realization chalcogenide-based technologies. Ultimately, a concerted effort to refine growth processes, improve device architectures, and develop robust transfer and integration methods is necessary to realize the potential of these unique quantum materials. By systematically tackling these issues, we may unlock entirely new frontiers in computing and sensing, transcending the charge-based paradigm that has underpinned Moore’s law, and ushering in an era where spin, light, and topology become essential resources for technological advancement.

Materials interfaces—challenges and opportunities

In his 2000 Nobel lecture, Herbert Kroemer famously stated that “the interface is the device,” highlighting that the performance of semiconductor heterojunctions is often determined more by the properties of the interface than by the bulk198. This concept, dating back to the 1950s, revolutionized electronics and optoelectronics by enabling band-gap engineering in heterojunction transistors, semiconductor lasers, and advanced integrated circuits. This perspective remains highly relevant, particularly as we explore novel chalcogenide quantum materials. These materials can host a variety of exotic electronic and magnetic states, yet they present a new set of material science challenges for device fabrication. Among these challenges are understanding and controlling the interfacial structure, cross-interface coupling, and material diffusion. Below, we discuss each of these aspects, highlighting recent insights and open questions in chalcogenide-based heterostructures.

Interfacial structure

Chalcogenides such as the transition-metal dichalcogenides (e.g., NbSe2, TiSe2) and tetradymite topological insulators (e.g., Bi2Te3, Bi2Se3) can form a variety of interface structures when layered together or when integrated with other materials. In traditional semiconductors, small lattice mismatches or differences in atomic arrangements at interfaces can cause defects, reconstructions, or strain that modifies electronic transport199,200,201,202. With chalcogenides, these effects can be even more pronounced. In many cases, the interlayer van der Waals forces relax lattice matching conditions, which suggests promising routes towards tailored device structures94,149,150. However, interfaces between atomically similar chalcogenide materials may undergo reconstructions or form interfacial defect layers, whereas interfaces that bridge different symmetries can, at times, be strikingly abrupt. For instance, as shown in Fig. 3, the interface of tetragonal superconducting Fe(Te,Se) grown on hexagonal Bi2Te3 or MnTe can be atomically sharp203,204,205, while the NbSe2/Bi2Se3 interface can exhibit a misfit layer with a distinct structure206. Such subtle differences have profound implications for functionality: the former may preserve high mobility or coupling between quantum states more readily, whereas the latter can create dead layers that may hinder desired proximity effects.

a, b Schematic and cross-sectional scanning transmission electron microscopy (STEM) image of Bi2Se3/monolayer NbSe2 heterostructure on bilayer graphene. A BiSe interfacial layer is formed at the heterojunction. Reproduced, with permission of Springer Nature, from ref. 206. c, d STEM images of Fe(Te,Se)/Bi2Te3 heterostructure. The schematic overlay in (d) highlights the epitaxial interface with no reconstruction. Reproduced, with permission of Wiley, from ref. 205.

These contrasting outcomes reveal a zoology of interface and defect structures, from interfacial phases to reconstructions to well-ordered junctions, and each variant can dramatically alter properties relevant to functional devices. Deeper investigations are required to unravel the mechanisms and energetics governing interfacial structures and to establish clear causal links between interfacial properties and device performance. For example, defects, interfaces, and grain boundaries can be problematic for carrier mobility, magnetic ordering, and excitonic lifetimes critical for neuromorphic applications113, while atomically sharp interfaces between functional layers facilitate long-term data retention in non-volatile floating gate memory devices59. Controlling magnetic dead layers is critical for spin-orbit torque-based magnetic switching in memory devices; however, control over interfacial symmetries can also dramatically improve performance of magnetism-based applications60,207,208. Hence, a key research avenue is understanding how to systematically tune these interface structures in scalable platforms and architectures to functionalize the desired exotic states. The ultimate goal is to trace the causal chain from interfacial structure to materials properties and, ultimately, device performance. However, more systematic studies are needed to discern whether these relationships follow universal rules or are system-specific.

Cross-interface coupling

Once an interface is formed, a second challenge lies in the electronic, magnetic, excitonic, and phononic couplings across the boundary. Charge transfer, band alignment, and the emergence of collective modes are all affected by the local environment at the interface. For example, charge transfer across a MoS2 and WSe2 heterojunction leads to a photoelectric effect with excited excitons controllable by interface engineering92,209, while band alignments can be controlled by chalcogenide stacking configuration and twist angles96,210,211. In addition, work function differences between materials are vital for forming ohmic contacts in device structures140.

For chalcogenides, these interfacial couplings can shape excitonic properties. With strong Coulomb interactions and reduced dielectric screening leading to large exciton binding energies, chalcogenide heterostructures enable room-temperature excitonic devices and high absorption for photodetection and optical devices over a wide range of band gaps13,212,213,214,215,216. When the work functions of adjacent layers differ or the dielectric screening at the interface changes significantly, excitons may localize in specific layers or form strongly bound interlayer complexes217,218,219,220,221,222,223. Tuning these interfacial properties thus provides an additional degree of freedom for quantum sensing and optoelectronic devices.

The cross-interface coupling of different degrees of freedom can lead to exotic states and dramatic enhancement of exotic quantum properties of technological interest. The interface of a topological insulator and even parity superconductor can yield Majorana-bound states, whose non-Abelian statistics and degenerate states topologically protected from local perturbations could be utilized for fault-tolerant quantum computations125,133,224. Another striking example is monolayer FeSe grown on SrTiO3 where charge transfer combined with the interaction between FeSe’s 2D electronic structure and SrTiO3’s high-energy optical phonons enhances the superconducting transition temperature far above its bulk value32,33,225. Similarly, in magnetic topological insulators like MnBi2Te4, the interplay between bulk antiferromagnetic layers, surface topological bands, and termination-dependent magnetization yields unusual hysteresis loops and even-odd layer–dependent axion and Chern insulator phases as well as exchange bias effects in device structures226,227,228,229,230. It has also been shown that the effective thickness in this even-odd dichotomy depends on fabrication processes for device structures231.

The preceding example underscores the remarkable diversity of phenomena that emerge from cross-interface coupling, yet a unified framework for predicting and controlling these effects is still lacking. Advancing the field will require systematic efforts to clarify how cross-interface interactions are governed and how they evolve under different nanofabrication processes.

Diffusion

A final, but equally critical, challenge in building chalcogenide-based heterojunctions is controlling diffusion across interfaces as outlined in Fig. 4. During material synthesis and device fabrication, cross-interface diffusion can degrade or, counterintuitively, enhance properties. Many traditional metals used for contacts in semiconductor device fabrication have been observed to chemically react and diffuse into chalcogenide materials232. Such diffusion can also be used to influence spin-orbit torques for manipulation of magnetic layers233. The van der Waals nature of this class of materials yields highly anisotropic diffusion pathways that can affect the material phases and resulting contact resistance234,235. Taking advantage of these anisotropic pathways may open an avenue for creating phase-engineered interfaces with tailored contact resistances236.

a Low-magnification STEM image of BixSb2-xTe3 (BST)/NiM/Ni interface where M denotes mixture of Bi, Sb, and Te. b Energy Dispersive Spectra (EDS) maps showing distribution of Bi, Sb, Te, and Ni at the interface. c Atomic-resolution STEM image of the interface for the dashed box in (a). Reproduced, with permission of ACS, from ref. 235. d Low-magnification STEM image of Pd/xPBT/Bi2Te3 heterostructure grown on a Si(111) substrate where xPBT is a Pd diffusion induced intermediate Pd1+x(Bi0.4Te0.2)2 phase. Reproduced, with permission of ACS, from ref. 238. Figure showing interlayer diffusion. e, f Synthesis of TiSe2 on TiO2 substrate by the diffusion of Ti. e Scanning Tunneling Microscopy (STM) image showing the surface atomic structure of TiSe2. f The Fermi surface of TiSe2 grown on TiO2 as shown by Angle Resolved Photoemission Spectroscopy (ARPES). Reproduced, with permission of IOP, from ref. 243. The TiSe2 atomic and electronic structure is the same as cleaved bulk TiSe2 crystals except for a shift of the Fermi level due to charge transfer between the film and the substrate.

However, the cross-interface diffusion of materials can also generate new materials, properties, or alter functionality of devices. For example, as shown in Fig. 4d, diffusion of Pd into (Bi,Sb)2Te3 may induce a topological superconducting phase potentially relevant for the creation of Majorana zero modes and quantum computing applications237,238. Similarly, the diffusion of Te across the Fe(Te,Se)/Bi2Te3 boundary can enhance superconductivity of the heterostructure, potentially making Majorana zero modes more accessible for device applications205. On the other hand, unintentional diffusion may introduce impurities or adatom defects that trap charge and act as scattering centers known to degrade carrier mobility134,142,167,177,239,240,241,242.

An extreme illustration of the impact of diffusion is the growth of TiSe2 by simply evaporating Se onto a heated TiO2 substrate, as shown in Fig. 4e, f. The Ti effectively migrates out of the oxide layer, forming a chalcogenide film with the same atomic and electronic structure as bulk TiSe2243. These examples underscore the double-edged nature of diffusion: it can be harnessed for device engineering but must be precisely understood and regulated. Going forward, systematic studies of diffusion pathways, barrier materials, and controlled doping profiles are crucial for reproducible high-performance and scalable device platforms based on chalcogenide heterojunctions.

Herbert Kroemer’s message continues to hold as we look beyond traditional semiconductor technologies. For chalcogenide quantum materials, the interface remains the core platform where exotic electronic, magnetic, and topological states can emerge, or be quenched. Although our focus centers on interfaces within the active chalcogenide layers, the same issues extend to encapsulation and passivation layers. Researchers commonly use materials as Se, Te, FeTe, AlOx, h-BN, Al2O3, etc., as provisional capping layers for materials characterization and device structures244,245,246,247. However, systematic efforts to engineer passivation layers that both safeguard key properties and remain compatible with device fabrication are underdeveloped.

To harness the diverse properties of chalcogenides, the interfacial structure, cross-interface coupling, and diffusion must be mastered to develop next-generation devices. With continued effort, these avenues will pave the way to breakthroughs in novel topological electronics, spintronic, and optoelectronic architectures that extend beyond the boundaries of Moore’s law for next-generation quantum technologies.

Device fabrication—challenges and opportunities

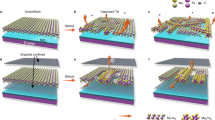

As discussed, chalcogenide materials exhibit exotic quantum properties with tremendous potential for use-inspired applications. Beyond understanding and controlling material interfaces, it is crucial to address the practical realities of integrating these sensitive quantum systems into scalable device architectures. While device fabrication is commonly viewed as an engineering task, many of the fundamental scientific principles underlying fabrication approaches for novel quantum materials remain unknown and underexplored. Significant questions regarding behavior of sensitive materials to energetic physical and chemical processing during nanofabrication and integration are of growing concern. Here, and highlighted in Fig. 5, we examine common pitfalls arising when traditional fabrication techniques are applied to low-dimensional chalcogenides, alongside mitigation strategies and novel approaches for translating the promise of exotic quantum states into scalable quantum technologies. For quick reference, a practical guide to common issues and possible solutions for each nanofabrication technique discussed below is presented in the Supplemental Information.

a Overview of the workflow from thin film to device prototype. b Schematic illustrating the post-lithography state, where thin layers of photoresist residue remain after development. c Schematics comparing dry etching (left) and wet etching (center). Wet etching produces an undercut, whose extent varies among different material layers. Scanning Electron Microscope (SEM) images (right) show an example where the color contrast is due to an undercut around the device edge. d SEM images of a successful (left) and an unsuccessful (right) prototype fabricated under near identical conditions. The hypersensitivity of chalcogenide materials demands careful processing to avoid unwanted chemical reactions. e Schematic of the lift-off process comparing two resist configurations: a bilayer (left) and a single-layer (right). In the bilayer configuration, differing development rates create an overhang that causes the metal layer to break at the top, enabling a cleaner lift-off. By contrast, a continuous metal film in the single-layer approach can inadvertently lift off with the resist, risking unwanted metal removal.

Lithography

In today’s device fabrication, e-beam and optical lithography are crucial for defining device features as outlined in Fig. 5a. Polymer resists (e.g., PMMA, EL, AZ, SPR) are coated onto substrates, baked (e.g., at 90 °C–200 °C), exposed, developed, rinsed, and dried, with optional post-exposure or hard bakes as needed. The resulting photoresist pattern then serves as a mask for subsequent processing. Applying these methods to chalcogenides requires careful consideration, as repeated exposure to aqueous developers (e.g., 2–3% TMAH) and organic solvents, alongside multiple heating/cooling cycles, can cause thermal degradation or introduce residual stress. Moreover, as shown in Fig. 5b, widely used e-beam and optical resists often leave organic residue that can impede lift-off, degrade surface characterization, and introduce non-uniform charges at metal–sample interfaces248. This residue can unintentionally dope materials and reduce mobility249,250, create trap states that lower photocurrent251, and block key phenomena in low-dimensional systems252. Although PMMA generally leaves less residue, complete removal remains difficult; time-of-flight secondary ion mass spectrometry confirms its persistent presence on 2D materials253.

A critical step in both photolithography and electron-beam lithography is the resist pre-bake. Photolithographic resists are usually baked near 100 °C, whereas standard e-beam resists require ≈180 °C. This bake removes residual solvent, anisole in the case of PMMA, before exposure. Solvent trapped during development blurs feature edges and limits aspect ratio, so the benefit of an effective bake increases as the critical dimension shrinks.

Chalcogenide materials, however, are unusually temperature-sensitive. Even moderate baking (~100 °C) accelerates chalcogen loss because of their high vapor pressures, and brief excursions to ≈200 °C can oxidize the chalcogen species. During molecular-beam epitaxy, practitioners compensate for this volatility by providing an excess chalcogen flux194,254; during pre-bake, by contrast, the same volatility drives chalcogen loss, creating vacancies and other defects255. For 2D chalcogenides, the effect is amplified at nanoscale dimensions, where vacancy formation quickly pushes the film off-stoichiometry195,256,257,258,259,260,261. These defects degrade the electronic and quantum properties of many chalcogen-based materials, including topological insulators, lowering carrier mobility, destabilizing phases, and reducing Hall mobility262,263.

Consequences are still more severe for chalcogenide superconductors such as Fe(Te, Se): off-stoichiometry introduced during resist baking can suppress the critical temperature or quench superconductivity altogether by introducing percolative normal-resistance paths264,265. Mitigation strategies, therefore, focus on minimizing thermal load—lowering bake temperature and time, omitting the bake entirely, or performing it in an inert atmosphere to eliminate oxidation. These approaches preserve chemical integrity at the expense of lithographic fidelity, often yielding blunter sidewalls. Ultra-thin chalcogenide films are especially vulnerable, whereas non-chalcogenide quantum-material platforms generally tolerate the modest heat budgets typical of resist baking.

Thermal annealing above 300 °C in argon, hydrogen, forming gas, or vacuum266,267,268 is widely used for residue removal. However, many chalcogenides degrade at this temperature, which is above their synthesis temperature, and annealing alone may not suffice253,266. Elevated temperatures can also introduce defects, unintentional doping, and oxidation; vacuum annealing may boost carrier mobility but risk generating amorphous carbon and additional defects269,270. In sulfide-based chalcogenides, annealing frequently induces sulfur vacancies271,272. Plasma treatments and wet cleaning with heated solvents have proven effective in traditional semiconductors273,274,275,276,277,278, but reactive plasma often introduces defects in 2D metal chalcogenides279. Alternatives such as contact atomic force microscopy (C-AFM)249,280, electron beam treatment281, and light-based treatments282 have shown promise for MoS2, WSe2, and graphene, though broader validation is needed for other low-dimensional systems. Ultimately, residue removal must balance cleaning efficacy with minimal damage, especially critical for chalcogenides prone to oxidation and thermal degradation. As lithographic techniques dominate device foundries, systematic study of these approaches in chalcogenides remains a vital yet underexplored need.

Wet etching

Wet etching is performed by immersing the sample in a reactive solution that dissolves or vaporizes by-products, making it one of the most straightforward and economical methods for material removal. This process can create complex structures unattainable by other etching techniques, particularly those requiring controlled under-etching for suspended patterns283,284. Another major advantage is its high selectivity: carefully formulated and optimized acids, bases, or mixtures can remove a specific layer in a multilayer stack without affecting other layers.

As shown in Fig. 5c, principal drawback is that wet etching is often isotropic, leading to significant undercutting below the mask285. This undercut can be exacerbated when the mask lifts slightly near the feature opening. Although pre- and post-baking of resists, judicious etchant selection, and fine-tuned process parameters can mitigate undercutting, it cannot be entirely avoided, making wet etching more suitable for larger features. Another key parameter is the etch rate, which can be controlled by optimizing the etchant concentration or solution temperature to improve precision.

Wet-chemical etching is a standard route for patterning layered chalcogenide films such as Bi₂Se₃, Bi₂Te₃, (Bi,Sb)Te, and (Bi,Sb)(Te,Se)286,287,288,289. These compounds, celebrated as topological insulators, have enabled a decade of device studies aimed at dissipation-free spintronics that exploit spin–momentum locking. Common mineral acids, HCl, HNO₃, H₂SO₄, and HF, readily etch the films, yet when used full-strength, they attack so aggressively that severe undercutting is routine. Diluting the acid with H₂O₂, de-ionized H₂O, or mild organic acids lengthens the etch time and sharply reduces undercut formation.

Mercury-based chalcogenides pose different chemistry. HgTe thin films, for example, are etched with a KI/I₂/HBr mixture diluted in water; the I₂ concentration sets the etch rate290,291. Magnetically doped topological-insulator films are often processed in a gentler bath of H₃PO₄/H₂O₂/H₂O, which gives a more controllable, intermediate rate.

Photoresist or e-beam resist generally serves as the etch mask and yields well-defined features. When still tighter control is required, a hard mask such as ALD-grown Al₂O₃ can be substituted; the hard mask is then removed in a separate, selective step292. Although effective at suppressing undercutting, this option lengthens the process flow.

Highly anisotropic, hexagon-edged etches have been demonstrated on transition-metal dichalcogenides (WS₂, MoS₂, MoSe₂) using a NH₄OH/H₂O₂/H₂O solution293,294. Patterning of Bi₂Te₃/FeTe heterostructures, candidate topological superconductors, has been achieved with an HCl/H₃PO₄/H₂O mixture295.

If the etch proceeds too slowly, a modest temperature rise (≈60–70 °C) can accelerate the reaction without inducing excessive undercutting. Post-baking the resist likewise suppresses under-cutting by hardening the mask, but any thermal step must be used judiciously for chalcogenides, where heat promotes chalcogen loss and sample degradation.

Perhaps the greatest virtue of wet etching is its chemical selectivity: properly chosen chemistries can remove a chalcogenide layer cleanly while leaving neighboring non-chalcogenide layers untouched, enabling sophisticated heterostructure devices with minimal collateral damage. However, more efforts are needed to understand chalcogen-specific etching chemistries.

Despite these challenges, wet etching remains a vital technique due to its simplicity, cost-effectiveness, and high selectivity. By selecting appropriate etchants, refining process conditions, and employing robust masking strategies, it can be successfully applied to numerous fabrication scenarios. As shown in Fig. 5d, to unleash the power of chalcogenide materials, suitable wet etching chemistries are indispensable and need further investigation. Fundamental chemistry and materials science investigations of etchants to improve chalcogenide selectivity while maintaining compatibility with traditional semiconducting material processes remain a critical gap.

Reactive ion etching

Reactive ion etching (RIE) is a plasma-based technique used to pattern materials during micro- and nanofabrication. Reactive ions generated in a plasma physically sputter or chemically react with select materials, forming volatile byproducts. The degree of directionality (anisotropic vs. isotropic) and selectivity is influenced by chamber pressure, gas flow rates, gas choice, and temperature.

Reactive-ion etching (RIE) of chalcogenide films is typically carried out with fluorine- or chlorine-based plasmas; common feed gases are SF₆, CHF₃, Cl₂, and BCl₃296,297,298,299,300. Etching proceeds through the strong chemical affinity of F⁻ and Cl⁻ radicals for the constituent elements. Layered transition-metal dichalcogenides (MoS₂, MoSe₂, WS₂, WSe₂) and topological chalcogenides (Bi₂Se₃, Bi₂Te₃, MnBi₂Te₄, WTe₂) are readily patterned in an SF₆ plasma. Raising the RF power accelerates removal of thick films, but at the cost of enhanced chalcogen volatility, which can degrade device performance. A standard workaround is to admix a small fraction of Ar (≈1:10 Ar:F/Cl gas). The heavier Ar⁺ ions provide a complementary physical sputter component, dislodging surface atoms while the F/Cl species perform the chemical step; the combined mechanism shortens the required plasma exposure and limits thermal damage.

Poor selectivity is the principal limitation of RIE. Halogen plasmas etch most materials, including gate dielectrics and metals, albeit at different rates, so precise knowledge of those rates is essential. They can vary with chamber geometry, pressure, and power density, meaning each tool must be calibrated individually. When chalcogenide heterostructures are involved, practitioners often lower the etch rate to achieve a clean stop at the intended interface; yet the slower recipe increases the risk of over-etching and roughening adjacent layers. In this respect, RIE contrasts with wet-chemical methods, where the reaction ceases automatically once the targeted layer is removed, preserving the underlying stack in chalcogenide devices.

RIE of chalcogenides can be problematic because these materials are highly sensitive to damage and contamination. Ion bombardment can break bonds, resulting in defects, amorphization, and stoichiometry changes—particularly in transition metal chalcogenides, where lighter atoms may be preferentially sputtered260,301,302,303. This can be particularly problematic for devices where the “cut” edge of the material forms the active device region. Residual ions and etch byproducts (e.g., reactive F or Cl species) can introduce unwanted dopants and alter intrinsic properties. As a solution, one can rinse with a wet-etchant to remove byproducts produced during the RIE process. Importantly, the wet-etchant must be dilute enough so that it does not cause undercutting as discussed in the previous section. The choice of masking materials is also critical for minimizing damage.

RIE is highly energetic, it can cause thermal damage to low-melting-point materials or generate additional defects at elevated temperatures. Although studies RIE-induced defects in Bi2Se3, Ge2Sb2Te5, WSe2, and MoSe2 exist303,304,305, there is a pressing need for more systematic investigations to fully understand the implications of these defects at the device-level304.

Defect formation is best curbed by running the plasma at lower RF power. With reduced power, the ions strike the surface with less energy, generating less Joule heating and thereby preserving film stoichiometry, suppressing RIE-induced defects, and minimizing roughening of underlying layers. Actively cooling the substrate stage, typically with a liquid-nitrogen loop or chilled water, adds a further thermal buffer. These precautions are especially critical for chalcogenide films, whose weak bonding leaves them highly vulnerable to heat-driven damage.

Moreover, RIE can affect underlying layers when overetching is required to ensure complete removal of the target layer. Such overetching often exposes the layer beneath to roughening, contamination, or other modifications.

Alternatives to conventional RIE include chemical etching, low-power chemically selective RIE, and ALE306,307,308. The choice of masking materials is also critical for minimizing damage. ALE, like ALD, involves cyclical exposure of the material to a reactive precursor (which modifies the surface), followed by the removal of that modified surface using low-energy ions or thermal energy, one atomic layer at a time. Although it can be time-consuming, ALE is ideal for atomically thin dichalcogenide materials because it reduces unwanted damage and preserves underlying layers. Although ALD has been well-established for some time, the application of ALE specifically to chalcogenides is a more recent development. ALE has been shown to be more effective than RIE for etching materials such as MoS₂ and WSe₂, achieving precise etching with minimal defect formation and surface roughness. It is important to note that when utilizing ALE, the temperature of the sample holder should be kept as low as possible, as elevated ambient temperatures (typically above ~80°C) are generally required to facilitate reactions within the ALE chamber. Recent reviews highlight the breadth of materials processed by ALE309, but further investigation is needed for reliable and scalable chalcogenide processing.

Focused ion beam milling and direct write processing

Focused ion beam (FIB) milling is a versatile technique for nanofabrication, modification, and characterization at the nanoscale. Ion beams are formed by extracting ions from an ion source (e.g., generated by plasma, field evaporation of liquid metal, or gas field ionization), which are subsequently accelerated (commonly 200 V–50 kV) and electrostatically focused into a nanoscale probe that is scanned deterministically across the sample310. The key advantage of FIB is that ions can transfer energy via elastic collisions, displacing or sputtering target atoms or implanting ion species, thereby altering the topography, structure, and chemistry of the target, without requiring the resists or etchants used in photo/e-beam lithography. As such, the so-called direct-write FIB process is particularly attractive for patterning environmentally and process-sensitive materials such as metal chalcogenides. Moreover, this approach greatly reduces contamination from organic residues. However, the high ion energies generate collision cascades in the target material, leading to damage and amorphization that can extend well beyond the beam’s incidence point. The extent of this delocalization and damage depends on factors such as the target material, ion species, ion energy, and incidence angle311.

Conversely, introducing defects during FIB irradiation can be detrimental, sometimes outweighing the advantages it offers over standard lithographic approaches. High-energy ions generate vacancies, interstitials, and even amorphous tracks in the target lattice312. In Pb-based chalcogenides, the beam can trigger local phase transformations in the material surrounding the impact zone313. Irradiation also produces intense, localized heating; because chalcogenide bonds are comparatively weak, these thermal spikes can exceed the bonding energy, sever bonds, and dramatically degrade electrical properties314. The resulting defect cascades and redeposited material can spread laterally over tens of micrometers, undermining neighboring regions and complicating the fabrication of micron-scale chalcogenide devices315,316,317. The risk is especially acute for chalcogenide superconductors: damage propagated by the beam tail or by sputtered ions reacting with residual gas can irreversibly suppress superconductivity in areas far beyond the intended write zone. Such is the case for FIB processing of chalcogenide thin film materials, as shown in Fig. 6. Direct milling of 10 nm Fe(Te,Se)/50 nm Bi₂Te₃ microstructures with Xe⁺ ions at high current (2 µA) destroyed superconductivity—likely due to sidewall damage and beam-induced amorphization propagating across a 10 µm-wide channel.

Thus, one needs to optimize the beam species as well. Ga⁺ beams have long been used to create planar Josephson junctions and superconducting quantum interference devices318,319,320,321,322. Plasma FIB (PFIB) systems further increase throughput by removing larger volumes more rapidly, while also offering the flexibility to select an ion species and mass that optimize elastic collisions with noble gas ions (Xe⁺, Ar⁺) or introduce inelastic processes through reactive species (O⁺, N⁺). High-resolution gas field ionization provides high brightness and resolution with lighter ions (He⁺, Ne⁺), enabling sub-10 nm patterning resolutions with inert species and reduced ballistic damage323,324. However, even these lighter ions can cause implantation, defect formation, and surface roughness, thereby affecting crystallinity, electrical properties, and magnetization (e.g., via domain wall pinning)325. Nonetheless, the impact of ion-induced defects is context-dependent: recent years have seen growing interest in defect engineering via the spatial precision and controlled defect introduction possible with FIB, particularly with He⁺ ions326,327. Low-temperature post-annealing can be effective in healing some of the defects caused by ion irradiation. Another critical strategy is to minimize the beam energy and current during irradiation. Utilizing low beam currents, such as around 10 pA, and lower voltages (approximately 20–30 kV) has been shown to cause minimal or even negligible damage to chalcogenide-based topological insulators. It is advisable to begin with a higher beam current and energy for initial etching, which allows for the efficient removal of larger portions of the material and reduces overall thinning time. As the process approaches the final device channel, both the beam energy and current should be significantly lowered (to around a few pA and approximately 5 kV) to minimize damage.

Whether the goal is to introduce defects or to avoid them, a deeper understanding and better predictability of the effects of ion species, energy, reactivity, flux, fluence, and reactive precursor gases are essential moving forward.

Electrical contacts

Electrical contact regulates charge flow from the metal electrode to the device channel. Contact resistance arises at the interface of dissimilar materials, stemming from energy-band discontinuities that disrupt charge transport144. To maximize device performance and minimize contact resistance, there are two important factors: (1) doping mismatch, where substantial differences in doping levels raise contact resistance; and (2) contact area, where a smaller area can induce “current crowding.” The current crowding effect can be significantly mitigated through the edge contact method. In this approach, the transition metal dichalcogenide (TMD) is first coated with an insulating layer, followed by a patterned etching step that exposes the edges of the layered structure for metal contacts. This edge contact configuration allows charge carriers to flow laterally into each layer of the chalcogenide, facilitating smaller device sizes. Consequently, this scaling down enhances device density, an essential factor for industrial scalability. Contact resistance is typically measured using four-probe methods, Kelvin probe, or Transmission Line Models328,329. Metal selection is also crucial. For traditional semiconducting materials, Cr and Ti often form ohmic contacts due to their low work functions and strong adhesion, while Pt and Ni generally create Schottky contacts. For many chalcogenides, these conventional metals may chemically react or diffuse into the material232,234,235. For example, despite its higher work function, Pd often achieves relatively low contact resistance but can also form tellurides and selenides at room temperature and thus alter the work function144,238,330. The peculiar properties necessitate the exploration of new contact materials or alternative approaches such as phase-engineering236. Au is widely regarded as forming an excellent Ohmic contact with chalcogenides compared to other contact metals. However, it is important to note that the adhesion of Au to chalcogenides is relatively poor. Recently, antimony (Sb) has been observed to exhibit extremely low contact resistance when deposited on MoS₂. Additionally, indium (In)/gold (Au) contact has demonstrated minimal contact resistance after annealing at 200 °C on transition metal dichalcogenides (TMDs) such as MoS₂ and WS₂331. These materials show promise as future contact options for ultralow contact resistance electronic devices.

There are several strategies to reduce contact resistance. It has been predicted and experimentally shown that insertion of a single layer of hBN between chalcogenide and metal significantly drops the contact resistance or the Schottky barrier height by reducing the interaction between the metal and the sample. Graphene has been demonstrated to enhance the TMD device performance when it is inserted between MoS2 and Ag contact332. Controlled annealing has been shown to improve the metal-semiconductor adhesion, but must be carefully managed to avoid thermal degradation of chalcogenide materials or harmful interfacial diffusion. Additional methods, such as carbide formation or carefully patterned contacts, further decrease contact resistance with materials like graphene333,334, although again, one must remain aware of chalcogenide stability at elevated temperatures. Another concern is wetting, where metals with high surface energy can form islands rather than continuous films on certain substrates, a challenge partly addressed by selective surface passivation335. Another innovative strategy that has recently emerged is the mechanical transfer of metal pads onto 2D chalcogenides336. In this approach, metal pads are pre-patterned and then transferred onto the chalcogenide layer with the assistance of polymer materials such as PMMA or PDMS. This method has demonstrated a significant reduction in contact resistance by several orders of magnitude.

Contact formation by metal deposition is a critical step in chalcogenide-device fabrication337. Because 2D chalcogenides are only a few atomic layers thick, they are far more vulnerable to process-induced damage than bulk silicon, the mainstay of conventional microelectronics. Sputtering and electron-beam (e-beam) evaporation are the two methods used most often. During e-beam evaporation, the arriving atoms carry ~0.1 eV of kinetic energy, whereas sputtered species arrive with 10–100 eV. The gentler bombardment in e-beam evaporation yields smoother, sharper metal/chalcogenide interfaces with minimal intermixing or interdiffusion, and thus less damage to the underlying crystal. For that reason, e-beam evaporation is generally preferred for layered chalcogenides. Contact quality improves still further when the metal is deposited in an ultrahigh-vacuum environment, which suppresses contamination and oxide formation.

Solid-phase epitaxy is especially relevant to layered chalcogenides, as shown in Fig. 7, where Pd or Pt can react to form superconducting compounds (Pd1-1.1Te, PdTe2, Pd6-7Se, and Pd4Se) with transition temperatures up to about 4K338. Remarkably, these reactions may occur at room temperature or with mild annealing, yielding highly transparent contacts on topological semiconductors—some with Josephson junction transparencies near 0.96237,339,340. Although largely self-limiting, such reactions can still show lateral metal migration up to tens of nanometers, complicating device design.

Ultimately, achieving low contact resistance in advanced materials, quantum or otherwise, requires balancing doping, contact geometry, interface cleanliness, and controlled solid-phase reactions. By managing these variables, it becomes possible to maintain stable, low-resistance interfaces that preserve the intrinsic properties of emerging material systems but require coordinated feedback between materials development and fabrication development.

Lift-off

Lift-off is a common process used for adding materials, selectively, to regions where photoresist has been removed. It is commonly used to pattern metal traces and pads to make electrical contacts across a sample. During lift-off, a material, typically a metal, is deposited across substrates that have been coated with photoresist and lithographically patterned. Following metal deposition, the entire substrate is placed in a chemical bath that removes the photoresist and leaves the deposited material remaining in the areas that were not masked by photoresist. It is a good alternative to etching metals because it prevents the underlying material from being exposed to harsh chemical etchants the higher temperatures, or reactive plasma of a reactive ion etcher. While a potentially gentler alternative to etching, poor lift-off can cause shorts or missing regions, undermining device performance. As schematically shown in Fig. 5e, common issues include residual photoresist under the metal, unintended bridging where metal spans masked and unmasked regions, and poor metal-substrate adhesion, all of which can lead to unwanted detachment330. To prevent these pitfalls, one typically removes resist residue before metal deposition (e.g., via brief etching), employs bilayer resists for undercuts, and roughens the substrate with plasma treatments to enhance adhesion. Brief etching is an effective technique for achieving optimal lift-off during the fabrication process. Typically, O₂ plasma is used to remove residual organic components left over from lithography. However, the use of O₂ plasma is not recommended for chalcogenides, as these materials are highly susceptible to oxidation due to the energetic oxygen ions. Instead, inert gas plasmas, such as argon (Ar) ion plasma, are preferred for this process. It is also crucial to operate at very low power when generating the plasma, and the etching duration should be kept minimal, generally around one minute, to prevent damage to the chalcogenide layers.

Adapting standard fabrication protocols remains critical for developing devices using quantum materials, yet alternative methods can reduce polymer residue. For instance, shadow or stencil lithography can form sub-micrometer contacts without resist341, though precise alignment, potentially achieved via flip-flop chip bonders, is needed for multiple patterning. Another strategy relies on selective adhesion, where metal-coated or SAM-treated (self-assembled monolayer) regions of a quantum material exhibit stronger bonding. Transferring these regions onto patterned substrates, then flipping them to expose pristine surfaces, allows device fabrication with minimal metal and SAM contamination342.

Outlook

Despite the challenges for functionalizing chalcogenide-based materials, recent developments show exciting progress towards scalable technologies. Progress in synthesis methods demonstrates that chalcogenide growth can be engineered at large scale and low temperatures, aligning with the stringent thermal budgets and CMOS processes. MOCVD strategies, for instance, have yielded wafer-scale crystalline films in mere minutes, controlling layer numbers from one to five while maintaining uniformity189,190. Likewise, strain engineering with silicon nitride capping layers has been shown to boost device performance, and the feasibility of solution-processed 2D materials points to future monolithic 3D memory–sensing–computing platforms181,186. Synthesis approaches using graphene or hexagonal boron nitride membranes also suggest novel approaches for synthesizing materials in specific device structures, thus avoiding many fabrication pitfalls268,343. Such achievements highlight the promise of integrating chalcogenides into industrial-scale technologies, but they also underscore the need for precise end-to-end control over defects and interfaces to enhance electronic properties critical for functional quantum devices.

Maintaining quantum properties during processing is critical for quantum technologies, and recent patterning and fabrication innovations have demonstrated fine-tuning quantum device structures. Phase engineering showcases how controlling stoichiometry and crystalline phases can achieve abrupt low-resistance contacts and even superconducting states on demand145,160,236. Photoreactive crosslinkers also show promise for creating patterned device networks without the need for photoresist344. These on-device strategies circumvent the complexities associated with transferring 2D layers between disparate substrates, with the potential for paving the way for more stable, reproducible devices at the atomic scale. Meanwhile, lower-energy electron beam lithography protocols are reducing damage in chalcogenide materials, demonstrating that even delicate quantum materials can be integrated into nanoscale circuits using traditional fabrication tools without compromising their unique electronic states345. Complementary techniques, such as adhesion lithography, further boost yield by capitalizing on differences in interfacial adhesion energies to define device geometries without harsh chemical processes342.

Finally, recent device architecture research underscores the strategic transition from transistor scaling to in-memory computing and other data-intensive paradigms. Large-scale integrated vector–matrix multipliers show that wafer-scale, high-yield arrays of floating-gate field-effect transistors are now within reach, supporting advanced signal processing and neural network applications346. Concurrently, next-generation 2D transistors are approaching theoretical performance limits, hinting at the possibility of ballistic transport, low contact resistance, and quantum effects dominating device operation are on the horizon347. Yet critical gaps remain, e.g., dielectric integration, contact optimization, and wafer-scale uniformity, which hamper the widespread adoption of 2D chalcogenides for high-performance logic and quantum circuits84,348. Overcoming these hurdles will require coordinating end-to-end concerted efforts for understanding how to translate exotic quantum properties into functional devices, ultimately position chalcogenides as a cornerstone of future quantum technologies.

Conclusions

As the impending end to Moore’s law approaches, we must explore paradigms beyond traditional electronics. Two-dimensional chalcogenides, featuring clean van der Waals interfaces, exotic electronic and magnetic phases, and remarkable excitonic and spin-dependent phenomena, offer enhanced performance and new functionalities for quantum, neuromorphic, and photonic applications.

Yet the same qualities that make chalcogenides appealing, such as atomically thin layers, dangling-bond-free interfaces, and strong many-body interactions, render them fragile under traditional fabrication methods. Processes like lithography, wet etching, or ion milling can degrade mobility or quench quantum states, while interface diffusion can be exploited for new functionalities or unintentionally compromise device performance.

Realizing this potential requires a reimagined co-design approach with end-to-end integration of materials growth, interface engineering, patterning, and device architecture to recognize the inherent sensitivity of quantum states across multiple length scales. In the quantum world, defects and environmental conditions can affect desired device functionality in ways different from classical devices using more traditional semiconducting and CMOS material systems. Systematic studies are needed to understand how quantum material property and device functionality are interlinked and how fabrication processes affect this translation. Such endeavors require community-level engagement with collaborations across materials science, engineering, physics, and chemistry to develop scalable workflows that preserve quantum properties.

Ultimately, 2D chalcogenides promise far more than incremental transistor improvements. By harnessing control over spin, light, topology, and excitonic interactions, they enable new classes of devices, from spintronics and valleytronics to fault-tolerant quantum circuits, transcending the limits of classical electronics. However, the entangled nature of quantum systems prohibits a simple separation of synthesis and fabrication processes, and systematic attention from material interfaces, trough integration and prototyping, must be paid for these materials to usher in quantum technologies that can truly move us beyond Moore’s law. Our perspective is that without such a co-design framework, explicitly aimed at closing integration gaps, building a shared empirical basis for process–property–performance correlations, and standardizing reproducible workflows, progress will remain incremental and fragmented. Establishing this framework now, while the field is still in a formative stage, will ensure that lessons learned in one application space (e.g., spintronics) accelerate advances in others (e.g., photonics or quantum information), creating a unified pathway toward scalable, high-impact chalcogenide technologies.

Data availability

The original data generated in this work will be made available upon reasonable request to the corresponding author.

References

Moore, G. E. Cramming more components onto integrated circuits. Electronics 38, 114 (1965).

Rudolph, P. & Jurisch, M. Bulk growth of GaAs: an overview. J. Crys. Growth 198-199, 325–335 (1999).

Bohr, M. The evolution of scaling from the homogeneous era to the heterogeneous era. In Proc.International Electron Devices Meeting 1.1.1–1.1.6 (IEEE, 2011).

Auth, C. et al. A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proc. 2012 Symposium on VLSI Technology (VLSIT), 131–132 (IEEE, 2012).

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat. Electron. 1, 442–450 (2018).

Pop, E., Sinha, S. & Goodson, K. E. Heat generation and transport in nanometer-scale transistors. Proc. IEEE 94, 1587–1601 (2006).

Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Transact. Electron Dev. 59, 1813–1828 (2012).

Frank, D. J. Power-constrained CMOS scaling limits. IBM J. Res. Dev. 46, 235–244 (2002).

Haron, N. Z. & Hamdioui, S. Why is CMOS scaling coming to an END?, In Proc. 2008 3rd International Design and Test Workshop, 98–103 (IEEE, 2008).

Wong, H. & Iwai, H. On the scaling issues and high-κ replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelect. Eng. 83, 1867–1904 (2006).

Frerking, M. A. & Beauchamp, P. M. JPL technology readiness assessment guideline. In Proc. 2016 IEEE Aerospace Conference 1–10 (IEEE, 2016).

Gonçalves Sotelo, G. et al. A review of superconducting fault current limiters compared with other proven technologies. Superconductivity 3, 100018 (2022).

Wilson, N. P., Yao, W., Shan, J. & Xu, X. Excitons and emergent quantum phenomena in stacked 2D semiconductors. Nature 599, 383–392 (2021).

Qiu, D. Y., da Jornada, F. H. & Louie, S. G. Optical spectrum ofMoS2: many-body effects and diversity of exciton states. Phys. Rev. Lett. 111, 216805 (2013).

Ye, Z. et al. Probing excitonic dark states in single-layer tungsten disulphide. Nature 513, 214–218 (2014).

Komsa, H.-P. & Krasheninnikov, A. V. Effects of confinement and environment on the electronic structure and exciton binding energy of MoS2 from first principles. Phys. Rev. B 86, 241201 (2012).

Shimazaki, Y. et al. Strongly correlated electrons and hybrid excitons in a moiré heterostructure. Nature 580, 472–477 (2020).

Qi, R. et al. Thermodynamic behavior of correlated electron-hole fluids in van der Waals heterostructures. Nat. Commun. 14, 8264 (2023).

Weber, B. et al. 2024 roadmap on 2D topological insulators. J. Phys.: Mater. 7, 022501 (2024).

Zhang, H. et al. Topological insulators in Bi2Se3, Bi2Te3 and Sb2Te3 with a single Dirac cone on the surface. Nat. Phys. 5, 438–442 (2009).

Xia, Y. et al. Observation of a large-gap topological-insulator class with a single Dirac cone on the surface. Nat. Phys. 5, 398–402 (2009).

Moore, J. E. The birth of topological insulators. Nature 464, 194–198 (2010).

Gong, C. & Zhang, X. Two-dimensional magnetic crystals and emergent heterostructure devices. Science 363, 706 (2019).

Swamynadhan, M. J. & Ghosh, S. Designing multifunctional two-dimensional layered transition metal phosphorous chalcogenides. Phys. Rev. Mater. 5, 054409 (2021).

Cysne, T. P. et al. Orbital magnetoelectric effect in nanoribbons of transition metal dichalcogenides. Phys. Rev. B 107, 115402 (2023).

Cardenas-Chirivi, G. et al. Room temperature multiferroicity in a transition metal dichalcogenide, npj 2. D Mater. Appl. 7, 54 (2023).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Splendiani, A. et al. Emerging photoluminescence in monolayer MoS2. Nano Lett 10, 1271–1275 (2010).

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotech. 7, 699–712 (2012).

Sangwan, V. K. & Hersam, M. C. Electronic transport in two-dimensional materials. Annu. Rev. of Phys. Chem. 69, 299–325 (2018).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Wang, Q.-Y. et al. Interface-induced high-temperature superconductivity in single unit-cell FeSe films on SrTiO3. Chin. Phys. Lett. 29, 037402 (2012).

Lee, J. J. et al. Interfacial mode coupling as the origin of the enhancement of Tc in FeSe films on SrTiO3. Nature 515, 245–248 (2014).

Moore, R. G. et al. Monolayer superconductivity and tunable topological electronic structure at the Fe(Te,Se)/Bi2Te3 interface. Adv. Mater. 35, 2210940 (2023).

Ugeda, M. M. et al. Characterization of collective ground states in single-layer NbSe2. Nat. Phys. 12, 92–97 (2015).

Song, T. et al. Unconventional superconducting quantum criticality in monolayer WTe2. Nat. Phys. 20, 269–274 (2024).

O’Hara, D. J. et al. Room temperature intrinsic ferromagnetism in epitaxial manganese selenide films in the monolayer limit. Nano Lett 18, 3125–3131 (2018).

Yu, W. et al. Chemically exfoliated VSe2 monolayers with room-temperature ferromagnetism. Adv. Mater. 31, 1903779 (2019).

Zhang, X. et al. Room-temperature intrinsic ferromagnetism in epitaxial CrTe2 ultrathin films. Nat. Commun. 12, 2492 (2021).

Guan, S., Liu, C., Lu, Y., Yao, Y. & Yang, S. A. Tunable ferroelectricity and anisotropic electric transport in monolayer β-GeSe. Phys. Rev. B 97, 144104 (2018).

Chang, K. et al. Microscopic manipulation of ferroelectric domains in snse monolayers at room temperature. Nano Lett 20, 6590–6597 (2020).

Gao, W. & Chelikowsky, J. R. Prediction of intrinsic ferroelectricity and large piezoelectricity in monolayer arsenic chalcogenides. Nano Lett 20, 8346–8352 (2020).

Higashitarumizu, N. et al. Purely in-plane ferroelectricity in monolayer SnS at room temperature. Nat. Commun. 11, 2428 (2020).

Guo, Y.-D. et al. Sliding ferroelectricity in kagome-B2X3 (X = S, Se, Te) bilayers. Appl. Phys. Lett. 124, 152901 (2024).

Wang, Q. et al. Magnetic and multiferroic properties of two-dimensional FePX3 and CuFeP2X6 (X = S, Se, and Te). ACS Appl. Electron. Mater. 7, 660–666 (2025).

Yue, X. et al. Single-layer MoSeN – a synthetic Janus two-dimensional transition-metal compound grown by plasma-assisted molecular beam epitaxy. 2D Mater. 12, 025004 (2025).

Wang, C., You, L., Cobden, D. & Wang, J. Towards two-dimensional van der Waals ferroelectrics. Nat. Mater. 22, 542–552 (2023).

Zhang, D., Schoenherr, P., Sharma, P. & Seidel, J. Ferroelectric order in van der Waals layered materials. Nat. Rev. Mater. 8, 25–40 (2022).

Gish, J. T., Lebedev, D., Song, T. W., Sangwan, V. K. & Hersam, M. C. Van der Waals opto-spintronics. Nat. Electron. 7, 336–347 (2024).

Podzorov, V., Gershenson, M. E., Kloc, C., Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. Appl. Phys. Lett. 84, 3301–3303 (2004).

Mitzi, D. B., Copel, M. & Chey, S. J. Low-voltage transistor employing a high-mobility spin-coated chalcogenide semiconductor. Adv. Mater. 17, 1285–1289 (2005).

Mitzi, D. B., Copel, M. & Murray, C. E. High-mobility p-type transistor based on a spin-coated metal telluride semiconductor. Adv. Mater. 18, 2448–2452 (2006).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotech. 6, 147–150 (2011).

Kim, S. et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat. Commun. 3, 1038 (2012).

Cheng, R. et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 1038 (2014).

Jadwiszczak, J. et al. Mixed-dimensional 1D/2D van der waals heterojunction diodes and transistors in the atomic limit. ACS Nano 16, 1639–1648 (2022).

Yu, Y. et al. Gate-tunable phase transitions in thin flakes of 1T-TaS2. Nat. Nanotech. 10, 270–276 (2015).

Li, H. M. et al. Metal-semiconductor barrier modulation for high photoresponse in transition metal dichalcogenide field effect transistors. Sci. Rep. 4, 4041 (2014).

Wang, H. et al. Ultrafast non-volatile floating-gate memory based on all-2D materials. Adv. Mater. 36, e2311652 (2024).

Yang, H. et al. Two-dimensional materials prospects for non-volatile spintronic memories. Nature 606, 663–673 (2022).

Gwon, O. H. et al. Systematic design and demonstration of multi-bit generation in layered materials heterostructures floating-gate memory. Adv. Funct. Mater. 31, 2105472 (2021).

Li, D. et al. Two-dimensional non-volatile programmable p–n junctions. Nat. Nanotech. 12, 901–906 (2017).

Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 4, 1624 (2013).

Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano 7, 3246–3252 (2013).

Joo, Y., Hwang, E., Hong, H., Cho, S. & Yang, H. Memory and synaptic devices based on emerging 2D ferroelectricity. Adv. Electron. Mater. 9, 2300211 (2023).

Liu, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotech. 16, 874–881 (2021).

Zhang, B., Lu, P., Tabrizian, R., Feng, P. X. L. & Wu, Y. 2D magnetic heterostructures: spintronics and quantum future. npj Spintronics 2, 6 (2024).

Xie, Z. et al. Orbital-selective spin texture and its manipulation in a topological insulator. Nat. Commun. 5, 3382 (2014).

Rao, Z. et al. Braiding reflectionless states in non-Hermitian magnonics. Nat. Phys. 20, 1904–1911 (2024).

Chumak, A. V., Vasyuchka, V. I., Serga, A. A. & Hillebrands, B. Magnon spintronics. Nat. Phys. 11, 453–461 (2015).

Jo, D., Go, D., Choi, G.-M. & Lee, H.-W. Spintronics meets orbitronics: emergence of orbital angular momentum in solids. npj Spintronics 2, 19 (2024).

Kajale, S. N., Hanna, J., Jang, K. & Sarkar, D. Two-dimensional magnetic materials for spintronic applications. Nano Res. 17, 743–762 (2024).

Lin, X., Yang, W., Wang, K. L. & Zhao, W. Two-dimensional spintronics for low-power electronics. Nat. Electron. 2, 274–283 (2019).

Suzuki, R. et al. Valley-dependent spin polarization in bulk MoS2 with broken inversion symmetry. Nat. Nanotech. 9, 611–617 (2014).

Xiao, D., Liu, G.-B., Feng, W., Xu, X. & Yao, W. Coupled spin and valley physics in monolayers of MoS2 and other group-VI dichalcogenides. Phys. Rev. Lett. 108, 196802 (2012).

Yakout, S. M. Spintronics: future technology for new data storage and communication devices. J. Supercond. Nov. Magn. 33, 2557–2580 (2020).

Dieny, B. et al. Opportunities and challenges for spintronics in the microelectronics industry. Nat. Electron. 3, 446–459 (2020).

Avsar, A. et al. Colloquium: spintronics in graphene and other two-dimensional materials. Rev. Mod. Phys. 92, 021003 (2020).

Ciarrocchi, A., Tagarelli, F., Avsar, A. & Kis, A. Excitonic devices with van der Waals heterostructures: valleytronics meets twistronics. Nat. Rev. Mater. 7, 449–464 (2022).

Mak, K. F., He, K., Shan, J. & Heinz, T. F. Control of valley polarization in monolayer MoS2 by optical helicity. Nat. Nanotech. 7, 494–498 (2012).

Kumar, N., He, J., He, D., Wang, Y. & Zhao, H. Valley and spin dynamics in MoSe2 two-dimensional crystals. Nanoscale 6, 12690–12695 (2014).

Zeng, H., Dai, J., Yao, W., Xiao, D. & Cui, X. Valley polarization in MoS2 monolayers by optical pumping. Nat. Nanotech. 7, 490–493 (2012).

Cao, T. et al. Valley-selective circular dichroism of monolayer molybdenum disulphide. Nat. Commun. 3, 1038 (2012).

Lau, C. S. et al. Dielectrics for two-dimensional transition-metal dichalcogenide applications. ACS Nano 17, 9870–9905 (2023).

Vitale, S. A. et al. Valleytronics: opportunities, challenges, and paths forward. Small 14, 1801483 (2018).

Bussolotti, F. et al. Roadmap on finding chiral valleys: screening 2D materials for valleytronics. Nano Futures 2, 032001 (2018).

Ang, Y. S., Yang, S. A., Zhang, C., Ma, Z. & Ang, L. K. Valleytronics in merging Dirac cones: all-electric-controlled valley filter, valve, and universal reversible logic gate. Phys. Rev. B 96, 245410 (2017).

Schaibley, J. R. et al. Valleytronics in 2D materials. Nat. Rev. Mater. 1, 16055 (2016).

Mak, K. F. & Shan, J. Photonics and optoelectronics of 2D semiconductor transition metal dichalcogenides. Nat. Photon. 10, 216–226 (2016).

Liu, X. & Hersam, M. C. 2D materials for quantum information science. Nat. Rev. Mater. 4, 669–684 (2019).

Xue, H., Yang, Y. & Zhang, B. Topological valley photonics: physics and device applications. Adv. Photonics Res 2, 2100013 (2021).

Dong, Z. et al. Broadband excitonic near-infrared photoresponse at the van der Waals heterostructure/metal interface. ACS Photonics 11, 4209 (2024).

Anantharaman, S. B. et al. Ultrastrong light–matter coupling in two-dimensional metal–organic chalcogenolates. Nat. Photon 19, 322–328 (2025).

Pham, P. V. et al. 2D heterostructures for ubiquitous electronics and optoelectronics: principles, opportunities, and challenges. Chem. Rev. 122, 6514–6613 (2022).

Ponraj, J. S. et al. Photonics and optoelectronics of two-dimensional materials beyond graphene. Nanotechnology 27, 462001 (2016).

Molina-Sánchez, A., Hummer, K. & Wirtz, L. Vibrational and optical properties of MoS2: from monolayer to bulk. Surf. Sci. Rep. 70, 554–586 (2015).

Peng, B., Ang, P. K. & Loh, K. P. Two-dimensional dichalcogenides for light-harvesting applications. Nano Today 10, 128–137 (2015).

Zhou, J. et al. Probing plexciton emission from 2D materials on gold nanotrenches. Nat. Commun. 15, 9583 (2024).

Saini, S. K. et al. Unveiling electric bias effects on ultrafast carrier dynamics in multiple stacked ZnTe/Bi2Te3 heterostructures. J. Phys. Chem. C 128, 11687–11698 (2024).

Pospischil, A. & Mueller, T. Optoelectronic devices based on atomically thin transition metal dichalcogenides. Appl. Sci. 6, 78 (2016).

Rani, A., Verma, A. & Yadav, B. C. Advancements in transition metal dichalcogenides (TMDCs) for self-powered photodetectors: challenges, properties, and functionalization strategies. Mater. Adv. 5, 3535–3562 (2024).

Lee, H. S. et al. MoS2 nanosheet phototransistors with thickness-modulated optical energy gap. Nano Lett. 12, 3695–3700 (2012).

Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotech. 8, 497–501 (2013).

Yu, W. J. et al. Highly efficient gate-tunable photocurrent generation in vertical heterostructures of layered materials. Nat. Nanotech. 8, 952–958 (2013).

Velusamy, D. B. et al. Flexible transition metal dichalcogenide nanosheets for band-selective photodetection. Nat. Commun. 6, 1038 (2015).

Yan, F. et al. Toward high-performance photodetectors based on 2D materials: strategy on methods. Small Methods 2, 1700349 (2018).

Zatko, V. et al. Band-gap landscape engineering in large-scale 2D semiconductor van der waals heterostructures. ACS Nano 15, 7279–7289 (2021).

Huang, L. et al. Enhanced light–matter interaction in two-dimensional transition metal dichalcogenides. Rep. Prog. Phys. 85, 046401 (2022).

Chen, R. et al. Monolayers of germanene/janus Ga2SeTe van der Waals heterostructures by first-principles calculations for high-performance optoelectronic devices. ACS Appl. Nano Mater. 6, 3453–3462 (2023).

Liao, L., Kovalska, E., Regner, J., Song, Q. & Sofer, Z. Two-dimensional van der Waals thin film and device. Small 20, 2303638 (2023).

Wen, Y. & Wu, Z. High-performance photodetectors based on band alignment of type-I Te/WSe2 and type-III Te/ReS2 van der Waals heterostructures. Chem. Phys. Lett. 831, 140849 (2023).

Tang, J. et al. A reliable all-2D materials artificial synapse for high energy-efficient neuromorphic computing. Adv. Funct. Mater. 31, 2011083 (2021).

Hadke, S., Kang, M. A., Sangwan, V. K. & Hersam, M. C. Two-dimensional materials for brain-inspired computing hardware. Chem. Rev. 125, 835–932 (2025).

Liu, K. et al. An optoelectronic synapse based on α-In2Se3 with controllable temporal dynamics for multimode and multiscale reservoir computing. Nat. Electron. 5, 761–773 (2022).

Zhai, Y. et al. Reconfigurable 2D-ferroelectric platform for neuromorphic computing. Appl. Phys. Rev. 10, 011408 (2023).

Sangwan, V. K., Liu, S. E., Trivedi, A. R. & Hersam, M. C. Two-dimensional materials for bio-realistic neuronal computing networks. Matter 5, 4133–4152 (2022).

Yan, X., Qian, J. H., Sangwan, V. K. & Hersam, M. C. Progress and challenges for memtransistors in neuromorphic circuits and systems. Adv. Mater. 34, 2108025 (2022).

Sangwan, V. K. & Hersam, M. C. Neuromorphic nanoelectronic materials. Nat. Nanotech. 15, 517–528 (2020).

Gupta, S. et al. Low power, CMOS-MoS2 memtransistor based neuromorphic hybrid architecture for wake-up systems. Sci. Rep. 9, 15604 (2019).

Soliman, M. et al. Photoferroelectric all-van-der-waals heterostructure for multimode neuromorphic ferroelectric transistors. ACS Appl. Mater. Interfaces 15, 15732–15744 (2023).

Zhang, Z. et al. 2D materials and van der Waals heterojunctions for neuromorphic computing. Neuromorph. Comp. Eng. 2, 032004 (2022).

Ai, L. et al. Van der Waals ferromagnetic Josephson junctions. Nat. Commun. 12, 2650 (2021).

Banerjee, A., Sundaresh, A., Ganesan, R. & Kumar, P. S. A. Signatures of topological superconductivity in bulk-insulating topological insulator BiSbTe1.25Se1.75 in proximity with superconducting NbSe2. ACS Nano 12, 12665–12672 (2018).

Chen, W. et al. Temperature effects on the electronic structures of epitaxial 1T′-WSe2 monolayers. J. Phys. Chem. Lett. 16, 2188–2195 (2025).

Fu, L. & Kane, C. L. Superconducting proximity effect and majorana fermions at the surface of a topological insulator. Phys. Rev. Lett. 100, 096407 (2008).

Li, Y. W. et al. Observation of topological superconductivity in a stoichiometric transition metal dichalcogenide 2M-WS2. Nat. Commun. 12, 2874 (2021).

Mong, R. S. K. et al. Universal topological quantum computation from a superconductor-abelian quantum hall heterostructure. Phys. Rev. X 4, 011036 (2014).

Nayak, C., Simon, S. H., Stern, A., Freedman, M. & Das Sarma, S. Non-Abelian anyons and topological quantum computation. Rev. Mod. Phys. 80, 1083–1159 (2008).

Ren, H. et al. Topological superconductivity in a phase-controlled Josephson junction. Nature 569, 93–98 (2019).

Sarma, S. D., Freedman, M. & Nayak, C. Majorana zero modes and topological quantum computation. npj Quant. Inform. 1, 15001 (2015).

Xu, J.-P. et al. Artificial topological superconductor by the proximity effect. Phys. Rev. Lett. 112, 217001 (2014).

Yuan, Y. et al. Evidence of anisotropic Majorana bound states in 2M-WS2. Nat. Phys. 15, 1046–1051 (2019).

Kitaev, A. Y. Fault-tolerant quantum computation by anyons. Ann. Phys. 303, 2–30 (2003).

Manzeli, S., Ovchinnikov, D., Pasquier, D., Yazyev, O. V. & Kis, A. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2, 17033 (2017).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).