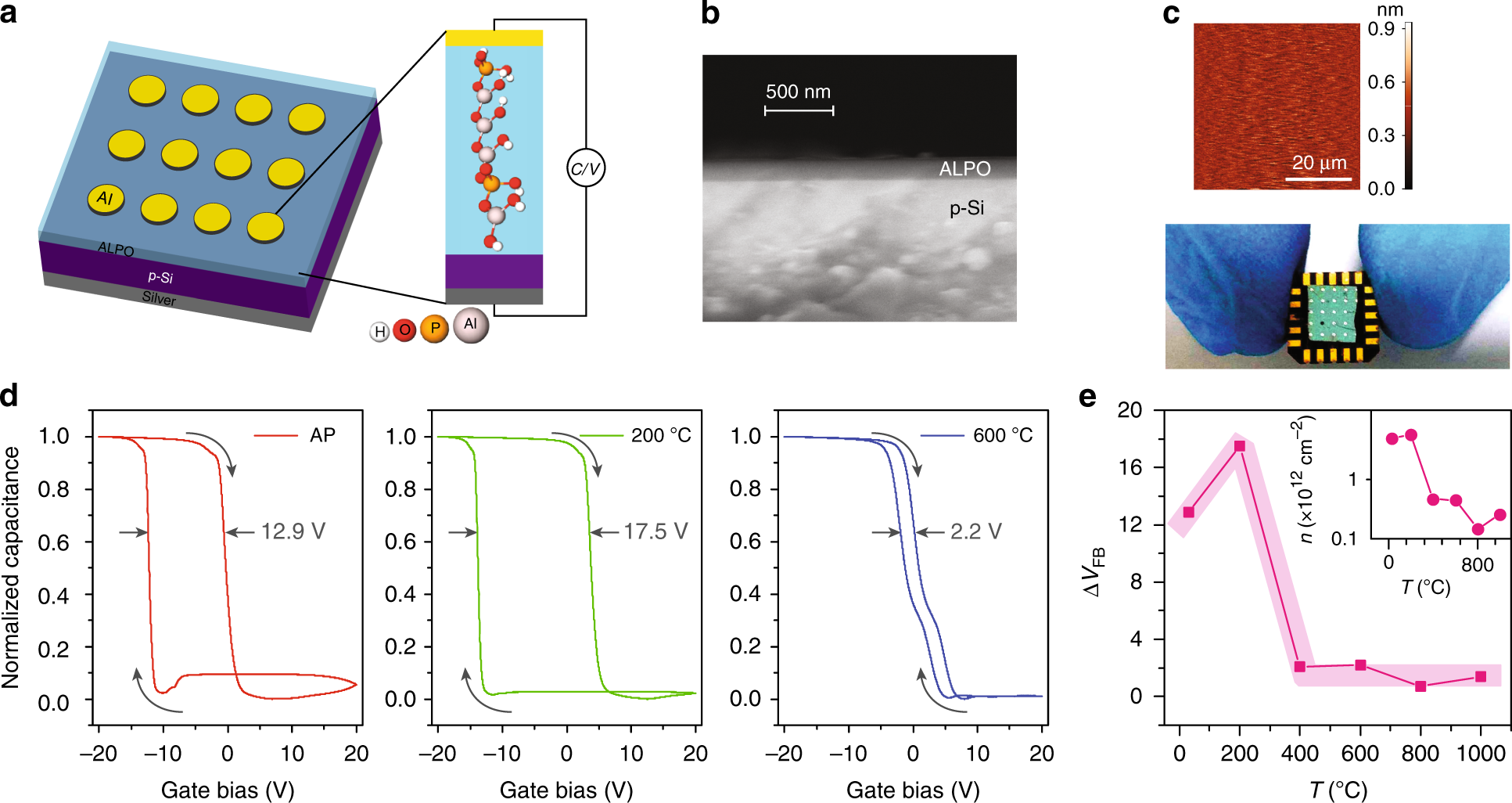

Fig. 1

Device and deep level charge trapping response. a Schematic of device architecture. b Cross-sectional scanning electron microscopy (SEM) image of a typical device (thickness of 139 nm). c (top-panel) Atomic force topography of the surface of the devices. (bottom-panel) Optical image taken with camera of an array of devices. d C–V traces of as prepared (AP), heated at 200 and 600 °C respectively (Supplementary Note 2). The heating was done for 1 h for each sample. C–V was measured with the up-down DC sweep of ±20 V at a rate of 2 V min−1 on the gate (Gate Bias) of the metal-insulator-semiconductor (MIS) while imposing a small AC with amplitude and frequency of 100 mV and 100 kHz, respectively. e Variation of hysteresis window (ΔVFB) as a function of heating temperature. (inset) variation of trap density as a function of heating temperature