Abstract

One of the most promising routes toward scalable quantum computing is a modular approach. We show that distinct surface code patches can be connected in a fault-tolerant manner even in the presence of substantial noise along their connecting interface. We quantify analytically and numerically the combined effect of errors across the interface and bulk. We show that the system can tolerate 14 times higher noise at the interface compared to the bulk, with only a small effect on the code’s threshold and subthreshold behavior, reaching threshold with ~1% bulk errors and ~10% interface errors. This implies that fault-tolerant scaling of error-corrected modular devices is within reach using existing technology.

Similar content being viewed by others

Introduction

Quantum devices made from noisy components require error correction1,2 to scale. Building error-corrected devices involves connecting a large number of qubits with gates of sufficiently high fidelity3. However, due to the general difficulty of controlling ever larger numbers of qubits within a single physical unit, quantum hardware platforms encounter practical system size limits. For example, limits in the range of 102–104 physical qubits are expected for trapped ions (due to spectral crowding of motional modes4), superconducting qubits (due to cryostat size and chip fabrication5), and Rydberg arrays (due to finite laser power and microscope field of view6,7). Because of these size limits, individual quantum processors may soon support multiple logical qubits8,9,10,11,12,13, but still not be truly scalable error-corrected devices.

To scale beyond these limits, one can consider architectures of local modules linked together via a physically distinct mechanism which is generally noisier and slower, e.g., trapped-ion chains connected via entangled photons14. For a quantum computer, such a modular approach reduces the task of achieving true scalability to designing a unit module of fixed qubit number equipped with a fault-tolerant quantum input/output interface, so that scaling simply involves connecting more identical modules. For quantum communication, a similar modular approach is already necessary to move quantum information between processors separated by long distances2.

A major challenge for error-corrected modular architectures is transferring quantum information between modules with sufficient speed and fidelity to satisfy the requirements for fault tolerance. Because inter-module communication channels are typically lossy, quantum communication is accomplished by post-selected entanglement distribution. Entanglement shared between two modules in the form of non-local Bell pairs then serves as a resource to enable teleported gates for inter-module operations15,16,17.

As even the heralded Bell pairs may still be noisy17,18, entanglement distillation has been proposed to convert many low-fidelity pairs into a smaller number of higher-fidelity pairs19. However, simple distillation protocols can only reach errors approximately ten times larger than the local gate errors, because they involve many local gates20,21. More sophisticated protocols are necessary to further reduce the noise, but the added complexity lowers the success rate, reducing the achievable code cycle rate and increasing the memory errors per code cycle18,22,23,24,25,26.

In this article, we show that logical qubits encoded in surface code patches in distinct modules can be fault-tolerantly connected despite substantially elevated noise along their shared interface (see Fig. 1a). While previous work pointed out that fault-tolerant quantum communication between code patches with noisy links is possible in the limit where the local noise in the bulk is asymptotically below threshold27,28, we instead study the code in the presence of noise throughout both the bulk and interface, as in Fig. 3. Developing an understanding of how bulk and interface noise contributions combine to form logical failure modes, we provide analytical bounds and numerical simulations to show that the threshold for interface noise is as high as ~10%, even with bulk noise close to the usual surface code threshold of ~1%. This relaxed threshold for communication errors implies that hardware platforms working toward building surface code patches (superconducting29,30, neutral atoms13,31,32, trapped ions18,33,34,35, solid-state defects36,37,38, and silicon photonics39,40), many already close to realizing local logical qubits8,9,10,11,12,13, only require noisy interconnects to immediately scale without distillation, better local gates, or other time or space overheads.

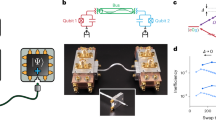

a Communication between surface codes in distinct modules is routed through a cross-connect switch. b A logical gate between two surface code “bulk" patches in separate modules connected along a lower dimensional “seam." Stabilizer checks span the seam with pink teleported gates. Pink data (open circle) and syndrome (filled circle) qubits lying along the interface of the two code patches experience elevated noise levels. \({\hat{X}}_{L},{\hat{Z}}_{L}\) indicate logical string operators.

Results

Modeling the logical qubit interface

The surface code41,42,43,44 is a Calderbank-Shor-Steane (CSS) code with a high circuit-level decoding threshold of \({p}_{{{{\rm{bulk}}}}}^{* }\approx\) 1%3. In Fig. 1 for an L × L surface code, the 4-body parity check operators Z⊗4 and X⊗4, each realized by local CNOT gates between a syndrome qubit and four nearby data qubits, are indicated by the four green or yellow leaves associated with each syndrome qubit. The logical Pauli operators are strings of X and Z Pauli operators along the vertical and horizontal directions of the surface code, respectively.

Various methods exist to perform fault-tolerant two-qubit gates between surface code patches in separate modules. These include lattice surgery45, braiding3, or even directly moving logical qubits between modules, but all reduce to maintaining a surface code patch spanning the two modules. For logical computation across modules, it then suffices to connect the edges of two distinct surface code patches and perform parity checks spanning the modules which merge the two patches into a single larger surface code straddling the modules45. As shown in Fig. 1b, along the interface or “seam" where the two code patches connect, one leaf from each check stretches between the code patches, indicating a (pink) CNOT gate between a syndrome qubit and a data qubit in separate modules.

Making contact with methods to realize the inter-module gates (highlighted in pink in Fig. 1b) via gate teleportation, Fig. 2 shows how Bell pair bit and phase flip noise propagates onto the target and control qubits of the teleported gate, respectively. Inspection of Figs. 1b and 2 shows that bit flip noise from the noisy Bell pair propagates to the right of the pink seam, and phase flip noise to the left of the pink seam. As the X and Z errors trigger distinct check operators and because they can be decoded with distinct minimum weight perfect matching (MWPM) decoders44, each decoder sees elevated noise on only a single strip of data+syndrome qubits to the right or left of the pink seam.

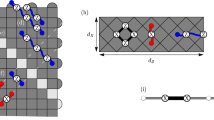

If the syndrome qubits were noiseless, the connecting interface would be equivalent to a 1D repetition code (bit and phase flip noise rates ps) embedded in the 2D surface code (bit and phase flip noise rates pb). To treat syndrome noise, we consider a generic phenomenological noise model where the bulk syndrome noise is set to be equal to the bulk data qubit noise qb = pb44, and similarly for the seam syndrome and data qubit noise qs = ps, since Bell pair noise propagates to both. Noisy syndrome decoding is accomplished through L rounds of syndrome extraction, extending the matching graph along the syndrome qubits into an extra dimension representing time3,44. This results in a Ds = (1 + 1) dimension lattice of size L × L on which errors occur with rate ps embedded in a Db = (2 + 1) dimension lattice of size L × L × L on which errors occur with error rate pb. Using this model of surface code patches, each locally error-corrected in a distinct module with a noisier interface connecting them, we next describe how to analytically model and numerically simulate the logical errors for various choices of L to extract threshold and subthreshold logical logical error behavior. From the extracted threshold behavior, we can determine the conditions under which two error-corrected logical qubits, housed and operating in distinct modules, can be interfaced using a noisy network. We find negligible degradation of fault tolerance even with interface noise 14 × higher than the circuit-level noise present within each module.

Analytical bounds

We now show how the seam, due to its lower dimension than the bulk, can tolerate elevated levels of noise without severely compromising the integrity of the code spanning the modules, even in the presence of noise near the threshold \({p}_{{{{\rm{b}}}}}^{* }\) within the bulk of the code. Intuitively, the threshold of a surface code is determined by both the qubit noise level (the probability to extend a chain along a particular edge) and the number of directions available in which to extend the error chain. In a lower dimension, fewer directions are available in which to extend error chains, resulting in a higher noise threshold. Because Db > Ds, the bulk and seam thresholds \({p}_{{{{\rm{b}}}}}^{* },{p}_{{{{\rm{s}}}}}^{* }\) then satisfy \({p}_{{{{\rm{s}}}}}^{* } > {p}_{{{{\rm{b}}}}}^{* }\).

Next, we consider how the extra seam noise in Fig. 1b affects the probabilities for \({\hat{X}}_{L}\) and \({\hat{Z}}_{L}\) logical errors. Since logical \({\hat{X}}_{L}\) errors can occur both in the bulk and along the seam, suppressing them requires both seam noise below seam threshold, \({p}_{{{{\rm{s}}}}} < {p}_{{{{\rm{s}}}}}^{* }\), and bulk noise below bulk threshold, \({p}_{{{{\rm{b}}}}} < {p}_{{{{\rm{b}}}}}^{* }\). This is the most stringent case and considered in Fig. 4 and the remainder of the paper. In contrast, even for \({p}_{{{{\rm{s}}}}} > {p}_{{{{\rm{s}}}}}^{* }\), a \({\hat{Z}}_{L}\) error still must penetrate the length of the bulk and can be suppressed so long as the bulk is below threshold. For equal data and syndrome qubit noise as we consider (qb = pb and qs = ps), the probability of generating “time-like" error chains stretching through the L rounds of error correction for both the bit and phase flip decoders is identical to that for \({\hat{X}}_{L}\). Thus, Fig. 4 also shows the probability for time-like bit and phase flip error chains spanning L rounds. However, once the threshold criteria from Fig. 4 are reached, these are easily suppressed by extending the code further in the time direction with more rounds of error correction per logical gate.

Now, in order for a logical bit flip error to occur, the combined effect of a round of errors and corrections must generate some nontrivial chain of bit flips {γ} of length at least L (see Fig. 3). For a single code patch with no seam, using the combinatoric path-counting approach from ref. 44, and also reviewed in refs. 46,47,48 and Supplementary Note 1, the logical failure probability Pfail is bounded by the number of such possible chains nnontrivial(L) times the probability for each to occur:

Here, the probability bound of 2LpL/2 originates from how MWPM fills in the rest of a nontrivial chain once L/2 bits flip due to environmental noise, and there being ≤2L ways to choose half or more of the L bits to have flipped. To express a bound on nnontrivial(L), consider how when appending each additional edge to {γ}, one can move in any direction on the lattice other than back, so in 2D − 1 directions in dimension D, bounding \({n}_{{{{\rm{nontrivial}}}}}(l)\le {(2D-1)}^{l}\equiv {\mu }_{D}^{l}\). We can then rewrite:

which is exponentially suppressed to zero as L → ∞ for p < p*. As μD is dimension dependent, so is the threshold bound \({p}^{* }\equiv 1/(4{\mu }_{D}^{2})\).

Edges are data qubits and vertices are check operators. Each X is a bit flip error due to the environment, and each dashed segment is a bit flip after decoding to return the logical qubit to the code space. In this example, if only the red seam bit flips occurred (and the bulk was error free pb = 0), we could successfully correct the qubit. However, with pb > 0 blue errors in the bulk can also occur and a logical error path then forms (green highlight) through this “excursion", {γB}, into the bulk. Imagining the logical error path growing from the bottom to the top, the small orange arrows indicate the different directions available to choose when hopping off/on the seam to create an excursion.

In Supplementary Note 1, we extend the techniques from ref. 44 to derive bounds (Eqs. (3)–(6)) constraining how the threshold changes in the presence of a noisy seam by counting the number of error chains, which hop between the seam and bulk. Here, we present a heuristic argument reaching the same conclusions and elucidating the failure mechanisms. We can interpret our expression for the logical failure (Eq. (2)) as the factor of \({\mu }_{D}\times 2\sqrt{p}\) for each additional edge appended to {γ} (so a probability of \({({\mu }_{D}\times 2\sqrt{p})}^{L}\) for appending L edges), with μD ways to add edges, and \(2\sqrt{p}\) as an effective “probability" per link (with the factor of 2 and the square root appearing because of how the MWPM procedure fills in missing links). If errors occur solely along the seam with pb = 0, as in Fig. 3a, we would have a factor of \({\mu }_{{{{\rm{s}}}}}\times 2\sqrt{{p}_{{{{\rm{s}}}}}}\) per appended edge. But making pb > 0, we suddenly allow additional paths through the bulk before appending the next seam link, as in Fig. 3, which adds terms corresponding to excursions into the bulk before reattaching to the seam. For a given excursion, in addition to flipping an arbitrary possible number of bulk edges ℓ, each of which can be appended in μb ways for a factor of \({({\mu }_{{{{\rm{b}}}}}\times 2\sqrt{{p}_{{{{\rm{b}}}}}})}^{\ell }\), an excursion also involves flipping two bulk edges orthogonal to the direction along the seam as well as a final seam link when hopping back on to the seam for another factor of \({\mu }_{{{{\rm{c}}}}}\times 2\sqrt{{p}_{{{{\rm{s}}}}}}{(2\sqrt{{p}_{{{{\rm{b}}}}}})}^{2}\). The coefficient μc ≡ 4Ds(Db − Ds), where Ds is the dimension of the seam and Db is the dimension of the bulk, counts the number of ways to choose both how to leave the seam (2(Ds − Db), as this is the number of edges which stick out from the seam into the bulk) and how to reattach to the seam (2Ds, as this is the number of directions one could choose within the seam itself when hopping back onto the seam to finish the excursion). See small orange arrows in Fig. 3 to visualize counting the ways to hop off/on the seam when creating an excursion. See Supplementary Note 1 for more details. By analogy with Eq. (2), we add up all of these ways to attach new seam links, giving us a modified factor containing a geometric series for each seam edge we append:

where in the second line, we have summed the geometric series over ℓ and defined αc ≡ 8μc.

Again by analogy, we would then expect the failure probability bound to be Eq. (3) raised to the power of γS (from Fig. 3, the number of edges in {γ} on the seam). We similarly introduce γB, the number of edges in {γ} in the bulk. Additionally, realizing that if γS < L, there must be at least γB = L − γS bulk links in {γ}, as {γ} must have at least L total links in order to fail, we arrive at:

The first two terms correspond to failure chains within purely the seam or bulk, and the additional cross terms apply when considering chains with excursions (with nonzero excursion length γB ≠ 0), in which case the threshold criteria mixes conditions on \(\frac{{p}_{{{{\rm{s}}}}}}{{p}_{{{{\rm{s}}}}}^{* }}\) and \(\frac{{p}_{{{{\rm{b}}}}}}{{p}_{{{{\rm{b}}}}}^{* }}\). All these terms are suppressed as L → ∞ provided that the quantities in brackets are smaller than unity. Re-expressing Eq. (3), we can see that it is equivalent to a small downward “sag" of the seam threshold bound:

Fixing \(\frac{{p}_{{{{\rm{s}}}}}}{{p}_{{{{\rm{s}}}}}^{* }}=\frac{{p}_{{{{\rm{b}}}}}}{{p}_{{{{\rm{b}}}}}^{* }}\), Eq. (4) reduces to:

plotted in Fig. 4a.

Error bars represent 95% CI. a Analytical bounds (Eq. (6)) for \({p}_{{{{\rm{b}}}}}/{p}_{{{{\rm{b}}}}}^{* }={p}_{{{{\rm{s}}}}}/{p}_{{{{\rm{s}}}}}^{* }\) (solid), in which case the seam and bulk curves (dot-dashed) now overlap when plotted against pb. Note that \({p}_{{{{\rm{b}}}}}^{* }\) here corresponds to the phenomenological threshold bound of 1% for 3D as derived in ref. 44 and \({p}_{{{{\rm{1b}}}}}^{* }\) shows the sag in the threshold bound we derive relative to the bound from ref. 44. Seam-bulk interactions reduce the threshold bound slightly to \({p}_{{{{\rm{1b}}}}}^{* }\) as indicated by the pink arrow. The logical failure rate converges to the values for no seam-bulk interactions once the bulk error is a few times below \({p}_{{{{\rm{b}}}}}^{* }\), as excursions into the bulk become “frozen out." b Same as (a) but exact numerical simulation with the choice pseam = 14pbulk, approximately \({p}_{{{{\rm{bulk}}}}}/{p}_{{{{\rm{bulk}}}}}^{* }={p}_{{{{\rm{seam}}}}}/{p}_{{{{\rm{seam}}}}}^{* }\), which aligns the thresholds for the bulk-only curves (dotted) and seam-only curves (dashed). The full simulation including seam-bulk interaction (solid) similarly sags slightly and then converges toward the seam-only curves as \({p}_{{{{\rm{bulk}}}}}/{p}_{{{{\rm{bulk}}}}}^{* }\) becomes small. c Numerically extracted threshold plotted in terms of pseam, pbulk (purple), where pb = 4pbulk. Pink shows the threshold bound (Eq. (5)), with arrows pointing to the light pink line showing how the bound formula relaxes when reducing the overcounting of paths by substituting numerical values for \({p}_{{{{\rm{seam}}}}}^{* }\) and \({p}_{{{{\rm{bulk}}}}}^{* }\) along with an effective value of αc→1.4, the minimal value still bounding all the numerical datapoints. The blue diagonal line illustrates the pseam = 14pbulk cut from b).

Numerical simulations

In Fig. 4, we compare these analytical bounds to numerical Monte Carlo simulations49,50 to quantify the effect of error chains stretching simultaneously across the bulk and the seam. To model two 2D patches of surface code in distinct modules with a noisy interface between them and corrected with repeated rounds of noisy syndrome extraction extending into the time direction3,44, we run the simulation with a Ds = (1 + 1) dimension lattice of size L × L (the seam) on which errors occur with rate ps embedded in a Db = (2 + 1) dimension lattice of size L × L × L (the bulk) with error rate pb. An additional consequence of the seam being a sublattice within the bulk is that per code cycle, while bulk qubits are addressed by four local gates, each seam qubit only interacts with a single Bell pair for communication. Letting pbulk represent the probability of a local gate in bulk to cause a bit flip on a bulk qubit, we model this by directly substituting 4pbulk = pb (leading to a reasonable \({p}_{{{{\rm{bulk}}}}}^{* }=0.75 \%\)) while maintaining pseam = ps, since seam qubit noise is dominated by the Bell pair. From Fig. 4, we see that the numerical results display the same qualitative behavior as the analytical formulas, with a slight sag in the threshold as well as subthreshold convergence of the logical failure to the same value as without excursions. By adjusting the parameters μs and μb to match the known surface code threshold values for Ds = 2 and Db = 344 and relaxing αc from the rigorous bound to a smaller effective value, the bound formulas also provide a fairly accurate analytical model of the threshold behavior. Notably, up to the small correction represented by the gray region of Fig. 4c, Pfail behaves approximately as if bulk and seam were decoupled without cross terms from Eq. (4):

with \({p}_{{{{\rm{bulk}}}}}^{* }\approx 1 \%\) and \({p}_{{{{\rm{seam}}}}}^{* }\approx 10 \%\). As long as \(\frac{{p}_{{{{\rm{seam}}}}}}{{p}_{{{{\rm{seam}}}}}^{* }}\approx \frac{{p}_{{{{\rm{bulk}}}}}}{{p}_{{{{\rm{bulk}}}}}^{* }}\), so pseam ≈ 10pbulk, the seam noise has almost no effect.

Discussion

Our formalism can further generalize to connecting surface code patches in a variety of configurations, such as transversal gates or a grid of smaller patches. While in Fig. 1b we aligned the physical edges of two code patches so that the seam extended in both space and time, the results from Fig. 4 can apply to any 2D subspace of a 3D lattice. Consequently, a transversal gate between logical qubits in separate modules mediated by Bell pairs and followed by rounds of local error correction on each logical qubit would be similarly robust to Bell pair noise, as the transversal gate occurs on a single code cycle and introduces noise on a 2D sublattice which now extends in two space directions rather than one space and one time direction as before. By adding multiple seams along space and/or time directions and counting the paths to hop between different seams, our formalism can be extended (see Supplementary Note 1 for details) and used to understand situations including repeated transversal gates51 or code patches spanning multiple modules, where one could tile large surface code patches together into a single larger logical qubit. This is because from Eq. (3), one can see that the contribution of an excursion is exponentially suppressed in the excursion length ℓ. When modules are large, excursions that hop between distinct seams are long, and thus have negligible contribution. In this case, each seam becomes approximately independent, so that the seam-bulk interaction of each seam alone determines the overall logical failure rate. In Supplementary Note 2, we give a quantitative example of this behavior. Furthermore, since the robustness to noisy links is a consequence of the interface between qubits being lower dimensional, our findings also apply to other families of topological codes sharing this property, such as color codes52, which also have protocols for lattice surgery53,54.

Our main result, that the interface can tolerate a noise level pseam ≈ 10pbulk (Eq. (7)), relaxes the communication fidelity required for fault-tolerance in ongoing experimental efforts to build modular architectures. Such efforts include optical interconnects between ions17, atoms55, or superconducting qubits56,57,58,59,60, direct superconducting microwave links61,62,63,64, or even shuttling ions65 or atoms13 between distinct subunits, some having already demonstrated communication errors below \({p}_{{{{\rm{seam}}}}}^{* }\approx 10 \%\)17,62,64. With multiple quantum computing platforms13,18,29,30,31,32,33,34,35,36,37,38,39,40 working toward realizing local surface code qubits and rapidly progressing toward module sizes of thousands of qubits and local gate noise targets of ~0.1%8,9,10,11,12,13, interconnects with a corresponding target of ~1% noise will directly enable fault-tolerant modular scalability. For even noisier networks, distillation can still be used, with the simplest and most efficient protocols being sufficient to reach errors of ~10pbulk21, enabling scalability.

Methods

Model details for the interface between surface code qubits

Here, we provide additional details regarding the interface between the two logical qubits and how it gives rise to the phenomenological error model we numerically simulate.

When the interface between modules is realized via distributed entanglement, that entanglement serves as a resource for enacting non-local, teleported gates between qubits in distinct modules. Fig. 2 shows how bit and phase flip noise on the distributed Bell pair propagates to the control and target qubits in the distinct modules that the (pink) teleported gate acts on. The propagation is identical for errors occurring on either of the Bell pair qubits, as must be the case since the Bell pair is invariant under the application of XX and ZZ.

Therefore, in Fig. 1b, one can see that bit flip noise on the Bell pair propagates to the target qubits, i.e., the column of qubits to the right of the seam, and phase flip noise to control qubits, i.e., the column of qubits on the left of the seam. As the bit and phase flip errors trigger distinct check operators and can be decoded with distinct MWPM decoders, we can consider correcting for bit and phase flip errors as two separate problems. The seam can be chosen along either the \({\hat{X}}_{L}\) or the \({\hat{Z}}_{L}\) direction, but as in Fig. 1b, for concreteness we choose the seam along the \({\hat{X}}_{L}\) direction, in which case a logical \({\hat{X}}_{L}\) error is possible if too many errors occur along the seam, even with no bulk noise.

For the numerical simulation, we then construct an L × L × L lattice representing errors on the 2D surface code with L repeated rounds of syndrome extraction extending into the time direction3,44. To simulate the noisy syndrome bit flip logical error rate, \({\hat{X}}_{L}\), with elevated bit flip noise along the seam, we randomly place bit flips on the edges of the 3D lattice, with elevated probabilities for bit flips occurring along the 2D sublattice constituting the seam, which extends in the \({\hat{X}}_{L}\) and time directions. We then decode the syndromes arising from each set of bit flips using the Pymatching MWPM decoder50 and apply the corresponding correction, which returns the state of the logical qubit to the code space. The fraction of times that the correction includes a set of remaining bit flips which are topologically equivalent to applying an \({\hat{X}}_{L}\) operator is the logical bit flip error rate, plotted in Fig. 4. By symmetry, time-like error strings of length L occur with the same rate as logical \({\hat{X}}_{L}\) errors shown in Fig. 4, giving rise to a distinct source of logical error, for example when attempting logical gates with L rounds of syndrome extraction during lattice surgery.

Bit and phase flip logical errors

With the seam oriented as in Fig. 1b, the situation for phase flip noise is different, as the seam does not stretch along the \({\hat{Z}}_{L}\) direction. Elevated phase flip noise on the Bell pairs then has virtually no effect on the rate of logical phase flips \({\hat{Z}}_{L}\), as generating a \({\hat{Z}}_{L}\) logical error requires phase flips to penetrate the entire length of the bulk, regardless of the level of phase flip noise present along the seam. However, the bulk and seam phase flip noise must still be below the same threshold results from Fig. 4 to control phase flip error strings from stretching long distances in the time direction. Once below this threshold condition, logical failure from long time-like error chains can be suppressed by simply doing more rounds of syndrome extraction per logical gate, which extends the code distance in the time direction with no additional overhead in qubit number. This asymmetry, resulting from the choice of the seam’s orientation, allows one to immediately take advantage of any bias in the seam noise by choosing the seam to be along the \({\hat{X}}_{L}\) or \({\hat{Z}}_{L}\) direction with the lower level of seam noise.

Data availability

All data and code needed to evaluate the conclusions are available from the corresponding author upon reasonable request.

References

Shor, P. W. Scheme for reducing decoherence in quantum computer memory. Phys. Rev. A 52, R2493–R2496 (1995).

Muralidharan, S. et al. Optimal architectures for long distance quantum communication. Sci. Rep. 6, 20463 (2016).

Fowler, A. G., Mariantoni, M., Martinis, J. M. & Cleland, A. N. Surface codes: towards practical large-scale quantum computation. Phys. Rev. A 86, 032324 (2012).

Cetina, M. et al. Quantum gates on individually-addressed atomic qubits subject to noisy transverse motion. preprint at: https://arxiv.org/abs/2007.06768 (2020).

Ang, J. et al. Architectures for multinode superconducting quantum computers. Preprint at: https://arxiv.org/abs/2212.06167 (2022).

Saffman, M. Quantum computing with atomic qubits and Rydberg interactions: progress and challenges. J. Phys. B 49, 202001 (2016).

Saffman, M. Quantum computing with neutral atoms. Natl. Sci. Rev. 6, 24–25 (2019).

IonQ. Ionq aria. https://ionq.com/quantum-systems/aria (2023).

IBM. What’s next in quantum is quantum-centric supercomputing. https://research.ibm.com/quantum-computing (2023).

IBM. Ibm unveils 400 qubit-plus quantum processor and next-generation ibm quantum system two. https://newsroom.ibm.com/2022-11-09-IBM-Unveils-400-Qubit-Plus-Quantum-Processor-and-Next-Generation-IBM-Quantum-System-Two (2023).

Google. A preview of bristlecone, google’s new quantum processor. https://ai.googleblog.com/2018/03/a-preview-of-bristlecone-googles-new.html (2023).

Google. Quantum computer datasheet. https://quantumai.google/hardware/datasheet/weber.pdf (2021).

Bluvstein, D. et al. A quantum processor based on coherent transport of entangled atom arrays. Nature 604, 451–456 (2022).

Monroe, C. et al. Large-scale modular quantum-computer architecture with atomic memory and photonic interconnects. Phys. Rev. A 89, 022317 (2014).

Gottesman, D. & Chuang, I. L. Demonstrating the viability of universal quantum computation using teleportation and single-qubit operations. Nature 402, 390–393 (1999).

Moehring, D. L. et al. Entanglement of single-atom quantum bits at a distance. Nature 449, 68–71 (2007).

Stephenson, L. J. et al. High-rate, high-fidelity entanglement of qubits across an elementary quantum network. Phys. Rev. Lett. 124, 110501 (2020).

Nigmatullin, R., Ballance, C. J., de Beaudrap, N. & Benjamin, S. C. Minimally complex ion traps as modules for quantum communication and computing. New J. Phys. 18, 103028 (2016).

Dür, W. & Briegel, H.-J. Entanglement purification for quantum computation. Phys. Rev. Lett. 90, 067901 (2003).

Campbell, E. T. Distributed quantum-information processing with minimal local resources. Phys. Rev. A 76, 040302 (2007).

Krastanov, S., Albert, V. V. & Jiang, L. Optimized entanglement purification. Quantum 3, 123 (2019).

Jiang, L., Taylor, J. M., Sørensen, A. S. & Lukin, M. D. Distributed quantum computation based on small quantum registers. Phys. Rev. A 76, 062323 (2007).

Li, Y. & Benjamin, S. C. High threshold distributed quantum computing with three-qubit nodes. New J. Phys. 14, 093008 (2012).

Fujii, K., Yamamoto, T., Koashi, M. & Imoto, N. A distributed architecture for scalable quantum computation with realistically noisy devices. arxiv https://arxiv.org/abs/1202.6588 (2012).

Nickerson, N. H., Li, Y. & Benjamin, S. C. Topological quantum computing with a very noisy network and local error rates approaching one percent. Nat. Commun. 4, 1756 (2013).

Nickerson, N. H., Fitzsimons, J. F. & Benjamin, S. C. Freely scalable quantum technologies using cells of 5-to-50 qubits with very lossy and noisy photonic links. Phys. Rev. X 4, 041041 (2014).

Fowler, A. G. et al. Surface code quantum communication. Phys. Rev. Lett. 104, 180503 (2010).

Li, Y. & Benjamin, S. C. Hierarchical surface code for network quantum computing with modules of arbitrary size. Phys. Rev. A 94, 042303 (2016).

Krinner, S. et al. Realizing repeated quantum error correction in a distance-three surface code. Nature 605, 669–674 (2022).

AI, G. Q. Suppressing quantum errors by scaling a surface code logical qubit. Nature 614, 676–681 (2023).

Wu, Y., Kolkowitz, S., Puri, S. & Thompson, J. D. Erasure conversion for fault-tolerant quantum computing in alkaline earth rydberg atom arrays. Nat. Commun. 13, 4657 (2022).

Auger, J. M., Bergamini, S. & Browne, D. E. Blueprint for fault-tolerant quantum computation with rydberg atoms. Phys. Rev. A 96, 052320 (2017).

Trout, C. J. et al. Simulating the performance of a distance-3 surface code in a linear ion trap. New J. Phys. 20, 043038 (2018).

Brown, K. R., Kim, J. & Monroe, C. Co-designing a scalable quantum computer with trapped atomic ions. npj Quantum Inf. 2, 16034 (2016).

Lekitsch, B. et al. Blueprint for a microwave trapped ion quantum computer. Sci. Adv. 3, e1601540 (2017).

Taminiau, T. H., Cramer, J., van der Sar, T., Dobrovitski, V. V. & Hanson, R. Universal control and error correction in multi-qubit spin registers in diamond. Nat. Nanotechnol. 9, 171–176 (2014).

Xue, X. et al. Quantum logic with spin qubits crossing the surface code threshold. Nature 601, 343–347 (2022).

Abobeih, M. H. et al. Fault-tolerant operation of a logical qubit in a diamond quantum processor. Nature 606, 884–889 (2022).

Rudolph, T. Why I am optimistic about the silicon-photonic route to quantum computing. APL Photonics 2, 030901 (2017).

Gimeno-Segovia, M., Shadbolt, P., Browne, D. E. & Rudolph, T. From three-photon greenberger-horne-zeilinger states to ballistic universal quantum computation. Phys. Rev. Lett. 115, 020502 (2015).

Kitaev, A. Fault-tolerant quantum computation by anyons. Ann. Phys. 303, 2–30 (2003).

Bravyi, S. B. & Kitaev, A. Y. Quantum codes on a lattice with boundary. preprint at: https://doi.org/10.48550/arXiv.quant-ph/9811052 (1998).

Freedman, M. H. & Meyer, D. A. Projective plane and planar quantum codes. Found. Comput. Math. 1, 325–332 (2001).

Dennis, E., Kitaev, A., Landahl, A. & Preskill, J. Topological quantum memory. J. Math. Phys. 43, 4452–4505 (2002).

Horsman, D., Fowler, A. G., Devitt, S. & Meter, R. V. Surface code quantum computing by lattice surgery. New J. Phys. 14, 123011 (2012).

Breuckmann, N. P. Phd thesis: homological quantum codes beyond the toric code. https://arxiv.org/abs/1802.01520 (2018).

Dumer, I., Kovalev, A. A. & Pryadko, L. P. Thresholds for correcting errors, erasures, and faulty syndrome measurements in degenerate quantum codes. Phys. Rev. Lett. 115, 050502 (2015).

Strikis, A., Benjamin, S. C. & Brown, B. J. Quantum computing is scalable on a planar array of qubits with fabrication defects. Phys. Rev. Appl. 19, 064081 (2023).

Tuckett, D. K. Tailoring surface codes: improvements in quantum error correction with biased noise. Ph.D. thesis, University of Sydney (qecsim: https://github.com/qecsim/qecsim) (2020).

Higgott, O. Pymatching: a python package for decoding quantum codes with minimum-weight perfect matching. ACM Transactions on Quantum Computing, https://dl.acm.org/doi/10.1145/3505637(2022).

Bluvstein, D. et al. Logical quantum processor based on reconfigurable atom arrays. Nature 626, 58–65 (2024).

Brown, B. J., Nickerson, N. H. & Browne, D. E. Fault-tolerant error correction with the gauge color code. Nat. Commun. 7, 12302 (2016).

Landahl, A. J. & Ryan-Anderson, C. Quantum computing by color-code lattice surgery. preprint at: https://arxiv.org/abs/1407.5103 (2014).

Thomsen, F., Kesselring, M. S., Bartlett, S. D. & Brown, B. J. Low-overhead quantum computing with the color code. preprint at: https://arxiv.org/abs/2201.07806v2 (2022).

Reiserer, A. & Rempe, G. Cavity-based quantum networks with single atoms and optical photons. Rev. Mod. Phys. 87, 1379–1418 (2015).

Sahu, R. et al. Quantum-enabled operation of a microwave-optical interface. Nat. Commun. 13, 1276 (2022).

Tu, H.-T. et al. High-efficiency coherent microwave-to-optics conversion via off-resonant scattering. Nat. Photonics 16, 291–296 (2022).

Delaney, R. D. et al. Superconducting-qubit readout via low-backaction electro-optic transduction. Nature 606, 489–493 (2022).

Zhu, N. et al. Waveguide cavity optomagnonics for microwave-to-optics conversion. Optica 7, 1291–1297 (2020).

Imany, P. et al. Quantum phase modulation with acoustic cavities and quantum dots. Optica 9, 501–504 (2022).

Magnard, P. et al. Microwave quantum link between superconducting circuits housed in spatially separated cryogenic systems. Phys. Rev. Lett. 125, 260502 (2020).

Burkhart, L. D. et al. Error-detected state transfer and entanglement in a superconducting quantum network. PRX Quantum 2, 030321 (2021).

Yan, H. et al. Entanglement purification and protection in a superconducting quantum network. Phys. Rev. Lett. 128, 080504 (2022).

Zhong, Y. et al. Deterministic multi-qubit entanglement in a quantum network. Nature 590, 571–575 (2021).

Pino, J. M. et al. Demonstration of the trapped-ion quantum ccd computer architecture. Nature 592, 209–213 (2021).

Acknowledgements

This project was funded in part by DARPA under the ONISQ program (grant # 134371-5113608), the MIT-Harvard Center for Ultracold Atoms, an NSF Physics Frontier Center (NSF grant # PHY-1734011), and AWS. Support is also acknowledged from the U.S. Department of Energy, Office of Science, National Quantum Information Science Research Centers, Quantum Systems Accelerator (contract # 7571809), The authors thank Dolev Bluvstein for helpful discussions.

Author information

Authors and Affiliations

Contributions

J.R. originally conceived the work, developed the theoretical formalism, and derived the bound results. J.R. and J.S. conceptually developed the work, performed and interpreted the numerical simulations, and drafted the manuscript. N.B. contributed to formalizing the bound proof and provided helpful discussions. V.V. supervised the project. All authors discussed the results and contributed to the writing of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests: V.V. is a co-founder and shareholder of QuEra.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ramette, J., Sinclair, J., Breuckmann, N.P. et al. Fault-tolerant connection of error-corrected qubits with noisy links. npj Quantum Inf 10, 58 (2024). https://doi.org/10.1038/s41534-024-00855-4

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41534-024-00855-4

This article is cited by

-

Volcano architecture for scalable quantum processor units

Science China Physics, Mechanics & Astronomy (2026)

-

Deterministic remote entanglement using a chiral quantum interconnect

Nature Physics (2025)

-

Demonstrating a universal logical gate set in error-detecting surface codes on a superconducting quantum processor

npj Quantum Information (2025)

-

A high-efficiency elementary network of interchangeable superconducting qubit devices

Nature Electronics (2025)

-

Modular architectures and entanglement schemes for error-corrected distributed quantum computation

npj Quantum Information (2025)