Abstract

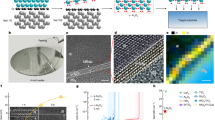

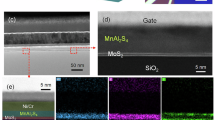

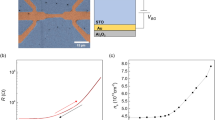

Tellurium (Te) is a promising p-type semiconductor but suffers from pronounced electrical hysteresis that limits device stability. The origin of hysteresis in Te field-effect transistors is investigated, and effective suppression strategies are demonstrated. In exposed devices, large hysteresis and abrupt current switching are observed, governed by the direction and range of gate voltage sweeps rather than gate polarity, and are attributed to the dynamic reorientation of dipolar gas molecules adsorbed on the Te surface. Dielectric encapsulation using Al2O3 significantly suppresses gas-induced hysteresis, resulting in improved mobility of ~80 cm2 V-1 s-1 and an ION/IOFF ratio exceeding 105 under ambient conditions. Nevertheless, residual hysteresis associated with charge trapping persists in single-gate devices. To further stabilize channel electrostatics, a dual-gate architecture employing Al2O3 top and bottom dielectrics is implemented, achieving hysteresis below 1 V across a wide range of sweep rates and exhibiting minimal degradation under prolonged bias stress. These results establish a comprehensive understanding of hysteresis in Te and enable reliable, BEOL-compatible p-type transistors for advanced integration.

Similar content being viewed by others

Data availability

The datasets generated and/or analyzed during the current study are not publicly available due to ongoing further studies but are available from the corresponding author on reasonable request.

References

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Pal, A., Chavan, T., Jabbour, J., Cao, W. & Banerjee, K. Three-dimensional transistors with two-dimensional semiconductors for future CMOS scaling. Nat. Electron. 7, 1147–1157 (2024).

Parthiban, S. & Kwon, J.-Y. Role of dopants as a carrier suppressor and strong oxygen binder in amorphous indium-oxide-based field effect transistor. J. Mater. Res. 29, 1585–1596 (2014).

Si, M. et al. Scaled indium oxide transistors fabricated using atomic layer deposition. Nat. Electron. 5, 164–170 (2022).

Kim, H. et al. Synthetic WSe2 monolayers with high photoluminescence quantum yield. Sci. Adv. 5, eaau4728 (2019).

Lien, D.-H. et al. Electrical suppression of all nonradiative recombination pathways in monolayer semiconductors. Science 364, 468–471 (2019).

Roy, T. et al. Dual-Gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Shi, M. et al. Counteractive coupling IGZO/CNT hybrid 2T0C DRAM accelerating RRAM-based computing-in-memory via monolithic 3D integration. In Proc. 2023 International Electron Devices Meeting (IEDM) (IEEE, 2023).

Zha, J. et al. A 2D heterostructure-based multifunctional floating gate memory device for multimodal reservoir computing. Adv. Mater. 36, 2308502 (2024).

Moon, J. H. et al. Scalable fabrication of mid-wavelength and long-wavelength infrared photodetectors based on narrow bandgap semiconductors: challenges and opportunities. Int. J. Extrem. Manuf. 8, 012012 (2026).

Liu, K. et al. A lithium-ion-driven electrolyte-gated 2D synaptic transistor based on Se0.3Te0.7 nanosheet for reservoir computing. Small 21, e2505436 (2025).

Zha, J. et al. Electronics and optoelectronics based on tellurium. Adv. Mater. 36, 2408969 (2024).

Amani, M. et al. Solution-synthesized high-mobility tellurium nanoflakes for short-wave infrared photodetectors. ACS Nano 12, 7253–7263 (2018).

Huang, H. et al. Precursor-confined chemical vapor deposition of 2d single-crystalline SexTe1–x nanosheets for p-type transistors and inverters. ACS Nano 18, 17293–117303 (2024).

Zha, J. et al. Electronic/optoelectronic memory device enabled by tellurium-based 2D van der Waals heterostructure for in-sensor reservoir computing at the optical communication band. Adv. Mater. 35, 2211598 (2023).

Liu, G. et al. Ultrahigh thermoelectric performance of Janus α-STe₂ and α-SeTe₂ monolayers. Phys. Chem. Chem. Phys. 24, 28295–28305 (2022).

Abd-Elnaiem, A. M. et al. Substituting silver for tellurium in selenium–tellurium thin films for improving the optical characteristics. J. Inorg. Organomet. Polym. Mater. 32, 2009–2021 (2022).

Wang, Y. et al. Field-effect transistors made from solution-grown two-dimensional tellurene. Nat. Electron. 1, 228–236 (2018).

Zhou, G. et al. High-mobility helical tellurium field-effect transistors enabled by transfer-free, low-temperature direct growth. Adv. Mater. 30, 1803109 (2018).

Zhao, C. et al. Tellurium single-crystal arrays by low-temperature evaporation and crystallization. Adv. Mater. 33, 2100860 (2021).

Zhao, C. et al. Evaporated tellurium thin films for p-type field-effect transistors and circuits. Nat. Nanotechnol. 15, 53–58 (2020).

Kim, T. et al. Growth of high-quality semiconducting tellurium films for high-performance p-channel field-effect transistors with wafer-scale uniformity. npj 2D Mater. Appl. 6, 4 (2022).

Kim, M. et al. Processes to enable hysteresis-free operation of ultrathin ALD Te p-channel field-effect transistors. Nanoscale Horiz. 9, 1990–1998 (2024).

Kim, T. et al. High-performance hexagonal tellurium thin-film transistor using tellurium oxide as a crystallization retarder. IEEE Electron Device Lett. 44, 269–272 (2022).

Yang, P. et al. Mechanisms of current fluctuation in high-mobility p-type tellurium field-effect transistors. IEEE Trans. Electron Devices 71, 6417–6423 (2024).

Kaushik, N. et al. Reversible hysteresis inversion in MoS2 field effect transistors. npj 2. D. Mater. Appl. 1, 34 (2017).

Late, D. J., Liu, B., Matte, H. R., Dravid, V. P. & Rao, C. Hysteresis in single-layer MoS2 field effect transistors. ACS Nano 6, 5635–5641 (2012).

Park, R. S. et al. Hysteresis in carbon nanotube transistors: measurement and analysis of trap density, energy level, and spatial distribution. ACS Nano 10, 4599–4608 (2016).

Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano 4, 7221–7228 (2010).

Wang, S.-T. et al. Reversible charge transfer doping in atomically thin In2O3 by viologens. ACS Appl. Mater. Interfaces 16, 5302–5307 (2024).

Li, T., Du, G., Zhang, B. & Zeng, Z. Scaling behavior of hysteresis in multilayer MoS2 field effect transistors. Appl. Phys. Lett. 105, 093107 (2014).

Late, D. J. et al. Sensing behavior of atomically thin-layered MoS2 transistors. ACS Nano 7, 4879–4891 (2013).

Zhang, J. et al. Room-temperature ferroelectric, piezoelectric and resistive switching behaviors of single-element Te nanowires. Nat. Commun. 15, 7648 (2024).

Li, T. et al. Thermodynamics and kinetics in van der Waals epitaxial growth of Te. Nanoscale 17, 9308–9314 (2025).

Xu, M. et al. Hydrogen-assisted growth of one-dimensional tellurium nanoribbons with unprecedented high mobility. Mater. Today 63, 50–58 (2023).

Cho, K. et al. Electric stress-induced threshold voltage instability of multilayer MoS2 field effect transistors. ACS Nano 7, 7751–7758 (2013).

Lee, S. W. et al. Positive gate bias stress instability of carbon nanotube thin film transistors. Appl. Phys. Lett. 101, 053504 (2012).

Hein, M. P. et al. Molecular doping for control of gate bias stress in organic thin film transistors. Appl. Phys. Lett. 104, 013507 (2014).

Jeong, J. K. et al. Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors. Appl. Phys. Lett. 93, 123508 (2008).

Kim, W. et al. Hysteresis caused by water molecules in carbon nanotube field-effect transistors. Nano Lett. 3, 193–1198 (2003).

Bartošík, M. et al. Mechanism and suppression of physisorbed-water-caused hysteresis in graphene field-effect transistor sensors. ACS Sens. 5, 2940–2949 (2020).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Lan, H.-Y. et al. Reliability of high-performance monolayer MoS2 transistors on scaled high-κ HfO2. npj 2. D. Mater. Appl. 9, 5 (2025).

Kang, C. G. et al. Mechanism of the effects of low temperature Al2O3 passivation on graphene field effect transistors. Carbon 53, 182–187 (2013).

Franklin, A. D. et al. Variability in carbon nanotube transistors: improving device-to-device consistency. ACS Nano 6, 1109–1115 (2012).

Park, R. S. et al. Hysteresis-free carbon nanotube field-effect transistors. ACS Nano 11, 4785–4791 (2017).

Lee, J. S. et al. Origin of gate hysteresis in carbon nanotube field-effect transistors. J. Phys. Chem. C 111, 12504–112507 (2007).

McGill, S. A. et al. High-performance, hysteresis-free carbon nanotube field-effect transistors via directed assembly. Appl. Phys. Lett. 89, 163123 (2006).

Ha, T.-J. et al. Highly stable hysteresis-free carbon nanotube thin-film transistors by fluorocarbon polymer encapsulation. ACS Appl. Mater. Interfaces 6, 8441–8446 (2014).

Yang, P. et al. Modeling the impact of interface and border traps on hysteresis in encapsulated monolayer MoS₂-based double-gated FETs. In Proc. 2024 Austrochip Workshop on Microelectronics (Austrochip) (IEEE, 2024).

Knobloch, T. et al. A physical model for the hysteresis in MoS2 transistors. IEEE J. Electron Devices Soc. 6, 972–978 (2018).

Illarionov, Y. Y. et al. Energetic mapping of oxide traps in MoS2 field-effect transistors. 2D Mater. 4, 025108 (2017).

Di Bartolomeo, A. et al. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 5, 015014 (2018).

Illarionov, Y. Y. et al. Variability and high temperature reliability of graphene field-effect transistors with thin epitaxial CaF2 insulators. npj 2. D. Mater. Appl. 8, 23 (2024).

Liao, Z.-M. et al. Hysteresis reversion in graphene field-effect transistors. J. Chem. Phys. 133, 044703 (2010).

Xu, H. et al. Investigating the mechanism of hysteresis effect in graphene electrical field device fabricated on SiO2 substrates using raman spectroscopy. Small 8, 2833–2840 (2012).

Winters, M., Sveinbjörnsson, E. Ö & Rorsman, N. Hysteresis modeling in graphene field-effect transistors. J. Appl. Phys. 117, 074501 (2015).

Acknowledgements

D.-H.L. acknowledges support from the National Science and Technology Council (NSTC 114-2112-M-A49-013), the NSTC T-Star Center Project: Future Semiconductor Technology Research Center (NSTC 114-2634-F-A49-001), the Ministry of Education (Yushan Scholar Program), and Taiwan Semiconductor Manufacturing Company. Y.-L.C. acknowledges support from the National Science and Technology Council, Taiwan (NSTC 113-2112-M-007-034-MY3, 114-2119-M-007-015-MBK, and 114-2628-E-007-001). We thank Integrated Service Technology (iST) for support with material characterization.

Author information

Authors and Affiliations

Contributions

S.-T.W., K.-W.L. and D.-H.L. conceived the idea. S.-T.W. and K.-W.L. performed the device fabrication and the measurement. S.-T.W., K.-W.L., T.-T.W. and Y.-C.C. helped the thin film growth. C.-F.C. helped the device measurement. C.-C.Chung and C.-H.L. carried out the TEM and Raman analysis. C.-Y.C. carried out the XPS analysis. S.-C.C. designed and developed the Low-T PVD tools. T.A. assisted with device simulations. S.-T.W., K.-W.L., Y.-L.C. and D.-H.L. analyzed the data. S.-T.L., Y.-F.L., I.R., T.Y.T.H., and C.-C.Cheng provided scientific guidance throughout. Y.-L.C. and D.-H.L. supervised the research. S.-T.W., K.-W.L., Y.-L.C. and D.-H.L. prepared the paper draft. All the authors contributed to the discussion and manuscript preparation and read the final manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Wang, ST., Li, KW., Weng, TT. et al. Suppression of hysteresis in ultrathin tellurium transistors. npj 2D Mater Appl (2026). https://doi.org/10.1038/s41699-026-00686-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-026-00686-1