Abstract

The rising computational demands of Artificial Intelligence (AI) are driving a rapid surge in carbon emissions from the Information and Communications Technology (ICT) sector. Traditional CMOS-based computing is reaching its scaling limits and struggling to meet these immense demands in a carbon-sustainable manner—underscoring the need for alternative hardware solutions for AI. Photonic computing has emerged as a promising alternative to CMOS through its energy-efficient computing capabilities in the optical domain. This perspective explores the potential of photonics as a carbon-sustainable solution for the next-generation AI hardware.

Similar content being viewed by others

Introduction

Over the past decade, there has been substantial growth in the computational demands of Artificial Intelligence (AI) models, leading to a significant rise in carbon emissions from the Information and Communications Technology (ICT) sector. The size of the GPT-based Large Language Models (LLMs) has grown by 1000× from GPT-1 (117 million parameters) to GPT-3 (175 billion parameters)1. The latest Llama-4 model (2025) from Meta has two trillion parameters2. The carbon impact of training and using these massive AI models is significant. As an example, training GPT-3 emitted ~500 metric tons of CO2eq (carbon dioxide equivalent), which is similar to driving an average passenger car for about a million miles3,4. Moreover, due to the explosive growth of AI usage, especially for ChatGPT-like services, inference operations for GPT-3 are estimated to produce ~12,800 metric tons of CO2eq, which is 25 × the emissions generated during training in just one year5. As a result, researchers are focusing on developing energy-efficient hardware for AI, leading to remarkable advancements in accelerators and GPUs optimized for AI workloads. The forefront of these advancements includes several hardware designs delivering hundreds to thousands of TFLOPS (tera floating point operations per second) while maintaining high energy efficiency. Among them, Google’s Tensor Processing Units (TPUs)6 leverage systolic arrays for efficient matrix computations; NVIDIA’s Tensor Core GPUs7,8 support high-performance parallel computing; and Meta’s MTIA9 is tailored for inference of recommendation models.

Despite the operational improvements in AI systems, their overall carbon footprint is far from being sustainable with traditional CMOS architectures. This is largely due to the growing complexity of the manufacturing process and the corresponding carbon emission (referred to as embodied carbon), as well as the limiting scaling capability of CMOS. These limitations led to the exploration of sustainable alternatives, with low carbon emissions during both operation and manufacturing. Photonics has emerged as a promising alternative to CMOS, offering energy-efficient computation in the optical domain. While photonics is already widely deployed in applications such as optical transceivers, LIDAR, and biosensing, its potential for accelerating machine learning workloads has recently gained increasing interest.

In this perspective, we discuss the limits of current CMOS architectures and examine how photonic platforms could provide a carbon-sustainable alternative to CMOS when facing the growing demand for AI. In our discussion, we account for both operational and embodied carbon of photonic computing systems and compare them with traditional CMOS-based computing systems. Finally, we project the total carbon emissions of a popular photonics-based AI hardware compared to CMOS-based AI hardware for the case of data centers running LLMs. We conclude the perspective by discussing some key research directions for the computing community to explore the full potential of photonics for sustainable AI.

Photonic chips as a sustainable alternative to CMOS chips

The rise of embodied carbon and limits of the CMOS architectures

To provide a clear comparison of the carbon footprint of photonics and CMOS chips, we discuss the role of carbon emission during operation (Operational Carbon Footprint, OCF), and manufacturing (Embodied Carbon Footprint, ECF)10. The total carbon footprint of a computing device is primarily the summation of operational and embodied carbon10. While frequently disregarded, embodied carbon is becoming the dominant contributor to total carbon emissions of traditional CMOS-based computing systems11. The increasing energy efficiency of the newer technology nodes is accompanied by the increasing complexity of the manufacturing process with diminishing returns11,12,13. This is primarily because the CMOS chips no longer scale in area or energy efficiency according to Moore’s Law, and it translates to traditional CMOS-based computing struggling to meet the immense demands of AI in a carbon-sustainable manner14.

A clean example of the role of embodied carbon in the carbon footprint of computing systems is the transition from iPhone 3 to iPhone 11, where the operational carbon decreased by ~2.5× due to the efforts in optimizing energy efficiency11. However, this improvement came at the cost of increasing complexity in the fabrication process, leading to a rise in the total carbon footprint by ~1.4× , despite the reduced operational carbon11. In iPhone 15, more than 80% carbon was reported to be embodied carbon3.

Another compelling example is cloud servers, where embodied carbon now contributes to 50–82% of the total carbon emissions13. Consequently, data centers running on CMOS chips now all over the world together emit more carbon than countries like Ireland and Denmark, with emissions projected to rise even more in the years ahead11,15,16. If this trend continues, the ICT sector could account for 20% of global carbon emissions by 203011.

Advantages of photonics in OCF

OCF can be calculated as the energy consumption during operation multiplied by the carbon intensity of the operational energy source, CIop (kg CO2eq/kWh), as shown in Eq. (1)10.

Therefore, OCF is directly related to the energy efficiency of a device. The key advantage of photonics over CMOS in terms of operational energy efficiency comes from its ability to compute in the optical domain with lower losses than electrical devices. This high energy efficiency of photonic computing helps to achieve a low OCF as well as high throughput in photonic systems.

Photonic chips can perform fast and energy-efficient General Matrix-Matrix Multiplication (GEMM) operations, which constitute over 90% of the operations in Deep Neural Networks (DNNs)17. By leveraging this promising performance, several electro-photonic AI accelerators have been developed, combining photonics for GEMM computation with electronics for other computation tasks and memory operations18,19,20,21,22,23,24. These accelerators achieve orders of magnitude improvements in throughput and energy efficiency over CMOS-based accelerators (primarily based on simulated results), driving the growing popularity of photonic computing for AI applications. The high energy efficiency of photonic computing translates directly into substantial reductions in OCF, as indicated in Eq. (1).

However, the current photonic systems are bottlenecked by their dependency on electronic components. This dependency arises primarily because photonic memory is not yet viable for widespread implementation due to challenges such as limited integration density, thermal management issues, fabrication complexity, and optical crosstalk25,26. Also, the non-linear operations (ReLU, tanH, etc.) of DNNs cannot be efficiently performed in photonics. So we need to switch to the electrical domain to perform those operations. As a result, data must be periodically converted between the electrical and photonic domains. These conversions are costly, especially when we need to maintain the high bit precision requirements of DNNs. The dependency on electronic components also limits the throughput of the photonic systems, because the electronic components would be extremely power-consuming to keep up with the computation speed of photonics. Hence, the current electro-photonic accelerators run at 5-10 GHz at most.

Despite these constraints, electro-photonic accelerators can gain multiple orders of magnitude higher energy efficiency than fully CMOS-based systems. In Table 1, we provide a short list of recent electro-photonic accelerators and how they compare with CMOS-based systems. Researchers are actively working on different optimization strategies to overcome the above-mentioned challenges to design efficient electro-photonic accelerators.

Advantages of photonics in ECF

ECF consists of several components from the fabrication process, including energy consumption of the tools, GreenHouse Gas (GHG) emission, and material extraction10. To estimate the ECF, we adopt the equation outlined in the well-established Architectural Carbon modeling Tool (ACT)10.

Here,

-

EPA (Energy Per unit Area) is the energy consumption of the manufacturing tools per unit area, which is multiplied by the carbon intensity of the energy source during manufacturing, CIfab.

-

GPA (GHG Per unit Area) is the GHG emissions from the manufacturing tools per unit area.

-

MPA (Material extraction carbon Per unit Area) is the raw material procurement cost per unit area.

-

Cpackage is the carbon cost of the integration process of chiplet-based systems.

The ECF advantages of photonic chips over CMOS chips come from two key factors: their simpler fabrication process and higher yield. We describe these factors in detail below.

Simpler fabrication process

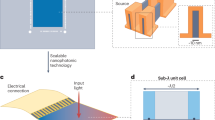

In Fig. 1a, we show the cross-section of an active photonic chip with off-chip laser sources (adapted from AIM Photonics multi-project wafer27). Figure 1b shows the cross-section of a generic CMOS chip, with 10 metal layers to represent a 28 nm technology node28. Newer technology nodes incorporate more metal layers to handle higher circuit complexity28.

In general, for all layers of both chips, the components (i.e., waveguides, metals, etc.) are fabricated with the necessary lithography, etching, cleaning, and sputter deposition steps, followed by polishing and oxide deposition using the Chemical Vapor Deposition (CVD) process29,30. Each chip also requires additional steps to meet its unique design and functionality requirements. Below we explain the differences between the two chips for the two stages of the fabrication process, i.e., the Front-end-of-Line (FEOL) and the Back-end-of-Line (BEOL)30. It should be noted that the FEOL/BEOL division is clearer for a CMOS chip than it is for a photonic chip - but in both cases, the electrical signal wiring layers can be called BEOL.

FEOL: In a photonic chip, computation is performed by manipulating optical signals propagating through waveguides. Therefore, FEOL involves silicon (Si) and silicon-nitride (SiN) layers to fabricate the waveguides, along with a germanium (Ge) photodiode layer to detect the optical signals. Additionally, to control the optical signals inside the waveguides using optical components like Mach-Zehnder Interferometers (MZIs) or Micro-Ring Resonators (MRRs), p-type and n-type regions are formed in the silicon through dopant implantation and thermal activation. Similarly, the Ge photodiode has doped regions for a p-i-n diode structure.

For a CMOS chip, computation is performed with transistors, and thus, the FEOL of a CMOS chip consists of transistors. There are typically two types of transistors in a CMOS chip - nMOS and pMOS. For each type of transistor, the fabrication process includes multiple iterations of lithography, etching, and cleaning steps, to ensure that the right concentration of implants is present for each type of transistor, making CMOS FEOL fabrication more energy-intensive than a photonic chip.

BEOL: In a photonic chip, the p-type and n-type regions are connected to metal layers (M1 and M2) through the via layers (V1 and V2). Typically, two metal layers suffice for constructing the interconnects and routing control signals to the optical components (MZIs, MRRs, etc.). In contrast, a CMOS chip requires more metal layers to route the interconnects to establish connections between nearby and far-separated transistors, distribute power, and distribute the clock signal. For instance, a 28 nm CMOS chip has 10 metal layers, and a 3 nm chip, with more transistor density than a 28 nm chip, has 20 metal layers28. The additional metal layers in CMOS chips necessitate more fabrication steps, significantly increasing the overall fabrication energy.

For both CMOS and photonic chips, bond pads are used to connect the chips to the external world through different integration methods, such as 2D, 3D or 2.5D. Lastly, for a photonic chip, a deep trench is formed with lithography, etching, and cleaning to expose the waveguide edge, enabling the connection of optical fibers to the photonic waveguides along the chip’s edge.

We can calculate the EPA of photonic chips using the median power and throughput values for each manufacturing step reported by Bardon et al.28, the same source used for estimating the EPA of CMOS chips.

We show the EPA comparison of photonic chip and CMOS chip in Table 2. We estimate the EPA of a photonic chip to be 4.1 × less than a 28 nm CMOS chip. The EPA reduction grows with the newer technology nodes due to the increased number of fabrication steps and complexity of the newer technology nodes28. As a result, compared to a 3 nm CMOS chip, a photonic chip consumes 14.77 × less EPA.

Higher yield

Photonic chips generally have wide spacing between waveguides (that are typically 100s of nm wide) to prevent optical coupling. As a result, the nanometer-scale defects that are typical in advanced fabrication processes have less detrimental impact on photonic chips compared to the densely packed CMOS chips. The critical area of a photonic chip can be estimated to be 20% of the total chip area31. Therefore, for the same defect density, photonic chips exhibit a higher yield than CMOS chips by a factor of e0.2, following a Poisson yield model (Eq. (3)).

This increased yield in photonic chips reduces the embodied carbon by minimizing the number of wasted chips due to fabrication defects.

Other metrics

For GPA and MPA, we can make conservative estimations due to the lack of publicly available data. We use the GPA of a 28 nm technology node10 (a technology node with higher fabrication steps than photonics) as the GPA for a photonic chip. Similarly, we set the MPA of photonic chips as 500 g/cm2, the same as the CMOS chips10. With these conservative assumptions, our estimated EPA, and yield, we can calculate the ECF of photonic chips following Eq. (2). We use this EPA calculation method in our case study. We summarize the EPA estimation method and our assumptions in Box 1 (top part).

Note that we calculate the ECF at a chip level, and assume that the lasers are off chip. The trench shown in Fig. 1a provides reliable light coupling from an optical fiber to an on-chip waveguide. This is a practical and commonly adopted design choice in today’s integrated photonics, where placing lasers off-chip helps avoid additional thermal management and fabrication complexity.

Potential carbon saving by adopting photonics in data centers

Inspired by the escalating carbon emissions driven by the substantial computational demands of LLMs like ChatGPT, we perform a case study to explore the potential carbon savings achieved through the use of photonics in data centers running LLMs. We experiment with the well-recognized electro-photonic accelerator, Lightening-Transformer (LT)23, and compare its carbon emissions against the NVIDIA A100 GPU7, the benchmark used in Zhu et al.23. The goal of this experiment is to provide a quantitative comparison of carbon footprint based on existing literature. We acknowledge that A100 is not the ideal baseline for comparison with LT, as A100 is a general-purpose accelerator, supporting diverse functionalities such as training and arithmetic operations with multiple data types, while LT is designed for inference workloads. Therefore, an inference-only accelerator would be a more appropriate baseline to compare with LT. Likewise, more recent GPUs, such as the H1008 and H20032, could offer higher energy efficiency (TOPS/Watt) but at a higher cost than A100 due to advanced fabrication. Nevertheless, to maintain fairness with A100, for ECF calculation, we focus solely on the portion of the A100’s area allocated to inference operations7. For OCF calculation, we directly use the reported energy and performance from Zhu et al.23, where the authors ensure a fair comparison between LT and A100 through the use of mixed precision in A100 and accurate inference energy measurement using NVIDIA profiling tools.

We summarize the methodology of our analysis in Box 1. Our analysis assumes a typical non-renewable (coal-based) energy for fabrication33 and renewable (wind-based) energy for operation34. For LT, we use our ECF estimation process of photonic chips for its photonic chiplet and ACT model for its CMOS chiplet. Additionally, we consider 3D integration of the photonic and electronic chiplet and estimate additional packaging carbon using the ECO-CHIP tool35.

In Fig. 2, we show the ECF and OCF per inference of LT and A100. LT and A100 have different areas, throughputs, and power consumptions; so, directly comparing raw ECF and OCF does not provide useful insights without a defined scenario. We leverage these values to calculate the total carbon footprint later in our case study, which considers a specific application scenario. In Fig. 2a, we show that LT consumes less ECF than A100 due to its smaller area and also because the photonic chip within the accelerator helps to reduce ECF.

a ECF (Embodied Carbon Footprint) and b OCF (Operational Carbon Footprint) per inference for the reported DNN models of LT (Lightening-Transformer, electro-photonic) and A100 (electronic) accelerators23. LT emits less ECF and OCF than A100. The breakdown of LT's ECF is shown. CMOS components contribute to the dominant portion of LT's ECF.

In Fig. 2b, we calculate the OCF/inference for BERT-large (LLM) and DeiT-B (vision transformer), two popular transformer models, based on the energy/inference values reported in Zhu et al.23. The reported energy for LT accounts for optical losses, electrical-to-optical and optical-to-electrical conversions, digital-to-analog and analog-to-digital conversions, and memory23. Due to the energy-efficient computing capabilities of photonics, LT achieves one order of magnitude lower OCF/inference than A100 on average. Additionally, LT delivers one order of magnitude higher throughput on average than A100, as reported in Zhu et al.23.

Next, we compare the total carbon emissions from LT and A100 in data centers to run BERT-large inferences. We set the current workload demand and its growth rate based on the ChatGPT compute load characterization presented in Chien et al.5. We consider a current daily inference request volume of 270 million, a peak throughput requirement of 10 million inferences per minute, and a usage growth rate of 1.4 × per year (based on data documented over 8 countries5). Initially, there are 500 accelerators (each for LT and A100), and more accelerators are added as necessary to meet rising usage demand. Figure 3 illustrates the cumulative carbon emissions of LT and A100 over the next 10 years. Due to the advantages of photonics in ECF and OCF, along with the high throughput, LT emits lower carbon compared to A100. Notably, the initial number of LT accelerators can suffice to support the growing inference demands for up to five years. After five years, more LT accelerators are needed, increasing the ECF according to the usage growth rate. Whereas the A100, which offers lower throughput than LT, requires additional accelerators starting from the first year. Overall, LT significantly reduces carbon emissions, producing two orders of magnitude less carbon than A100 over a 10-year period.

Y-axis shows the cumulative carbon emission (embodied + operational carbon footprint) when running BERT-large on LT (Lightening-Transformer) and A100 in data centers over the next 10 years. Workload intensity and growth rate adapted from5 based on ChatGPT statistics. LT can potentially emit two orders of magnitude lower carbon than A100.

Ideally, as of now, the state-of-the-art accelerator to compare with would be more recent GPUs like H1008 or H20032, which would have higher energy efficiency (TOPS/Watt) at the cost of advanced fabrication than A1007. Using speculated metrics for the H100, our back-of-the-envelope calculation suggests that H100 would also emit more than one order of magnitude higher carbon than LT.

Outlook

In this perspective, we discuss the potential of photonics to offer a carbon-sustainable solution for DNNs through both lower embodied and operational carbon than CMOS, even under conservative assumptions. This creates a strong call to action for the computing community to prioritize further exploration of the full potential of photonics for sustainable AI. We conclude this perspective by outlining some key research directions as the next steps toward creating a sustainable computing environment with photonics.

Developing a precise ECF model for photonics

The imminent crucial step for leveraging photonics to enable sustainable computing is to comprehensively examine photonic chip fabrication data across the various photonic manufacturing plants, and develop a precise carbon footprint model for photonic chips. The model should encompass information on all relevant components, including fabrication processes, chiplet integration methods, GHG emissions, materials, and packaging. For this to succeed, chip fabrication industries need to come forward and share detailed data on their manufacturing practices and environmental impacts. Open collaboration among industry, academia, and policymakers is vital to creating a transparent and reliable carbon footprint model. An accurate carbon footprint model would not only enable the computing community to maximize the carbon-saving potential of photonics with the right design choices but also promote the growth of photonic technology, making it more applicable and accessible worldwide.

Designing carbon-aware systems with photonics

The absence of a comprehensive carbon footprint model for photonic chips has left current photonic systems unoptimized for carbon efficiency. For example, in the electro-photonic accelerator ADEPT19, more than 80% of the area is occupied by CMOS components, which leads to a huge ECF. Also, in LT23, more than 50% of ECF comes from CMOS. Reducing dependency on CMOS components would be the key to reducing their overall carbon footprint for these accelerators. Some practical steps to reduce this dependency can be as follows.

-

Co-optimizing photonic compute and CMOS components: Co-optimizing photonic compute with supportive CMOS components can reduce the CMOS demand. Co-optimization ideas include reducing SRAM size, sharing data converters among multiple compute units, exploring different dataflow, etc.

-

Photonic-compatible memory: In-memory computing with emerging technologies such as Optically controlled Phase-Change Memory (OPCM) can reduce reliance on CMOS-based memory and enable fast, energy-efficient photonic computing directly within the OPCM cells.36,37.

-

Nonlinear functions with photonics: Implementing nonlinear functions with photonics can significantly reduce dependency on CMOS arithmetic units and data converters. While optical nonlinear units are still limited in efficiency and scale, research into all-optical activation functions is rapidly advancing38.

Furthermore, there exist limitations in operational carbon efficiency in some accelerators as well. For example, DEAP-CNN21 consumes more than 100 W due to the costly modulation process with MRR banks, which leads to a large OCF. Therefore, it is essential to perform a detailed carbon footprint analysis of the existing systems to identify their limitations. We need to address these limitations to develop the next generation of photonic systems with carbon-awareness.

Analyzing the applicability of photonics

Photonic systems may not be carbon-friendly across all application scenarios, particularly for lightweight workloads. In such cases, the CMOS alternatives are often sufficient to meet the performance needs and might be more carbon-sustainable than photonics. For example, for the small AI models for identifying face, voice, activities, or fingerprints in our personal or home devices, where the usage rate is low and high throughput is not required, there are many energy-efficient CMOS accelerators with < 10 mm2 area and mW level power consumption39,40,41. An electro-photonic accelerator, typically with > 100 mm2 area and tens of Watts of power (18,19), would be an overkill for these scenarios. Thus, it is essential to evaluate the interplay between AI model types, usage scenarios, resource constraints, accelerator architectures, and carbon costs to identify where photonics delivers the most carbon benefits.

Dealing with the deployment challenges

Once we clearly determine the potential of photonics to provide carbon savings, the next step will be to deploy electro-photonic computing systems in place of traditional fully CMOS-based computing systems. However, this is not a straightforward task. Completely replacing existing fully CMOS-based systems could result in significant carbon wastage, due to under-utilizing the already invested embodied carbon in those systems. Additionally, since CMOS-based systems are pervasive and capable of performing a wide range of tasks, they cannot be easily substituted with electro-photonic systems in many cases. For example, motivated by the results from our case study between LT and A100, one cannot simply replace all A100 accelerators with LT. This is because the A100 and many other GPUs in the data centers support various tasks, such as handling multiple data types, sparsity optimization, and training, whereas the photonic systems are still in their earlier stages of development. Therefore, there has to be a well-thought-out strategy to replace specific CMOS-based systems and distribute workload between remaining CMOS-based systems and newly deployed electro-photonic systems, ensuring minimal carbon wastage while maximizing resource utilization.

Comparison with analog computing

Analog computing is an emerging paradigm for accelerating AI, aimed at overcoming the memory wall problem. Analog AI accelerators typically adopt Compute-in-Memory (CiM) architectures, where memory cells are used not only to store data but also to perform operations such as matrix-vector multiplications directly within the memory array42. By minimizing data movement between memory and processing units, this approach offers substantial improvements in energy efficiency over traditional von Neumann architectures. Notable examples include43,44,45,46,47, and many more that leverage different types of Non-Volatile Memory (NVM) cells such as RRAM (Resistive Random-Access Memory), FeFET (Ferroelectric Field-Effect Transistor), and PCM (Phase-Change Memory) for both data storage and in-memory computation.

While these accelerators offer strong energy advantages by reducing communication with main memory, they also face several challenges, including limited bit precision, high write energy and latency, device non-ideality, and shorter operational lifetimes. For example, recent DNN models with trillions of parameters may not be a good choice to run on NVM-based analog CiM accelerators. This is because if the full weights of the models do not fit into the CiM accelerator memory, then frequent weight updates would be required, which can cause significant latency and energy consumption, making the CiM accelerator impractical to use. As a result, while NVM-based analog CiM may be preferable for small models with low-precision requirements, electro-photonic accelerators like LT are more suitable for large-scale models that demand both high throughput and high precision. A thorough comparison across various workloads, constraints, and with attention to recent architectural and algorithmic optimizations for LLMs48,49,50-would provide valuable insights for the research community. Additionally, comparison between fabricated electro-photonic accelerators-such as those developed by Lightmatter51 or Lightelligence52-and CiM-based accelerators would be insightful to assess their true relative performance and efficiency.

Analyzing all aspects of sustainability

Reducing carbon emissions from our computing systems is just one aspect of sustainability. Computing systems also have other environmental impacts related to extensive use of Ultra Pure Water (UPW) and waste generation53. The production of UPW consumes substantial energy and produces chemical waste. Additionally, the disposal of obsolete electronic devices contributes to the growing problem of electronic waste (e-waste), which often contains hazardous materials that can percolate into the environment. Beyond the environmental impacts, the changes we make in our hardware directly influence human life in areas like the economy, employment, and overall community progress.

Addressing these interconnected aspects requires collaboration among experts from diverse fields. For example, photonic components are already being utilized in biodegradable medical sensors54,55; building on this, computer architects and material scientists can collaborate to develop, possibly, biodegradable photonic chips for computing to reduce e-waste. Likewise, computer architects can work with economists to assess the cost trade-offs between photonics, and CMOS technologies and explore the potential impacts on employment when the photonics-driven fast AI model computing becomes widely accessible. By fostering interdisciplinary collaboration, we can create innovative solutions that not only reduce the environmental impacts of the computing systems but also drive societal and economic benefits, paving the way for a truly sustainable computing environment.

As AI models become pervasive in various domains like language processing, autonomous driving, and communication, analyzing the sustainability of the underlying hardware is critical to ensure that these technological advancements do not harm our environment. Moving forward, the computing community needs to make sustainability the first-order design constraint, and actively engage in exploring the use of photonics for designing sustainable computing systems.

Data availability

The data for calculating embodied carbon of photonic chips can be obtained from the authors upon request. All other data are publicly available and can be found from the corresponding references.

References

Wu, C.-J. et al. Sustainable ai: Environmental implications, challenges and opportunities. Proc. Mach. Learn. Syst. 4, 795–813 (2022).

The llama 4 herd: The beginning of a new era of natively multimodal ai innovation. https://ai.meta.com/blog/llama-4-multimodal-intelligence/.

Wu, C.-J., Acun, B., Raghavendra, R. & Hazelwood, K. Beyond efficiency: Scaling ai sustainably. IEEE Micro (2024).

Greenhouse gas emissions from a typical passenger vehicle. https://www.epa.gov/greenvehicles/greenhouse-gas-emissions-typical-passenger-vehicle.

Chien, A. A. et al. Reducing the carbon impact of generative ai inference (today and in 2035). In Proceedings of the 2nd workshop on sustainable computer systems, 1–7 (2023).

Tpu v6e. https://cloud.google.com/tpu/docs/v6e.

Nvidia a100 tensor core gpu datsheet. https://www.nvidia.com/en-us/data-center/a100/.

Nvidia h100 tensor core gpu. https://www.nvidia.com/en-us/data-center/h100/.

Firoozshahian, A. et al. Mtia: First generation silicon targeting meta’s recommendation systems. In Proceedings of the 50th Annual International Symposium on Computer Architecture, 1–13 (2023).

Gupta, U. et al. Act: Designing sustainable computer systems with an architectural carbon modeling tool. In Proceedings of the 49th Annual International Symposium on Computer Architecture, 784–799 Introduces the ACT tool to calculate the carbon footprint of CMOS chips, setting a foundation for sustainability-aware system design. (2022).

Gupta, U. et al. Chasing carbon: The elusive environmental footprint of computing. In 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 854–867 (IEEE, 2021). Highlights embodied carbon as a significant contributor to the overall carbon footprint of computing systems.

Wang, J., Gupta, U. & Sriraman, A. Peeling back the carbon curtain: Carbon optimization challenges in cloud computing. In Proceedings of the 2nd Workshop on Sustainable Computer Systems, 1–7 (2023).

Wang, J. et al. Designing cloud servers for lower carbon. In 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA), 452–470 (IEEE, 2024).

Eeckhout, L. Focal: A first-order carbon model to assess processor sustainability. In Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, 401–415 (2024).

Masanet, E., Shehabi, A., Lei, N., Smith, S. & Koomey, J. Recalibrating global data center energy-use estimates. Science 367, 984–986 (2020).

Our world in data. https://ourworldindata.org/energy (2020).

Chen, Y., Xie, Y., Song, L., Chen, F. & Tang, T. A survey of accelerator architectures for deep neural networks. Engineering 6, 264–274 (2020).

Shiflett, K. et al. Albireo: Energy-efficient acceleration of convolutional neural networks via silicon photonics. In 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA), 860–873 (IEEE, 2021).

Demirkiran, C. et al. An electro-photonic system for accelerating deep neural networks. ACM J. Emerg. Technol. Comput. Syst. 19, 1–31 (2023).

Peng, J. et al. A deep neural network accelerator using residue arithmetic in a hybrid optoelectronic system. ACM J. Emerg. Technol. Comput. Syst. (JETC) 18, 1–26 (2022).

Bangari, V. et al. Digital electronics and analog photonics for convolutional neural networks (deap-cnns). IEEE J. Sel. Top. Quantum Electron. 26, 1–13 (2019).

Sunny, F. et al. Reclight: A recurrent neural network accelerator with integrated silicon photonics. In 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 98–103 (IEEE, 2022).

Zhu, H. et al. Lightening-transformer: A dynamically-operated optically-interconnected photonic transformer accelerator. In 2024 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 686–703 (IEEE, 2024). Presents an electro-photonic accelerator for transformer models, which we use in our case study to analyze its carbon footprint.

Demirkiran, C., Yang, G., Bunandar, D. & Joshi, A. Mirage: An rns-based photonic accelerator for dnn training. In 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA), 73–87 (IEEE, 2024).

Alexoudi, T., Kanellos, G. T. & Pleros, N. Optical ram and integrated optical memories: a survey. Light.: Sci. Appl. 9, 91 (2020).

Pintus, P. et al. Integrated non-reciprocal magneto-optics with ultra-high endurance for photonic in-memory computing. Nature Photonics 1–9 (2024).

Fahrenkopf, N. M. et al. The aim photonics mpw: A highly accessible cutting edge technology for rapid prototyping of photonic integrated circuits. IEEE J. Sel. Top. Quantum Electron. 25, 1–6 (2019).

Bardon, M. G. et al. Dtco including sustainability: Power-performance-area-cost-environmental score (ppace) analysis for logic technologies. In 2020 IEEE International Electron Devices Meeting (IEDM), 41–4 (IEEE, 2020).

OP-TEC. Integrated photonics. https://photonics.creol.ucf.edu/wp-content/uploads/sites/4/2019/06/Integrated_Photonics_2016.pdf (2016).

Baker, R. J.CMOS: circuit design, layout, and simulation (John Wiley & Sons, 2019).

Zhang, Z. et al. Adjoint-based particle defect yield modeling for silicon photonics. In Optical Modeling and System Alignment, vol. 11103, 196–205 (SPIE, 2019).

Nvidia h200 tensor core gpu datsheet. https://nvdam.widen.net/s/nb5zzzsjdf/hpc-datasheet-sc23-h200-datasheet-3002446.

Yin, Y. & Yang, Y. Sustainable transition of the global semiconductor industry: Challenges, strategies, and future directions. Sustainability 17, 3160 (2025).

Rollinson, W., Urquhart, A. & Thomson, M. Technoeconomic feasibility of wind and solar generation for off-grid hyperscale data centres. Energies 18, 382 (2025).

Sudarshan, C. C. et al. Eco-chip: Estimation of carbon footprint of chiplet-based architectures for sustainable vlsi. In 2024 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 671–685 (IEEE, 2024). Presents a carbon footprint model of heterogeneous CMOS-based systems.

Yang, G. et al. Processing-in-memory using optically-addressed phase change memory. In 2023 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 1–6 (IEEE, 2023).

Yang, G., Karimi, S., Ocampo, C. A. R., Coskun, A. K. & Joshi, A. Sophie: A scalable recurrent ising machine using optically addressed phase change memory. In 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), 1548–1561 (IEEE, 2024).

Pappas, C. et al. Programmable tanh-, elu-, sigmoid-, and sin-based nonlinear activation functions for neuromorphic photonics. IEEE J. Sel. Top. Quantum Electron. 29, 1–10 (2023).

Chen, Y.-H., Krishna, T., Emer, J. S. & Sze, V. Eyeriss: An energy-efficient reconfigurable accelerator for deep convolutional neural networks. IEEE J. solid-state circuits 52, 127–138 (2016).

Lee, J. et al. Unpu: An energy-efficient deep neural network accelerator with fully variable weight bit precision. IEEE J. Solid-State Circuits 54, 173–185 (2018).

Moons, B., Uytterhoeven, R., Dehaene, W. & Verhelst, M. 14.5 envision: A 0.26-to-10tops/w subword-parallel dynamic-voltage-accuracy-frequency-scalable convolutional neural network processor in 28nm fdsoi. In 2017 IEEE International Solid-State Circuits Conference (ISSCC), 246–247 (IEEE, 2017).

Seo, J.-s et al. Digital versus analog artificial intelligence accelerators: Advances, trends, and emerging designs. IEEE Solid-State Circuits Mag. 14, 65–79 (2022).

Chi, P. et al. Prime: A novel processing-in-memory architecture for neural network computation in reram-based main memory. ACM SIGARCH Comput. Architecture N. 44, 27–39 (2016).

Shafiee, A. et al. Isaac: A convolutional neural network accelerator with in-situ analog arithmetic in crossbars. ACM SIGARCH Comput. Architecture N. 44, 14–26 (2016).

Soliman, T. et al. First demonstration of in-memory computing crossbar using multi-level cell fefet. Nat. Commun. 14, 6348 (2023).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Le Gallo, M. et al. A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference. Nat. Electron. 6, 680–693 (2023).

Kang, M., Shin, H. & Kim, L.-S. A framework for accelerating transformer-based language model on reram-based architecture. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 41, 3026–3039 (2021).

Sridharan, S., Stevens, J. R., Roy, K. & Raghunathan, A. X-former: In-memory acceleration of transformers. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 31, 1223–1233 (2023).

Wolters, C., Yang, X., Schlichtmann, U. & Suzumura, T. Memory is all you need: An overview of compute-in-memory architectures for accelerating large language model inference. arXiv preprint arXiv:2406.08413 (2024).

Ahmed, S. R. et al. Universal photonic artificial intelligence acceleration. Nature 640, 368–374 (2025).

Hua, S. et al. An integrated large-scale photonic accelerator with ultralow latency. Nature 640, 361–367 (2025).

Ruberti, M. The chip manufacturing industry: Environmental impacts and eco-efficiency analysis. Sci. Total Environ. 858, 159873 (2023).

Deng, K. et al. A biodegradable, flexible photonic patch for in vivo phototherapy. Nat. Commun. 14, 3069 (2023).

Wu, X. & Guo, Q. Bioresorbable photonics: materials, devices and applications. In Photonics, vol. 8, 235 (MDPI, 2021).

Acknowledgements

This research was partially funded by the Institute for Global Sustainability (IGS) Graduate Student Summer Fellowship program at Boston University.

Author information

Authors and Affiliations

Contributions

F.F. carried out the research under the guidance of S.P.R., A.J., and U.G. C.D. and D.B. provided domain expertise and constructive feedback across multiple stages of the project. All authors contributed to preparing and refining the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Physics thanks Thomas Van Vaerenbergh, Hangbo Yang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Fayza, F., Demirkiran, C., Papa Rao, S. et al. Photonics for sustainable AI. Commun Phys 8, 403 (2025). https://doi.org/10.1038/s42005-025-02300-0

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s42005-025-02300-0