Abstract

Due to the excellent mechanical, chemical, and electrical properties of third-generation semiconductor silicon carbide (SiC), pressure sensors utilizing this material might be able to operate in extreme environments with temperatures exceeding 300 °C. However, the significant output drift at elevated temperatures challenges the precision and stability of measurements. Real-time in situ temperature monitoring of the pressure sensor chip is highly important for the accurate compensation of the pressure sensor. In this study, we fabricate platinum (Pt) thin-film resistance temperature detectors (RTDs) on a SiC substrate by incorporating aluminum oxide (Al2O3) as the transition layer and utilizing aluminum nitride (AlN) grooves for alignment through microfabrication techniques. The composite layers strongly adhere to the substrate at temperatures reaching 950 °C, and the interface of the Al2O3/Pt bilayer remains stable at elevated temperatures of approximately 950 °C. This stability contributes to the excellent high-temperature electrical performance of the Pt RTD, enabling it to endure temperatures exceeding 850 °C with good linearity. These characteristics establish a basis for the future integration of Pt RTD in SiC pressure sensors. Furthermore, tests and analyses are conducted on the interfacial diffusion, surface morphological, microstructural, and electrical properties of the Pt films at various annealing temperatures. It can be inferred that the tensile stress and self-diffusion of Pt films lead to the formation of hillocks, ultimately reducing the electrical performance of the Pt thin-film RTD. To increase the upper temperature threshold, steps should be taken to prevent the agglomeration of Pt films.

Similar content being viewed by others

Introduction

The aerospace, environmental, and automotive industries are often characterized by harsh environments featuring high temperatures and corrosion conditions. In aeroengines, the temperature and pressure of the combustion chamber can exceed 1000 °C and 1.5 MPa1,2, respectively. Real-time in situ monitoring of temperature and pressure parameters for critical components is highly important for material selection and failure analysis3,4. Traditional discrete devices have high costs and require large installation spaces. It is necessary to develop an on-chip integrated sensor for the simultaneous monitoring of temperature and pressure. Additionally, since conventional silicon-based pressure sensors cannot adapt to high temperatures exceeding 300 °C5,6, the development of high-temperature pressure sensors based on third-generation wide-bandgap semiconductor silicon carbide (SiC) has attracted considerable attention. However, the temperature drift characteristics of SiC-based pressure sensors severely affect the accuracy of the sensor7; thus, it is urgent to carry out the in situ temperature compensation of SiC-based pressure sensors. Based on the aforementioned applications, which involve the in situ monitoring of the temperatures of SiC pressure sensor chips and the compensation of the temperature drift characteristics of pressure sensors, it is necessary to conduct research on temperature sensors based on SiC wafers. This research lays the foundation for the on-chip integration of temperature sensors with SiC pressure sensors. In this paper, a temperature sensor based on SiC that is resistant to high temperatures is proposed for the first time.

There are several studies on the fabrication of temperature sensors using the temperature-sensitive properties of SiC, including thermistors based on SiC thin films and diode temperature detectors based on SiC. These devices can withstand temperatures that do not exceed 600 °C8,9,10,11. However, Pt resistors exhibit high precision and good linearity over a wide temperature range, are not easily oxidized and are easy to integrate with MEMS processes12,13,14,15. Therefore, Pt resistors are selected as the temperature sensing unit in this study. The aims of this paper are to elucidate the preparation processes of Pt RTD on SiC substrates and to explore its high-temperature performance.

When fabricating Pt thin-film resistors, it is common to add a metal adhesion layer, such as chromium, titanium, or tantalum16,17 to prevent the Pt thin film from detaching from the substrate. However, chromium, titanium, and tantalum adhesion layers oxidize or diffuse at 300, 450, and 600 °C, respectively18,19,20,21,22. In particular, the diffusion of the adhesion layer to the Pt film reduces the temperature coefficient of resistance (TCR) of the Pt RTD23,24 and promotes the deterioration of the surface of the Pt film25,26, which decreases its electrical performance and stability. Furthermore, the degradation of the adhesion layer promotes the shedding of the Pt film23, resulting in the direct removal of the Pt resistors. The interface diffusion between platinum (Pt) and the substrate degrades the electrical performance of Pt resistors19,27,28. Therefore, it is crucial to add a suitable intermediate layer between the Pt and the substrate to prevent diffusion between the Pt and the substrate and between the Pt and the intermediate layer to enhance the high-temperature resistance of the Pt.

Herein, a MEMS preparation method based on AlN groove-fixed Pt thin-film RTD using an Al2O3 intermediate layer was proposed. A Pt thin-film RTD was successfully prepared on a SiC substrate, and the interface between the Pt film and the Al2O3 intermediate layer was stable at high temperatures (reaching 950 °C), which promoted the good high-temperature electrical performance of the RTD. The surface morphologies of the Pt films on the SiC substrates at high temperatures, the interfacial diffusion between the Pt film and the substrate, and the electrical properties of the Pt thin-film RTD were examined. Correlations between the electrical properties, changes in the surface morphology, and microscopic stresses of the Pt thin films were established. The reasons for the poor stability and repeatability of Pt RTD were revealed microscopically.

Experimental procedures

Sample preparation

In this work, Al2O3 was proposed as an intermediate layer between the Pt resistor and the SiC substrate. However, due to the weak adhesion between the Pt thin film and the Al2O3 film, which could detach the Pt thin-film resistor, a microfabrication process was developed. This process utilized grooves in the AlN film to securely anchor the Pt thin-film resistors, as illustrated in Fig. 1. Four-inch 4H-SiC substrates, each with a thickness of 350 µm, were purchased from TanKeBlue Semiconductor Co., Ltd. The substrate underwent a series of processes beginning with the deposition of an AlN film via magnetron sputtering (Fig. 1b). Homogenization was achieved using an EPG 535 photoresist (Fig. 1c). ZX-238 solution was used for development after ultraviolet exposure (Fig. 1d). After development, a photolithographic pattern of the Pt resistor shape was formed. Simultaneously, the AlN film was etched by the developer solution, creating grooves in the shape of a Pt resistor. These grooves were used to anchor the Pt thin-film resistors. The process continued with the deposition of the Al2O3 film and Pt film through radio frequency (RF) and direct current (DC) magnetron sputtering, respectively, without breaking the vacuum. The vacuum conditions were maintained at 4.3 ×10−5 Torr with an argon flow rate of 60 sccm, corresponding to a working pressure of 1.36 Pa (Fig. 1e). The divestiture step, which is shown in Fig. 1f, involved removing the photoresist to form Pt thin-film resistors using acetone as the peeling solution. The thickness of the Pt thin-film resistor was less than that of the AlN film. Therefore, the Pt thin-film resistor could be fully anchored within the grooves of the AlN without easily detaching. Thus, Pt thin-film RTDs were successfully prepared on SiC substrates. A schematic diagram of the structure of the Pt thin-film RTD, a physical diagram of a single-chip post-dicing device with dimensions of 7.5 mm × 7.5 mm, and an optical image showing distinct structural features are shown in Fig. 1g. The resistor width was 10 µm, and the linewidth error was less than ±1~2 µm. The chip underwent an annealing process in air with a heating rate of 10 °C/min, as detailed in Fig. 1h, for 1.5 h at various temperatures (650, 750, 850, and 950 °C). This process was followed by furnace cooling. Figure 1i shows the chip mounted on an alumina substrate for subsequent testing. The electrical connection between the chip and the external circuit involved three steps: initially, the chip and a Pt sheet were attached to the alumina substrate using high-temperature cement; then, gold wires were employed for electrical connection between the Pt pad on the chip and the Pt sheet; and finally, a high-temperature conductive silver paste was used to bond the Pt wire to the Pt sheet.

a SiC wafer cleaning using standard RCA procedures; b sputtering of an AlN film on a SiC substrate; c homogenization of photoresists; d lithographic patterning of sensitive resistance strips; e sputtering of Al2O3/Pt; f removal of the photoresist; g image of a single chip; h thermal annealing of the chip in a tube furnace; and i packaging of the chip for performance tests

Characterization

The interfacial diffusion and crystal orientation characteristics of the Pt films were characterized by Lorentz transmission electron microscopy (Talos F200X, Thermo Fisher Scientific, America). The sample was sliced by a focused ion beam (FIB) (Thermo Scientific Helios 5 UX, Thermo Scientific, The Czech Republic) and placed on a copper grid. The copper grid with the sample was inserted into a Lorentz transmission electron microscope and observed in high-angle annular dark field (HAADF) mode. The surface microtopographies of the Pt films were characterized by field-emission scanning electron microscopy (FE-SEM) (su-8010, Hita chi, Japan). The film surface morphology was observed in secondary electron mode with a voltage setting of 10 kV. The cross-sectional micromorphologies and thicknesses of the Al2O3/Pt double-layer films were characterized by FE-SEM (Gemini SEM 500, Zeiss, Germany). The cross-sectional morphology was observed, and the film thickness was measured in InLens mode with a voltage setting of 10 kV. The surface roughnesses of the Pt films were characterized by atomic force microscopy (AFM) (INNOVA, Bruker, America). The tap mode was used during AFM scanning. The scanning area was set to 20 µm × 20 µm. The crystal information of the Pt film was characterized by X-ray diffraction (XRD) (D8 ADVANCE, Bruker, USA). The X-ray source was a copper target with a wavelength of 0.15418 nm. Scanning was conducted in grazing incidence mode. The operating voltage was set to 40 V, with an operating current of 40 mA. The scanning angle ranged from 20° to 90° with a step size of 3417, and each step scan took 0.4 s. The square resistance of the Pt film was characterized by a four-point probe tester (HPS 2526, China). The measurements were conducted in point mode at medium speed. The sample size was 14 mm × 4.5 mm.

Resistivity testing of Pt thin films

The Pt film samples examined for resistivity were from the same batch as those used for RTD, measuring 14 mm × 4.5 mm. The square resistance was characterized by a four-point probe tester, and the thickness was measured by FE-SEM. The resistivity was calculated by the following equation:

where Rsq is the square resistance of the film in units of ohms per square and h is the thickness of the film in nm.

Calculation of the grain size and crystal plane spacing of the Pt thin films

The grain size was estimated using the Scherrer formula29:

The crystal plane spacing was calculated using the Bragg diffraction formula:

where D is the grain size; λ is the X-ray wavelength, and for \({K}_{\alpha }\) of Cu, λ is equal to 0.15406 nm; K is the Scherrer constant, which is equal to 0.89; β is the full width at half maximum; θ is the Bragg diffraction angle; and d is the crystal plane spacing.

High-temperature electrical performance test of Pt thin-film RTD

A programmed high-temperature furnace (SXC-2-13G, Hangzhou Blue Sky Instrument Co., Ltd., China) was utilized to establish a high-temperature testing environment. Nine temperature points ranging from 0 to 800 °C, namely, 25 °C (ambient temperature), 100, 200, 300, 400, 500, 600, 700, and 800 °C, were set, and the heating rate was 5 °C/min. The samples were placed in the furnace, and temperature changes were monitored using an external K-type armored thermocouple. At each temperature point, the duration time was set to 30 min to ensure stable temperature conditions for the tests.

The resistance and temperature were recorded using a DAQ 6510 data collection and recording multimeter system (DAQ 6510, Tektronix, America). During the heating process mentioned above, nine temperature points and the corresponding resistance values were collected as the average of the temperature and resistance when the furnace temperature was stable (i.e., when the temperature error was less than 5%) during the 30-min holding period. The sensitivity and linearity (R2) of the Pt thin-film RTD were calculated. TCR, which is the sensitivity indicator of Pt thin-film RTD, was expressed as follows:

where R0 is the resistance at 0 °C. A larger TCR indicated a higher sensitivity of the Pt thin-film RTD.

Results and discussion

SiC-based Pt thin-film RTDs were annealed at different temperatures to explore the effects of annealing temperature on the interfacial diffusion, stress, surface morphological, and electrical properties and the relationships among micromorphological, microscopic stress, and electrical properties.

Microstructural analysis of Pt thin-film RTDs

Interfacial diffusion analysis

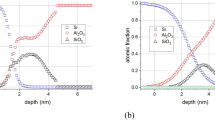

To elucidate the interfacial diffusion between the Pt film and the substrate, the SiC/Al2O3/Pt multilayer slice (after annealing at 950 °C for 1.5 h in air) was observed via Lorentz transmission electron microscopy. As shown in the high-resolution image in Fig. 2a, the cross-section of the Al2O3/Pt multilayer film was clear and smooth. Figure 2b shows the distributions of the various elements on the cross-section, and Fig. 2c–g illustrates the distributions of the elements in the cross-section. As observed from the distributions of Al, O and Pt, no diffusion occurred between the Al2O3 layer and the Pt layer. The interface between the Al2O3 film and Pt film was stable. Figure 2h shows the crystal structures of the alumina film and the Pt film. Figure 2i, j shows the fast Fourier transform (FFT) analyses of high-resolution images of the cross-sections of the Pt thin film and Al2O3 thin film, respectively. The Pt film had (111) and (222) crystal planes, and its (111) crystal plane spacing was 0.2248 nm. However, the Al2O3 film was polymorphic. As demonstrated by the experimental results in this section, no mutual diffusion occurred between the Pt film and the SiC substrate after aging in air at 950 °C for 1.5 h by adding the Al2O3 layer.

a Cross-sectional image of a multilayer film. b Various element distributions across the entire cross-section. c–g Element distribution across the entire cross-section. h Crystal structures of the Al2O3 film and the Pt film. i, j FFT analyses of the high-resolution images of a Pt thin film and an Al2O3 thin film on a cross-section

The thicknesses of the Al2O3 layers were measured at four arbitrary positions, as annotated in Fig. 2a. From left to right, the thicknesses of the Al2O3 were 74.04, 62.02, 66.66, and 74.52 nm. The average thickness was 69.31 nm, with a standard deviation of 5.24 nm. This variation in thickness was attributed to process errors during sputtering of the Al2O3 film, leading to nonuniformity; however, the variation was acceptable. If the Al2O3 layer disappeared, an interfacial reaction occurred between SiC and Pt above 500 °C, resulting in the formation of Pt and Si compounds, which degraded the electrical performance of Pt, as investigated in the literature30,31,32,33,34.

Microtopography analysis

Surface topography characterization and cross-sectional morphology characterization by SEM were performed on Al2O3/Pt films to explore the effect of annealing temperature on the quality of the Pt film. Figure 4a shows that the thickness of the Pt film was 242.7 nm. Figure 4f, which was captured in the backscatter mode of FE-SEM, illustrates the presence of a thin layer of Al2O3 on the SiC substrate. This layer had a thickness of 8.19 nm. As shown in Fig. 3a and Fig. 4a, the surface of the deposited Pt film appeared dense, and the cross-section was dense and uniform, indicating the good quality of the deposited film. After annealing at 650 °C, the surface of the Pt film remained dense, as shown in Fig. 3b. Moreover, the cross-section of the Pt film remained dense and uniform, as shown in Fig. 4b. After annealing at 750 °C, holes began to appear but did not extensively erode the surface of the film, as illustrated in Figs. 4c and 3c. As the annealing temperature increased to 850 °C, the holes completely pierced the Pt film in the thickness direction, as depicted in Fig. 4d. Additionally, the number of holes increased, and microscale ridges and valleys emerged on the surface of the Pt film, as shown in Fig. 3d. As the annealing temperature increased to 950 °C, the holes were enlarged, causing the film to break into islands, as shown in Fig. 3e. This observation aligned with the phenomenon depicted in Fig. 4e, indicating that the holes grew and merged, creating “islands”. Similar results were observed for both Ti/Pt and Ta/Pt films by SL Firebaugh et al.18. It was determined that by increasing the annealing temperature above 750 °C, the surface quality of the Pt film deteriorated. The appearance of holes and islands was caused by the self-diffusion of Pt and thermal stress18.

To evaluate the deterioration of the surface quality of the Pt film and to elucidate the deterioration mechanism, the particle size and pore density with increasing annealing temperature of the film were characterized using AFM. The scanning results are shown in Fig. 5. Table 1 shows the results of the scanning images processed by the NanoScope Analysis software. Ra and Rq represent the absolute mean deviation and the root mean square deviation of the surface roughness, respectively, as listed in Table 1. The smallest Ra and Rq values were observed for the as-deposited films. The film roughness first increased when annealed at 650 °C because of Pt recrystallization and then increased sharply from 750 to 950 °C because of the agglomeration and coalescence of the grains. In addition, the average particle diameter and pore density are provided in Table 1. There were no obvious out-of-plane convex particles on the surfaces of the as-deposited Pt film and the samples annealed at 650 °C. These results were consistent with those shown in Fig. 5a, b. When the annealing temperature reached 750 °C, out-of-plane convex particles and pores appeared on the surface of the film, with an average particle size of 0.111 µm and a pore density of 0.844%. The formation of these bulges and pores were similar to that of holes reported in published articles35,36,37. Holes appeared because the force driving grain growth caused by the annealing temperature of the Pt film was overly high, resulting in film coalescence and agglomeration. Therefore, when the annealing temperature reached 850 °C, the grains of the Pt film quickly coalesced, and some of them formed islands. Furthermore, film agglomeration was obvious, and the pore density increased to 1.14%. When the annealing temperature reached 950 °C, the agglomeration of the film was severe, and the pore density reached 19.88%. Thus, the surface of the Pt film became rough as the annealing temperature increased, resulting in a decrease in the TCR of the Pt thin-film RTD and a decrease in the average linearity of the three R–T curves, as shown in Table S4.

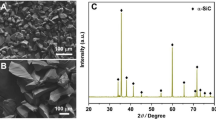

Microstructural analysis

The grain size and crystal plane spacing were obtained from the XRD pattern to microscopically reveal the deterioration mechanism of the surface quality of the Pt film. Figure 6a shows the XRD pattern of the Pt film. The (111) crystal plane was the preferential orientation, and the (111) peak strength increased with increasing annealing temperature. Figure 6b shows that the grain size of the Pt thin film depended on the annealing temperature. The grain size listed in Table 2 was calculated by considering the broadening of the (111) crystal plane according to Eq. 2. For the as-deposited Pt film, the grain size was 35.5 nm. The grain size increased with increasing annealing temperature, from 70.1 nm at 650 °C to 74.6 nm at 750 °C. At 750 °C, the grain size peaked because of secondary recrystallization. After annealing at temperatures greater than 750 °C, the grain size decreased to 52.4 nm at 850 °C and then reached a minimum of 52 nm at 950 °C. The crystal plane spacing d11123 was used to characterize the residual stress in the plane of the Pt film. The in-plane compressive stress led to perpendicular lattice expansion, whereas the in-plane tensile stress led to perpendicular lattice contraction. The changes in d111 with annealing temperature are shown in Fig. 6c. For bulk Pt, the standard d111 was 2.265 Å, while the d111 of the as-deposited Pt film in this study was 2.2556 Å, implying that the as-deposited Pt film experienced tensile stress. This phenomenon differed from the findings in the literature, where the as-deposited Pt films exhibited compressive stress25. The reason for this stress was that the working pressure was greater in this study. The decrease in d111 indicated an increase in stress with increasing annealing temperature. At 750 °C, d111 reached a minimum value of 2.2506 Å, and the residual stress of the Pt film peaked. At this temperature, the residual tensile stress of the Pt film reached the strength limit and was subsequently relieved by plastic deformation. Accordingly, Pt atoms moved along the grain from the interior to the film surface boundary, resulting in the formation of hillocks. Additionally, the Tammann temperature (Tm) of Pt (defined as 0.5 TM, where TM is the melting point of the material, expressed in Kelvin) was approximately 750 °C, at which point self-diffusion occurred for metallic materials. At the microscale, under these conditions, the atomic mobility of the material was high38. As the temperature exceeded 750 °C, the migration of Pt atoms accelerated, resulting in additional pores in the Pt films and the formation of islands. This phenomenon was consistent with the surface topography characterization results of the Pt film. The self-diffusion rate of Pt films was closely related to the temperature, oxygen, and adhesion of the Pt film to the substrate, all of which greatly affected the agglomeration of Pt18. It was inferred that the tensile stress and self-diffusion of Pt films resulted in the formation of hillocks.

Electrical properties of the Pt thin-film RTD

The electrical properties of the Pt thin-film RTD were tested in this section to evaluate the effect of annealing on the sensing performance of the Pt thin-film RTD. The optimal annealing process conditions were obtained.

Effect of thermal annealing on the resistivity of the Pt thin-film RTD

The variations in the square resistance and grain size of the Pt film as functions of annealing temperature are shown in Fig. 7c. The obtained square resistance at each annealing temperature was the average of three independent measurements. Notably, Fig. 7c reveals that annealing temperatures below 750 °C effectively reduced the square resistance of the Pt film. This reduction was accompanied by an increase in the grain size D111. This change suggested a strong correlation between the reduction in the resistivity of the Pt thin film and the growth of its grains. Grain growth is typically associated with the annihilation of voids, a reduction in dislocation density39, and a decrease in grain boundaries40. According to Matthiessen’s rule41, reductions in defects and grain boundaries decreased the resistivity of Pt films. When the annealing temperature exceeded 750 °C, the square resistance of the Pt film began to increase from 1.037 Ω per square at 750 °C to 1.048 Ω per square at 850 °C and reached a maximum of 1.479 Ω per square at 950 °C. This increase in the square resistance was attributed to the agglomeration of Pt film, which deteriorated the surface quality of the film.

a Schematic diagram of the temperature–resistance test platform. b Temperature–resistance test platform built in the laboratory. c Sheet resistance and grain size D111 values of Pt thin films under different annealing temperatures. d Sheet resistance and TCR values of Pt thin films under different annealing temperatures. e–h Temperature–resistance curves and calculated TCRs of Pt thin-films annealed for 1.5 h at different annealing temperatures in air

Effect of thermal annealing on the TCR of the Pt thin-film RTD

The effect of annealing temperature on the TCR of the Pt thin-film RTD was investigated in this section. The samples were annealed in air for 1.5 h at 650 °C, 750 °C, 850 °C and 950 °C. Figure 7a shows a schematic of a high-temperature test platform for Pt thin-film RTD. Figure 7b shows a high-temperature experimental system built in the laboratory for Pt thin-film RTD. The temperature of the furnace was calibrated in the temperature range of 200–900 °C by an external K-type armored thermocouple with an accuracy of 0.034 °C. Figure 7e–h shows the temperature–resistance curves of the Pt thin-film RTD at temperatures ranging from 25 to 850 °C. A total of 12 sensors was used. Every 3 samples with very close resistance values were selected for each annealing temperature (650, 750, 850, and 950 °C) and then tested. Each sensor underwent three heating ramp (HR) tests. Since the differences between the three samples at each annealing temperature were small, the test data of only one sample were provided here. The average TCR, maximum operating temperature, and goodness-of-fit were calculated from the three temperature increase tests, as shown in Table 3. The changes in the TCR of the Pt thin-film RTD with annealing temperature are shown in Fig. 7d. Below 650 °C, the resistivity of the Pt film was inversely proportional to the TCR, as reported in other literature42. Therefore, to obtain an increased TCR, it was necessary to reduce the resistivity of the Pt film. However, due to the appearance of holes and islands in the Pt film at temperatures of at least 750 °C, the resistivity of the Pt film was not related to the TCR. As shown in Table 3 and Fig. 7e–h, annealing generally improved the TCR and linearity of the Pt thin-film RTD. Specifically, with increasing annealing temperature, the TCR reached a maximum value of 2.845 × 10−3/°C at 650 °C. This peak occurred due to the growth of grains and the decrease in the number of grain defects in the Pt film at temperatures below 650 °C. However, the TCR decreased when annealing at 750 °C due to the appearance of pores in the Pt film. During annealing at 850 °C, the TCR was greater than that at 750 °C. One possible reason for this phenomenon was the increased thicknesses of the Pt film islands caused by agglomeration42. For annealing at 750 °C and 950 °C, the repeatability and linearity of the resistance–temperature curves were poor. Considering the data in Table 3 and the repeatability of the Pt thin-film RTD data in Fig. 7, we believed that the optimal annealing temperature for the Pt films was 650 °C, at which point the TCR and linearity of the Pt thin-film RTD were both high.

The Al2O3/Pt bilayer film with a Pt thickness of 242.7 nm that was prepared on a SiC substrate had excellent electrical properties after annealing in air at 650 °C. When the thickness of the Pt film increased, the TCR further increased. Compared with the results reported in previous literature, the Pt thin-film RTD prepared in this study had a wide working range, reaching 850 °C. Additionally, the TCR of the Pt thin-film RTD prepared in this study was higher than that obtained in the same working range, as shown in Fig. 8. The major reason for the difference in this work from the literature was that there was no mutual diffusion between Pt and the substrate.

As seen in the T–R test results in Fig. 7e–g, the Pt thin-film temperature sensor based on the SiC substrate underwent three consecutive heating tests, with temperatures reaching 850 °C. The sensor exhibited a high temperature coefficient of resistance (TCR) and good linearity, indicating its excellent performance in high-temperature environments, which laid the foundation for on-chip integration with SiC pressure sensors for temperature compensation. Based on the high-temperature pressure testing curves of the SiC pressure sensor previously published by our group43, it was evident that the zero-pressure output and full-scale output varied significantly with temperature, indicating significant temperature drift in the pressure sensor. To improve the accuracy of the pressure sensor, it was necessary to monitor the on-chip temperature and perform real-time compensation to eliminate the influence of temperature on the pressure sensor output.

Relationships among microscopic quality, surface morphology, and electrical properties

The relationships among the microscopic stress, surface morphological, and electrical properties of the Pt films are presented in Fig. 9. The optimized performance of the Pt RTD in this study was provided. Notably, the Al2O3/Pt bilayer film prepared in this study maintained interfacial stability at 950 °C in air. Thus, the high-temperature electrical properties of the Pt RTD films were not affected by interfacial diffusion but were only related to surface agglomeration. The surface agglomeration of Pt films appeared in the form of sharp increases in surface roughness, particle size and pore density, which reduced the electrical properties, including resistivity and TCR, and the output linearity of Pt thin-film RTDs. The thermal stress and self-diffusion levels of Pt films were the forces driving film agglomeration. Therefore, reducing the self-diffusion coefficient and reasonably controlling the stress of the film was highly important for reducing agglomeration and improving the high-temperature electrical properties of Pt films RTD.

The Pt thin-film temperature detector based on a SiC substrate developed in this paper laid the foundation for future on-chip integration with SiC pressure sensors, thereby enabling temperature compensation for the pressure sensor. Based on the high-temperature pressure testing results of the SiC pressure sensor in our previously published work43, it was evident that the zero-pressure output and full-scale output varied significantly with temperature, indicating significant temperature drift in the pressure sensor output at high temperatures. To improve the accuracy of the pressure sensor, it was necessary to monitor the on-chip temperature and perform real-time compensation to eliminate the influence of temperature on the pressure sensor output. The Pt thin-film temperature detector in this study was designed to perform temperature monitoring, i.e., in situ temperature monitoring of SiC pressure sensor chips, in the future. When SiC pressure sensors operated in unknown high-temperature environments, temperature fluctuations caused significant drifts in the pressure sensor outputs, reducing the pressure measurement stability and accuracy. Therefore, for temperature compensation, it was necessary to accurately monitor the temperatures of SiC pressure sensor chips and to calibrate and eliminate the effect of temperature on the pressure sensor output to obtain an accurate output value corresponding to the loaded pressure.

Conclusion

In this paper, we proposed a novel microfabrication method for fabricating Pt thin-film RTDs anchored in AlN grooves with additional Al2O3 layers. This fabrication technique successfully produced Pt-film RTDs on SiC substrates. At high temperatures, specifically 950 °C, the Pt thin-film RTD demonstrated strong adhesion to the substrate. The Al2O3/Pt bilayer film developed in this study exhibited a stable interface at 950 °C, which provided a solid basis for the high-temperature electrical performance of the Pt thin-film RTD. The maximum operating temperature exceeded 850 °C, with a TCR of 2.845 × 10−3/°C and high linearity, as demonstrated by the experimental results.

This research established a foundational approach for integrating Pt-film RTDs with SiC pressure sensors on a single chip. Furthermore, in-depth analyses of the changes in interfacial diffusion, microstructure, microscopic stress, and electrical properties of Pt films at various annealing temperatures were provided. This study established relationships between these factors and the electrical performance characteristics of Pt thin-film RTDs. Notably, the Al2O3/Pt bilayer film maintained a stable interface after annealing at 950 °C. There was no evidence of elemental diffusion. Consequently, any deterioration in the surface quality of the Pt film was not attributed to the Al2O3 layer.

The study revealed that below 650 °C, grain recrystallization, and growth reduced the numbers of defects and grain boundaries in the Pt film, thereby decreasing the resistivity and increasing the TCR. The initial stress in the as-deposited Pt film acted as tensile stress, which increased with increasing annealing temperature. At 750 °C, the stress in the Pt film reached its strength limit. At approximately this temperature, close to the Tammann temperature of the Pt film, the Pt atoms exhibited high mobility, leading to the formation of holes in the film. This phenomenon intensified with increasing annealing temperature, eventually resulting in the formation of isolated islands at 950 °C, thereby disrupting the continuity of the film. This deterioration in the surface quality of the Pt film substantially reduced the TCR and linearity of the Pt thin-film RTD. Therefore, the annealing temperature of the film should preferably be below 750 °C. The optimum annealing temperature in this paper was 650 °C. To further enhance the temperature resistance of the Pt film, appropriate measures should be taken to suppress the agglomeration of the Pt film.

References

Kurtz, A. D., Chivers, J. W., Ned, A. A. & Epstein, A. H. Sensor requirements for active gas turbine engine control. In RTO AVT Symposium on “Active Control Technology for Enhanced Performance Operational Capabilities of Military Aircraft, Land Vehicles and Sea Vehicles" 12-1–12-10 (NATO, 2001).

Silva, R. A., Buiatti, C. M., Cruz, S. L. & Pereira, J. A. F. R. Pressure wave behaviour and leak detection in pipelines. Comput. Chem. Eng. 20, S491–S496 (1996).

George, T., Son, K. A., Powers, R. A., Del Castillo, L. Y., & Okojie, R. in In SENSORS. 6.

Zhang, H., Zhu, J., Liang, E. B. & Teng, G. R. Effect of mistuned bladed-disk induced by cracked blades on vibration characteristics of aero-engine. J. Aerosp. Power 28, 2076–2082 (2013).

Hunter, G. W. in 2014 MRS Fall Meeting & Exhibit.

Marsi, N., Majlis, B. Y., Mohd-Yasin, F. & Hamzah, A. A. The capacitance and temperature effects of the SiC- and Si-based MEMS pressure sensor. J. Phys. Conf. Ser. 431, 2022 (2012).

Okojie, R. S., Lukco, D., Chang, C. W. & Savrun, E. in International Conference on Solid-State Sensors, Actuators and Microsystems & Eurosensors XXXIII. 2080–2083.

Nagai, T. & Itoh, M. SiC thin-film thermistors. IEEE Trans. Ind. Appl. 26, 1139–1143 (1990).

Mo, J. et al. A highly linear temperature sensor operating up to 600°C in a 4H-SiC CMOS technology. IEEE Electron Device Lett. 44, 995–998 (2023).

Pascu, R. et al. 60–700 K CTAT and PTAT temperature sensors with 4H-SiC Schottky diodes. Sensors 21, 942 (2021).

Hou, S. B., Hellström, P. E., Zetterling, C.-M. & Östling, M. in Materials Science Forum. 630–633 (Trans Tech Publ).

Ekkels, P., Rottenberg, X., Puers, R. & Tilmans, H. A. C. Evaluation of platinum as a structural thin film material for RF-MEMS devices. J. Micromech. Microeng. 19, 065010 (2009).

Kim, N. H., Na, D. M., Ko, P. J., Park, J. S. & Lee, W. S. Electrical and thermal properties of platinum thin films prepared by DC magnetron sputtering for micro-heater of microsensor applications after CMP process. Solid State Phenom. 124, 267–270 (2007).

Ciftyuerek, E., Sabolsky, K. & Sabolsky, E. M. Platinum thin film electrodes for high-temperature chemical sensor applications. Sens. Actuators B. Chem. 181, 702–714 (2013).

Li, C., Liu, X. Z., Peng, B., Shu, L. & Li, Y. R. AlN-based surface acoustic wave resonators on platinum bottom electrodes for high-temperature sensing applications. Rare Met. 35, 408–411 (2016).

Silvestre, C., Lecursi, N., Moulzolf, S. C., Frankel, D. J. & Lad, R. J. Performance of Zr and Ti adhesion layers for bonding of platinum metallization to sapphire substrates. Sens. Actuators B. 77, 368–374 (2001).

Vittorio et al. Platinum metallization for MEMS application. Biomatter 4, e28822 (2014).

Firebaugh, S. L., Jensen, K. F. & Schmidt, M. A. Investigation of high-temperature degradation of platinum thin films with an in situ resistance measurement apparatus. J. Microelectromech. Syst. 7, 128–135 (1998).

Maeder, T., Sagalowicz, L. & Muralt, P. Stabilized platinum electrodes for ferroelectric film deposition using Ti, Ta and Zr adhesion layers. Jpn. J. Appl. Phys. 37, 4R (1998).

Kneer, E. A., Birnie, D. P., Podlesny, J. C. & Teowee, G. Evolution of surface relief during firing of PZT thin films. Ferroelectrics 152, 67–72 (1994).

Briand, D., Heimgartner, S., Leboeuf, M. & Rooij, N. F. D. Processing influence on the reliability of platinum thin films for MEMS applications. Mrs Online Proc. Libr. Arch. 729, 25 (2002).

Moret, M. P. et al. Damage after annealing and aging at room temperature of platinized silicon substrates. Thin Solid Films 434, 283–295 (2003).

Tiggelaar, R. M., Sanders, R. G. P., Groenland, A. W. & Gardeniers, J. G. E. Stability of thin platinum films implemented in high-temperature microdevices. Sens. Actuators A Phys. 152, 39–47 (2009).

Ababneh, A. et al. Electrical and morphological characterization of platinum thin-films with various adhesion layers for high temperature applications. Microsyst. Technol. 23, 1–7 (2017).

Golosov, D. A. et al. Stability of the platinum electrode during high temperature annealing. Thin Solid Films 661, 53–59 (2018).

Schmid, U. The impact of thermal annealing and adhesion film thickness on the resistivity and the agglomeration behavior of titanium/platinum thin films. J. Appl. Phys. 103, 875 (2008).

Esch, H. et al. The stability of Pt heater and temperature sensing elements for silicon integrated tin oxide gas sensors. Sens. Actuators B Chem. 65, 190–192 (2000).

Courbat, J., Briand, D. & Rooij, N. F. D. Reliability improvement of suspended platinum-based micro-heating elements. Sens. Actuators A. 142, 284–291 (2008).

Zribi, A. et al. Design, fabrication and characterization of thin film resistances for heat flux sensing application. Sens. Actuators A. 245, 26–39 (2016).

Chou, T. Anomalous solid state reaction between SiC and Pt. J. Mater. Res. 5, 601–608 (1990).

Bermudez, V. & Kaplan, R. Investigation of the structure and stability of the Pt/SiC (001) interface. J. Mater. Res. 5, 2882–2893 (1990).

Chou, T. High temperature reactions between SiC and platinum. J. Mater. Sci. 26, 1412–1420 (1991).

Chen, J. et al. Solid-state reaction of Pt thin film with single-crystal (001) β–SiC. J. Mater. Res. 9, 648–657 (1994).

Porter, L., Davis, R., Bow, J., Kim, M. & Carpenter, R. Chemistry, microstructure, and electrical properties at interfaces between thin films of platinum and alpha (6H) silicon carbide (0001). J. Mater. Res. 10, 2336–2342 (1995).

Wang, K., Yao, K. & Chua, S. J. Titanium diffusion and residual stress of platinum thin films on Ti⁄ SiO2⁄ Si substrate. J. Appl. Phys. 98, 3538-1–3538-5 (2005).

Nam, H.-J., Choi, D.-K. & Lee, W.-J. Formation of hillocks in Pt/Ti electrodes and their effects on short phenomena of PZT films deposited by reactive sputtering. Thin Solid Films 371, 264–271 (2000).

Jung, W. W., Choi, S. K., Kweon, S. Y. & Yeom, S. J. Platinum (100) hillock growth in Pt/Ti electrode stack for SrBi2Ta2O9 ferroelectric random access memory. J. Electroceram. 13, 55–63 (2004).

Aubert, T. et al. Behavior of platinum/tantalum as interdigital transducers for SAW devices in high-temperature environments. IEEE Trans. Ultrason., Ferroelectr. Freq. Control 58, 603–610 (2011).

Weihnacht, V. & Brückner, W. Abnormal grain growth in {111} textured Cu thin films. Thin Solid Films 418, 136–144 (2002).

Resnik, D. et al. Microstructural and electrical properties of heat treated resistive Ti/Pt thin layers. Thin Solid Films 639, 64–72 (2017).

Bass, J. Deviations from Matthiessen’s Rule. Adv. Phys. 21, 431–604 (1972).

Zhai, Y. et al. Study on the resistance characteristic of Pt thin film. Phys. Proc. 32, 772–778 (2012).

Wu, C. et al. Exploring the nonlinear piezoresistive effect of 4H-SiC and developing MEMS pressure sensors for extreme environments. Microsyst. Nanoeng. 9, 41 (2023).

Han, J. et al. MEMS-based Pt film temperature sensor on an alumina substrate. Mater. Lett. 125, 224–226 (2014).

Schössler, T., Schön, F., Lemier, C. & Urban, G. Effect of high temperature annealing on resistivity and temperature coefficient of resistance of sputtered platinum thin films of SiO2/Pt/SiOx interfaces. Thin Solid Films 698, 137877 (2020).

Lin, X. et al. The impact of thermal annealing on the temperature dependent resistance behavior of Pt thin films sputtered on Si and Al2O3 substrates. Thin Solid Films 685, 372–378 (2019).

Guarnieri, V., Biazi, L., Marchiori, R. & Lago, A. Platinum metallization for MEMS application: focus on coating adhesion for biomedical applications. Biomatter 4, e28822 (2014).

Garraud, A., Combette, P. & Giani, A. Thermal stability of Pt/Cr and Pt/Cr2O3 thin-film layers on a SiNx/Si substrate for thermal sensor applications. Thin Solid Films 540, 256–260 (2013).

Acknowledgements

The authors are thankful for support from the National Natural Science Foundation of China (Nos. 52175517 and 51720105016), the Zhejiang Laboratory (2022MG0AB03), the China Postdoctoral Science Foundation (No. 2017M610634), the Recruitment Program of Global Experts (Grant No. WQ2017610445), the Innovation Capability Support Program of Shaanxi Province (No. 2021TD-23), and the China National Postdoctoral Program for Innovative Talents (BX20230289). The authors also appreciate the support from the High-Performance Computing Platform and the Analysis and Testing Center of Xi’an Jiaotong University.

Author information

Authors and Affiliations

Contributions

Z.J. and X.F. conceived the idea; Z.F., C.W., and D.Z. designed the device, designed the experiment, and established the experimental setups; and Z.F., X.W., H.Z., and Z.Z. conducted the experiment and completed the testing and data sorting. B.T., L.Z., T.L., P.V., and R.M. initiated, coordinated, and supervised the research. Z.F. and X.F. contributed to the preparation of the paper.

Corresponding authors

Ethics declarations

Conflict of interest

The authors have no conflict of interest to declare.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Fang, Z., Wu, X., Zhao, H. et al. Pt thin-film resistance thermo detectors with stable interfaces for potential integration in SiC high-temperature pressure sensors. Microsyst Nanoeng 10, 133 (2024). https://doi.org/10.1038/s41378-024-00746-w

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41378-024-00746-w

This article is cited by

-

MEMS-based non-dispersive mid-infrared sensor for condition monitoring of lubricants

Microsystem Technologies (2025)