Abstract

Two-dimensional (2D) semiconductors and van der Waals (vdW) heterostructures with graphene have generated enormous interest for future electronic, optoelectronic, and energy-harvesting applications. The electronic transport properties and correlations of such hybrid devices strongly depend on the quality of the materials via chemical vapor deposition (CVD) process, their interfaces and contact properties. However, detailed electronic transport and correlation properties of the 2D semiconductor field-effect transistor (FET) with vdW graphene contacts for understanding mobility limiting factors and metal-insulator transition properties are not explored. Here, we investigate electronic transport in scalable all-2D CVD-grown molybdenum disulfide (MoS2) FET with graphene contacts. The Fermi level of graphene can be readily tuned by a gate voltage to enable a nearly perfect band alignment and, hence, a reduced and tunable Schottky barrier at the contact with good field-effect channel mobility. Detailed temperature-dependent transport measurements show dominant phonon/impurity scattering as a mobility limiting mechanisms and a gate-and bias-induced metal-insulator transition in different temperature ranges, which is explained in light of the variable-range hopping transport. These studies in such scalable all-2D semiconductor heterostructure FETs will be useful for future electronic and optoelectronic devices for a broad range of applications.

Similar content being viewed by others

Introduction

Increasing demand for sustainable and energy-efficient electronics requires novel semiconductor materials on the smallest scales, with an objective to achieve enhanced control over their electronic, chemical and optical properties1,2,3. Presently, conventional silicon technology dominates the semiconductor industry, however, it faces challenges for ultrathin, self-powered, flexible, wearable and implantable integrated electronics3,4,5,6,7. This brings enormous interest in two-dimensional (2D) semiconducting transition metal dichalcogenides (TMDs) such as MoS2 for a wide range of potential applications2,3,4,5,6,7,8,9,10,11. In addition to direct bandgap semiconductors12, near-ideal band alignment, self-passivated dangling-bond-free surfaces, atomically thin bodies and ultrahigh optical absorption coefficients make them potential candidates for ultrathin field-effect transistors (FETs)13, tunnel transistors14, rectifiers15, light-emitting diodes16 and solar energy-harvesting devices17,18. Furthermore, realizing such 2D devices will create unprecedented opportunities in a broad range of industries, from consumer electronics to aerospace19,20,21.

Despite these promising prospects, several challenges must be circumvented for their versatile applications. It remained challenging to form low-resistance contacts with 2D semiconductors22,23, develop appropriate gate dielectrics and gate-electrodes21,24, enhance channel mobility, grow large-area materials, develop scalable encapsulation processes25 and discover reliable doping schemes26 for atomically thin materials. The advantage of their layered structures enables van der Waals (vdW) heterostructures27 without the constraint of lattice matching, offering numerous options for novel device design4. Graphene is a promising monolayer material for 2D semiconductor-based all-2D FETs, demonstrating novel electronic28 and optoelectronic29 functionalities. This includes the use of graphene with 2D semiconductors to demonstrate sub-nm gate length30,31, gate-tunable Schottky barrier32, mitigating Fermi-level pinning for electronics33,34 and solar cells17, highly sensitive photodetection35 and light-matter interactions36. Usually, exfoliated materials33,34,37,38 were used for preliminary investigation, but they are not favorable for industrial implementation. On the other hand, large-area 2D materials via chemical vapor deposition (CVD) process are inevitable for industry-compatible batch fabrication processes and integrated circuits25,39,40,41. However, all-2D CVD-grown 2D semiconductor FETs with graphene contacts are still in their infancy and detailed electronic transport and electron correlation properties of the devices for understanding mobility limiting factors and metal-insulator transition (MIT) properties with temperature are not explored34,42.

Here, we combine CVD-grown 2D semiconductor MoS2 and graphene in vdW heterostructure that offers the possibility to create devices with various functionalities. We demonstrate all-2D MoS2 FET with graphene contacts, which shows low and tunable Schottky barrier and contact resistances, high ON current and good channel mobility. Temperature-dependent transport properties of the all-2D FETs are investigated to understand the evolution of scattering mechanisms for mobility limiting factors and the electronic correlations to explain gate- and bias-induced MIT. These studies on all-2D transistors are useful to optimize the performances for utilization in a broad range of applications at various temperatures.

Device fabrication and material characterization of all-CVD-grown MoS2 FET with graphene contacts

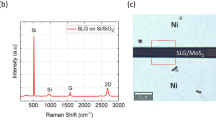

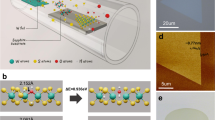

To fabricate MoS2/graphene vdW heterostructure devices, first CVD graphene (grown on Cu foil) is transferred to SiO2/Si substrate. Next, graphene was patterned into stripes by electron-beam lithography (EBL) and O2 plasma etching. Later, the wet transfer technique43 was used to transfer CVD-grown44,45 monolayer MoS2 onto the graphene stripes. Subsequently, e-beam lithography was performed to make metallic contacts on the materials for studying transport properties in the devices (see the Methods for details). Figure 1a, b shows the schematic and fabricated device picture consisting of CVD-grown graphene and MoS2 vdW heterostructure device on SiO2/Si substrate, which is used to apply back gate (Vg). The corresponding band structures of graphene and MoS2 are depicted in Fig. 1c, where graphene possesses semimetallic Dirac band and MoS2 is an n-type semiconductor. In this device geometry, the gate voltage can tune the Fermi level (EF) in both materials and influence the transport properties. Such tuning of EF allows to reduce Schottky barriers that are inevitable for high-performance (opto-) electronic devices. First, we perform a Raman spectroscopy analysis of graphene and MoS2 to investigate the atomic structure after the EBL and wet transfer technique. Figure 1d demonstrates the Raman spectra of bare graphene (bottom panel) and MoS2 (top panel). The higher intensity of the 2D-peak compared to the G-peak with a very small D-peak in the Raman spectrum of graphene indicates the good quality of single-layer graphene46. As expected, the characteristic peaks (E2g and A1g) for single-layer MoS2 are also observed in Raman spectrum analysis47,48.

a Schematic of the MoS2 FET with van der Waals graphene contacts on SiO2/Si substrate. b Optical image of the fabricated heterostructure device of CVD monolayer MoS2 (colored-green triangle) transferred on the CVD graphene stripes. The metallic contacts on graphene are deposited for external electronic connections for electrical measurements. The scale bar is 10 μm, and the average channel width and length are 10.75 μm and 11 μm, respectively. c Band diagram of graphene and n-type MoS2 along with associated Fermi levels (EF) in these materials that are tunable via gate voltage (Vg). d Raman spectra of single-layer CVD graphene and MoS2 using 638 nm LASER. e Gate-dependent resistivity of graphene channels in heterostructure and pristine regions, probed with four-terminal measurement geometry. f MoS2 FET characterization with conventional metallic contacts showing Ids vs. Vg at Vds = 1 V in linear and logarithmic scale. All the measurements are conducted at room temperature. The device micrograph is in the inset, and the scale bar is 10 μm. The channel length and width are 1.4 μm and 12 μm.

We performed electrical characterization of the individual materials to inspect the transport properties after going through the fabrication processes. Figure 1e presents the gate-dependent resistivity of the graphene channels in graphene-MoS2 heterostructure and pristine regions. The Dirac points of graphene in the graphene-MoS2 heterostructure and pristine regions are 8 V and 15 V, respectively. We estimated the maximum field-effect mobility33 (\(\mu =\frac{L{g}_{m}}{W{C}_{g}{V}_{{ds}}}\)) of graphene channels is about 1260 cm2 V−1 s−1 in the graphene-MoS2 heterostructure region and 900 cm2 V−1 s−1 in the pristine region. Here, L, W, Cg, and gm are channel length, width, gate capacitance per area (1.15 × 10-8 Fcm−2) and transconductance, respectively. Higher μ of the graphene channel in the heterostructure region with respect to the pristine region can be due to the protection of the graphene channel from residues with top MoS2 during the fabrication processes. Next, the source-drain current (Ids) vs. gate voltage (Vg) of MoS2 with metallic contacts at Vds = 1 V in linear and logarithmic scale are depicted in Fig. 1f. Here, the Ids increases with applying Vg towards positive value due to an upsurge of electron concentration in the channel, agreeing to the n-type transport mechanism in our CVD-grown MoS2 material. The estimated μ = 1.9 cm2 V−1s−1, on-off ratio in this FET is about 106, threshold voltage (Vth) = 5.5 V and subthreshold swing (SS) = 1.42 V/dec. These preliminary electrical properties of the graphene channels and MoS2 crystal imply hitherto the good quality of heterostructure devices, and the adapted wet transfer technique does not erode the phenomenal electrical transport properties of the materials.

Room temperature transport properties of all-CVD MoS2 FET with vdW graphene contacts

The detailed transport properties of all-2D CVD MoS2 transistors with graphene contacts are measured. Figure 2a shows the schematic of the fabricated MoS2 FET with graphene contacts on the Si/SiO2 substrate along with the measurement geometry. Current-voltage (I–V) properties at various Vg are presented in Fig. 2b. Channel current (Ids) increases with increasing Vg due to an increase of carrier concentration in the MoS2 channel and the I-V is slightly non-linear at higher Vg, which can be due to the long channel length (~ 11 µm) of MoS2 and the vdW gap in the contact region42. Transfer properties (Ids vs. Vg) at different Vds are shown in Fig. 2c and the inset of Fig. 2c shows the Ids as a function of Vg with Vds = 1 V in a logarithmic scale. We find the Vth = -35 V, the on-off ratio is ~105, subthreshold swing, SS = 5.88 V/dec and mobility, μ = 14.5 cm2 V−1 s−1 in this all-2D FET.

a Schematic representation of the MoS2 FET with graphene contacts. b Ids vs. Vds at various Vg of the MoS2 FET with graphene contacts. c Ids vs. Vg at different Vds (0.5 V to 1 V) of the MoS2 FET with graphene contacts. The inset shows the transfer properties in the MoS2 FET with graphene contacts at Vds = 1 V in logarithmic scale along with a linear fitting to estimate subthreshold swing.

It can be noticed that the MoS2 FET characteristic did not reach the off-saturation limit while decreasing gate voltage (−Vg), as shown in the inset of Fig. 2c. This could affect the calculation of on-off ratio and SS. It is to be mentioned that we took into account the non-uniform shape of the MoS2 for mobility extraction. We approximated the channel width by averaging the channel width at the source and drain electrodes and considered the distance between the two electrodes as the channel length. Overall, we observed higher Ids and μ, and lower Vth in the MoS2 FET with graphene electrodes (Fig. 2c) with respect to the one with evaporated metallic electrodes (Fig. 1f). The performance enhancement of the MoS2 FET with graphene electrodes could be due to the absence of Fermi-level pinning in the interface between the MoS2 channel and graphene contacts49.

Gate-tunable Schottky barrier and mobility in the all-2D CVD MoS2-graphene heterostructure FET

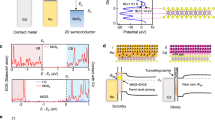

Temperature-dependent transport properties of MoS2 FET with graphene contacts (shown schematically in Fig. 3a) are investigated to understand device performance. The transport characteristic curves (Ids vs. Vg) are shown in Fig. 3b from 70 K to 300 K at Vds = 1 V. At this temperature (T) range with this applied Vds, the transfer properties show insulating behavior, where Ids decreases with decreasing temperature. The thermionic emission model is used to estimate the Schottky barrier (SB) height in this heterostructure junction, and the Arrhenius plots of ln(Ids/T3/2) vs. 1000/T at different Vg are shown in Fig. 3c22,50,51,52,53. Figure 3d depicts the estimated SB at different Vg at Vds = 1 V. The flat-band SB is found to be 52 meV at around Vg = 13 V. The SB decrease with increasing Vg, and at Vg ≥ 30 V the calculation deviates from the thermionic emission model, limiting further estimation of SB.

a Schematic of all-CVD-grown MoS2-graphene vdW heterostructure FET device and measurement geometry. b Ids vs. Vg plots at Vds = 1 V of the CVD MoS2 FET with vdW graphene contacts. b Ids vs. Vg at different temperatures with Vds = 1 V. c Arrhenius plots of ln(Ids/T3/2) vs. 1000/T at different Vg. d Estimated Schottky barrier at different Vg. e A pictorial illustration of band alignment to explain the reduction of the Schottky barrier at different Vg. In this measurement geometry, Vg changes the Fermi-level in graphene and MoS2 simultaneously and modulates band structure accordingly from depletion to inversion region through the flat-band condition. f Estimated mobility (μ) at different temperatures with power law (\(\mu \,\propto \,{T}^{\gamma }\)) fitting (solid lines) in the all-CVD MoS2 FET with graphene contacts.

Here, the applied Vg modulates the Fermi level (EF) of graphene and MoS2 simultaneously. Figure 3e shows the illustration of the band alignment of MoS2-graphene FET to explain the gate modulation of SB. When Vg is lower (≤7 V), graphene electrodes are p-doped and the MoS2 channel is in the off state, giving rise to a higher SB height. However, with increasing Vg, EF in graphene electrodes moves toward the conduction band (CB), and in MoS2, it moves towards Ec. At Vg = 13 V, the flat-band condition is reached (Fig. 3e, middle panel). Increasing Vg further moves the EF in graphene into the CB and in MoS2, EF moves nearer to Ec. At Vg > 13 V, inversion in MoS2 takes place and graphene shows accumulation contact properties37,54.

To understand the mobility limiting factors in the all-2D CVD MoS2 FET with graphene contacts, we estimated the mobility (μ) at different temperatures (T). The extracted μ at different T are shown in Fig. 3f along with a power law (\(\mu \,\propto \,{T}^{\gamma }\)) fitting (solid line)55,56. In this device at the lower T range (T ≤ 230 K), a slight change of μ with T is observed (γ ≈ 0.1) due to impurity scattering. At the higher T range (T ≥ 230) K, μ decreases drastically with T (γ ≈ −1) due to dominant phonon scattering55,56.

Gate- and bias-induced metal-to-insulator transition in all-CVD MoS2 FET with graphene contacts

To examine the responsible transport mechanisms, we further investigated the temperature-dependent transport properties of the all-CVD MoS2 FET with graphene contacts at various applied biases (Vds). The transport properties and corresponding color contour plots at different temperatures for various Vds are depicted in Fig. 4a, b, respectively. The transport properties show insulating behavior at Vds = 1 V in this temperature range at all Vg. In the insulating regime, Ids increases with increasing T, and it can be observed in Fig. 4b (top panel) that the highest Ids is observed at higher T = 300 K. Interestingly, at the higher Vds (5 and 10 V), temperature-dependent transport shows similar characteristics. At the higher Vg (>60 V) and high T range (200–300 K), it shows metallic properties (Ids decreases with increasing T), as shown in the bottom two panels in Fig. 4a, b. However, it shows insulating properties at lower Vg (<60 V) and lower T range (70–200 K). This kind of partial metal-to-insulator transition (MIT) at the higher Vg and Vds in the all-CVD MoS2 FET with graphene contacts is interesting because usually, MIT is observed in the MoS2 FET with metallic contacts at the higher Vg and Vds in a broad temperature spectrum57.

a, b Measured temperature-dependent transfer characteristics and corresponding color contour plots of the all-CVD MoS2 FET with vdW graphene contacts at Vds = 1 V, 5 V, and 10 V, respectively. c Estimated hopping parameter, ξ, as a function of Vg for the MoS2 FET with vdW graphene contacts at various Vds. d Deformation of hopping potential barrier of the MoS2 channel at low and high biases.

Next, we correlated the gate- and bias-induced partial-MIT transport phenomena of the all-CVD MoS2 FET with graphene contacts to a 2D variable-range hopping (VRH) model. This model accounts for transport carriers hopping through the trap states in the channel, such as defects in the MoS2 crystal structure and trap sites at the MoS2/SiO2 and MoS2/graphene interfaces. According to the VRH model58,59, the conductance (σ) can be written as

where A is constant, T0 is a hopping parameter related to characteristics temperature, \({\rm{\gamma }}\) = 1/3 for charge transport that takes place in a wide (>>kbT) band of localized states and m is between −1 and −0.8. The Arrhenius plots of ln σT0.8 vs. T−1/3 in the all-CVD MoS2 FET with vdW graphene contacts are shown in Supplementary Fig. S1 for various Vds to estimate T0. Previous reports on 2D materials showed 2D VRH transport and gate- and bias-induced MIT phenomena, where the localization length (ξ2 ∝ 1/T0, see the equation 1 in the Supplementary Information) increases due to an efficient screening of the potential of trap states at higher carrier density57,58,59,60. The estimated ξ at different gate voltages with Vds = 1 V, 5 V, and 10 V are depicted in Fig. 4c. It is conspicuous that ξ increases linearly to 25 nm with Vg at Vds = 1 V, but at higher Vds = 5 V and 10 V, ξ increases upto 50 nm and partial-MIT emerges.

Overall, high ξ values at the higher T range (>200 K) indicate unlocalized transport in the MoS2 channel, where the carriers hop through unlocalized states, resulting in metallic transport within this T range. On the other hand, in the insulating regime, the carriers hop through localized potential barriers, as illustrated in Fig. 4d. At the elevated bias and high carrier concentration (Vg), the effective potential barrier of the trap states reduces, giving rise to the screening of potential trap sites that results in metallic transport with temperature in the all-CVD FET. However, the exact origin and mechanism of bias- and gate-induced MIT in 2D materials are yet to be well understood. Recently, the percolation-mediated 2D VRH model has been used to explain MIT in 2D semiconductors57. Furthermore, conductivity and temperature scaling behavior are also used to illustrate MIT due to the quantum-phase transition61,62. However, the demonstration of such scaling behavior does not unequivocally certify the corresponding effect for MIT observation because of the presence of other factors like weak localization, trap sites, and heating effects along with intermediate carrier density that can influence the transport mechanism58. Further theoretical insights, along with this experimental observation, can unveil the exact origin of the gate- and bias-induced MIT in such 2D semiconductors.

Summary and outlook

We demonstrated all-2D CVD-grown 2D FETs by combining scalable semiconductor MoS2 channel with graphene contacts. We confirmed that the CVD-grown 2D materials can endure complex fabrication processes and exhibit good charge transport properties. We observed the ease of Fermi-level tunability of graphene contacts to MoS2 via gate voltage, achieving appropriate band alignment, tunable Schottky barrier and improved channel mobility. Our comprehensive temperature-dependent transport measurements have shed light on the impurity and phonon mediated mobility limiting factors. Additionally, we observed gate- and bias-induced partial metal-insulator transitions due to the variable-range hopping mechanism in the all-2D CVD-grown FET. Utilizing graphene contacts overcomes Fermi-level pinning and enhances the transport properties of MoS2 FET with promising implications for sustainable electronics, optoelectronics and energy-harvesting devices. Further development of such high-performance scalable CVD-grown 2D FETs can pave the way for ultrathin, flexible, transparent, wearable, implantable and self-powered electronics.

Methods

The all-2D field-effect transistor was fabricated using all-CVD-grown monolayer graphene (from Graphenea) and MoS2 heterostructures. The four-inch wafer-scale CVD graphene grown on Cu foil is transferred onto a highly doped SiO2/Si (thermally grown 285 nm thick) substrate. First, graphene contacts were patterned by electron-beam lithography and oxygen plasma etching and cleaned afterwards by acetone and IPA. The CVD-grown monolayer MoS2 layers of triangular shape with a typical size of about 50–100 μm were grown by the CVD process as described in George, A. et al.44,45. on a SiO2 (300 nm)/Si substrate. A wet-transferred technique was employed to transfer CVD MoS2 on top of CVD graphene contacts43. An appropriate heterostructure region was identified by an optical microscope for device fabrication. We used EBL to define the contacts and e-beam evaporation for depositing 1 nm TiO2/80 nm Co, followed by the lift-off process in warm acetone at 65 °C. The use of such contacts is motivated by the observation of the lower Schottky barrier at the MoS2-metal interface50,51 and for spin transport studies63. The tunnel contacts are used to characterize only MoS2 materials and the all-2D CVD MoS2 is studied with graphene contacts. It is to be noted that no annealing was performed in the devices presented in this manuscript, but we believe that proper annealing, passivation and encapsulation can further improve the transport properties of the devices64,65. The highly doped SiO2/Si is used as a back gate. We used Keithley 2612B dual channel source meter to apply bias and back gate voltages and to measure channel current. The transport measurements were conducted in a vacuum cryostat.

Data availability

The data that support the findings of this study are available from the corresponding authors on a reasonable request.

References

Tan, T., Jiang, X., Wang, C., Yao, B. & Zhang, H. 2D material optoelectronics for information functional device applications: status and challenges. Adv. Sci. 7, 2000058 (2020).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Wei, T. et al. Two dimensional semiconducting materials for ultimately scaled transistors. iScience 25, 105160 (2022).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Wang, S., Liu, X. & Zhou, P. The road for 2D semiconductors in the silicon age. Adv. Mater. 34, 2106886 (2022).

Huang, X., Liu, C. & Zhou, P. 2D semiconductors for specific electronic applications: from device to system. Npj 2D Mater. Appl 6, 1–19 (2022).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Shrivastava, M. & Ramgopal Rao, V. A roadmap for disruptive applications and heterogeneous integration using two-dimensional materials: state-of-the-art and technological challenges. Nano Lett. 21, 6359–6381 (2021).

Zhang, Q., Liu, C. & Zhou, P. 2D materials readiness for the transistor performance breakthrough. iScience 26, 106673 (2023).

Xia, F., Wang, H., Xiao, D., Dubey, M. & Ramasubramaniam, A. Two-dimensional material nanophotonics. Nat. Photonics 8, 899–907 (2014).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 1–15 (2016).

Kanungo, S., Ahmad, G., Sahatiya, P., Mukhopadhyay, A. & Chattopadhyay, S. 2D materials-based nanoscale tunneling field effect transistors: current developments and future prospects. Npj 2D Mater. Appl 6, 1–29 (2022).

Zhang, X. et al. Near-ideal van der Waals rectifiers based on all-two-dimensional Schottky junctions. Nat. Commun. 12, 1522 (2021).

Choi, M. et al. Flexible active-matrix organic light-emitting diode display enabled by MoS2 thin-film transistor. Sci. Adv. 4, eaas8721 (2018).

Nassiri Nazif, K. et al. High-specific-power flexible transition metal dichalcogenide solar cells. Nat. Commun. 12, 7034 (2021).

Das, S., Pandey, D., Thomas, J. & Roy, T. The role of graphene and other 2D materials in solar photovoltaics. Adv. Mater. 31, 1802722 (2019).

Kumbhakar, P. et al. Prospective applications of two-dimensional materials beyond laboratory frontiers: a review. iScience 26, 106671 (2023).

Zhao, B. et al. A room-temperature spin-valve with van der waals ferromagnet Fe5GeTe2/graphene heterostructure. Adv. Mater. 35, 2209113 (2023).

Chakraborty, S. K., Kundu, B., Nayak, B., Dash, S. P. & Sahoo, P. K. Challenges and opportunities in 2D heterostructures for electronic and optoelectronic devices. iScience 25, 103942 (2022).

Zhang, P. et al. Contact engineering for two-dimensional semiconductors. J. Semicond. 41, 071901 (2020).

Karpiak, B. et al. 1D ferromagnetic edge contacts to 2D graphene/h-BN heterostructures. 2D Mater. 5, 014001 (2017).

Schram, T., Sutar, S., Radu, I. & Asselberghs, I. Challenges of wafer-scale integration of 2D semiconductors for high-performance transistor circuits. Adv. Mater. 34, 2109796 (2022).

Quellmalz, A. et al. Large-area integration of two-dimensional materials and their heterostructures by wafer bonding. Nat. Commun. 12, 917 (2021).

Lee, D. et al. Remote modulation doping in van der Waals heterostructure transistors. Nat. Electron. 4, 664–670 (2021).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Castro Neto, A. H. 2D materials and van der Waals heterostructures. Science 353, aac9439 (2016).

Geim, A. K. & Novoselov, K. S. The rise of graphene. Nat. Mater. 6, 183–191 (2007).

Nair, R. R. et al. Fine structure constant defines visual transparency of graphene. Science 320, 1308–1308 (2008).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Wang, J. et al. High mobility MoS2 transistor with low schottky barrier contact by using atomic thick h-BN as a tunneling layer. Adv. Mater. 28, 8302–8308 (2016).

Tian, H. et al. Novel field-effect Schottky barrier transistors based on graphene-MoS2 heterojunctions. Sci. Rep. 4, 5951 (2014).

Kim, T., Fan, S., Lee, S., Joo, M.-K. & Lee, Y. H. High-mobility junction field-effect transistor via graphene/MoS2 heterointerface. Sci. Rep. 10, 13101 (2020).

Roy, K. et al. Graphene–MoS2 hybrid structures for multifunctional photoresponsive memory devices. Nat. Nanotechnol. 8, 826–830 (2013).

Mueller, T. & Malic, E. Exciton physics and device application of two-dimensional transition metal dichalcogenide semiconductors. Npj 2D Mater. Appl 2, 1–12 (2018).

Qiu, D. & Kim, E. K. Electrically tunable and negative schottky barriers in multi-layered graphene/MoS2 heterostructured transistors. Sci. Rep. 5, 13743 (2015).

Du, Y. et al. MoS2 field-effect transistors with graphene/metal heterocontacts. IEEE Electron Device Lett. 35, 599–601 (2014).

Choi, S. H. et al. Large-scale synthesis of graphene and other 2D materials towards industrialization. Nat. Commun. 13, 1484 (2022).

Xu, X. et al. Growth of 2D materials at the Wafer scale. Adv. Mater. 34, 2108258 (2022).

Cai, Z., Liu, B., Zou, X. & Cheng, H.-M. Chemical vapor deposition growth and applications of two-dimensional materials and their heterostructures. Chem. Rev. 118, 6091–6133 (2018).

Ciampalini, G. et al. Unexpected electron transport suppression in a heterostructured graphene–MoS2 multiple field-effect transistor architecture. ACS Nano 16, 1291–1300 (2022).

Winter, A. et al. Lateral heterostructures of two-dimensional materials by electron-beam induced stitching. Carbon 128, 106–116 (2018).

George, A. et al. Controlled growth of transition metal dichalcogenide monolayers using Knudsen-type effusion cells for the precursors. J. Phys. Mater. 2, 016001 (2019).

Shree, S. et al. High optical quality of MoS2 monolayers grown by chemical vapor deposition. 2D Mater. 7, 015011 (2019).

Malard, L. M., Pimenta, M. A., Dresselhaus, G. & Dresselhaus, M. S. Raman spectroscopy in graphene. Phys. Rep. 473, 51–87 (2009).

Li, F. et al. Anomalous lattice vibrations of CVD-grown monolayer MoS2 probed using linear polarized excitation light. Nanoscale 11, 13725–13730 (2019).

Yang, L. et al. Lattice strain effects on the optical properties of MoS2 nanosheets. Sci. Rep. 4, 5649 (2014).

Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Chen, J.-R. et al. Control of schottky barriers in single layer MoS2 transistors with ferromagnetic contacts. Nano Lett. 13, 3106–3110 (2013).

Dankert, A., Langouche, L., Kamalakar, M. V. & Dash, S. P. High-performance molybdenum disulfide field-effect transistors with spin tunnel contacts. ACS Nano 8, 476–482 (2014).

Dankert, A. & Dash, S. P. Electrical gate control of spin current in van der Waals heterostructures at room temperature. Nat. Commun. 8, 16093 (2017).

Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 12, 246–252 (2013).

Yu, L. et al. Graphene/MoS2 hybrid technology for large-scale two-dimensional electronics. Nano Lett. 14, 3055–3063 (2014).

Ovchinnikov, D., Allain, A., Huang, Y.-S., Dumcenco, D. & Kis, A. Electrical transport properties of single-layer WS2. ACS Nano 8, 8174–8181 (2014).

Radisavljevic, B. & Kis, A. Mobility engineering and a metal–insulator transition in monolayer MoS2. Nat. Mater. 12, 815–820 (2013).

Moon, B. H. et al. Anomalous conductance near percolative metal–insulator transition in monolayer MoS2 at low voltage regime. ACS Nano 13, 6631–6637 (2019).

Patil, P. D. et al. Gate-induced metal–insulator transition in 2D van der Waals layers of copper indium selenide based field-effect transistors. ACS Nano 13, 13413–13420 (2019).

Ghatak, S., Pal, A. N. & Ghosh, A. Nature of electronic states in atomically thin MoS2 field-effect transistors. ACS Nano 5, 7707–7712 (2011).

Chen, X. et al. Probing the electron states and metal-insulator transition mechanisms in molybdenum disulphide vertical heterostructures. Nat. Commun. 6, 6088 (2015).

Moon, B. H., Han, G. H., Radonjić, M. M., Ji, H. & Dobrosavljević, V. Quantum critical scaling for finite-temperature Mott-like metal-insulator crossover in few-layered MoS2. Phys. Rev. B 102, 245424 (2020).

Moon, B. H. et al. Soft Coulomb gap and asymmetric scaling towards metal-insulator quantum criticality in multilayer MoS2. Nat. Commun. 9, 2052 (2018).

Hoque, A. M. D. et al. Spin-valley coupling and spin-relaxation anisotropy in all-CVD graphene-MoS2 van der Waals heterostructure. Phys. Rev. Mater. 7, 044005 (2023).

Lee, G.-H. et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano 9, 7019–7026 (2015).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Acknowledgements

The authors acknowledge financial support from 2D TECH VINNOVA competence center (No. 2019-00068), FlagEra project H2O and MagicTune (funded by VR), European Union Graphene Flagship project 2D Materials of Future 2DSPIN-TECH (No. 101135853), Wallenberg Initiative Materials Science for Sustainability (WISE) funded by the Knut and Alice Wallenberg Foundation, EU Graphene Flagship (Core 3, No. 881603), Swedish Research Council VR project grants (No. 2021–04821, 2018-07046), FLAG-ERA project 2DSOTECH (VR No. 2021–05925), Graphene center, AoA Nano, AoA Materials and AoA Energy programs at Chalmers University of Technology. This research was also supported by the Deutsche Forschungsgemeinschaft through SPP2244 “2D Materials—Physics of van der Waals [hetero]structures” (TU149/21-1, Project No. 535253400) and through the individual research grant TU149/16-1, Project No. 464283495. This work was performed in part at Myfab Nanofabrication facility at Chalmers. We acknowledge the help of staff at the Quantum Device Physics Laboratory and Nanofabrication Laboratory in our Department of Microtechnology and Nanoscience at the Chalmers University of Technology. This work was performed in part at Myfab Chalmers.

Funding

Open access funding provided by Chalmers University of Technology.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Hoque, M.A., George, A., Ramachandra, V. et al. All-2D CVD-grown semiconductor field-effect transistors with van der Waals graphene contacts. npj 2D Mater Appl 8, 55 (2024). https://doi.org/10.1038/s41699-024-00489-2

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41699-024-00489-2

This article is cited by

-

Novel vertical contact architecture for significantly reduced contact resistance in 2D nanosheet FETs

npj 2D Materials and Applications (2025)