Abstract

Silicon photonic switches are widely considered as a cost-effective solution for addressing the ever-growing data traffic in datacenter networks, as they offer unique advantages such as low power consumption, low latency, small footprint and high bandwidth. Despite extensive research efforts, crosstalk in large-scale photonic circuits still poses a threat to signal integrity. In this paper, we present two designs of silicon Mach-Zehnder Interferometer (MZI) switches achieving ultra-low-crosstalk, driven thermally and electrically. Each switch fabric is optimized at both the device and circuit level to suppress crosstalk and reduce system complexity. Notably, for the first time to the best of our knowledge, we harness the inherent self-heating effect in a carrier-injection-based MZI switch to create a pair of phase shifters that offers arbitrary phase differences. Such a pair of phase shifters induces matched insertion loss at each arm, thus minimizing crosstalk. Experimentally, an ultra-low crosstalk ratio below −40 dB is demonstrated for both thermo-optic (T-O) and electro-optic (E-O) switches. The T-O switch exhibits an on-chip loss of less than 5 dB with a switching time of 500 µs, whereas the E-O switch achieves an on-chip loss as low as 8.5 dB with a switching time of under 100 ns. In addition, data transmission of a 50 Gb/s on–off keying signal is demonstrated with high fidelity on the E-O switch, showing the great potential of the proposed switch designs.

Similar content being viewed by others

Introduction

Recent years have seen the explosive growth of data traffic in both intra- and inter-datacenter networks, driven by the proliferation of data-intensive applications such as artificial intelligence (AI), cloud computing, and live streaming1. This escalating demand for optical interconnects has propelled advancements in optical switching technologies, taking advantage of their low power consumption, low latency, high bandwidth, and the elimination of optical-electrical conversions2. It is widely recognized that the future datacenter network architectures would be greatly benefited from optical circuit switching technologies, together with electrical packet switching3. To date, a variety of optical switches have been demonstrated based on different material systems and fabrication techniques, such as microelectromechanical systems (MEMS)4,5, liquid crystal6, lithium niobate (LiNbO3)7, III–V compounds8,9, silicon nitride (SiN)10,11, and silicon-on-insulator (SOI)12,13. Among these, the SOI platform is distinguished by its compact footprint, high-efficiency phase tuning, and most importantly, the compatibility of the complementary metal-oxide-semiconductor (CMOS) process for mass-production. Silicon exhibits a strong thermo-optic (T-O) coefficient (1.8 × 10−4 K−1), however, it does not possess linear electro-optic effects and its quadratic effects are very weak. The free-carrier dispersion (FCA) effect through carrier injection or depletion offers the best all-silicon electro-optic (E–O) solution.

Silicon switches typically rely on interferometric structures, such as micro-ring resonators (MRRs) or Mach-Zehnder interferometers (MZIs) that are actuated by either T-O or E-O phase-shifting effect. In contrast to the MRR-based switches that are usually specialized for wavelength-selective routing, MZI switches offer broader bandwidths, relaxed fabrication requirements, and simplified control schemes14. Yet, their performance still falls short for practical adoptions, mainly on the aspects of insertion loss and coherent crosstalk. There are viable solutions on solving the switch loss by introducing additional gain blocks, via either monolithically or heterogeneously integrations, such as flip-chip bonding15,16 and micro-transfer printing17. The crosstalk, on the other hand, represents a trickier issue to tackle, given the inevitable fabrication variations, inherent deficiency in switch topologies, and the most-challenging electro-absorption loss in E-O designs. This is particularly pronounced for large-scale switches, where the cumulative effect of crosstalk is more severe, considerably jeopardizing signal integrity18.

Generally, the switch crosstalk is bounded by the fabrication imperfections in 3-dB couplers, where a slight deviation from the 50:50 splitting ratio could largely deteriorate the crosstalk. For example, 2% and 5% deviations could degrade the crosstalk ratio to below −28 dB and −20 dB, respectively19. For E-O switching, the situation gets worse due to the inherent electro-absorption loss on carrier injections. Current solutions for addressing these issues include employing a dilated topology to eliminate first-order crosstalk20, implementing extra MZI stages as variable splitters21,22, and applying nested MZI structures to improve power balance23,24,25. These approaches, however, all trade against the number of components, and thus resulting in larger device footprint and higher complexity. Thus, these demonstrations are more applicable to modest port count devices.

In this paper, we present two designs of silicon switches driven both thermally and electrically with ultra-low crosstalk. Customized strategies from the component level to the topology level are seamlessly combined with minimized system complexity. In specific, we demonstrate T-O and E-O switch elements with ultra-high extinction ratios, incorporating a dual-stage design to correct splitting-ratio errors and exploiting the self-heating effect in the E-O designs for loss balancing across MZI arms. These optimized switch elements are then applied to establish multi-port switch fabrics, being strategically deployed in the stages that are most vulnerable to crosstalk, in the partially dilated double-layer network (DLN) topology. Experimental results illustrate that both T-O and E-O switches in the scale of 8 × 8 achieve superior crosstalk ratios below −40 dB at the center wavelength of 1550 nm. This, to the best of our knowledge, sets a new record for the E-O switch fabrics. Additionally, the optical transmission of a 50 Gb on-off key (OOK) signal is performed on the E-O switch with high fidelity, demonstrating great potential for high-throughput optical interconnects.

Results

Design of T-O and E-O Switches

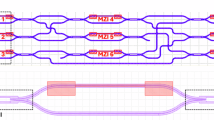

As schematically shown in Fig. 1a, both the 8 × 8 T-O and E-O switches are assembled in a DLN topology that comprises 5 stages with a total of 64 switch elements. In such a topology, only the switch elements in the central stage encounter the first-order crosstalk, setting a limitation to the circuit26. Therefore, we implement dual-MZI switch elements in the central stage as ultra-low-crosstalk 2 × 2 cells, while the remaining four stages utilize regular MZIs as 1 × 2 or 2 × 1 cells, as shown by the insets in Fig. 1a. This effectively suppresses the circuit crosstalk and reduces the total number of switch cells. Each single-MZI 1 × 2 and 2 × 1 cell comprises a pair of T-O or E-O phase shifters driven in a push-pull manner, while the dual-MZI 2 × 2 cell includes an additional MZI element with T-O phase shifters, serving as a variable power splitter. Thus, its coupling ratio can be complementarily matched with the that of the output combiner for mitigating the fabrication variation. It should be noted that the second MZI of the E-O 2 × 2 cell employs a doped phase shifter pair with distinct lengths and doping profiles, denoted as PS 1 and PS 2, respectively. This configuration aims to offer an arbitrary phase difference while maintaining an identical insertion loss on each MZI arm. Both 8 × 8 switches are optimized for TE mode operation at a wavelength of 1550 nm and utilize multimode interferometers (MMIs) to enable a broadband operation. Figure 1b, c provide detailed schematics of the T-O and E-O phase shifters, respectively. The T-O phase shifter consists of a 300 μm TiN micro-heater, which is surrounded by deep air trenches for thermal isolation. As for the E-O phase shifter pair, the waveguide is laterally sandwiched between p- and n-doped regions. In specific, the E-O PS 1 features a length of 500 μm and contains heavily doped regions only, while the E-O PS 2 has a much shorter length of 100 μm and incorporates lightly doped regions in between the waveguide and the heavily doped regions. For both phase shifters, the p- and n-doped regions are separated by 2 μm to lower the driving voltage and maintain isolation from waveguide mode. Additionally, they are equipped with a metal heater only for phase correction.

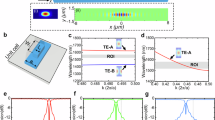

a The 8 × 8 DLN switch topology. Insets show the structure of the 1 × 2 and 2 × 2 MZI switch elements. b Schematic of the T-O phase shifter. c Schematic of the E-O differential phase shifter pair. d Insertion loss under different phase shift settings. Dots and circles on the curves represent the loss and phase for each phase shifter when the switch element is configured in the bar state. e I–V characteristics of the E-O phase shifters, with dots and circles indicating the voltage and current for each phase shifter in the bar state. f Switching time of the E-O differential phase shifter pair, varying with pulse peak voltages

In typical E-O switches, the phase modulation is realized by injecting free carriers from the doped regions into the waveguides, where the concentration increase of free carriers lowers the waveguide’s refractive index via free carrier dispersion (FCD). This, however, introduces unwanted loss due to the free-carrier absorption (FCA) that creates power imbalances between the MZI arms, leading to incomplete interference and, consequently, crosstalk. To mitigate this issue, we incorporate a specially-engineered E-O phase shifter on the opposite arm that introduces loss with minimal phase change, thereby balancing the FCA. To break the bound of phase change and loss, we harness the self-heating effect inherent in the p-i-n junction, where the heat stems from both the current flow of free carriers and their recombination near the junction. While self-heating in regular E-O phase shifters is generally considered undesirable, our approach transforms it into a benefit. Specifically, self-heating modifies the waveguide’s refractive index in a manner opposite to FCD. Consequently, when self-heating becomes sufficiently pronounced, it can completely neutralize the carrier-induced phase shift, leaving only the absorption effect. We systematically examined how various design parameters affect the phase shift and loss in an E-O phase shifter19, and based on these findings, developed two doped phase shifters with different lengths. The specially-engineered phase shifter that aims to match the FCA of the regular one, is designed to operate with high bias, intensifying the self-heating effect. The inclusion of lightly doped regions further exacerbates this impact, as carrier recombination rates are higher in these regions. It thus undergoes both FCD and self-heating effects, offers nearly counterbalanced phase change but FCA-induced loss. Meanwhile, the regular phase shifter relies solely on FCD to deliver rapid phase modulation. Such a phase shifter pair can thus operate differentially to achieve a balanced loss and an arbitrary overall phase difference to trigger switching with minimal crosstalk, as illustrated in Fig. 2d. The detailed I-V characteristics for each phase shifter are shown in Fig. 2e. The current cell design is simulated to have an overall insertion loss of 6 dB, with a power consumption of approximately 100 mW. This performance limitation primarily attributed to the metal electrodes surrounding the waveguide core, which function as unintended heat sinks and divert heat away from the phase shifter. To compensate for such thermal energy loss, the required forward bias voltage increases, inducing higher level carrier injection that enhances FCA. It is expected that the insertion loss and power consumption can be further reduced to 2 dB and around 20 mW, respectively, by further shortening the length of PS 2 and optimizing the position of its electrodes to enhance self-heating27.

a The microscope image of the T-O switch. b The packaged T-O switch. c The microscope image of the E-O switch. d The package E-O switch

Notably, in the proposed E-O 2 × 2 cell, the self-heating effect inevitably impairs the switching speed. Simulations indicate that both the rise and fall times triggered by the self-heating effect are approximately 12 μs. In this work, pulse excitation technique28 and differential control schemes29 are employed to enhance the switching speed. Specifically, an additional excitation pulse is applied on top of the step-on signal to overdrive it and accelerate the temperature rise. Conversely, when cooling it, a pulse is applied to the phase shifter on the other MZI arm to rapidly heat it, thereby reducing the temperature differential between the two arms and the resultant phase difference. Figure 2f confirms that by applying excitation pulses with sufficiently high voltages, the switching time of the proposed device can be reduced to less than 100 nanoseconds.

Experimental characterization

Figure 2a, b showcase the microscope images of the T-O and E-O switch chips, respectively, with each occupying a footprint of 6.5 × 5.7 mm2 and 7.8 × 6.1 mm2. Figure 2c, d illustrate these chips after electrical and optical packaging. The T-O and E-O chip respectively have 162 and 276 electrical pads in total and both are wire-boned to customized PCBs for electrical connections.

To characterize the switch performance, we first perform switch calibrations. Figure 3a illustrates the transmission of a T-O 1 × 2 cell in accordance with the driving power, where approximately 2 mW of power is required to achieve a π phase shift. The 2 × 2 cell, on the other hand, consumes 1 mW to toggle between cross and bar states, as shown in Fig. 3b. For the E-O switch, its 1 × 2 switch element necessitates about 1 mW, as per Fig. 3c, while this number goes up to around 100 mW for the 2 × 2 cell since the self-heating effect is enhanced. Figure 3d presents the 2 × 2 switch element’s transmission response to bias current variations. The tilting pattern rising from the bottom left to the top right indicates the increasing self-heating effects in E-O PS 2. This agrees well with the simulations. Regarding insertion loss, the T-O 1 × 2 and 2 × 2 elements exhibit losses of about 0.4 dB and 0.6 dB, respectively. Meanwhile, the E-O 1 × 2 element has an insertion loss of around 1.2 dB, and the E-O 2 × 2 element experiences approximately 0.7 dB in the cross state and 5.2 dB in the bar state.

a–d The transmission of the 1 × 2 and 2 × 2 T-O and E-O switch elements against the driving power, respectively. e, f The transmission spectra of all routing paths for the 8 × 8 T-O and E-O switches, respectively. The colored lines represent the transmission from specific input ports to their corresponding output ports, with grey lines indicating crosstalk leaked to undesired outputs

Figure 3e shows the spectral responses of different optical paths for the T-O switch over the wavelength window between 1520 nm and 1580 nm. The on-chip propagation loss spans 4–5 dB, primarily influenced by variations in path length and the number of waveguide crossings. The average insertion loss is about 4.6 dB, comprising approximately 1.6 dB from the four 1 × 2/2 × 1 switching elements, 0.6 dB from the 2 × 2 switching element, 1.3 dB from the connecting waveguides, and 1.1 dB from the waveguide crossings. The crosstalk is below −40 dB at the central wavelength and stays under −30 dB across a bandwidth greater than 40 nm. Figure 3f presents the transmission spectra of the E-O switch, with certain optical paths unavailable also due to faulty E-O phase shifters. As can be seen, the on-chip propagation loss measures as low as 8.5 dB, when the middle-stage 2 × 2 switch elements are set to the cross state, and increase to at most 14.4 dB when they are switched to the bar state. Breaking down these losses shows that 4.8 dB comes from the four 1 × 2/2 × 1 switching elements, 0.7 or 5.2 dB from the 2 × 2 switching element (depending on its state), 2.3 dB from the connecting waveguides, and 1.1 dB from the waveguide crossings. Under both states, our E-O switch maintains a crosstalk ratio below −40 dB at the wavelength of 1550 nm, with worst-case performance sustaining <−30 dB crosstalk over a 10 nm window.

To characterize the transient response of the switches, we utilize square wave signals of either 0.1 kHz or 1 kHz from an arbitrary waveform generator (AWG), which are amplified by an electrical amplifier and applied to drive the T-O or E-O switch. The output signal from the switch circuit is amplified using an erbium-doped fiber amplifier (EDFA), which is filtered for detection. The rise and fall times are then measured through an oscilloscope. Figure 4a, b presents the recorded rising and falling temporal waveforms of the 1 × 2 and 2 × 2 T-O switch elements, respectively, both featuring a switching time of approximately 500 µs. Similarly, Fig. 4c, f illustrates the temporal waveforms of the 1 × 2 E-O switch element with a regular E-O phase shifter, showing a rise time of 10 ns and a fall time of 60 ns. As for the 2 × 2 E-O switch element with differential phase shifters, using a conventional driving method—where square wave signals are applied simultaneously to both shifters—results in a rise and fall times of 1 µs and 7 µs, respectively, as shown in Fig. 4d. Such a reconfiguration speed results from the time required for the waveguide to reach thermal equilibrium, owing to the inducement of self-heating. A pulse excitation technique is subsequently adopted combining with the differential control to drive the two phase shifters. In specific, when heating up, we accelerate the process by applying an additional high-energy pulse, while at cooling down, we rapidly heat the other arm to quickly reduce the temperature difference, effectively mimicking fast cooling. Figure 4e details the applied driving signals, where PS 2 receives a 5 V pulse with a duration of 40 ns at the rising edge, and PS 1 receives a 4 V, 50 ns pulse at the falling edge. Here both amplitude and duration of these pulses are carefully optimized to shorten the switching time while preventing any over-drive damage. Figure 4f depicts the measured waveforms, showing a rise time of 40 ns and a fall time of 100 ns, respectively. Note that the switching speed can be further improved by applying higher-energy pulses, but a thorough investigation on the burn-down threshold at different doping levels has to be conducted. Thus, we opt to employ a moderate pulse energy as a balanced choice, since a switching speed of <100 ns is widely considered sufficient for datacenter applications30.

a, b Measured rise and fall time of the 1 × 2 and 2 × 2 T-O switch elements, respectively. c Measured rise and fall time of the 1 × 2 E-O switch element. d Measured rise and fall time of the 2 × 2 E-O switch element under regular driving. e The differential driving signals. f Measured rise and fall time of the 2 × 2 E-O switch element after applying the differential control scheme

Data transmission performance

To verify the switching capabilities of our designs, a data transmission experiment is conducted using the 8 × 8 E-O switch as an example. During the measurement, a continuous-wave (CW) laser operating at 1559 nm is modulated by a 50 Gb/s non-return-to-zero on-off keying (NRZ-OOK) signal generated from an AWG (Keysight 8194 A), utilizing an electro-absorption modulator (EAM) for optical intensity modulation. The modulated signal is subsequently amplified through an EDFA and polarization-controlled to TE mode before being coupled into the switch chip. Upon traversing the switching path, the output optical signal undergoes variable attenuation via a variable optical attenuator (VOA) to optimize the power level for detection. A high-speed digital storage oscilloscope (DSO, Keysight Infiniium UXR) operating at 256 GSa/s captures the waveform for offline digital signal processing (DSP). The DSP workflow involves frequency offset compensation and synchronization between transmitted and received sequences, followed by adaptive equalization using a 13-tap least mean square (LMS) based equalizer. Finally, the bit error rate (BER) is calculated, and eye diagrams are reconstructed to evaluate signal integrity. Figure 5a illustrates the analytical fit of the BER results for both the back-to-back (BtB) transmission and the transmission involving the switch. Meanwhile, Fig. 5b presents the eye diagrams for the eight routing paths at a received optical power of −5 dBm. The results reveal that, at a fixed BER of 10−2, the inclusion of the E-O switch in the system introduces a power penalty of less than 0.8 dB due to post-amplification, demonstrating high fidelity.

a BER results of the BtB transmission and the eight routing paths from input I8; b Eye diagrams of the BtB transmission and the eight routing paths from input I8

Discussion and conclusion

To highlight the demonstrated switches, this work is placed in context with other demonstrations of low-crosstalk switch fabrics on the SOI platform, as shown in Table 1. By employing a partially-dilated DLN topology with a dual-MZI design in the central stage, our T-O switch achieves superior crosstalk suppression, with values below −40 dB at the central wavelength and under −30 dB across a 40 nm range, matching the performance of fully-dilated strictly non-blocking topologies. Thanks to excellent thermal isolation, each T-O switch element consumes only about 2 mW to toggle between the cross and bar states. Note that while the thermal isolation impacts switching speed, this can still be mitigated using pulse excitation techniques, leaving the switching time constrained only by the heat propagation from the heater to the waveguide.28 On the other hand, the proposed E-O switch also realizes a crosstalk level below −40 dB, being >10 dB better than state-of-the-art results. This advantage is attributed to the usage of differential phase shifter pair, which addresses the FCA-induced power imbalances through a straightforward structure.

The experimental results validate the effectiveness of our proposed approach for mitigating crosstalk in silicon MZI switches. The T-O switch, with its lower insertion loss and reduced system complexity, is particularly suited to circuit-oriented applications involving well-scheduled, long-duration tasks, while the E-O device offers a nanosecond switching time that enables packet-level operations, making it ideal for handling burst traffic in modern datacentres and benefiting latency-sensitive computing workloads9,31. Although deploying these switches in larger-scale networks may increase the total switch count and number of hops compared to those high-port-count MEMS switches32, a number of studies have shown that the benefit of dynamic reconfiguration can still be reaped with modest-radix switches18,33.

Moreover, our switch design features the scalability towards larger port counts. The inherent characteristics of the DLN topology ensure that low crosstalk can be maintained by applying the proposed differential phase shifter design in the central stage, regardless of switch size. To manage the increased control complexity in large-scale switches, a column-row addressing method can be implemented to selectively actuate the necessary phase shifters34, significantly reducing the number of electrical control signals.

In conclusion, we present two generations of ultra-low-crosstalk silicon switches driven thermally and electrically. Utilizing a DLN topology with customized switch elements, both switches achieve crosstalk levels below −40 dB, setting a new performance benchmark in the field. Moreover, the T-O switch delivers an insertion loss of <5 dB with a 500 µs switching time, while the E-O switch offers an insertion loss as low as 8.5 dB and a switching speed of <100 ns. The optical transmission of a 50 Gb OOK signal is demonstrated, showing a high fidelity. Overall, the proposed switch fabrics can bring about a breakthrough in the scalability of E-O switch fabrics, and thus may find wide applications in the next-generation datacenter networks.

Methods

Simulation of the differential E-O phase shifter pair

ANSYS Lumerical CHARGE and MODE software tools are used to conduct comprehensive electrical, thermal and optical simulations of the differential E-O phase shifter pair. Initially, a coupled heat and charge transport solver is set up to model the heat propagation and carrier distribution within the phase shifter under various bias voltages. This solver self-consistently solves the drift-diffusion equations with Poisson’s equation and the heat transport equation using the finite-element method (FEM). The profiles generated from this process are subsequently imported into a finite-difference eigenmode (FDE) solver, which calculates the resultant changes in the effective refractive index Δneff and FCA loss. Finally, Δneff is translated into phase shift Δϕ using the following equation:

where \(\lambda\) is the wavelength of the signal, \(\varGamma\) is the confinement factor, and \(L\) is the length of the phase shifter.

To estimate the switching time of the E-O phase shifter, we perform a transient analysis. The process begins by determining the steady-state current density and recombination rate of the phase shifter with the MZI in the bar state, using a charge transport solver. These parameters are then used to calculate the heat generation within the device by the following equations:

where Jn,p is the current density, En,p is the electric field, q is the electron charge, Eg is the bandgap energy, k is the Boltzmann constant, T is the temperature, and R is the net recombination rate. During the simulation of the switching process, this generated heat is treated as a source within the heat transport solver, which operates in transient mode. The activation and deactivation of this heat source are controlled by a step signal incorporating a 10 ns rise time that follows a logarithmic profile, mimicking the exponential change in carrier concentration during actuation. This setup allows for the extraction of temperature variations over time in the waveguide core, from which the switching time is determined. Throughout these simulations, the ambient temperature is maintained at 300 °K around the simulation region.

Chip fabrication and packaging

The T-O and E-O switches chips are fabricated via an Advanced Micro Foundry (AMF) silicon photonics multi-project wafer (MPW) run, employing 193-nm deep ultraviolet (DUV) lithography capable of achieving feature sizes down to 140 nm. The process is based on 220-nm silicon-on-insulator (SOI) technology, with a 3-µm buried oxide (BOX) layer and a 2-µm top cladding layer.

Two 20-channel single mode fibre arrays (SMFAs) are used to couple to and from the two facets of each chip, with a coupling loss of around 4 dB per facet. A thermistor is attached to the bottom of the chip, and a thermoelectric cooler (TEC) is placed underneath to form a negative feedback mechanism, facilitating the temperature stabilization during testing.

An automatic electrical control plane has been developed to drive the switches. Control signals generated by a computer are first sent to a microcontroller unit (MCU), then transmitted to high-resolution digital-to-analog converters (DACs) via a serial peripheral interface (SPI). The voltages from the DACs are subsequently amplified and loaded onto the chip. Specifically, current-output DACs are used for the differential E-O phase shifters to precisely control the current flow, while voltage-output DACs are employed for the T-O phase shifters and regular E-O phase shifters.

Chip calibration

To calibrate the switches, we employ a C-band tunable laser set at an output power of 0 dBm as the light source, while the output signals from the switches are collected by an 8-channel optical power meter. In the calibration of each switch element within the T-O switch, we sweep the bias voltage applied to its phase shifter and monitor the optical power at the related output ports. We then determine the voltages for setting these switch elements in the cross and bar states by identifying the bias voltages that maximize or minimize the output power difference. Additionally, the central dual-MZI switch elements necessitate the fine-tuning of both phase shifters. To avoid the time-consuming two-dimensional sweep, we employ a gradient descent algorithm to efficiently search for the optimal bias voltages.

The calibration process for the E-O switch mirrors that of the T-O switch. We calibrate each 1 × 2/2 × 1 switch element at the bilateral stages by sweeping the bias voltages on the heaters to identify the 0 and π phase biases. After setting the heater’s voltage to the quadrature point to achieve a π/2 phase bias for the push-pull configuration, we adjust the voltages on the E-O phase shifters. This creates a look-up table (LUT) for maximizing or minimizing transmission power, forming a control map for both heaters and E-O phase shifters that defines the cross and bar states of the 1 × 2/2 × 1 MZI cells. For the central 2 × 2 switch elements, we initially use a gradient descent algorithm to identify the optimal bias voltages for their heaters to pre-bias these elements to the cross state. Once all switch elements are set to the cross state, we refine the voltage combinations for the differential E-O phase shifters to set their bar state. Consequently, the control LUT for the entire E-O switch is obtained.

Data availability

For the purpose of open access, the author has applied a Creative Commons Attribution (CC BY) license to any Author Accepted Manuscript version arising. Data underlying the results presented in this paper are available at https://doi.org/10.17863/CAM.112412.

References

Cisco Annual Internet Report - Cisco. https://www.cisco.com/c/en/us/solutions/executive-perspectives/annual-internet-report/index.html.

Cheng, Q., Bahadori, M., Glick, M., Rumley, S. & Bergman, K. Recent advances in optical technologies for data centers: a review. Optica 5, 1354 (2018).

Zervas, G., Yuan, H., Saljoghei, A., Chen, Q. & Mishra, V. Optically disaggregated data centers with minimal remote memory latency: technologies, architectures, and resource allocation. J. Opt. Commun. Netw. 10, A270 (2018).

Zhang, X., Kwon, K., Henriksson, J., Luo, J. & Wu, M. C. A large-scale microelectromechanical-systems-based silicon photonics LiDAR. Nature 603, 253–258 (2022).

Quack, N. et al. Integrated silicon photonic MEMS. Microsystems Nanoeng. 9, (2023).

Zhang, Y. et al. Ultrabroadband 2D-dispersive wavelength selective switch with 1.57 GHz hyperfine spectral resolution and >1600 channels. Laser Photon. Rev. 17, 2300232 (2023).

Chen, Q., Wang, M. K., Ma, X. X., Yao, H. & Chen, K. X. Broadband and low-random-phase-errors 2 × 2 optical switch on thin-film lithium niobate. IEEE Photonics J. 14, 1–5 (2022).

Feyisa, D. W., Shi, B., Kraemer, R., Calabretta, N. & Stabile, R. Compact 8×8 SOA-Based Optical WDM Space Switch in Generic InP Technology. J. Light. Technol. 40, (2022).

Xue, X. & Calabretta, N. Nanosecond optical switching and control system for data center networks. Nat. Commun. 13, 2257 (2022).

Ruf, F., Nielsen, L., Volet, N. & Heck, M. J. R. Analysis and design of low-loss and fast all-optical switch elements on silicon nitride for integrated quantum photonics. J. Light. Technol. 40, 7598–7609 (2022).

Gao, W. et al. Broadband 32 × 32 strictly-nonblocking optical switch on a multi-layer Si3N4-on-SOI platform. Laser Photonics Rev. 17, (2023).

Suzuki, K. et al. Low-insertion-loss and power-efficient 32 × 32 silicon photonics switch with extremely high-Δ silica PLC connector. J. Light. Technol. 37, 116–122 (2019).

Chen, X., Lin, J. & Wang, K. A Review of Silicon-Based Integrated Optical Switches. Laser and Photonics Reviews. 17 (2023).

Zhu, X. et al. Low-loss and polarization insensitive 32 × 4 optical switch for ROADM applications. Light Sci. Appl 2024 131 13, 1–10 (2024).

Konoike, R. et al. Gain-Integrated 8 × 8 Silicon Photonics Multicast Switch with On-Chip 2 × 4-ch. SOAs. J. Light. Technol. 38, 2930–2937 (2020).

Dupuis, N. et al. A 4 × 4 Electrooptic Silicon Photonic Switch Fabric with Net Neutral Insertion Loss. J. Light. Technol. 38, 178–184 (2020).

Zhang, J. et al. Lossless High-speed Silicon Photonic MZI switch with a Micro-Transfer-Printed III-V amplifier. Proc. - Electron. Components Technol. Conf. May, 441–445 (2022).

Cheng, Q., Rumley, S., Bahadori, M. & Bergman, K. Photonic switching in high performance datacenters. Opt. Express 26, 16022–16043 (2018).

Bao, P. et al. Harnessing Self-Heating Effect for Ultralow-Crosstalk Electro-Optic Mach-Zehnder Switches. Photonics Res. 11, 1757, https://doi.org/10.1364/prj.492807 (2023).

Jiang, J. et al. 16×16 silicon photonic switch with nanosecond switch time and low-crosstalk architecture. in IET Conference Publications 2019 (2019).

Suzuki, K. et al. Ultra-high-extinction-ratio 2 × 2 silicon optical switch with variable splitter. Opt. Express 23, 9086–9092 (2015).

Wilkes, C. M. et al. 60dB high-extinction auto-configured Mach–Zehnder interferometer. Opt. Lett. 41, 5318–5321 (2016).

Dupuis, N. et al. Ultralow crosstalk nanosecond-scale nested 2 × 2 Mach–Zehnder silicon photonic switch. Opt. Lett. 41, 3002–3005 (2016).

Lu, Z., Celo, D., Mehrvar, H., Bernier, E. & Chrostowski, L. High-performance silicon photonic tri-state switch based on balanced nested Mach-Zehnder interferometer. Sci. Rep. 7, 1–7 (2017).

Dupuis, N. et al. Nanosecond-scale shift-and-dump Mach–Zehnder switch. Opt. Lett. 44, 4614 (2019).

Lu, C. C. & Thompson, R. A. The double-layer network architecture for photonic switching. J. Light. Technol. 12, 1482–1489 (1994).

Zhao, J. et al. Analysis of the thermo-optic effect in lateral-carrier-injection SOI ridge waveguide devices. J. Semicond. 31, 126003 (2010).

Atabaki, A. H., Eftekhar, A. A., Yegnanarayanan, S. & Adibi, A. Sub-100-nanosecond thermal reconfiguration of silicon photonic devices. Opt. Express 21, 15706–15718 (2013).

Iino, K. & Kita, T. Ultrafast operation of Si thermo-optic switch using differential control method. Jpn. J. Appl. Phys. 62, 012002 (2022).

Cheng, Q. et al. Photonic switch fabrics in data center/high-performance computing networks. in Integrated Photonics for Data Communication Applications (2023). https://doi.org/10.1016/B978-0-323-91224-2.00003-5.

Dupuis, N. et al. Nanosecond-Scale Mach-Zehnder-Based CMOS Photonic Switch Fabrics. J. Light. Technol. 35, (2017).

Poutievski, L. et al. Jupiter evolving: Transforming googles datacenter network via optical circuit switches and software-defined networking. in SIGCOMM 2022 - Proceedings of the ACM SIGCOMM 2022 Conference https://doi.org/10.1145/3544216.3544265 (2022).

Rumley, S. et al. Optical interconnects for extreme scale computing systems. Parallel Comput. 64, 65–80 (2017).

Ribeiro, A. et al. Column-row addressing of thermo-optic phase shifters for controlling large silicon photonic circuits. IEEE J. Sel. Top. Quantum Electron. 26, 1–8 (2020).

Chen, L. et al. Compact, low-loss and low-power 8×8 broadband silicon optical switch. Opt. Express 20, 18977–18985 (2012).

Konoike, R., Suzuki, K., Kawashima, H. & Ikeda, K. Port-alternated switch-and-select optical switches. J. Light. Technol. 39, 1102–1107 (2021).

Li, D. et al. 16 × 16 silicon Mach–Zehnder interferometer switch actuated with waveguide microheaters. Photonics Res. 4, 202–207 (2016).

Dumais, P. et al. Silicon photonic switch subsystem with 900 monolithically integrated calibration photodiodes and 64-fiber package. J. Light. Technol. 36, 233–238 (2018).

Dupuis, N. et al. An 8×8 Silicon Photonic Switch Module with Nanosecond-Scale Reconfigurability. in 2020 Optical Fiber Communications Conference and Exhibition, OFC 2020 - Proceedings (2020).

Acknowledgements

This work was supported by the UK EPSRC Programme Grant QUDOS (EP/T028475/1), TRANSNET (EP/R035342/1), Communication Hub TITAN (EP/X04047X/1 and EP/Y037243/1), UK EPSRC CEPS CDT (EP/S022139/1), the European Union’s Horizon Europe Research and Innovation Program under Agreement 101070560 (PUNCH), and the European Union’s Horizon 2020 research and innovation program, project INSPIRE (101017088). C.Y. and C.T. thank the scholarship provided by Cambridge Trust and China Scholarship Council. The authors thank Dr. Giuseppe Talli and Dr. Maxim Kuschnerov for the support in the project.

Author information

Authors and Affiliations

Contributions

P.B. conceived the switch design, performed the optical simulations, and drawn the chip layout. P.B. performed the characterization of switch performance and analyzed the data with C.Y. and M.C.’s help. P.B., C.T. and A.Y.Y. designed and conducted the data transmission experiment. P.B. drafted the manuscript, with C.Y., Q.C., C.T., S.J.S. and M.C.’s input. R.P. and Q.C. supervised the project.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no competing interests.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Bao, P., Yao, C., Tan, C. et al. Ultra-low-crosstalk silicon switches driven thermally and electrically. Microsyst Nanoeng 11, 58 (2025). https://doi.org/10.1038/s41378-025-00911-9

Received:

Revised:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41378-025-00911-9