Abstract

Two-dimensional (2D) semiconductors are promising for next-generation field-effect transistors (FETs), but their integration into complementary-metal-oxide-semiconductors (CMOS) logic is hindered by improper threshold voltages (\({V}_{{th}}\)), leading to excessive power consumption. While past efforts have focused on improving gate electrostatics and near-ideal subthreshold swing (\({SS}\)), systematic \({V}_{{th}}\) engineering in 2D FETs remains unexplored. Here, we investigate high-κ van der Waals (vdW) dielectrics including metal oxyhalides such as LaOBr, BiOBr, and BiOCl, and bimetallic thiophosphates such as LiInP2S6 (LIPS), LiInP2Se6 (LIPSe) and CuInP2S6 (CIPS), and demonstrate that bimetallic thiophosphates enable programmable and non-volatile \({V}_{{th}}\) tuning in both n-type monolayer MoS2 and p-type bilayer WSe2 FETs. Leveraging ion-mediated \({V}_{{th}}\) tuning, we realize 2D CMOS inverters with nearly three orders of magnitude reduction in static power while maintaining high switching speed. Combining experiments with industry-compatible SPICE modeling, we identify an optimal \({V}_{{th}}\) window that minimizes power with negligible delay overhead, enabling built-in power gating and improved power–performance–area metrics without additional sleep transistors.

Similar content being viewed by others

Introduction

Two-dimensional (2D) semiconductors have become increasingly pivotal in the development of nanoscale field-effect transistors (FETs) as traditional Si-based FETs face significant challenges with scaling down device dimensions, owing to weak electrostatic control and degradation in performance1,2. Moreover, as techniques for large-area growth of these materials, such as chemical vapor deposition (CVD)3 and metal-organic CVD (MOCVD)4, continue to mature, 2D materials show great potential in producing a large number of FETs5,6,7, for integration into very large scale integrated circuits (ICs)8,9,10,11. Additionally, considerable effort has been devoted to enhance the performance of these Schottky-type 2D FETs12 via contact engineering13,14, chemical doping15, etc., aiming to attain superior on-state performance. More recent efforts focus on improving the dielectric interfaces16,17,18,19,20,21,22 minimize the interface trap charge density \(({D}_{{it}}),\) leading to near-ideal subthreshold slope (\({SS}\)) and thereby enabling more efficient operation of the 2D FETs. However, a crucial missing element in the development of 2D FETs is threshold voltage (\({V}_{{th}}\)) engineering, which directly impacts the operation and power consumption of integrated circuits (ICs). In complementary metal-oxide-semiconductor (CMOS) logic circuits, n-type FETs require a positive \({V}_{{th}}\), while p-type FETs require a negative \({V}_{{th}}\). In silicon FETs, \({V}_{{th}}\) is primarily controlled via substitutional doping, with additional precision achieved through engineering high-κ gate dielectrics and metal gate work function23. However, achieving the correct \({V}_{{th}}\) polarity and tunability remains a challenge for 2D FETs. Both p-type and n-type 2D FETs9,24 often exhibit negative \({V}_{{th}}\), leading to high static power dissipation25,26 in 2D CMOS circuits, with precise \({V}_{{th}}\) control still lacking.

Conventional oxides such as SiO227, Al2O34, HfO228, etc., introduce unintended n-type doping due to interface states, fixed charges, and adsorbates like H2O and O229,30. While passivation techniques, e.g., rapid thermal annealing (RTA)31 or hexagonal boron nitride (h-BN) encapsulation17, improve interface quality and \({SS}\), they often fail to impart a positive \({V}_{{th}}\) to n-type 2D FETs. Emerging interface engineering approaches32,33,34,35,36 – including molecular crystals (e.g., PTCDA)18, seed layer (e.g., Sb2O3)19, and crystalline dielectrics (e.g., CaF220, SrTiO321,37,38)—offer improved electrostatics via van der Waals interface, but \({V}_{{th}}\) control remains elusive. A limited number of studies have attempted to correct \({V}_{{th}}\) polarity in n-type MoS2 FETs39,40,41,42,43,44. Yu et al.40 achieved positive \({V}_{{th}}\) for MoS2 FETs by minimizing trapped and fixed charges at the MoS2/dielectric interface, while Jeon et al.44 demonstrated \({V}_{{th}}\) shift using fluoropolymer encapsulation. Leong et al.39 showed that controlling sulfur vacancies can adjust \({V}_{{th}}\) in exfoliated MoS245, though precise tunability remained unachieved. Most \({V}_{{th}}\) tuning approaches rely on gate bias in a dual-gated configuration41,42,43, which are inherently volatile. Meanwhile, p-type FETs46 based on WSe2 generally exhibit the correct \({V}_{{th}}\) polarity, but tunability is yet to be demonstrated. Although our recent work demonstrated low-power 2D CMOS through process optimization45, comprehensive, non-volatile \({V}_{{th}}\) engineering in 2D FETs, and its direct impact on CMOS circuits, remain largely unexplored.

In this work, we investigate a range of high-κ vdW dielectrics, including LaOBr, BiOBr, BiOCl, which belong to the family of metal oxyhalide as well as LiInP2S6 (LIPS), LiInP2Se6 (LIPSe)47, and CuInP2S6 (CIPS), which belong to the family of bimetallic thiophosphates, grown via chemical vapor transport (CVT), to identify optimal candidates for precise \({V}_{{th}}\) control in 2D FETs. We find that bimetallic thiophosphates (LIPS, LIPSe, CIPS) stand out as particularly promising owing to their programmable and non-volatile ion migration, which enables fine-tuned and stable \({V}_{{th}}\) modulation. As proof of concept, we fabricated dual-gated n-type monolayer MoS2 and p-type bilayer WSe2 FETs using LIPS as the top-gate dielectric and achieved nearly three orders of magnitude reduction in static power dissipation in 2D CMOS inverters through systematic \({V}_{{th}}\) tuning. Dual-gated transport measurements further reveal a high effective dielectric constant for LIPS (\({\kappa }_{{eff}}\,\)~ 41), reinforcing the suitability of thiophosphates for low-power logic. Complementing experiments with SPICE-compatible compact models, we capture the power–delay tradeoff and identify an optimal \({V}_{{th}}\) window that minimizes leakage without compromising speed. Moreover, the ability to dynamically reprogram \({V}_{{th}}\) enables built-in power gating without additional sleep transistors, improving power, performance, and area (PPA) while offering runtime control over switching thresholds and noise margins. These results establish vdW thiophosphates as an attractive materials platform for non-volatile \({V}_{{th}}\) engineering, paving the way for energy-efficient 2D CMOS technology.

Results

Importance of \({{{\boldsymbol{V}}}}_{{{\boldsymbol{th}}}}\) engineering in 2D FETs

First, we highlight the importance of adjusting the \({V}_{{th}}\) for designing ICs by investigating the \({V}_{{th}}\) dependency in 2D FETs with conventional 3D oxides. We fabricated back-gated FETs with a 25 nm thick Al2O3, HfO2 or ZrO2 dielectric layer, grown via atomic layer deposition (ALD) on a 50 nm thick Ti/Pt gate metal stack. MOCVD grown bilayer WSe2 and monolayer MoS2 films were used as p- and n-type semiconducting channels, respectively. These films were transferred onto the prefabricated back-gate stack from the sapphire growth substrate using the PMMA-assisted wet transfer method. We defined the channels by dry etching WSe2 and MoS2 using SF6 plasma at a temperature of 5 °C48. Next, the source and drain contacts were defined using electron beam lithography, followed by electron beam evaporation of 40/30 nm of Pd/Au for WSe2 FETs and 40/30 nm of Ni/Au for MoS2 FETs. All the back-gated FETs have a channel length (\({L}_{{CH}}\)) and width (\({W}_{{CH}}\)) of 500 nm. Additional information about the synthesis of WSe2 and MoS2 and the fabrication of back gated 2D FETs can be found in the “Methods” and in our earlier works9,11,49,50,51. Supplementary Fig. 1 shows the schematics, optical images, and representative Raman spectra obtained from MoS2 and WSe2 back-gated FETs.

Supplementary Fig. 2a–c show the transfer characteristics, i.e., source-to-drain current (\({I}_{{DS}}\)) as a function of the back-gate voltage (\({V}_{{BG}}\)) for a constant source-to-drain bias of, \({V}_{{DS}}\) = 1 V for 20 representative WSe2 FETs with Al2O3, HfO2 and ZrO2 as a back-gate dielectric, respectively. WSe2 FETs exhibit dominant hole transport, owing to the pinning of the metal Fermi level at the middle of the band gap (\({E}_{g}\)), with a closer proximity to the valence band51,52. We also found that the p-type WSe2 FETs exhibit enhancement mode operation with negative \({V}_{{th}}\) values irrespective of the back-gate oxide. The median \({V}_{{th}}\) values, extracted using iso-current method at an \({I}_{{DS}}\) of 10 nA/µm, were found to be −2.35 V, −2.85 V and −3.1 V for Al2O3, HfO2 and ZrO2, respectively, as shown in Supplementary Fig. 2d. Similarly, Supplementary Fig. 2e-g depicts the transfer characteristics for 20 representative MoS2 FETs with the same dielectrics, showing unipolar n-type transport due to Fermi level near the conduction band. Unlike WSe2 FETs, MoS2 FETs operate in depletion mode with negative \({V}_{{th}}\) values. The extracted median \({V}_{{th}}\) values were found to be −0.36, −0.52 and −0.12 V, respectively, for Al2O3, HfO2 and ZrO2 as summarized in Supplementary Fig. 2h.

To assess the impact of non-ideal \({V}_{{th}}\) on circuit performance, we examined CMOS inverters based on p-type WSe2 and n-type MoS2 FETs with different back-gate oxides. Supplementary Fig. 3a-c displays the voltage transfer characteristics, i.e., the output voltage (\({V}_{{out}}\)) as a function of the input voltage (\({V}_{{in}}\)) for supply voltage, \({V}_{{DD}}\) = 2, 3, and 4 V. The switching threshold (\({V}_{{SW}}\)), ideally at \({V}_{{DD}}/2\) for optimal noise margin, is significantly lower due to negative \({V}_{{th}}\) of the n-type MoS2 FETs as seen in Supplementary Fig. 3d. Beside \({V}_{{SW}}\), static power dissipation (\({P}_{{static}}\)) is also influenced by \({V}_{{th}}\). Supplementary Fig. 3e-g shows the inverter timing diagrams for \({V}_{{OUT}}\) and \({I}_{{DD}}\). While \({I}_{{DD}}\) remains low at ~10 pA/µm for an output logic of ‘0’, it significantly increases for an output logic of ‘1’, due to the depletion-mode operation of the n-type MoS2 FET, leading to higher \({P}_{{static}}\). Supplementary Fig. 3h shows \({P}_{{static}}\) across different \({V}_{{DD}}\) values, with Al2O3 yielding the lowest (~11 nW) and HfO2 the highest (~16 nW) for \({V}_{{DD}}\) = 2 V, correlating with the least and most negative \({V}_{{th}}\) values for the respective n-type MoS2 FETs. \({P}_{{static}}\) further rises with increasing \({V}_{{DD}}\). These findings highlight the need for \({V}_{{th}}\) adjustment to enable low-power digital circuit design.

vdW dielectrics for 2D FETs

Next, we explored single-crystal vdW dielectrics, including LaOBr, BiOBr, BiOCl, LIPS, and CIPS as interfacial and capping layer as well as top-gate dielectrics for 2D FETs. The synthesis of these vdW dielectrics is described in the “Methods”. Supplementary Table 1 shows the theoretically predicted static permittivity (\({\varepsilon }_{s}\)) and bandgap (\({E}_{g}\)) values for these vdW dielectrics53,54. Most of these vdW dielectrics can be considered high-κ dielectrics with \({\varepsilon }_{s}\) ranging from ~10 to 40. However, their \({E}_{g}\) values, ranging between 2.8 and 6 eV, are relatively lower compared to conventional 3D oxides.

To evaluate the impact of vdW dielectrics on the \({V}_{{th}}\) of n-type MoS2 FETs, we fabricated two types of devices: (1) FETs with vdW dielectrics as an interfacial layer between the back-gate oxide and the monolayer MoS2 channel and (2) FETs with vdW dielectrics as the capping layer on top of the MoS2 channel. Finally, we evaluate these vdW dielectrics as top gate dielectric in dual-gated MoS2 FETs. Supplementary Fig. 4a, b illustrates the device schematic and the SEM image of MoS2 FET with 2D dielectric as the interfacial layer. The fabrication process is described in the “Methods”. Supplementary Fig. 4c–g shows the transfer characteristics of several MoS2 FETs with 2D dielectric/Al2O3 back-gate stack for LaOBr, BiOBr, BiOCl, LIPS and CIPS, respectively. Supplementary Fig. 4h displays the box plot for \({V}_{{th}}\) distribution for these vdW dielectrics used as the interfacial layer. Regardless of the vdW dielectric used, median \({V}_{{th}}\) values were consistently found to be negative. While interactions with the substrate, such as charge traps at the interface, are known to promote n-type doping in 2D FETs with 3D oxides as the back-gate dielectric55, the results presented above suggest that adsorbates play a more significant role in the n-type doping of MoS2, alongside growth defects like sulfur vacancies, leading to the undesired negative \({V}_{{th}}\) in MoS2 FETs.

This led us to investigate the electrical characteristics of back-gated MoS2 FETs with 2D vdW dielectrics as the encapsulation layer. Supplementary Fig. 5a, b, respectively, illustrates the device schematic and a representative SEM image of an MoS2 FET with 2D dielectrics as the encapsulation layer. The fabrication process is described in the “Methods”. The transfer characteristics of 10 representative MoS2 FETs with LaOBr, BiOBr, BiOCl, LIPS, and CIPS as the vdW encapsulating layer are depicted in Supplementary Fig. 5c–g, respectively. The distribution of \({V}_{{th}}\) values is summarized in Supplementary Fig. 5h. Interestingly, median \({V}_{{th}}\) values were consistently positive regardless of the vdW encapsulation layer. This finding is particularly noteworthy because previous studies that utilized conventional 3D oxides, h-BN, or other encapsulation layers have rarely achieved a positive \({V}_{{th}}\). This unique observation can be attributed to (1) p-type surface charge transfer doping from these vdW dielectrics or (2) protection from surface adsorbents through modification of the energy landscape that gives rise to n-type doping.

To understand the positive \({V}_{{th}}\) in encapsulated MoS2 devices, first-principles density functional theory (DFT) calculations were performed to analyze charge difference density (CDD) across various vdW dielectric/MoS2 stacks. The DFT results (Supplementary Fig. 6a, b) reveal charge depletion in MoS2 and accumulation in the dielectrics, forming interface dipoles that contribute to positive \({V}_{{th}}\), with LIPS and CIPS exhibiting strong interlayer interactions and charge transfer dynamics. Further characterization using Raman spectroscopy (Supplementary Fig 7a–e) confirms interfacial charge transfer, as indicated by the blue shifts observed in the characteristic in-plane \({E}_{2g}^{1}\) and out-of-plane \({A}_{1g}\) peaks at the vdW dielectric capped MoS2, compared to pristine MoS2, indicating p-type doping56,57. Nevertheless, while vdW dielectric encapsulation enables \({V}_{{th}}\) polarity correction, precise \({V}_{{th}}\) tuning is essential for circuit design and remains to be accomplished.

LIPS as top-gate dielectric for \({{{\boldsymbol{V}}}}_{{{\boldsymbol{th}}}}\) engineering

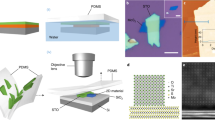

In this section, we investigated these vdW dielectrics as the top-gate dielectric for 2D FETs to assess their potential for \({V}_{{th}}\) engineering. Among them, the bimetallic thiophosphates, i.e., LIPS, LIPSe, and CIPS emerge as promising candidates, offering programmable and non-volatile ion migration, which enables precise and stable \({V}_{{th}}\) modulation. The quality of the as-grown thiophosphate crystals was evaluated using X-ray Diffraction (XRD). As shown in Supplementary Fig. 8a, the XRD intensity plot for LIPS reveals well-defined diffraction peaks in the pristine LIPS crystals, predominantly aligned along the (00 l) planes. Additionally, from the Raman spectroscopy analysis of LIPS flakes as depicted in Supplementary Fig. 8b, we found that the dominant P2S6 modes are observed above 200 cm−1, while the dominant In-S modes appear below 200 cm−1, and all vibrational modes are consistent with the reported literature58. Furthermore, we performed scanning electron microscopy (SEM) combined with energy-dispersive X-ray spectroscopy (EDS) elemental mapping, illustrated in Supplementary Fig. 8c, for LIPS, confirming the presence of constituent elements. Given that SEM-EDS cannot detect Li, the presence of Li is inferred from the deficiency of the secondary metal cation, with the expected stoichiometry being InP2S6. Similar results were obtained for LIPSe and CIPs as shown in Supplementary Figs. 9 and 10, respectively. The schematic and representative SEM image of dual-gated 2D FET with LIPS as top-gate dielectric and a 25 nm thick Al2O3 as the back-gate dielectric are shown in Fig. 1a, b, respectively.

a Schematic and b angled scanning electron microscope (SEM) image of dual-gated 2D FET with LiInP2S6 (LIPS) as top-gate dielectric and a 25 nm thick Al2O3 as the back-gate dielectric. Dual-sweep top-gate transfer characteristic of a c MoS2 FET obtained by sweeping the top-gate voltage (\({V}_{{TG}}\)) from −10 V to 10 V at a constant back-gate voltage, \({V}_{{BG}}\) = 3 V and source-to-drain bias, \({V}_{{DS}}\) = 1 V and a representative (d) WSe2 FET obtained by sweeping the \({V}_{{TG}}\) from −8 V to 8 V at a constant \({V}_{{BG}}\) = −4 V and \({V}_{{DS}}\) = 1 V, both exhibiting a counterclockwise (CCW) hysteresis. CCW hysteresis was consistently observed in four e n-type MoS2 FETs and f p-type WSe2 FETs with LIPS as the top-gate dielectric.

In all devices, a 50/30 nm of Ni/Au stack was used as the gate metal. Figure 1c shows dual-sweep top-gate transfer characteristic obtained by sweeping the \({V}_{{TG}}\) from −10 to 10 V at a constant \({V}_{{BG}}\) of 3 V for MoS2 FETs. Similarly, for WSe2 FETs, the top-gate transfer characteristics were measured by sweeping \({V}_{{TG}}\) from −8 to 8 V at a constant \({V}_{{BG}}\) of −4 V as depicted in Fig. 1d. Interestingly, we observed counterclockwise (CCW) hysteresis in both MoS2 and WSe2 FETs, a phenomenon often linked to ferroelectric FETs, where polarization switching is known to induce such behavior. However, CCW hysteresis can also result from mobile ions in the gate dielectric, which migrate under an electric field and induce similar effects, even in non-ferroelectric FETs59,60. For instance, in an ionic transistor with a Li-based dielectric, Li⁺ ions move toward the semiconducting channel during the forward sweep of the gate bias and diffuse back during the reverse sweep60, resulting in CCW hysteresis. CCW hysteresis was consistently observed across multiple n- and p-type 2D FETs with LIPS as the top-gate dielectric as illustrated in Fig. 1e, f, respectively, confirming the reproducibility of this phenomenon. Importantly, this behavior is not unique to LIPS but is generic across the thiophosphate family. Similar CCW hysteresis signatures were also observed in MoS2 FETs gated with LIPSe and CIPS as shown in Supplementary Fig. 11a, b, respectively, with the latter attributable to the migration of mobile Cu⁺ ions.

To investigate the presence of Li+ ions in LIPS, we performed X-ray photoelectron spectroscopy (XPS) to analyze its surface composition and elemental binding energies (Supplementary Fig. 12a). The XPS spectra confirms a Li 1 s peak at ~55.5 eV, indicating Li in an ionic environment rather than metallic form, as metallic Li typically appears at a lower binding energy61. Additionally, a dominant In2+ peak confirms a sulfide-like environment, with minor In3+ signals indicating surface oxidation. Besides Li, all other elements exhibited binding energies consistent with their expected oxidation states. Similarly, the presence of Cu⁺ ions in CIPS was verified by XPS (Supplementary Fig. 12b). The spectra showed a distinct Cu 2p3/2 peak at ~932.85 eV without satellite features, confirming Cu(I), along with an In 3 d₅/₂ peak at 445.26 eV consistent with the expected oxidation state of indium in the CIPS lattice. Together, these results establish that Li in LIPS and Cu in CIPS exist predominantly in the +1 ionic oxidation state.

To probe further into the origin of CCW hysteresis in LIPS gated MoS2 and WSe2 FETs, dual-sweep top-gate transfer characteristics were obtained for varying \({V}_{{TG}}\) ranges from ±3 V to ±8 V, as shown in Fig. 2a, b, respectively. Minor loops are observed, which can be ascribed to dielectrics containing mobile positive ions. When a positive \({V}_{{TG}}\) is applied, positively charged mobile ions in the dielectric start moving away from the gate electrode and toward the semiconductor-dielectric interface. These ions effectively screen part of the applied gate field, modifying the local electrostatic potential and shifting the \({V}_{{th}}\). As \({V}_{{TG}}\) sweeps forward (increasing), the ions take time to migrate, leading to a delayed response in \({V}_{{th}}\) shift. When \({V}_{{TG}}\) is swept back (decreasing), the ions do not immediately return to their original positions but instead diffuse back gradually, creating a lag in the electrical response. This results in a CCW hysteresis loop in the transfer characteristics. Furthermore, when \({V}_{{TG}}\) does not complete a full sweep (e.g., if it reverses before reaching the maximum applied voltage), the mobile ions do not fully redistribute. Instead, they settle in intermediate positions, leading to an incomplete memory effect. This causes nested, smaller hysteresis loops (minor loops) within the larger main hysteresis cycle. The extent of these minor loops depends on how far the \({V}_{{TG}}\) is swept before reversing direction—if the sweep is too short, the ions do not move significantly, and the loop remains small. The hysteresis window (\({V}_{{Hyst}}\)) as a function of the sweep range (\({V}_{{sweep}}\)) extracted from the minor loops for MoS2 and WSe2 FETs is shown in Fig. 2c, d, respectively.

Dual-sweep top-gate transfer characteristics illustrating nested, minor hysteresis loops in a MoS2 FET and b WSe2 FET, resulting from incomplete ion redistribution within the LIPS during partial top-gate (\({V}_{{TG}}\)) voltage sweeps. c, d Hysteresis window (\({V}_{{Hyst}}\)) dependence on sweep (\({V}_{{sweep}}\)) range extracted from minor loops for MoS2 and WSe2 FETs, respectively. The \({V}_{{Hyst}}\) is determined by the extent of the \({V}_{{sweep}}\) range, a shorter sweep exhibit minimal ion movement, resulting in a smaller \({V}_{{Hyst}}\). Dual-sweep transfer characteristics of e MoS2 and f WSe2 FETs measured at varying sweep rates (\({t}_{{sweep}}\) : 1 ms–1 s), showing increased \({V}_{{Hyst}}\) with longer sweep times. g, h Corresponding \({V}_{{Hyst}}\) as a function of \({t}_{{sweep}}\), confirming ion migration in LIPS, as the primary cause of the CCW hysteresis. i Temperature-dependent dual-sweep transfer characteristics for MoS2 FET, measured across different temperatures, T = −25 °C, 0°C, 25 °C and 50 °C. j Extracted \({V}_{{Hyst}}\) at different temperatures depicting a larger window at higher temperatures due to enhanced ion mobility and near suppression at T = -25 °C. k Top-gate transfer characteristics measured at lower temperatures for varying \({t}_{{sweep}}\), highlighting minimal hysteresis for \({t}_{{sweep}}\) ≤ 100 ms and significant increase at longer sweep rates. l Corresponding \({V}_{{Hyst}}\) confirming reduced ion mobility at low temperatures, requiring longer \({t}_{{sweep}}\) for noticeable hysteresis. These results collectively confirm the role of gate-induced ion migration as the primary mechanism underlying CCW hysteresis in LIPS-gated 2D FETs.

Note that minor loops can also result from partial polarization switching in ferroelectric-gated FETs, highlighting the need for sweep rate-dependent hysteresis measurements to differentiate the underlying mechanisms. This is because, mobile ions in the gate-dielectric require finite time to move and redistribute in response to an external electric field. At slower sweep rates, ions have more time to reach equilibrium, leading to larger \({V}_{{Hyst}}\). Conversely, at faster sweep rates, ions cannot follow the gate voltage change effectively, leading to smaller or even suppressed hysteresis. In contrast, ferroelectric polarization switching occurs via domain nucleation and growth, which is much faster than ion migration. In FeFETs, the \({V}_{{Hyst}}\) remains relatively stable across different sweep rate because ferroelectric dipoles switch on timescales of nanoseconds to microseconds, much faster than ion drift. To experimentally verify this effect, we measured the transfer characteristics of LIPS gated 2D FETs at different sweep rates. Figure 2e depicts the dual-sweep transfer characteristics for LIPS-gated MoS2 FETs, obtained by sweeping the \({V}_{{TG}}\) from −8 to 8 V at a constant \({V}_{{BG}}\) of 3 V for different \({t}_{{sweep}}\) ranging from 1 ms to 1 s. Similarly, Fig. 2f illustrates the dual-sweep transfer characteristics of a representative WSe2 FET, where \({V}_{{TG}}\) is swept from −8 to 8 V at a constant \({V}_{{BG}}\) of −4 V, with \({t}_{{sweep}}\) varying from 1 ms to 500 ms. Figure 2g, h show the extracted \({V}_{{Hyst}}\) corresponding to each \({t}_{{sweep}}\). It is evident that the magnitude of \({V}_{{Hyst}}\) increases with increasing \({t}_{{sweep}}\), confirming the ion migration in LIPS as responsible for the CCW hysteresis.

Additionally, ion movement is thermally activated. As temperature (\(T\)) increases, ion mobility increases, leading to larger \({V}_{{Hyst}}\) at a given \({t}_{{sweep}}\). Conversely, at lower temperatures, ions move more slowly, reducing \({V}_{{Hyst}}\). To experimentally investigate this fact, we performed temperature-dependent measurements of a LIPS-gated MoS2 FET. Figure 2i presents the dual sweep top-gate transfer characteristics of LIPS gated MoS2 FET measured by sweeping the \({V}_{{TG}}\) from −6 to 6 V at a constant \({V}_{{BG}}\) of 2 V across different temperatures, \(T\) = 50, 25, 0 and −25 °C. The extracted \({V}_{{Hyst}}\) corresponding to each temperature is shown in Fig. 2j. As expected, the \({V}_{{Hyst}}\) is found to be larger (~6 V) at 50 °C and is nearly suppressed at −25 °C. Additionally, Fig. 2k presents the dual sweep top-gate transfer characteristics of LIPS gated MoS2 FET measured at −25 °C for \({t}_{{sweep}}\) = 1 ms, 10 ms, 100 ms and 1 s and Fig. 2l shows the extracted \({V}_{{Hyst}}\) at each \({t}_{{sweep}}\). While \({V}_{{Hyst}}\) remains negligible for \({t}_{{sweep}}\) up to 100 ms, a larger \({V}_{{Hyst}}\) is obtained at \({t}_{{sweep}}\) = 1 s. This is expected since slower ion mobility at low temperatures requires longer time for ion movement. FeFETs also exhibit temperature dependence, but the coercive field (\({E}_{C}\)) and remanent polarization (\({P}_{r}\)) do not change significantly unless near the Curie temperature (\({T}_{C}\)). Collectively, these results establish that the CCW hysteresis in LIPS-gated 2D FETs arises from gate-bias-driven ion migration. In fact, as indicated earlier, this behavior was found to be generic across the thiophosphate family. Supplementary Fig. 13a, b shows that LIPSe- and CIPS-gated MoS2 FETs exhibit similar dependencies on sweep range and sweep rate.

To further elucidate the physical mechanism of ion migration, we performed comprehensive sweep-time-dependent measurements on a representative LIPSe-gated MoS2 FET. The dual-sweep top-gate transfer characteristics measured for \({t}_{{sweep}}\) ranging from 10 µs to 10 s at different temperatures (\(T\) = 0, 20, 40, and 80 °C) are shown in Supplementary Fig. 14a. The corresponding hysteresis window (\({V}_{{Hyst}}\)), defined as the voltage difference between the forward and reverse sweeps at a fixed current level, is plotted as a function of \({t}_{{sweep}}\) in Supplementary Fig. 14b. At each temperature, Li⁺ migration within LIPSe produces a non-monotonic dependence of \({V}_{{Hyst}}\) on \({t}_{{sweep}}\), with a distinct maximum at a characteristic time \({t}_{{peak}}\). Importantly, \({t}_{{peak}}\) systematically shifts to shorter values with increasing temperature, consistent with thermally activated ion mobility, while the maximum value of \({V}_{{Hyst}}\), remains nearly constant. To quantify the migration energetics, we constructed an Arrhenius plot of the temperature-induced shift in \({t}_{{peak}}\) (Supplementary Fig. 14c). Note that, \({t}_{{peak}}\) can be expressed as the time required for Li⁺ ions to drift across the full thickness of LIPSe (\({d}_{{LIPSe}}\)) under an applied electric field, as described by Eq. (1):

In Eq. (1), \({E}_{0}\) represents the time-averaged electric field during the sweep, \({E}_{a}\) is the migration barrier for mobile ions, \({D}_{m}\) is the diffusion coefficient, \(q\) is the electronic charge, and \({\kappa }_{B}\) is the Boltzmann constant. Therefore, the slope of the \({t}_{{peak}}\) versus \(T\) plot yields \({E}_{a}\), which was extracted to be 0.431 eV for Li+ migration. This value is consistent with reported barriers for Li⁺ diffusion in layered chalcogenides, confirming the ionic origin of the observed hysteresis. In other words, the measured hysteresis dynamics directly reflect the fundamental ion transport parameters of the dielectric, establishing a quantitative framework for understanding ion migration in thiophosphates.

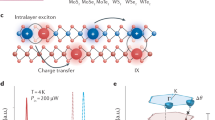

Next, we demonstrate that the ion movement in LIPS is programmable, non-volatile, and can be leveraged for \({V}_{{th}}\) engineering in 2D FETs. Specifically, we exploit the minor loops observed in the top-gate transfer characteristics shown in Fig. 2a, b. Notably, when mobile ions settle at intermediate positions within the top-gate dielectric layer, distinct threshold voltage values can be achieved, as described by Eq. (2) and illustrated schematically in Fig. 3a.

a Schematic representing the migration of Li+ ion within the top-gate dielectric layer, e.g., LIPS. The mobile ions occupy intermediate positions within LIPS as the top-gate bias (\({V}_{{TG}}\)) is applied for a finite duration of time. \({E}_{f,m}\) corresponds to the back gate metal Fermi level, \({E}_{C}\) is denoted as the conduction band minima and \({E}_{V}\) corresponds to valence band maxima. b Back-gate transfer characteristics of a MoS2 FET were measured by sweeping back-gate voltage (\({V}_{{BG}}\)) from −1 to 3 V at \({V}_{{DS}}\) =1 V. Tunable back-gate threshold voltage (\({V}_{{th},{BG}}\)) values (0.25–1.5 V) were obtained by programmable and non-volatile ion movement in LIPS, achieved using a \({V}_{{TG}}\) pulse of 8 V pulse with durations from 1 s to 50 s. c The distinct \({V}_{{th},{BG}}\) values showed no detectable drift measured over 150 s, reaffirming the non-volatile retention. Similarly, the back-gate transfer characteristics of a d WSe2 FET were assessed by sweeping the \({V}_{{BG}}\) from −4 V to 0 V at \({V}_{{DS}}\) =1 V. e Four distinct negative \({V}_{{th},{BG}}\) bands (−1.25 V to −2.25 V) were achieved with no noticeable drift over time, confirming the non-volatile retention of the programmed \({V}_{{th},{BG}}\).

In Eq. (2), \({V}_{{{th}}_{o},{BG}}\) represents the threshold voltage of the back-gate without any mobile ions in the top-gate dielectric, \({Q}_{m}\) is the mobile ion charge, \({X}_{m}\) is the centroid of the mobile ion charge distribution, \({C}_{{TG}}\) is the capacitance of the top gate dielectric, and \({t}_{{TG}}\) is the thickness of the top gate dielectric. Figure 3b shows the back-gate transfer characteristics obtained by sweeping the \({V}_{{BG}}\) from −1 to 3 V at a constant \({V}_{{DS}}\) of 1 V for a representative MoS2 FET. The device exhibits tunable \({V}_{{th},{BG}}\) values, achieved by programming the LIPS. A fixed programming pulse of magnitude, \({V}_{{TG}}\,\)= 8 V was applied, with the pulse duration varied from 1 to 50 s, enabling discrete \({V}_{{th},{BG}}\) values ranging from 0.25 to 1.5 V. Notably, the device characteristics for each \({V}_{{th},{BG}}\) setting were measured 15 times over a span of 150 s, showing no detectable drift, as illustrated in Fig. 3c, confirming non-volatile retention of the programmed \({V}_{{th},{BG}}\). Similarly, we investigated threshold voltage engineering for p-type WSe2 FETs. Figure 3d shows the back-gate transfer characteristics obtained by sweeping the \({V}_{{BG}}\) from −4 to 0 V at a constant \({V}_{{DS}}\) of 1 V for a representative WSe2 FET after programming the LIPS through top-gate pulses. Four distinct bands of negative \({V}_{{th},{BG}}\) values, ranging from −1.25 to −2.25 V, were achieved. Here too, the device characteristics for each setting were measured 15 times, showing no drift, as seen in Fig. 3e, further confirming the non-volatile retention of the programmed \({V}_{{th},{BG}}\).

Supplementary Fig. 15a shows long-term retention of four distinct \({V}_{{th},{BG}}\) states in LIPS-gated MoS2 devices for over 103 s, with two states remaining stable beyond 104 s. Comparable results were obtained in LIPSe-gated MoS2 FETs, where four discrete \({V}_{{th},{BG}}\) levels were also retained (Supplementary Fig. 15b). While these results demonstrate excellent non-volatile programmability, periodic refresh of \({V}_{{th},{BG}}\) may be required for even longer retention times. Given the low power required for programming, such refresh operations are not difficult to implement and resemble established practices in conventional Si CMOS, such as periodic refresh cycles in dynamic random-access memory (DRAM). This suggests that thiophosphate-gated 2D FETs can combine non-volatile programmability with practical refresh strategies to ensure robust long-term circuit operation. We next examined the relationship between programming voltage amplitude (\({V}_{{TG}}\)) and the required pulse duration (\({\tau }_{P}\)) for \({V}_{{th},{BG}}\) tuning in thiophosphate-gated FETs. As shown in Supplementary Fig. 16a, b, MoS2 FETs with LIPS and LIPSe top-gate dielectrics exhibit distinct programmed \({V}_{{th},{BG}}\) states (baseline and tuned) that can be achieved with different combinations of \({V}_{{TG}}\) and \({\tau }_{P}\). For LIPS-gated devices, stable programming was obtained with \({V}_{{TG}}\) = 14 V and \({\tau }_{P}\) as short as 100 ms, corresponding to a ~500× reduction compared to \({\tau }_{P}\) = 50 s. Similarly, in LIPSe-gated devices, increasing \({V}_{{TG}}\) from 6 V to 12 V shortened \({\tau }_{P}\) from 10 s to 50 ms, nearly 200× faster. These results confirm that \({\tau }_{P}\) is not constrained by intrinsic material limitations but can be engineered through the applied programming field, enabling fast, energy-efficient, and non-volatile \({V}_{{th},{BG}}\) tuning in 2D FETs.

We also designed an experiment to assess the mobility of Li+ ions in LIPS. Supplementary Fig. 17a shows the \({I}_{{DS}}\) of a representative LIPS dual-gated MoS2 transistor measured over 100 s at a constant \({V}_{{BG}}\) of 2 V and \({V}_{{DS}}\) of 1 V with a \({V}_{{TG}}\) of 4 V. Over time, the migration of Li⁺ ions within the LIPS induces a continuous shift in \({V}_{{th}}\), which manifests as a monotonic increase in \({I}_{{DS}}\). To establish a baseline for comparison, Supplementary Fig. 17b displays the initial back-gate transfer characteristics of the same transistor prior to the experiment, along with a theoretical fit obtained using the virtual source (VS) model62,63,64. The \({V}_{{th}}\) was extracted from this fit and subsequently tracked as a function of time using the data from Supplementary Fig. 17a. The resulting time evolution of \({V}_{{th}}\) is depicted in Supplementary Fig. 17c. Next, the centroid of the Li+ ion charge distribution, \({X}_{m}\), was calculated using Eq. (1). Supplementary Fig. 17d shows \({X}_{m}\) as a function of time alongside a fit created using Eq. (3) listed below.

Here, \({\mu }_{m}\) is the mobility of Li+ ions, \(E={V}_{{TG}}/{t}_{{TG}}\) is the electric field, and \({D}_{m}\) is the diffusion coefficient of the Li+ ions. We found that \({\mu }_{m}\) = 0.55\(\times\)10−18 m2 V−1 s−1, and \({D}_{m}\) = 11.06\(\times\)10−18 m2 s−1. These values are in reasonable agreement with literature reports for Li⁺ ion transport in solid electrolytes, further validating our experimental methodology and analysis.

Evaluation of CMOS inverters using LIPS-gated 2D FETs

Next, we assess the performance of 2D CMOS inverters based on LIPS-gated n-type MoS2 an p-type WSe2 FETs with different \({V}_{{th},{BG}}\) values. To systematically analyze their impact, we select three distinct \({V}_{{th},{BG}}\) levels for both n- and p-type FETs, respectively, ensuring drain current values of 10 pA/µm, 100 pA/µm and 1 nA/µm at \({V}_{{BG}}\) = 0 V as shown in Fig. 4a. We will refer to these current values as \({I}_{{OFF},N}\) and \({I}_{{OFF},P}\), allowing us to investigate how different threshold voltages influence inverter behavior. The voltage transfer characteristics of CMOS inverters constructed with these \({V}_{{th},{BG}}\) combinations at \({V}_{{DD}}\) = 2 V are presented in Fig. 4b. Corresponding transient inverter responses are provided in Supplementary Fig. 18. Figure 4c depicts the extracted \({P}_{{static}}\) for different \({I}_{{OFF},N}\) and \({I}_{{OFF},P}\) combinations. Our results reveal that \({P}_{{static}}\) reaches as low as ~26 pW for the highest \({V}_{{th},{BG}}\) magnitudes, whereas \({P}_{{static}}\) rises to ~1 nW for the lowest \({V}_{{th}}\) magnitudes. This trend aligns with our expectations, as lower \({V}_{{th},{BG}}\) results in increased \({I}_{{OFF},N}\) and \({I}_{{OFF},P}\), leading to higher \({P}_{{static}}\). These findings underscore the critical role of precise \({V}_{{th}}\) engineering in achieving ultra-low-power CMOS logic design.

a Back-gate transfer characteristics illustrating different threshold voltages (\({V}_{{th},{BG}}\)) programmed in LIPS-gated n-type MoS2 and p-type WSe2 FETs, with corresponding off-currents (\({I}_{{OFF},N}\) and \({I}_{{OFF},P}\)) of 1 nA, 100 pA, and 10 pA per micrometer at \({V}_{{BG}}\,\)= 0 V. b Voltage transfer characteristics of CMOS inverters constructed from MoS2 and WSe2 FETs at varying threshold voltages, demonstrating the impact of threshold voltage engineering on inverter operation. c Extracted static power consumption (\({P}_{{static}}\)) for CMOS inverters, highlighting low power dissipation (~26 pW) at higher \({V}_{{th}}\) magnitudes and increased power (~1 nW) at lower \({V}_{{th}}\) magnitudes, underscoring the importance of \({V}_{{th}}\) engineering for ultra-low-power 2D CMOS inverter design. d Circuit schematics of a conventional CMOS inverter, a power-gated CMOS inverter using additional high-\({V}_{{th}}\) sleep transistors, and a \({V}_{{th}}\)-tuned CMOS inverter based on LIPS-gated MoS2/WSe2 FETs. \({V}_{{DD}}\) corresponds to the supply voltage applied to the CMOS inverters, \({V}_{{IN}}\) is the input voltage applied to the inverter modules, \({V}_{{OUT}}\) is the corresponding output voltage, \({C}_{L}\) is the load capacitance connected to the inverter output, \({V}_{{sleep}}\) corresponds to the input voltage applied to the sleep transistors. M1 and M4 are the corresponding n- and p-type sleep transistors used in power-gated CMOS inverters, whereas M2 and M3 correspond to the n- and p-type 2D FETs. e Benchmarking results of \({P}_{{static}}\) and Delay highlights that intrinsic \({V}_{{th},{BG}}\) modulation in LIPS-gated FETs enables built-in power gating without extra transistors, improving power, performance, and area (PPA) simultaneously compared to conventional approaches.

Beyond the experimental demonstration of \({V}_{{th}}\) engineering for low-power 2D CMOS inverters, we developed SPICE-compatible compact models for LIPS-gated 2D FETs using the industry-standard BSIM-IMG framework for double-gate FETs with independent gates. The models were calibrated to experimentally measured back-gated transfer characteristics across multiple programmed \({V}_{{th},{BG}}\) states (Supplementary Fig. 19a) and subsequently used to analyze inverter performance as a function of threshold voltage tuning. \({P}_{{static}}\) in these devices arises from gate leakage and subthreshold leakage. Because the gate leakage floor is extremely low (~0.1 pA), \({P}_{{static}}\) is dominated by the subthreshold leakage (\({I}_{{DS}}\) at \({V}_{{BG}}\) = 0 V) drawn from the supply voltage (\({V}_{{DD}}\)) for both logic states (0 and 1)45. As shown in Supplementary Fig. 19b, \({P}_{{static}}\) decreases strongly with increasing magnitude of \({V}_{{th},{BG}}\), dropping by more than four orders of magnitude at extreme threshold voltages (~1.4 V for MoS2 n-type FETs and –1.2 V for WSe2 p-type FETs). However, this comes at the expense of performance: transient simulations reveal that the propagation delay increases by ~5× under extreme \({V}_{{th},{BG}}\) compared to devices with \({V}_{{th},{BG}}\) tuned for a leakage floor of ~1 nA (Supplementary Fig. 19c). This establishes an inherent trade-off between power and speed. From this analysis, the optimal operating window is identified as \({V}_{{th},{BG}}\) = 0.35–0.6 V for n-type MoS2 and –0.6 to –0.25 V for p-type WSe2, which minimizes static power dissipation without significant performance loss.

We further benchmarked these devices against conventional CMOS power-gating scheme, where leakage suppression is achieved by inserting sleep transistors, i.e., a p-type FET and an n-type FET with high threshold voltage in the pull-up and pull-down network, respectively, as shown in Fig. 4d65. While effective, these additional transistors reduce overall circuit speed and increase area overhead. By contrast, the intrinsic \({V}_{{th},{BG}}\) modulation capability of LIPS-gated MoS2 and WSe2 FETs enables built-in power gating without additional devices. During active operation, \({V}_{{th},{BG}}\) can be tuned within the optimal window for balanced power–performance characteristics, while in sleep mode, \({V}_{{th},{BG}}\) can be shifted to extreme values to suppress leakage. As summarized in Fig. 4e, this approach improves power, performance, and area (PPA) simultaneously, paving the way for practical low power 2D CMOS circuits. Moreover, runtime \({V}_{{th},{BG}}\) tuning provides an additional degree of freedom to dynamically adjust the switching threshold, thereby enhancing noise margins and improving robustness against supply rail fluctuations.

Evaluation of dielectric strength of LIPS

Finally, we evaluate the dielectric strength of these thiophosphates. Figure 5a illustrates the transfer characteristics of a representative dual-gated (DG) MoS2 FET, where the back-gate voltage (\({V}_{{BG}}\)) is swept from 3 to −1 V, while gradually reducing the top-gate voltage (\({V}_{{TG}}\)) from 1 to −5 V. Notably, the maximum \({I}_{{ON}}\) is achieved when both the bottom and top gate voltages are set to positive values, facilitating maximum charge accumulation in the channel. However, it should be noted that the back-gate covers the complete MoS2 channel, extending beneath both the source/drain regions, allowing \({V}_{{BG}}\) to electrostatically control the MoS2 regions under the contacts. In other words, \({V}_{{BG}}\) can affect the width of the Schottky barrier formed at the 2D/contact interface allowing the back-gate to control the contact resistance and hence the charge injection in the channel. In contrast, the top-gate can only control the channel between the contacts. Therefore, while the on-state characteristics of dual-gated 2D FETs are entirely governed by \({V}_{{BG}}\), the off-state current and \({V}_{{th},{BG}}\) can be efficiently determined by \({V}_{{TG}}\), as the latter regulates the barrier height in the top-gated region of the channel. Interestingly, the relative strength of the two gates can be assessed by plotting back-gate \({V}_{{th},{BG}}\) as a function of the \({V}_{{TG}}\) as depicted in Fig. 5b. Note that the slope of the \({V}_{{th},{BG}}\) versus \({V}_{{TG}}\) curve remains constant for more negative \({V}_{{TG}}\), and then begins to decrease as \({V}_{{TG}}\) increases. This behavior is due to the channel being depleted for more negative \({V}_{{TG}}\), resulting in a negligible channel capacitance, \({C}_{{CH}}\) ~ 0. In this region, the slope of the \({V}_{{th},{BG}}\) versus \({V}_{{TG}}\) curve is proportional to the ratio of the back-gate capacitance (\({C}_{{BG}}\)) to the top-gate capacitance (\({C}_{{TG}}\)), i.e., \({C}_{{BG}}/{C}_{{TG}}\). For more positive \({V}_{{TG}}\), the channel enters accumulation, making \({C}_{{CH}}\) finite and adding to the total top-gate capacitance, causing the slope to decrease with increasing \({V}_{{TG}}\). Nevertheless, the constant slope regime of the \({V}_{{th},{BG}}\) versus \({V}_{{TG}}\) curve can be used to extract the effective dielectric constant of the top-gate dielectric (\({\kappa }_{{TG}}\)). Note that, \({C}_{{BG}}\) = 3.3 × 10−3 Fm−2, for our 25 nm Al2O3 with \({\kappa }_{{BG}}\) ~ 10, indicating that \({C}_{{TG}}\) ~ 1.8 × 10−3 Fm−2 since the slope was found to be ~1.85. Figure 5c shows the AFM image of the LIPS flake used in this device, revealing a thickness of ~53 nm and hence the effective dielectric constant can be estimated to be \({{{\rm{\kappa }}}}_{{LIPS}}\) ~ 41. Similarly, we extracted κ ≈ 12 for LIPSe as shown in Supplementary Fig. 20.

a Back-gate transfer characteristics, i.e., source to drain current (\({I}_{{DS}}\)) measured by sweeping the back-gate voltage (\({V}_{{BG}}\)) for different top-gate voltages (\({V}_{{TG}}\)) at a constant source-to-drain voltage, \({V}_{{DS}}\) = 1 V and b back-gate threshold voltage (\({V}_{{th},{BG}}\)) extracted using the iso-current method at \({I}_{{DS}}\) = 10 nA/µm as a function of \({V}_{{TG}}\) for LIPS gated MoS2 FETs. The slope of the \({V}_{{th},{BG}}\) versus \({V}_{{TG}}\) curve is proportional to the ratio of the back-gate and top-gate effective oxide thickness (\({EOT}\)) values. c Atomic force microscopic (AFM) image along with the thickness across the dotted line of LIPS film used as top-gate dielectric for MoS2 FET. The AFM analysis reveals a height of ~ 53 nm, estimating a relative dielectric constant of ~ 41 for LIPS.

Next, we evaluated the reliability of LIPS as a top-gate dielectric under repeated Li⁺ migration. Programming/reset endurance tests were performed by toggling \({V}_{{TG}}\) between ± 8 V for up to 106 cycles. To assess dielectric stability, we tracked the effective permittivity (\({\kappa }_{{LIPS}}\)) throughout cycling. Supplementary Fig. 21a shows representative back-gate transfer characteristics after stress levels ranging from 100 to 106 cycles, while \({\kappa }_{{LIPS}}\) was extracted from the slope of \({V}_{{th},{BG}}\) versus \({V}_{{TG}}\) plots (Supplementary Fig. 21b). Both the ratio \({V}_{{th},{BG}}\)/\({V}_{{TG}}\) (Supplementary Fig. 21c) and the derived \({\kappa }_{{LIPS}}\) (Supplementary Fig. 21d) remained essentially unchanged up to 106 cycles, confirming stable high-κ response without measurable dielectric degradation. Furthermore, the top-gate leakage current (\({I}_{{TG}}\)) remained low and stable across the entire endurance window (Supplementary Fig. 21e), indicating no evidence of ion-induced leakage paths. Collectively, these results demonstrate that the Li⁺-driven programming mechanism preserves the structural and electrical integrity of LIPS, establishing it as a reliable vdW dielectric for long-term operation.

It is important to note that lithium is traditionally regarded as a mobile ion contaminant in advanced Si CMOS fabrication. However, the van der Waals (vdW) dielectric paradigm employed here is fundamentally distinct from unintentional Li incorporation in conventional oxides or interlayers. In LIPS and LIPSe, Li is structurally incorporated into a crystalline lattice rather than introduced as a random impurity. As demonstrated experimentally, Li⁺ migration in these materials is both programmable and spatially confined, enabling discrete and stable \({V}_{{th},{BG}}\) states with no observable drift under repeated cycling. Potential reliability concerns can be further addressed through well-established mitigation strategies. For example, ultrathin blocking or buffer layers (e.g., ultrathin h-BN or Al2O3) can be incorporated to confine ion motion within a safe spatial window, thereby preventing undesired drift into the channel. Analogous approaches are widely employed in industry, where diffusion barriers such as Ta, TaN, and TiN are used to block Cu⁺ migration out of interconnects and into surrounding dielectrics66,67,68. These barriers ensure that Cu⁺ remains confined within the metal lines, preserving reliability while enabling continued device scaling. A more ambitious route involves engineering, the dielectric thickness and electric field profile such that ion migration becomes inherently self-limited. In this scenario, Li⁺ ions rapidly occupy stable interstitial or trapping sites near the semiconductor–dielectric interface, beyond which further drift is energetically suppressed. Finally, we note that analogous functionality can be achieved using other members of the thiophosphate family, such as CuInP2S6, where Cu⁺ migration provides a similar handle for \({V}_{{th}}\) programming. More broadly, the bimetallic thiophosphate family (ABP2X6, A = Li, Ag, Cu, Cr, etc., B = In, Sc, V, etc., and X = S, Se) offers extensive chemical diversity, with many constituent elements already compatible with standard CMOS process flows. Furthermore, the dual-gated architecture employed here allows one gate to serve as an ionic programming terminal, while the other can be dedicated to high-speed operation under biasing conditions that suppress further ion drift. Collectively, these considerations underscore the practicality of integrating vdW thiophosphates into future CMOS platforms without compromising device reliability.

We also note that the on-state current in dual-gated 2D FETs is partly limited by the lateral dimensions of the exfoliated LIPS/LIPSe flakes, which are typically >1 µm in length. In our scaled MoS2 devices with a channel length (\({L}_{{ch}}\)) of 200 nm and 25 nm thick Al2O3 back-gate dielectric, we observe a maximum on-state current of 140 µA/µm with a median value of 90 µA/µm. Furthermore, scaling down the back-gate dielectric to a thinner 10 nm high-κ layer (HfO2) enables on-state currents exceeding 250 µA/µm for n-type MoS2 FETs and 185 µA/µm for p-type WSe2 FETs as shown in Supplementary Fig. 22a–c. In addition, LIPSe-gated MoS2 FETs deliver a maximum on-current of 32 µA/µm (median 22 µA/µm) for \({L}_{{CH}}=\)1 μm, with excellent on/off ratios >10⁷ and subthreshold slopes as low as ~70 mV/decade as shown in Supplementary Fig. 23. These results highlight that high-performance drive currents are not only achievable but are consistently attainable in aggressively scaled 2D FETs.

In conclusion, we show that ion-migration in vdW thiophosphates enable non-volatile, programmable \({V}_{{th}}\) engineering in 2D FETs, offering precise control, long retention, and robust endurance. By leveraging \({V}_{{th}}\) tuning in LIPS-gated n-type MoS2 and p-type WSe2 FETs, we demonstrated 2D CMOS inverters with \({P}_{{static}}\) reduced to ~26 pW. Compact modeling reveals an optimal \({V}_{{th}}\) window balancing leakage and speed, while dynamic tuning provides built-in power gating without added transistors, enhancing power, performance, and area (PPA). Collectively, these results highlight the critical role of \({V}_{{th}}\) engineering in optimizing 2D CMOS circuits and underscore the importance of developing novel vdW dielectrics to address power consumption challenges in 2D FET technology.

Methods

Synthesis of LaOBr crystals

Lanthanum carbonate octahydrate (99.95%, Ganzhou Wanfeng Adv. Materials Tech. Co., Ltd.) was used as the starting material without further purification. LaBr3·7H2O was prepared by dissolving the oxide in concentrated hydrobromic acid (47%, Fisher Scientific) and crystallizing the heptahydrate from an acidic solution (pH ~5) on a steam bath. A mixture of 5 g of LaBr3·7H2O, 4.2 g of NaBr (99%, LachNer), and 10.9 g of MgBr2 (98%, Sigma-Aldrich) was placed in a corundum crucible, heated to 150°C for 5 h to evaporate water, then gradually raised to 1000 °C at 2 °C/min for 48 h. The mixture was then cooled to 650 °C at 0.1 °C/min to grow LaOBr crystals. After cooling, the crucible was leached in boiling water for 24 h, and the product was separated by vacuum filtration. MgO impurities were removed by washing with dilute sulfuric acid, yielding colorless LaOBr platelets up to 1 mm in size.

Synthesis of BiOBr crystals

BiOBr crystals were prepared by crystallization from aqueous solution. In total, 3 g of bismuth oxide (99.99, Alfa Aesar, Germany was dissolved in 50 mL of boiling hydrobromic acid (40 wt.%). After dissolving bismuth oxide, to the reaction mixture is added 2 L of boiling water and boiling continue till any formed precipitate is dissolved. Reaction vessel is covered with heat insulation and overnight cooled on room temperature. Platelet crystals were separated by suction filtration, washed with water and acetone and dried in vacuum oven at 50 °C.

Synthesis of BiOCl crystals

BiOCl crystals were prepared from aqueous solution. 3 g of bismuth oxide (99.99, Alfa Aesar, Germany) were dissolved in 300 mL of 10 wt.% hydrochloric acid at 90 °C. After dissolving all bismuth oxide is added 2.5 L of boiling water and the boiling is continued till clear solution is formed. Subsequently, the vessel was covered with heat isolated and freely cooled on room temperature overnight. Formed platelet BiOCl crystals are separated by suction filtration, washed with water and acetone and dried in vacuum oven at 50 °C.

Synthesis of LiInP2S6 (LIPS) and LiInP2Se6 (LIPSe) crystals

LIPS and LIPSe crystals were grown using the Chemical Vapor Transport (CVT) method in a two-zone furnace. Pre-synthesized polycrystalline LIPS69 and LIPSe70 materials (2.5 g) were initially combined with transport agent I2 (50 mg) and loaded into a fused silica tube with 16 mm and 18 mm inner and outer diameters, respectively and a length of 28 cm. The mixture was sealed under vacuum conditions using an oxy/natural gas torch. The CVT growth process involved two temperature zones: Source Zone (660 °C): The mixture was placed in this zone. Over 12 h, the temperature increased to 560 °C and held there for 4 h. Subsequently, it was heated to 660 °C over 3 h and maintained for 144 h. Finally, the temperature was reduced to ambient levels over 12 h. Deposition Zone (560 °C): LIPS and LIPSe crystals were obtained in this zone. The heating process followed a similar pattern: 12 h to 660 °C, 4 h holding time, 3 h to 560 °C, 144 h holding time, and cooling to ambient temperature over 12 h. Notably, these LIPS and LIPSe crystals were collected from the CVT tubes inside the N2-filled glovebox, as these crystals are highly sensitive to humidity. Furthermore, these crystals are characterized directly without any further processing steps. The resulting crystals exhibit uniform-plane surfaces, making them suitable for device fabrication.

Synthesis of CuInP2S6 (CIPS) crystals

CuInP2S6 synthesis was performed in quartz ampoule by chemical vapor transport. In quartz ampoule were placed powder copper (99.9%, −100 mesh, STREM, USA], indium (99.99, −100 mesh, Wuhan Xinrong New Materials Co., China) with sulfur (99.9999%, 2–6 mm, Wuhan Xinrong New Materials Co., China} and phosphorus (99.9999%, 2–6 mm, Wuhan Xinrong New Materials Co., China) in stochiometric ratio corresponding to 15 g and melt sealed under high vacuum (1 × 10–3 Pa) using oil diffusion pump and LN2 trap. As a vapor transport medium were added iodine (0.5 g) and sulfur and phosphorus were used in 1 at. % excess towards stoichiometry. The ampoule was first heated in muffle furnace and heated on 450 °C for 25 h, on 500 °C for 50 h and on 600 °C for 50 h. The reaction mixture was mechanically homogenized by shaking and ampoule was placed in two zone horizontal furnaces. First the source zone was heated on 500 °C and growth zone on 700 °C. After 2 days, the thermal gradient was switched, and the source zone was kept on 700 °C while the growth zone on 600 °C. After 10 days, the ampoule was cooled at room temperature and opened in an argon filled glovebox, where the material was stored.

Large-area monolayer MoS2 film growth

Monolayer MoS2 films were grown on a 2-inch pre-scored, double-side polished c-plane sapphire substrate using metalorganic chemical vapor deposition (MOCVD). A cold-wall horizontal reactor with an inductively heated graphite susceptor and wafer rotation was employed to ensure uniform deposition, as detailed in previous work71. Molybdenum hexacarbonyl (Mo(CO)6) and hydrogen sulfide (H2S) served as the precursors. The metal precursor, Mo(CO)6, was maintained at 10 °C and 950 Torr in a stainless-steel bubbler, delivering a flow of 0.036 sccm, while 400 sccm of H2S was supplied. The deposition took place at 1000 °C and 50 Torr under a hydrogen atmosphere, achieving monolayer growth in 18 min. Prior to growth, the substrate was preheated to 1000 °C in H2 for 10 min. Following deposition, the substrate was cooled in H2S to 300 °C to prevent decomposition of the MoS2 film.

Large-area WSe2 film growth

Multilayer WSe2 was grown on a 2-inch diameter c-plane sapphire substrate using metal-organic chemical vapor deposition (MOCVD) at Penn State’s 2D Crystal Consortium Materials Innovation Platform (2DCC-MIP) facility. The MOCVD system featured a cold-wall horizontal reactor with an inductively heated graphite susceptor and gas-foil wafer rotation71. Tungsten hexacarbonyl (W(CO)6) with ≥99.9% trace metals purity, obtained from Sigma-Aldrich, LLC, served as the metal precursor, while hydrogen selenide (H2Se) was used as the chalcogen precursor. Hydrogen (H2) acted as the carrier gas. The W(CO)6 powder was maintained at 30°C and 400 torr in a stainless-steel bubbler. The synthesis followed a multi-step process—nucleation, ripening, and lateral growth. Specifically, nucleation occurred for 30 s at 850 °C, followed by ripening at 850 °C for 5 min and then at 1000 °C for another 5 min, with subsequent growth at 1000 °C for a set duration. During lateral growth, the tungsten flow rate was 3.8 × 10⁻³ sccm, and the chalcogen flow rate was 75 sccm, while the reactor pressure was maintained at 200 torr. Afterward, WSe2 was annealed in an H2 and H2Se atmosphere for 10 min, with the same ambient maintained for 8 min during cooling to facilitate metal adatom diffusion and reduce selenium vacancies. Under these conditions, multilayer WSe2 was achieved across the 2-inch substrate with a growth time ranging from 25 to 35 min.

Fabrication of back gated 2D FETs

To define the channel regions of the MoS2 transistors discussed in this work, the ALD deposited 25 nm thick Al2O3, HfO2 and ZrO2 substrates, with MoS2/WSe2 transferred on top, was spin-coated with PMMA A6 (4000 RPM for 45 s) and baked at 180 °C for 90 s. The resist was then exposed using a Raith EBPG5200 e-beam lithography tool and developed using a 1:1 mixture of 4-methyl-2-pentanone (MIBK) and IPA (60 s) and then rinsed using IPA (45 s). The exposed monolayer MoS2 film was subsequently etched using a sulfur hexafluoride (SF6) RIE process at 5 °C for 30 s. Next, the sample was rinsed in acetone and IPA to remove the e-beam resist. A subsequent lithography step was conducted to form source/drain electrodes. The substrate was spin-coated at 4000 RPM for 45 s with methyl methacrylate (MMA) EL6 and PMMA A3; following application, these resists were baked at 150 °C for 90 s and 180 °C for 90 s, respectively. E-beam lithography was again used to pattern the source and drain, and development was again performed using a 1:1 mixture of MIBK/IPA and an IPA rinse for the same times as previously. 40 nm of Ni and 30 nm of Gold (Au) were deposited using e-beam evaporation to form the electrodes in case of MoS2 FETs and 40 nm of Pd and 30 nm of Gold (Au) for WSe2 FETs. Finally, a lift-off process was performed to remove the excess Ni/Au by immersing the sample in acetone for 1 h, followed by IPA for another 30 min to clean the substrate.

Fabrication of back gated 2D FETs with vdW interfacial layers

First, the 2D dielectric crystals (LaOBr, BiOBr, BiOCl, LIPS and CIPS) were mechanically exfoliated on 25 nm thick Al2O3 substrates. To define the channel regions of the MoS2 transistors in this study, with MoS2 wet transferred on top, the substrate was spin-coated with PMMA A6 (4000 RPM for 45 s) and baked at 180 °C for 90 s. The resist was then exposed using a Raith EBPG5200 e-beam lithography tool and developed with a 1:1 mixture of 4-methyl-2-pentanone (MIBK) and IPA for 60 s, followed by a 45 s IPA rinse. The exposed monolayer MoS2 film was etched using an SF6 RIE process at 5 °C for 30 s. Afterward, the sample was cleaned in acetone and IPA to remove the e-beam resist. A second lithography step was performed to form the source/drain electrodes. The substrate was spin-coated at 4000 RPM for 45 s with methyl methacrylate (MMA) EL6 and PMMA A3; these resists were baked at 150 °C and 180 °C for 90 s each. E-beam lithography was used again to pattern the source and drain, followed by development with MIBK/IPA and an IPA rinse, as before. For MoS2 FETs, 50 nm of Ni and 30 nm of Au were deposited via e-beam evaporation to form the electrodes. Finally, a lift-off process was conducted to remove excess Ni/Au by soaking the sample in acetone for 1 h, followed by a 30-min IPA rinse to clean the substrate.

Fabrication of dual-gated 2D FETs

To begin with, monolayer MoS2 was transferred on 25 nm thick Al2O3 substrates. The substrate was spin-coated with PMMA A6 (4000 RPM for 45 s) and baked at 180°C for 90 s. The resist was then exposed using a Raith EBPG5200 e-beam lithography tool and developed with a 1:1 mixture of 4-methyl-2-pentanone (MIBK) and IPA for 60 s, followed by a 45 s IPA rinse. The exposed monolayer MoS2 film was etched using an SF6 RIE process at 5 °C for 30 s. Afterward, the sample was cleaned in acetone and IPA to remove the e-beam resist. Next, the 2D dielectrics were mechanically exfoliated on top of the pre-patterned MoS2 channels. A second lithography step was performed to form the source/drain and top-gate electrodes. The substrate was spin-coated at 4000 RPM for 45 s with methyl methacrylate (MMA) EL6 and PMMA A3; these resists were baked at 150 °C and 180 °C for 90 s each. E-beam lithography was used again to pattern the source and drain, followed by development with MIBK/IPA and an IPA rinse, as before. For MoS2 FETs, 50 nm of Ni and 30 nm of Au were deposited via e-beam evaporation to form the electrodes. Finally, a lift-off process was conducted to remove excess Ni/Au by soaking the sample in acetone for 1 h, followed by a 30-min IPA rinse to clean the substrate.

Raman spectroscopy

Raman spectroscopy of the MoS2 and WSe2 films were performed using a Horiba LabRAM HR Evolution confocal Raman microscope with a 532 nm laser. The laser power was initially set to 34 mW and reduced to 1.7 mW using a 1% filter. A ×100 objective with a 0.9 numerical aperture was used, with a grating spacing of 1800 g/mm for Raman spectroscopy and 300 g/mm for PL spectroscopy. For the 2D dielectrics, the Raman spectra was collected using confocal SPID Nano Raman and TERS System, equipped with an excitation wavelength 633 nm.

X-ray diffraction

Powder X-ray diffraction patterns of synthesized crystals were obtained using a Rigaku Miniflex600 X-ray diffraction system equipped with a Dtex silicon 1-D detector. The Cu Kα radiation (wavelength λ = 1.5406 Å) was generated by applying a voltage of 40 kV and a current of 15 mA. The radiation was filtered with a graphite monochromator and a Kβ foil filter. A zero-background silicon holder was used for the measurements.

X-ray photoelectron spectroscopy

X-ray Photoelectron Spectroscopy (XPS) Measurements were performed using a Thermo Scientific NEXSA G2 XPS equipped with an electron flood gun and a scanning ion gun at room temperature. The crystals were placed on copper tape, which served as the adhesive substrate. The data were analyzed using Thermo Scientific Avantage Data System software.

Atomic force microscopy

Atomic force microscopy was utilized to investigate the thickness profile of exfoliated multilayer flakes before and after plasma treatments. RTESPA-150 probe tips were used with a Bruker Dimension Icon AFM. All images were collected in peak force tapping mode with a peak force of 12 nN and a scan rate of 0.5 Hz. Images were processed and exported using Nanoscope.

Scanning electron microscopy

Scanning electron microscopy (SEM): Scanning electron microscopy (SEM) of the 2D MoS2 transistors used in this study was conducted using a Zeiss Gemini 500 field emission scanning electron microscopy (FESEM) system at an accelerating voltage of 5 kV.

Energy-dispersive X-ray spectroscopy (EDS)

EDS analysis was performed on micrometer-sized bulk crystal flakes using an ESEM Q250 SEM instrument. A tungsten source with an accelerating voltage of 30 kV was utilized to determine the elemental composition of the crystals.

Density functional theory

All the Density Functional theory (DFT) calculations were performed by using the Quantum Atomistic Tool Kit with the Linear Combination of Atomic Orbitals (LCAO) as the basis set. Perdew–Burke–Ernzerhof (PBE) method calculates the electronic exchange interaction and the exchange-correlation functionals described within generalized gradient approximation (GGA). “PseudoDojo” pseudopotential is taken with a “Medium” basis set. The Brillouin-zone integrations were performed with Monkhorst-Pack k-points with a grid sampling of 9 × 9 × 1 and kinetic cutoff energy to 125 Hartree. The Grimme (DFT-D2) correction was used to describe the van der Waals interaction (vdW) interactions. A vacuum region of 12 Å along the z-direction is utilized to avoid interaction between adjacent slab surfaces. All the geometric structures of BiOBr/MoS2, BiOCl/MoS2, LaOBr/MoS2, LIPS/ MoS2 and CIPS/MoS2 heterostructures are shown in Supplementary Fig. 6, with the corresponding lattice mismatch varying between 2.4 and 2.9%. After structure optimization, both MoS2 and 2D dielectrics (BiOBr, BiOCl, LaOBr, LIPS and CIPS) layers in 2D/2D heterostructures show no sign of distortion with the corresponding interlayer distance are 3.29 Å, 3.39 Å, 3.41 Å, 3.24 Å, 3.06 Å. All the heterostructures were fully relaxed to minimize the total energy until the force on each atom decreased less than 0.01 eV/Å, using a Limited Memory Broyden–Fletcher–Goldfarb–Shannon (LBFGS) method. The iteration control parameters comprised 200 steps with a 10−3 eV/Å3 stress tolerance limit.

Electrical characterization

Electrical characterization of the fabricated devices was performed using a semi-automated Formfactor 12000 probe station under atmospheric conditions with a Keysight B1500A parameter analyzer.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

Code availability

The codes used for plotting the data are available from the corresponding authors on request.

References

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Zhang, Y. et al. Recent progress in CVD growth of 2D transition metal dichalcogenides and related heterostructures. Adv. Mater. 31, 1901694 (2019).

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Dodda, A. et al. Active pixel sensor matrix based on monolayer MoS2 phototransistor array. Nat. Mater. 21, 1379–1387 (2022).

Schranghamer, T. F. et al. Radiation resilient two-dimensional electronics. ACS Appl. Mater. Interfaces 15, 26946–26959 (2023).

Ghosh, S. et al. An all 2D bio-inspired gustatory circuit for mimicking physiology and psychology of feeding behavior. Nat. Commun. 14, 6021 (2023).

Ghosh, S. et al. Monolithic and heterogeneous three-dimensional integration of two-dimensional materials with high-density vias. Nat. Electron. 7, 892–903 (2024).

Pendurthi, R. et al. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. Nat. Nanotechnol. 19, 970–977 (2024).

Jayachandran, D., Sakib, N. U. & Das, S. 3D integration of 2D electronics. Nat. Rev. Electr. Eng. 1, 17 (2024).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In 2021 IEEE International Electron Devices Meeting (IEDM) 7.2. 1–7.2. 4 (IEEE, 2021).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Lan, H.-Y., Tripathi, R., Liu, X., Appenzeller, J. & Chen, Z. Wafer-scale CVD monolayer WSe2 p-FETs with record-high 727 μA/μm I on and 490 μS/μm g max via hybrid charge transfer and molecular doping. In 2023 International Electron Devices Meeting (IEDM) 1−4 (IEEE, 2023).

Lan, H.-Y., Oleshko, V. P., Davydov, A. V., Appenzeller, J. & Chen, Z. “Dielectric interface engineering for high-performance monolayer MoS2 transistors via TaO x interfacial layer. IEEE Trans. Electron Devices 70, 2067–2074 (2023).

Lan, H.-Y., Tripathi, R., Appenzeller, J. & Chen, Z. Near-ideal subthreshold swing in scaled 2D transistors: the critical role of monolayer hBN passivation. IEEE Electron Device Lett. 45, 1337–1340 (2024).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Rasyotra, A. et al. Nanosheets derived from titanium diboride as gate insulators for atomically thin transistors. ACS Nano 19, 19646–19658 (2025).

Yu, B. et al. Gate engineering for deep-submicron CMOS transistors. IEEE Trans. Electron Devices 45, 1253–1262 (1998).

Das, M. et al. High-performance p-type field-effect transistors using substitutional doping and thickness control of two-dimensional materials. Nat. Electron. 8, 24–35 (2024).

Ravichandran, H. et al. A peripheral-free true random number generator based on integrated circuits enabled by atomically thin two-dimensional materials. ACS Nano 17, 16817–16826 (2023).

Ravichandran, H. et al. A monolithic stochastic computing architecture for energy efficient arithmetic. Adv. Mater. 35, 2206168 (2023).

Guo, Y. et al. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 106, 103109 (2015).

Ganapathi, K. L., Bhattacharjee, S., Mohan, S. & Bhat, N. High-performance HfO 2 back gated multilayer MoS2 transistors. IEEE Electron Device Lett. 37, 797–800 (2016).

Li, T., Du, G., Zhang, B. & Zeng, Z. Scaling behavior of hysteresis in multilayer MoS2 field effect transistors. Appl Phys. Lett. 105, 093107 (2014).

Cho, K. et al. Electric stress-induced threshold voltage instability of multilayer MoS2 field effect transistors. ACS Nano 7, 7751–7758 (2013).

Pan, Y. et al. Near-ideal subthreshold swing MoS2 back-gate transistors with an optimized ultrathin HfO2 dielectric layer. Nanotechnology 30, 095202 (2019).

Zhu, C. Y. et al. 2D indium phosphorus sulfide (In2P3S9): an emerging van der Waals high-k dielectrics. Small 18, 2104401 (2022).

Kim, Y. H. et al. Gate stack engineering of two-dimensional transistors. Nat. Electron. 8, 770–783 (2025).

Yao, Z. et al. Transferrable, wet-chemistry-derived high-k amorphous metal oxide dielectrics for two-dimensional electronic devices. Nat. Commun. 16, 1482 (2025).

Yuan, J. et al. High-κ samarium oxysulfate dielectric for two-dimensional electronics with enhanced gate coupling. Nat. Commun. 17, 1245 (2026).

Zhu, C.-Y. et al. Magnesium niobate as a high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 7, 1137–1146 (2024).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Sen, D. et al. Multifunctional 2D FETs exploiting incipient ferroelectricity in freestanding SrTiO3 nanomembranes at sub-ambient temperatures. Nat. Commun. 15, 10739 (2024).

Leong, W. S. et al. Tuning the threshold voltage of MoS2 field-effect transistors via surface treatment. Nanoscale 7, 10823–10831 (2015).

Yu, L. et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Jiang, J., Ahyi, A. C. & Dhar, S. Dual-gate MoS2 FET with a coplanar-gate engineering. IEEE Trans. Electron Devices 63, 573–577 (2015).

Yi, J. et al. Double-gate MoS2 field-effect transistors with full-range tunable threshold voltage for multifunctional logic circuits. Adv. Mater. 33, 2101036 (2021).

Zhang, H. et al. Complementary logic with voltage zero-loss and nano-watt power via configurable MoS2/WSe2 Gate. Adv. Funct. Mater. 28, 1805171 (2018).

Jeon, P. J. et al. Low power consumption complementary inverters with n-MoS2 and p-WSe2 dichalcogenide nanosheets on glass for logic and light-emitting diode circuits. ACS Appl. Mater. Interfaces 7, 22333–22340 (2015).

Ghosh, S. et al. A complementary two-dimensional material-based one instruction set computer. Nature 642, 327–335 (2025).

Ghosh, S. et al. High-performance p-type bilayer WSe2 field effect transistors by nitric oxide doping. Nat. Commun. 16, 5649 (2025).

Sen, D. et al. Complementary photoresponse in van der Waals heterostructures for insect-inspired neuromorphic vision. ACS Nano 20, 672–682 (2026).

Subbulakshmi Radhakrishnan, S. et al. A sparse and spike-timing-based adaptive photoencoder for augmenting machine vision for spiking neural networks. Adv. Mater. 34, 2202535 (2022).

Schranghamer, T. F. et al. Ultrascaled contacts to monolayer MoS2 field effect transistors. Nano Lett. 23, 3426–3434 (2023).

Jayachandran, D. et al. Insect-inspired, spike-based, in-sensor, and night-time collision detector based on atomically thin and light-sensitive memtransistors. ACS Nano 17, 1068–1080 (2023).

Oberoi, A. et al. Toward high-performance p-type two-dimensional field effect transistors: contact engineering, scaling, and doping. ACS Nano 17, 19709–19723 (2023).

Das, S. & Appenzeller, J. WSe2 field effect transistors with enhanced ambipolar characteristics. Appl. Phys. Lett. 103, 103501 (2013).

Osanloo, M. R., Van de Put, M. L., Saadat, A. & Vandenberghe, W. G. Identification of two-dimensional layered dielectrics from first principles. Nat. Commun. 12, 5051 (2021).

Jia, H. et al. Room temperature synthesis of BiOBr 1− x I x thin films with tunable structure and conductivity type for enhanced photoelectric performance. RSC Adv. 10, 41755–41763 (2020).

Jiang, Z. et al. Lanthanum oxyhalide monolayers: an exceptional dielectric companion to 2-D semiconductors. IEEE Trans. Electron Devices 70, 1509–1519 (2023).

Iqbal, M. W., Shahzad, K., Akbar, R. & Hussain, G. A review on Raman finger prints of doping and strain effect in TMDCs. Microelectron. Eng. 219, 111152 (2020).

Guo, Y. et al. Van der Waals polarity-engineered 3D integration of 2D complementary logic. Nature 630, 346–352 (2024).

Liang, J. et al. Manual shaking exfoliation of large-size two-dimensional LiInP2S6 nanosheets with exponential change in ionic conductivity for water detection. SmartMat 5, e1266 (2024).

Georgiou, V. et al. Ferroelectricity in polar polymer-based FETs: a hysteresis analysis. Adv. Funct. Mater. 28, 1705250 (2018).

Nikam, R. D., Kwak, M., Lee, J., Rajput, K. G. & Hwang, H. Controlled ionic tunneling in lithium nanoionic synaptic transistor through atomically thin graphene layer for neuromorphic computing. Adv. Electron. Mater. 6, 1901100 (2020).

Nikam, R. D. et al. Near ideal synaptic functionalities in Li ion synaptic transistor using Li3POxSex electrolyte with high ionic conductivity. Sci. Rep. 9, 18883 (2019).

Sadaf, M. U. K., Sakib, N. U., Pannone, A., Ravichandran, H. & Das, S. A bio-inspired visuotactile neuron for multisensory integration. Nat. Commun. 14, 5729 (2023).

Das, S., Dodda, A. & Das, S. A biomimetic 2D transistor for audiomorphic computing. Nat. Commun. 10, 3450 (2019).

Sebastian, A., Pannone, A., Subbulakshmi Radhakrishnan, S. & Das, S. Gaussian synapses for probabilistic neural networks. Nat. Commun. 10, 4199 (2019).

Jiang, H., Marek-Sadowska, M. & Nassif, S. R. Benefits and costs of power-gating technique. In 2005 International Conference on Computer Design 559–566 (IEEE, 2005).

Kim, H. et al. Robust TaNx diffusion barrier for Cu-interconnect technology with subnanometer thickness by metal-organic plasma-enhanced atomic layer deposition. J. Appl. Phys. 98, 014308 (2005).

Braud, F. et al. Ultra thin diffusion barriers for Cu interconnections at the gigabit generation and beyond. Microelectron. Eng. 33, 293–300 (1997).

Aubel, O., Hasse, W., Hommel, M. & Koerner, H. Model for the barrier diffusion into Cu interconnects at high temperatures. Microelectron. Eng. 82, 600–606 (2005).

Qian, Eric K. et al. Van der Waals Layered Chiral Structure with Alkali Cation Exchange in LiInP2S6. Chem. Mater. 36, 9718–9728 (2024).

Chica, Daniel G. et al. Direct thermal neutron detection by the 2D semiconductor 6LiInP2Se6. Nature 577, 346–349 (2020).

Choudhury, T.H. et al., Comparison of the MOCVD growth and properties of wafer-scale transition metal dichalcogenide epitaxial monolayers. 2D Materials 12, 045009 (2025).

Acknowledgements