Abstract

A low-cost, flexible processor is essential to realise affordable flexible electronic systems and transform everyday objects into smart-objects. Thin film transistors (TFTs) based on metal-oxides (or organics) are ideal candidates as they can be manufactured at low processing temperatures and low-cost per unit area, unlike traditional silicon devices. The development of complementary metal–oxide–semiconductor (CMOS) technology based on these materials remains challenging due to differences in performance between n- and p-type TFTs. Existing geometric rules typically compensate the lower mobility of the metal-oxide p-type TFT by scaling up the width-to-length (W/L) ratio but fail to take into account the significant off-state leakage current. Here we propose the concept of an optimal geometric aspect ratio which maximises the inverter efficiency represented by the average switching current divided by the static currents. This universal method is especially useful for the design of low-power CMOS inverters based on metal-oxides, where the large off-current of the p-type TFT dominates the static power consumption of the inverter. We model the inverter efficiency and noise margins of metal-oxide CMOS inverters with different geometric aspect ratios and compare the performance to different inverter configurations. The modelling results are verified experimentally by fabricating CMOS inverter configurations consisting of n-type indium-silicon-oxide (ISO) TFTs and p-type tin monoxide (SnO) TFTs. Notably, our results show that reducing W/L of metal-oxide p-type TFTs increases the inverter efficiency while reducing the area compared to simply scaling up W/L inversely with mobility. We anticipate this work provides a straightforward method to geometrically optimise flexible CMOS inverters, which will remain relevant even as the performance of TFTs continues to evolve.

Similar content being viewed by others

Introduction

Flexible electronic devices are fabricated on substrates such as paper, polymer and metal foil1. Metal-oxides, organics and amorphous silicon are commonly used active materials. Compared to traditional silicon devices, they offer a number of advantages including thinness, conformability and low manufacturing costs. Mature low-cost, thin, flexible and conformable devices have been succesfully developed. These include sensors2, memories3, batteries4, light-emitting diodes, energy harvesters5, near-field communication/radio frequency identification6 and printed circuitry such as antennas; essential electronic components to build any smart integrated electronic device. A low-cost flexible microprocessor employing CMOS technology is yet to be realised. Silicon processors are unsuitable as they are unlikely to reach a price point at which everyday items, such as bottles, food packaging, and wearables, can be turned into smart-objects. Therefore, there is a strong interest in low-power circuit designs and larger-scale integration of flexible thin film transistors (TFTs). Processors have been fabricated using low-temperature poly-silicon (LTPS) TFTs7 but high manufacturing costs and poor scalability of this technique make it unsuitable for high-volume, low-cost, flexible integrated smart systems8. Organics are also actively researched and excellent low-voltage CMOS inverters have been reported9,10,11. However, their use is limited to low-end backplane and circuit applications due to lower mobility, stability, uniformity and limited scalability8. Metal-oxides are arguably the most promising due to their high mobility, excellent spatial uniformity and scalability. A flexible processing engine fabricated with 0.8 μm n-type metal-oxide TFT technology has recently been reported12. It contains ~ 1000 gates (resistive load logic) and its gate-density is 45 times higher than previous metal-oxide processors3,6,12,13,14. The same authors have since fabricated a flexible 32-bit processor consisting of 18,334 gates14. Earlier this year, the same TFT technology was used to fabricate a flexible microprocessor using pseudo-CMOS logic15. While these works show the potential of metal-oxide processors, they also highlight its main shortcoming; only n-type TFTs were used since there is currently considered to be no compatible p-type material. Any further increase in gates requires CMOS technology as the static power consumption, Pstat, of unipolar technology becomes unfeasibly high14,15.

CMOS technology, which combines n- and p-type TFTs, benefits from low power consumption, high circuit integration density, high logic output, and high noise margins16. The development of thin film CMOS is therefore vital for low-cost flexible processors. Ideally, the output characteristics of n- and p-type TFTs in complementary inverters are perfectly matched. Indeed, the success of silicon CMOS is partly due to excellent control of n- and p-type MOSFET characteristics. In contrast the use of oxides and organics is challenging due to poor performance of oxide p-type and n-type organic TFTs relative to silicon MOSFETs.

Development of p-type oxide TFTs has been hampered by the low mobility and current-switching-ratio (Ion/Ioff) caused by the high off-state current, Ioff, that is typically observed17,18. Cuprous oxide (Cu2O) and tin monoxide (SnO) TFTs demonstrate promising results but mobilities are generally limited to ~ 1 cm2/Vs18,19. Both these materials, but primarily SnO, have been used in all-oxide CMOS inverters19,20. A high geometric aspect ratio, (W/L)p/(W/L)n, is normally used to increase the maximum output current, Imax, of the p-type TFT to match the n-type TFT using the same design rule that is applied to silicon CMOS.

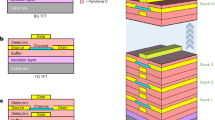

For silicon CMOS this method results in an excellent match of the n- and p-type output characteristics provided the threshold voltages (Vth) of the n- and p-type transistor are approximately equal and opposite in sign (ideally close to 0 V). Moreover, the transistors should fit the standard MOSFET equations well with a constant saturation mobility. As a result, the propagation delays of the low-to-high and high-to-low transitions are roughly equal and the switching voltage is approximately VDD/2, maximising noise margins. In the Supplementary Information, the static states of the CMOS inverter and dynamic low-to-high and high-to-low transitions are illustrated, along with the terminology for the different performance variables used in this work (Fig. S1). Ideally, both the n- and p-type transistors exhibit complete channel depletion in the off-state and have a turn-on voltage, Von, of ~ 0 V. In this case, the minimum output current at VGS = 0 V, Imin, and Ioff both remain constant as the width-to-length ratio (W/L) (or VDS) is increased. Since the static current of the p-type device equals Imin, increasing (W/L)p (or VDS) does not affect Pstat of the inverter. This represents the ideal (‘silicon’) scenario (Fig. 1a,b,f,g). Note there are subthreshold models for Si transistors showing the off-current roughly scales with W/L and therefore Pstat of the inverter does increase with W/L21. However, for Si CMOS inverters the effect is negligible as the overall power consumption is dominated by the dynamic power (due to the higher operation frequency and low off-current).

Transfer characteristics and output characteristics of: (a,f) ‘ideal silicon’ n-type transistor with Von ~ 0 V and complete channel depletion; Ioff = Imin,n does not scale with (W/L)n. (b,g) p-type transistor with Von ~ 0 V and complete channel depletion; to match the higher mobility of the n-type, Imax,p is scaled by (W/L)p, Ioff = Imin,p does not scale with (W/L)p. (c,h) p-type transistor with Von > 0 V and complete channel depletion; at VGS = 0 V the transistor is partly turned on and both Imax,p and Imin,p scale with (W/L)p. (d,e,h) ‘oxide’ p-type transistor without complete channel depletion; both Ioff and Imin,p scale with (W/L)p. (i) Maximum and minimum output currents for n- (green) and p-type transistors, and the ratio between them after scaling with (W/L)p.

Simply scaling W/L inversely with mobility does not work well for (flexible) TFTs based on metal-oxides and organics as large differences (in mobility, subthreshold swing, Ion, Ioff, Vth) remain between the performance of n- and p-type TFTs. It is therefore surprising to see that this method is widely used for TFT-based CMOS inverters. As reported for Cu2O17, we observe in SnO that Ioff scales with VDS and (W/L)p. This dependence is likely due to accumulation of electrons in the off-state, which decreases channel resistance17. This suggests a common mechanism for p-type oxides. Therefore, increasing (W/L)p also increases Ioff and Imin (Fig. 1d,e,h). Considering Ioff of metal-oxide p-type TFTs is typically at least tenfold higher than for its n-type counterpart, simply scaling up (W/L)p so that Imax,n = (W/L)pImax,p creates an even greater mismatch between the off-currents and directly increases Pstat of the inverter. A similar effect can be observed for p-type (n-type for organics case, referred to in brackets from here onwards) transistors where Von is considerably above (below) 0 V. The transistor is now partly turned on at VGS = 0 V and Imin also scales with VDS and W/L (Fig. 1c,h). This can be observed in many transistors, including n-type organic and p-type oxide TFTs, where precise control of characteristics remains challenging. The dependence of Imin on W/L is likely to remain an issue even as the performance of TFTs improves. Moreover, new transistor technologies may emerge in the future with similar characteristics.

In this work, we experimentally investigate the effects of changing W/L of a p-type SnO TFT on the voltage transfer characteristics (VTC) and current transfer characteristics (CTC) of all-oxide CMOS inverters. We fabricated n-type amorphous indium-silicon-oxide (a-ISO) TFTs and p-type SnO TFTs to combine them into all-oxide CMOS inverters. A model was developed to verify CMOS performance and compare it to the ideally matched case, as well as a unipolar resistive load inverter. We define inverter efficiency, Ip/Istat, as the average switching current (Ip) divided by the sum of the static currents (Istat). We show that reducing W/L of oxide p-type TFTs increases Ip/Istat compared to simply scaling up W/L inversely with mobility, while reducing the area.

Finally, we propose the concept of an optimal geometric aspect ratio which is universally applicable to silicon, metal-oxide and organic complementary inverters. This ratio determines the W/L of the p-type (n-type) transistor that best matches the maximum and minimum output currents of both n- and p-type TFTs equally so that inverter efficiency is maximised. This is critical to reduce the static power consumption (Pstat) and enable large-scale integration of metal-oxide TFTs. We estimate that by using the approach developed in this work it is possible to reduce Pstat by a factor > 100 and increase Ip/Istat by a factor > 100, compared to unipolar resistive technology, based on the current performance of p-type SnO TFTs, thus enabling a further increase in gate density.

Characteristics of n-type a-ISO and p-type SnO TFTs

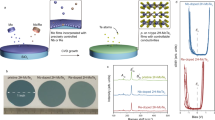

Figure 2d,i show schematics of the a-ISO and SnO TFTs (fabrication details provided in “Methods”). The a-ISO TFT (W/L = 20) has an ideal Von of ~ 0 V and Ioff of ~ 400 pA as shown in Fig. 2a. Ioff is independent of VDS which demonstrates complete channel depletion. The subthreshold swing (SS) is 0.35 V/dec, the Ion/Ioff is ~ 106 for VDS = 10 V, and the threshold voltage (Vth) is 0.2 V. The mobility increases linearly and reaches 4 cm2/Vs at VGS = 20 V. For the SnO TFT (Fig. 2b,c), Von is ~ 8 V and Ioff ranges from 200 pA to 20 nA as VDS varies from − 0.1 to − 10 V (for W/L = 100) indicating the difficulty to turn off the device. This scaling of Ioff with VDS and W/L is commonly observed for p-type oxides like SnO and Cu2O17,22,23,24,25. The SnO transfer characteristics in Fig. 2c exhibit similar dependence; for W/L ratios of 20, 50 and 100, Ioff is 280, 750 and 1400 pA respectively. The parameters of the SnO TFT are as follows; SS = 2.5 V/dec, the Ion/Ioff is ~ 2 × 104 for VGS = [− 10 V, 30 V], and Vth = 2.3 V. The mobility increases linearly up to VGS = − 10 V and then saturates at ~ 1 cm2/Vs, as shown in Fig. 2b. Hysteresis is a common problem for SnO TFTs and is likely caused by the high trap state density near the interface between the SnO layer and the SiO2 insulator. It has been shown that (alumina) interfacial layers can help to reduce the high trap state density26.

Experimentally measured transfer characteristics and linear mobility of (a) a-ISO TFT and (b) SnO TFT. Transfer characteristics of SnO TFT with different W/L ratios (c). Output characteristics (red) and modelled curves (blue) of the a-ISO TFT and the SnO TFT (b,d) in log (e,f) and linear scales (g,h). Schematic cross section of (d) the a-ISO TFT and (i) SnO TFT.

The output characteristics of both TFTs exhibit a clear linear and saturation region as shown in Fig. 2g,h (W/L = 20 for both TFTs). The saturation current of the a-ISO TFT ranges from Imin,n = 300 pA (VGS = 0 V) to Imax,n = 35 µA (VGS = 10 V). The range of the SnO TFT ((W/L)p = 20) is smaller and varies from Imin,p = 60 nA to Imax,p = 7 µA. In a CMOS inverter, the output characteristics of the n- and p-type transistors are ideally matched exactly, and usually (W/L)p is increased to match the higher mobility and on-current of the n-type device. This can be achieved by setting (W/L)p = 100. In this case the output currents align more closely for VGS = [3, 5, 10 V] but the gap increases for VGS = [0, 1 V] since Ioff of the p-type device scales with (W/L)p. This raises the question whether increasing (W/L)p actually improves the inverter performance.

Modelling of inverters

A model for the output characteristics was developed based on the standard MOSFET equations modified by a pre-factor, \(\alpha \left({V}_{GS}-{V}_{\mathrm{th},\mathrm{n}}\right)\), where Vth,n is the threshold of the n-type TFT. This takes into account the linear dependence of mobility on VGS, as shown in Fig. 2a,b. The equations for the a-ISO and SnO TFTs in the linear regime respectively are:

In the saturation regime, IDS,n and IDS,p equal the maximum value when \(\frac{\partial {I}_{\mathrm{DS}}}{\partial {V}_{\mathrm{DS}}}=0\) (further details in Supplementary Information). Figure 2e–h show the model closely fits the measured data. The logarithmic graphs in Fig. 2e,f show a good match for lower VGS and especially for Imin, which represents the static off-current of the CMOS inverter when Vin = VGS is low (0 V) and high (VDD) for the n- and p-type devices, respectively. Figure 2g,h demonstrate a good fit on a linear scale at higher VGS. We created a MATLAB model of an inverter in which the n-type a-ISO TFT functions as the pull-down network with a range of different loads. The model simulates the VTC and CTC based on the intersection points of the output characteristics. Figure 3 shows the simulation results of four different configurations.

Output characteristics of ISO TFT (W/L)n = 20 (blue) with (a) 6MΩ resistor, (b) SnO (W/L)p = 100, (c) SnO (W/L)p = 20, (d) perfectly matched p-type TFT. (e–h) Corresponding inverter voltage transfer characteristics, MEC noise margins are represented by the largest square between the transfer curves. (i–l) Inverter current transfer characteristics.

The configuration in Fig. 3a,e,i contains a 6 MΩ load and is similar to unipolar resistive inverters currently used in several flexible processors12,13,14. The VTC show a limited output swing since Vout > 0.5 V. The Maximum Equal Criteria (MEC) noise margin (NM) is 26% of the maximum value of VDD/2 for VDD = 5 V. The output swing and NMs decline drastically as VDD is reduced to 3 V and 1 V. The CTC shows the static current at Vin = 0 V (Istat,0) is negligible (Istat,0 = Imin,n = 300 pA). The resistor current increases, reaching its peak (Ipeak) when Vin = VDD. Therefore, the static current at Vin = VDD (Istat,1) is 400 nA and 750 nA for VDD = 3 V and VDD = 5 V respectively, which is > 1000-fold greater than Istat,0.

In Fig. 3d,h,l the resistor is replaced with a theoretically ideal p-type TFT with the same output characteristics as the n-type a-ISO TFT to form a complementary inverter. This represents an ideal setup for comparison as metal-oxide p-type TFTs with this performance do not currently exist. The CMOS inverter characteristics are excellent; even at VDD = 1 V it achieves a rail-to-rail swing and NM = 46%. Most importantly the p-type TFT turns off when Vin = VDD, meaning Istat,1 = Imin,p = 400 pA. Ipeak is still ~ 750 nA when Vin = VDD/2 but both of the static currents are only 400 pA, reducing Pstat by > 1000-fold. This advantage of CMOS operation is essential for high-density circuits.

VTCs, NMs and gain are widely reported for inverters but provide little information about switching speed and (static) power consumption (i.e. from this information alone it is impossible to tell whether an inverter is an ‘efficient’ CMOS inverter or a resistive load inverter). Here we define a dimensionless inverter efficiency, Ip/Istat, as the average switching current divided by the sum of the static currents, (Istat = Istat,0 + Istat,1). The average switching current, Ip, is defined such that it scales with the switching frequency (f). f scales with the inverse of the overall propagation delay (tp), where tp equals the sum of the high-to-low (tpHL) and low-to-high (tpLH) transitions. For constant VDD, the time taken to discharge and charge a constant load capacitance (CL) scales with the inverse of the maximum discharge (Imax,HL) and charge current (Imax,LH) respectively (see Eq. (3) and Fig. S1). Therefore, f scales with Imax,HLImax,LH/(Imax,HL + Imax,LH) which we define as Ip.

Note in reality the shape of Imax,HL and Imax,LH (as a function of the voltage across CL) also affects tpHL and tpLH but we ignore this as a second order effect. This leads to the dimensionless definition for the inverter efficiency in Eq. (4). This is an excellent performance parameter as it leverages switching speed over static power and provides a way to quantify this.

For the basic n-type unipolar resistive load inverter Imax,HL = Imax,n, Istat,0 = Imin,n, and Imax,LH = Istat,1 = Imax,R where Imax,R is the peak current through the resistor. This results in an upper bound of Ip/Istat < 1 (Eq. (5)) since Imin,n is generally negligible compared to Imax,R and represents a ‘worst-case scenario’. For the inverter in Fig. 3a,e,i Ip/Istat = 0.86.

For the CMOS inverter, Imax,HL = Imax,n, Imax,LH = Imax,p, Istat,0 = Imin,n and Istat,1 = Imin,p. This results in the inverter efficiency in Eq. (6). Ip/Istat for the perfectly matched CMOS is given in Eq. (7) using Imax,n = Imax,p = Imax and Imin,n = Imin,p = Imin.

For the perfectly matched inverter in Fig. 3d,h,l, Ip = 0.5Imax,n = 2.7 µA, Istat = 2Imin,n = 800 pA, Ip/Istat = 3300 (at VDD = 5 V). The performance of the SnO TFTs is inferior to that of the a-ISO TFTs and therefore Ip/Istat should be somewhere between 1 and 3300 for an a-ISO/SnO CMOS inverter.

In Fig. 3b,f,j the resistor has been replaced with the p-type SnO TFT with (W/L)p = 100 to form a complementary inverter with (W/L)p/(W/L)n = 5. Increasing (W/L)p/(W/L)n is common practice19,20,27 to compensate for the lower mobility of the p-type TFT. In this case, the output currents are matched at VGS = 5 V but the mismatch at VGS = 0 V,1 V is increased, as shown in Fig. 3b. The VTCs show the NMs nearly double (compared to the unipolar case) and at VDD = 5 V a rail-to-rail voltage swing is achieved. Istat,1 = Imin,p is reduced to 200 nA and Ip increases to 3.0 µA. At VDD = 5 V, this inverter switches four times as fast and Istat is reduced by ~ 3.5, resulting in Ip/Istat = 15. Therefore, this inverter is 15 times more ‘efficient’ than the unipolar resistive inverter (note this is an underestimate as a TFT generally discharges the load capacitance quicker than a resistor). At VDD = 3 V, Ip is only 810 nA and Ip/Istat = 4. For VDD = 1 V, Vout = ~ 0.7 V at Vin = 1 V and no inversion is possible; the gain is < 1 resulting in sub-zero NMs.

In Fig. 3c,g,k the inverter is modelled using the p-type SnO TFT with (W/L)p = 20 ((W/L)p/(W/L)n = 1). The output currents are no longer matched at VGS = 5 V but the match improves at lower VGS (Fig. 3c). Figure 3g shows improved performance at lower voltages resulting in rail-to-rail swing and a NM = 44% when VDD = 3 V. At VDD = 1 V, the gain is just above unity with a small NM = 4% but Vout > 0.3 V. Interestingly, the NM at VDD = 5 V also improves, despite a larger mismatch at VGS = 5 V. Crucially, this shows that matching Imin,n and Imin,p at the expense of mismatching Imax,n and Imax,p improves the NMs over a wide range of VDD. Moreover, Istat,1 = Imin,p is reduced from 200 to 40 nA. Ip is reduced to 1.1 µA (VDD = 5 V) and 350 nA (VDD = 3 V) causing a longer propagation delay. However, the overall efficiency is higher since Ip/Istat is ~ 26 and ~ 9 for VDD = 5 V and VDD = 3 V respectively. This shows that reducing (W/L)p from 5 to 1 nearly doubles the efficiency, and improves the NMs. Compared to ~ 3300 for the ideally matched case, 26 is relatively low, but is still > 25-fold improvement over the unipolar resistive inverter. Since the power consumption of recent flexible microprocessors employing resistive load technology is > 99% static14, a 25-fold reduction in Pstat could potentially result in a 25-fold increase in the number of gates. An additional advantage is that (W/L)p/(W/L)n = 1 reduces the area occupied by the CMOS inverter, as well as parasitic capacitance. Whether these advantages outweigh the complexity of adding the p-type (n-type) material varies for different applications. Note that Si processors operate at higher frequencies since the mobility of crystalline Si is > 100 times higher than for metal-oxides and organics. Combined with the low off-current of Si transistors (resulting in a high Ip/Istat), this means Pstat of Si CMOS gates is usually negligible compared to the dynamic power (Pdyn) as defined in Eq. (8). Further note that Pdyn scales with f (and therefore Ip) which makes it impossible to optimise Ip/Idyn in Eq. (9) (for constant VDD, CL and assuming the input rise time, ts, is negligible). For this reason the inverter efficiency is defined as Ip/Istat. The type of application also matters, for example in a microprocessor the average number of gates that switch at any time is a relatively low percentage (x in Eq. (9)) of the total number of gates which reduces Pdyn. In less complex systems, a higher proportion of gates might be switching and x will be larger.

All-oxide CMOS inverter performance

The modelling results were verified experimentally by connecting SnO and a-ISO TFTs to form two all-metal-oxide CMOS inverters with different (W/L)p/(W/L)n. The first inverter consists of the a-ISO TFT with (W/L)n = 20 and the SnO TFT with (W/L)p = 100. In the second configuration the SnO TFT with (W/L)p = 20 is used. The measured VTCs and CTCs are represented by the dotted lines in Fig. 4a,b,c,d. The difference between the forward and backward sweeps is caused by the hysteresis of the SnO TFT (Fig. 2b,c).

Measured and modelled (solid line) voltage transfer characteristics for the a-ISO + SnO inverters (a,b) and current transfer characteristics (c,d). Peak, static currents and the ratio between them for VDD = [0,5 V] of different inverter configurations (e) unipolar resistive, CNT ambipolar28, IGZO zero-VGS29, (f) CMOS a-ISO + SnO (W/L)p/(W/L)n = 100/20, (g) CMOS a-ISO + SnO (W/L)p/(W/L)n = 20/20, (h) CMOS ISO perfectly matched, (i) CMOS IGZO + SnO22, (j) CMOS IGZO + SnO30.

Figure 4a–d show the model fits the measured data well for both configurations across a range of VDD. It should be noted that a correction was applied to account for a reduction in measured Imax,p and Imin,p, caused by hysteresis from sweeping VGS = Vin. For (W/L)p = 20 and VDD = 1 V, the measured device achieves rail-to-rail swing and outperforms the model due to the reduced Imin,p. The Supplementary Information provides details on the modelling and hysteresis effects.

Figure 4f–h shows Ip, Istat and Ip/Istat of the two measured devices and perfectly matched inverter for VDD = [0, 5 V]. By changing (W/L)p from 100 to 20, Istat is reduced by a factor 5 while Ip is only reduced by 3; Ip/Istat therefore improves by 60%. This confirms that reducing (W/L)p increases Ip/Istat compared to simply scaling up (W/L)p inversely with mobility as long as (i) Imin,p scales with (W/L)p and (ii) Imin,p is considerably larger than Imin,n.

Figure 4h shows Ip/Istat for the perfectly matched CMOS inverter reaches ~ 3300 for VDD = 5 V due to the low Istat. For CMOS devices, Ip scales with VDD while Istat remains approximately constant. Therefore, Ip/Istat increases and the inverter becomes more ‘efficient’ at higher VDD. This key advantage of CMOS over other inverters is quantitively captured by Ip/Istat.

Figure 4e shows Ip/Istat is ~ 1 for the (6 MΩ) unipolar resistive inverter since Istat = ~ Ip as VDD increases. Two other inverter configurations that commonly employ TFTs are shown; an ambipolar inverter28 and zero-VGS metal-oxide inverter29. Both these devices achieve ultralow power consumption (< 1 nW) but their use is limited since Ip/Istat = 1. The ambipolar inverter operates down to 0.5 V where Istat = 100 pA but since Ip = Istat the operating frequency is ~ 10 Hz, limiting the range of applications. The device can operate at higher voltages but Istat increases with Ip, as for the unipolar resistive inverter. In this case, the complementary configuration improves the VTCs and NMs but not Ip/Istat. The zero-VGS inverter combines two Schottky-barrier IGZO TFTs. The pull-up TFT operates in saturation with VGS = 0 V resulting in an ultralow operating current of ~ 100 pA for VDD = 2 V. This is similar to operating with a large resistive load (Ip/Istat = ~ 1) and the switching frequency is once again limited to ~ 10 Hz. Both the ambipolar and zero-VGS configurations are suitable for ultralow-power, low-frequency applications but not for flexible processors where a high Ip/Istat is required for operation > 1 kHz and low Pstat.

In Fig. 4i,j the Ip/Istat of two state-of-the-art all-oxide CMOS inverters have been calculated and plotted for comparison22,30. The SnO TFTs reported in these works have an Ion/Ioff of ~ 105 and SS of ~ 1 V/dec, which are superior to our SnO TFTs (likely due to thin high-quality Al2O3 dielectric layers). As expected, Ip/Istat of these inverters is considerably higher but for both devices (W/L)p/(W/L)n has been scaled up using the silicon CMOS approach (to 5 and 3 respectively) to simply compensate for the mobility difference. In the next section, we explain how Ip/Istat for these inverters can be improved by scaling (W/L)p/(W/L)n optimally.

Optimal geometric aspect ratio

In this work we have shown that reducing (W/L)p/(W/L)n can increase Ip/Istat compared to simply scaling up W/L inversely with mobility, while reducing the area. This raises the question whether an optimal (W/L)p/(W/L)n exists, which maximises these parameters. Ideally the maximum (VGS = ± VDD) and minimum (VGS = 0 V) drain currents of the n-type TFTs, Imax,n and Imin,n, equal the ones of the p-type TFTs, Imax,p and Imin,p. For silicon transistors with full channel depletion Imin,p and Imin,n are usually similar and independent of (W/L). This means the lower hole mobility is compensated by scaling (W/L)p up until ((W/L)pImax,p) matches Imax,n (Fig. 1b,g). As long as Vth,p and Vth,n are well matched, and the oxide capacitance is uniform, an excellent match of the output characteristics is achieved. As explained previously, this does not work for metal-oxide TFTs since the p-type (SnO) TFT has a high Imin,p and low Imax,p compared to the n-type (a-ISO) TFT as illustrated in Fig. 1i. Scaling up (W/L)p brings (W/L)pImax,p closer to Imax,n but increases the gap between (W/L)pImin,p and Imin,n. Here we propose the optimal (W/L)p can be found by setting the ratios Imax,n/(W/L)pImax,p and (W/L)pImin,p/Imin,n equal (assuming Imax,p and Imin,p correspond to (W/L)p = 1). As such, a compromise is made between matching minimum and maximum output currents. The optimal (W/L)p can be found by solving:

This value is dependent on VDD since the output characteristics vary with VDS. For silicon transistors Imin,p no longer scales with (W/L)p and equals ~ Imin,n; therefore (W/L)pImin,p/Imin,n can be set to ~ 1. This results in an optimal (W/L)p equal to Imax,n/Imax,p = μsat,n/μsat,p as expected:

For TFTs where Imin,p (or Imin,n for organics) scales with (W/L)p ((W/L)n), corresponding to the scenarios in Fig. 1c,d,e,h, the following are applicable:

When calculating the optimal (W/L), it should be noted that Imin,p and Imax,p in Eq. (12) are the normalised values corresponding to (W/L)p = 1 (similarly Imin,n and Imax,n in Eq. (13) correspond to (W/L)n = 1). By taking the derivative of Ip/Istat w.r.t. (W/L)p and setting this equal to zero, we show that the expression in Eq. (12) indeed maximises Ip/Istat (for (W/L)p > 0). The expression for Ip/Istat for a CMOS inverter where both Imin,p and Imax,p scale with (W/L)p is given in Eq. (14). Equation (15) shows that the optimal (W/L)p from Eq. (12) sets the top part of the derivative of Ip/Istat with respect to (W/L)p equal to zero. In the Supplementary Information a plot of Ip/Istat versus (W/L)p is included for the inverters in this work (Fig. S4).

It is suggested to calculate the optimal (W/L)p ((W/L)n) for the maximum required VDD. If Imin,n (Imin,p) is much smaller than other currents in the system, (i.e. for IGZO TFTs Imin,n can be ~ 1fA) it is advised to set Imin,n (Imin,p) equal to the lowest critical current. This method can also be applied to maximise Ip/Istat for Si CMOS inverters. However, the low Istat means the effect on the overall power consumption will be negligible and it makes more sense to scale (W/L)p to maximise NMs.

For the a-ISO-SnO inverter with (W/L)n = 20, the optimal (W/L)p were calculated as 4 and 5 at VDD = 5 V and VDD = 10 V respectively. Using the model, Ip/Istat and the NMs were estimated for different (W/L)p. Figure 5a shows reducing (W/L)p from 100 to 5, nearly doubles Ip/Istat for VDD = 5 V and improves it by over 60% for VDD = 10 V. However, reducing (W/L)p any further from 5 to 0.5 leads to a decrease in Ip/Istat and 5 is therefore the optimal value. Increasing (W/L)p from 5 to 20 reduces Ip/Istat by only 10%. The perfectly matched and resistive load cases are shown for comparison. It also includes the scenario where Vth,p is reduced by 1 V to 1.3 V resulting in a considerable reduction in Imin,p and therefore increase in Ip/Istat. This shows changing (W/L)p makes a noticeable difference but combining it with an optimal Vth,p can have significantly greater impact (note the optimal (W/L)p is 10 in this case). The Vth of oxide TFTs is difficult to control as there is no appropriate doping process. It can be improved by reducing the dielectric thickness (and using a high k dielectric), and removing defects between the dielectric and semiconductor interface (i.e. by annealing, interface layers, choice of materials and processing conditions).

NMs are equally important and modelled as a function of (W/L)p (Fig. 5b) which confirms that reducing (W/L)p from 100 to 20 increase the NMs for VDD < 8 V. For (W/L)p = 5 the NMs improve for VDD < 3 V but a further reduction to (W/L)p = 0.5 lowers them for all VDD. NMs for the perfectly matched and resistive load are included for reference.

To take into account both Ip/Istat and the NMs, a new dimensionless parameter is introduced, (Ip/Istat)*NM/(VDD/2), and plotted in Fig. 5c. This shows that for VDD < 5 V the performance of (W/L)p = 5 and (W/L)p = 20 is very close (and nearly double that of (W/L)p = 0.5 and (W/L)p = 100). For VDD > 5 V, (W/L)p = 20 outperforms (W/L)p = 5 as the NM increases more than Ip/Istat. This shows that (W/L)p = 5 represents a lower bound which maximises Ip/Istat but that it might be worth increasing (W/L)p to above this value to increase NMs further. Alternatively a larger (W/L)p might be required to achieve higher switching frequency. In this case we suggest to increase (W/L)n first (and therefore Imax,n) and find the corresponding optimal (W/L)p. For example, the inverter with (W/L)p/(W/L)n = 60/60 achieves the same average switching current (Ip) as (W/L)p/(W/L)n = 100/20 while the sum of the static currents is only half (improving Ip/Istat by a factor two with the same total area at VDD = 5 V).

Table 1 shows the actual and suggested optimal (W/L)p/(W/L)n, corresponding output currents, and Ip/Istat. For the inverter in Fig. 4i22, Ip/Istat can almost be tripled by choosing the optimal (W/L)p/(W/L)n, while reducing the total area. This represents a straightforward method to geometrically optimise the inverter performance, provided the maximum and minimum output currents of the n- and p-type TFTs are measured (or modelled). Calculating NMs is more difficult but can be obtained by adjusting the modelling parameters in Eqs. (1) and (2). Ip/Istat for the inverter in Fig. 4j30 is close to the optimal value and therefore the gains are limited. Optimisation based on NMs and switching speed is likely to be more important in this case. For the SnO-ZnO CMOS inverter27 Ip/Istat is only 1.8. This inverter has excellent NMs (> 60%), but Ip/Istat shows that the inverter efficiency is only marginally better than the unipolar resistive inverter. The last row contains an estimate for the optimal (W/L)p/(W/L)n for an organic complementary inverter11 for which the p-type TFT outperforms the n-type. However, note that for this inverter Ip/Istat is already > 1000, meaning it is unlikely that Pstat is the dominant factor.

Conclusions (and outlook for all-oxide CMOS inverters)

We have proposed an optimal (W/L)p/(W/L)n that maximises Ip/Istat and can be applied universally to silicon, metal-oxide and organic complementary inverters. Notably, our results show that reducing W/L of metal-oxide p-type TFTs increases Ip/Istat while reducing the area compared to simply scaling up W/L inversely with mobility. A high inverter efficiency is critical to reduce Pstat and increase the gate density of (flexible) processors; we have shown that Ip/Istat of state-of-the-art all-oxide CMOS inverters can be maximised by adopting the optimal (W/L)p/(W/L)n. In this way n- and p-type TFTs with significant differences in performance can be matched optimally without changing the intrinsic properties such as Vth, SS, Ion/Ioff and mobility.

Despite the clear need for all-oxide CMOS inverters required for low-cost flexible electronics, only a handful have been reported. For ambipolar, unipolar resistive and zero-VGS configurations Ip/Istat = 1; they simply cannot provide the necessary reduction in Istat without sacrificing switching speed. The high Ioff of SnO TFTs remains a bottleneck, but has reached a sufficiently low level to reduce Istat by at least 100-fold over unipolar logic for VDD ~ 3–5 V. While this might seem small compared to a ratio of ~ 3300 for a perfectly matched CMOS inverter, it makes a significant difference for natively flexible microprocessors. The recently reported microprocessor containing 18,334 NAND2 gates with unipolar n-type resistive load logic operates at a maximum clock-frequency of 29 kHz14. The power consumption is ~ 21 mW, of which > 99% is static. Based on these figures and VDD = 3 V, we estimate Ip = Istat,1 for each gate to be ~ 750 nA which is close to Ip values reported in this work and recent literature. This shows that replacing the resistive load with a state-of-the-art SnO TFT, combined with the correct W/L ratio, could reduce Istat by a factor > 200 at VDD = 3 V (constant Ip). Since Pstat is the dominant factor, this reduces total power by nearly 200-fold, potentially increasing the number of gates on the chip to over a million, approaching VLSI standards. This shows that while the performance of current SnO TFTs is still significantly behind their n-type counterpart, they are already able to reduce Pstat to such a level that it is no longer the dominant component. A further reduction of Ioff is welcome but will not affect the overall power consumption significantly as the dynamic power will start to dominate. To realise a flexible microprocessor employing all-oxide CMOS technology it is critical to improve the stability (hysteresis) and repeatability of SnO TFTs.

Methods

Device fabrication

The CMOS inverters are formed by interconnecting a bottom-gate staggered n-type a-ISO TFT to a bottom-gate staggered p-type SnO TFT. The schematic structure of each TFT is shown in Fig. 2d,i. The substrate of the n-type TFT is glass on which a 100 nm Cr bottom electrode layer is deposited using a Metallifier Sputter Coating System (Precision Atomics). The gate electrode was patterned using Cr etchant. On top of this a 180 nm Al2O3 dielectric layer (47 nF/cm2) was deposited at 150 °C by atomic layer deposition (MVSystems). After this the 10 nm ISO (10 wt% Si) channel layer was deposited by rf-sputtering (MVSystems) at an oxygen-to-argon flow ratio of 16.7%, rf power of 150 W, and deposition pressure of 4 mTorr. The top layer is a 100 nm Mo deposited by the Metallifier Sputter Coating System to form source/drain (S/D) electrodes. Patterning of this layer was done by reactive ion etching (Philips RIE) at a power of 100 W and pressure of 150 mTorr. All layers were patterned with AZ5214E photoresist. The a-ISO devices were annealed for two hours in ambient air at 200 °C to improve the performance. The W/L ratio of the devices was 20 with a constant channel length of 20 μm.

For the p-type TFTs, 10 nm SnO layers were formed on thermally-grown SiO2 on a p+-Si substrate by ALD (Beneq TFS-200) at 170 °C using a tin(II) amide precursor. The p+-Si and SiO2 (∼ 200 nm) were used as a common gate electrode and a gate insulator (12 nF/cm2), respectively. A 100 nm Au layer was deposited as S/D electrodes using a thermal evaporator (Edwards E306A). Finally, a 70 nm passivation layer of Al2O3 was deposited. The devices were annealed for two hours at 200 °C in ambient air. The active layers and S/D electrodes were patterned by a lift-off process using AZ5214E photoresist. The W/L ratio varied from 20 to 100 with a constant channel width of 1000 μm.

The maximum fabrication temperature of the above processes is 200 °C resulting in low fabrication costs and the ability to deposit on flexible substrates such as DuPont Kapton HN sheet. A further reduction in annealing temperature to 170 °C should be possible by increasing the annealing time. Note a p+-Si substrate with SiO2 was used for the p-type device for ease of manufacturing but in the future this could easily be replaced by a glass or flexible substrate with oxide dielectric.

Device characterisation

The electrical performance of the TFTs and the inverters were analysed using a Keithley 4200 semiconductor characterisation system. A six probe configuration was used to interconnect the gate electrodes of different n- and p-type TFTs and feed in a common input voltage. Similarly the drain electrodes were interconnected to measure the output voltage. This setup allows to connect p-type TFTs with different W/L ratios to the same n-type TFT and isolate the effects of changing (W/L)p/(W/L)n.

Data availability

The datasets generated during and/or analysed during the current study are available in the Cambridge University Data Repository (http://www.repository.cam.ac.uk/).

References

Nathan, A. et al. Flexible electronics: The next ubiquitous platform. Proc. IEEE 100, 1486–1517. https://doi.org/10.1109/JPROC.2012.2190168 (2012).

Xu, K., Lu, Y. & Takei, K. Multifunctional skin-inspired flexible sensor systems for wearable electronics. Adv. Mater. Technol. 4(3), 1–25. https://doi.org/10.1002/admt.201800628 (2019).

Myny, K. et al. 30.1 8b thin-film microprocessor using a hybrid oxide- organic complementary technology with inkjet- printed P 2 ROM memory. IEEE Int. Solid-State Circuits Conf. 486–488 (2014).

Chang, J. et al. Flexible and stable high-energy lithium-sulfur full batteries with only 100% oversized lithium. Nat. Commun. 9(1), 1–11. https://doi.org/10.1038/s41467-018-06879-7 (2018).

Jeong, C. K. et al. Self-powered fully-flexible light-emitting system enabled by flexible energy harvester. Energy Environ. Sci. 7(12), 4035–4043. https://doi.org/10.1039/c4ee02435d (2014).

Myny, K. et al. 15.2 A flexible ISO14443-A compliant 7.5mW 128b metal-oxide NFC barcode tag with direct clock division circuit from 13.56MHz carrier. IEEE Int. Solid-State Circuits Conf. 262–264 (2017).

Karaki, N., Nanmoto, T., Ebihara, H., Utsunomiya, S., Inoue, S. and Shimoda, T. 14.9 A Flexible 8b asynchronous microprocessor based on low-temperature poly-silicon TFT technology. IEEE Int. Solid-State Circuits Conf. 272–274(2005).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1(1), 30–39. https://doi.org/10.1038/s41928-017-0008-6 (2018).

Zschieschang, U., Bader, V. P. & Klauk, H. Below-one-volt organic thin-film transistors with large on/off current ratios. Org. Electron. 49, 179–186. https://doi.org/10.1016/j.orgel.2017.06.045 (2017).

Zschieschang, U. et al. Mixed self-assembled monolayer gate dielectrics for continuous threshold voltage control in organic transistors and circuits. Adv. Mater. 22(40), 4489–4493. https://doi.org/10.1002/adma.201001502 (2010).

Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445(7129), 745–748. https://doi.org/10.1038/nature05533 (2007).

Ozer, E. et al. A hardwired machine learning processing engine fabricated with submicron metal-oxide thin-film transistors on a flexible substrate. Nat. Electron. 3, 419–425. https://doi.org/10.1038/s41928-020-0437-5 (2020).

Ozer, E. et al. Binary neural network as a flexible integrated circuit for odour classification. FLEPS 2020—IEEE Int. Conf. Flex. Printable Sensors Syst. 0–3, https://doi.org/10.1109/FLEPS49123.2020.9239529.

Biggs, J. et al. A natively flexible 32-bit arm microprocessor. Nature 595(7886), 532–536. https://doi.org/10.1038/s41586-021-03625-w (2021).

Celiker, H., Sou, A., Cobb, B., Dehaene, W. & Myny, K. Flex6502: A flexible 8b microprocessor in 0.8µm metal-oxide thin-film transistor technology implemented with a complete digital design flow running complex assembly code Hikmet. 2022 IEEE Int. Solid-State Circuits Conf. 65, 272–274 (2022).

Robinson, A. L. CMOS future for microelectronic circuits: Low power consumption of complementary metal-oxide-semiconductor integrated circuits drives next stage of ultraminiaturization. Science 224(4650), 705–707. https://doi.org/10.1126/science.224.4650.705 (1984).

Han, S. & Flewitt, A. J. The Origin of the high off-state current in p-type Cu2O thin Film transistors. IEEE Electron Device Lett. 38(10), 1394–1397. https://doi.org/10.1109/LED.2017.2748064 (2017).

Han, S., Niang, K. M., Rughoobur, G. & Flewitt, A. J. Effects of post-deposition vacuum annealing on film characteristics of p-type Cu2O and its impact on thin film transistor characteristics. Appl. Phys. Lett. 109(17), 173502. https://doi.org/10.1063/1.4965848 (2016).

Wang, Z., Nayak, P. K., Caraveo-Frescas, J. A. & Alshareef, H. N. Recent developments in p-type oxide semiconductor materials and devices. Adv. Mater. 28(20), 3831–3892. https://doi.org/10.1002/adma.201503080 (2016).

Li, Y. et al. Complementary integrated circuits based on p-type SnO and n-type IGZO thin-film transistors. IEEE Electron Device Lett. 39(2), 208–211 (2018).

Bhavnagarwala, A. J., Austin, B. L., Bowman, K. A., Meindl, J. D. & Fellow, L. A minimum total power methodology for projecting limits on CMOS GSI. IEEE Trans. VLSI Syst. 8(3), 235–251ss (2000).

Li, Y. et al. Complementary integrated circuits based on n-type and p-type oxide semiconductors for applications beyond flat-panel displays. IEEE Trans. Electron Devices 66(2), 950–956. https://doi.org/10.1109/TED.2018.2887270 (2019).

Yang, J. et al. Highly optimized complementary inverters based on p-SnO and n-InGaZnO with high uniformity. IEEE Electron Device Lett. 39(4), 516–519. https://doi.org/10.1109/LED.2018.2809796 (2018).

Liang, L. Y. et al. Ambipolar inverters using SnO thin-film transistors with balanced electron and hole mobilities. Appl. Phys. Lett. 100(26), 263502. https://doi.org/10.1063/1.4731271 (2013).

Napari, M. et al. Role of ALD al2o3surface passivation on the performance of p-type Cu2O thin film transistors. ACS Appl. Mater. Interfaces 13(3), 4156–4164. https://doi.org/10.1021/acsami.0c18915 (2021).

Jang, Y. et al. Reduction of the hysteresis voltage in atomic-layer-deposited p-type SnO thin-film transistors by adopting an Al2O3 interfacial layer. Adv. Electron. Mater. 5(7), 1900371. https://doi.org/10.1002/aelm.201900371 (2019).

Chiu, I., Li, Y., Tu, M.-S. & Cheng, I.-C. Complementary Oxide—semiconductor-based circuits with n-channel Zno and p-channel. IEEE Electron Device Lett. 35(12), 1263–126 (2014).

Zhao, J. et al. Ambipolar deep-subthreshold printed-carbon-nanotube transistors for ultralow-voltage and ultralow-power electronics. ACS Nano 14(10), 14036–14046. https://doi.org/10.1021/acsnano.0c06619 (2020).

Lee, S. & Nathan, A. Subthreshold Schottky-barrier thin-film transistors with ultralow power and high intrinsic gain. Science 354(6310), 302–304. https://doi.org/10.1126/science.aah5035 (2016).

Yuan, Y. et al. Oxide-based complementary inverters with high gain and nanowatt power consumption. IEEE Electron Device Lett. 39(11), 1676–1679. https://doi.org/10.1109/LED.2018.2871053 (2018).

Acknowledgements

This work was supported by the UKRI Engineering and Physical Sciences Research Council through the Centre of Doctoral Training in Integrated Photonic and Electronics Systems (EP/L015455/1) and grant EP/P027032/1. For the purpose of open access, the author has applied a Creative Commons Attribution (CC BY) licence to any Author Accepted Manuscript version arising.

Author information

Authors and Affiliations

Contributions

N.C.A.F. and A.J.F. conceived of and designed the overall experiments. N.C.A.F. and K.M.N. fabricated the devices. J.D.P. and A.L.J. fabricated the SnO thin film. N.C.A.F. characterised and modelled the devices. N.C.A.F., K.M.N. and A.J.F. wrote the main manuscript text. All the authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

van Fraassen, N.C.A., Niang, K.M., Parish, J.D. et al. Optimisation of geometric aspect ratio of thin film transistors for low-cost flexible CMOS inverters and its practical implementation. Sci Rep 12, 16111 (2022). https://doi.org/10.1038/s41598-022-19989-6

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-022-19989-6