Abstract

Silicon nanowires (SiNWs) have emerged as promising candidates for advanced transistor applications due to their exceptional electronic properties, compatibility with standard semiconductor fabrication processes, and scalability toward miniaturized device architectures. In this study, we present a fabrication technique for SiNW-based device using atomic force microscope (AFM) lithography via the local anodic oxidation (LAO) process. To further refine the dimensions of the fabricated SiNWs, a self-limiting oxidation (SLO) process was employed as a post-patterning treatment. This combined approach addresses the limitations of conventional AFM-LAO by enabling dimensional scaling while improving nanowire uniformity and surface quality. The effects of oxidation temperature and the number of SLO cycles were systematically investigated to assess their influence on nanowire morphology and electrical performance. Results demonstrated that the most significant dimensional reduction occurred at 1000 °C after three SLO cycles. Electrical characterization through I–V measurements revealed a reduction in drain-source current (Ids), which corresponds to an increase in channel resistance due to decreased nanowire cross-sectional area. This behaviour is consistent with expected nanoscale device physics, where reduced dimensions enhance surface-to-volume ratio and electrostatic control. These findings underscore the effectiveness of the proposed fabrication strategy for improving the structural and electrical performance of SiNW-based field-effect transistor.

Similar content being viewed by others

Introduction

Silicon plays a crucial role in addressing numerous technological challenges due to its versatility and wide range of applications across various domains. It remains the foundation of modern electronic device fabrication, continually evolving in accordance with Moore’s law, which drives the scaling down of device features and dimensions1,2. Among the various nanoscale structures, silicon nanowires (SiNWs) have attracted substantial interest. These structures are considered one-dimensional (1D) materials with diameters typically below 100 nm3,4, resulting in a significantly high surface-to-volume ratio (SVR)5,6. This characteristic enhances their functionality in electronic components, particularly in sensing applications. In previous studies, SiNWs have been employed as the basis for highly responsive biosensors, including those designed for detecting dengue virus7,8, cardiac biomarkers9,10, and influenza viruses11,12, highlighting their strong potential in biomedical sensing applications.

Within the broader fields of nanoscience and nanotechnology, the precise fabrication of SiNWs with tailored geometries and physical properties plays a significant role, particularly for applications in sensing, electronics, and nanodevices. Considerable advancements have been made in fine-tuning the morphology, dimensions, and material composition of SiNWs across length scales ranging from atomic to macroscopic levels. Generally, the fabrication of SiNWs structures can be divided into two main approaches: top-down and bottom-up methods. Top-down techniques involve the removal of material to define nanostructures, often through etching or lithographic processes, whereas bottom-up approaches assemble nanostructures atom by atom or molecule by molecule. The choice of fabrication route significantly influences the resulting physical and functional characteristics of SiNWs.

Top-down fabrication offers superior control over geometry and alignment with other device structures compared to bottom-up approaches. It is also known as stepwise design that facilitates easier integration into functional systems due to its high yield and predetermined substrate positioning. This fabrication method employs a variety of lithographical techniques to create nanoscale patterns from bulk materials. Common conventional top-down nanofabrication techniques include electron beam lithography13,14,15, photolithography16,17, and focused ion beam lithography18. However, these methods are often considered less favourable because they have high operating costs, complicated multi-step processes, and accessibility issues. Consequently, new unconventional techniques for nanoscale patterning have been introduced, including atomic force microscopy (AFM) lithography and nano-imprint lithography. AFM lithography, in particular, proves to be a valuable technique for fabricating and characterizing microarray, nanoscale structures, sensors, and devices.

AFM-based local anodic oxidation (AFM-LAO) is a maskless, resist-free technique that allows direct patterning of oxide structures on a silicon substrate using a biased AFM tip in a humid environment. However, despite its flexibility and nanoscale resolution, AFM-LAO often produces nanowire structures with edge roughness, dimensional non-uniformity, and limited reproducibility across array. While AFM-LAO has been previously reported as a patterning method19, its output is often limited by edge roughness, dimensional non-uniformity, and low reproducibility due to factors like unstable meniscus formation and tip variability. To address these issues, this study integrates AFM-LAO with a self-limiting oxidation (SLO) process. The SLO method enables high-temperature thermal oxidation that refines nanowire dimensions, smooths sidewalls, and improves array uniformity outcomes critical for functional SiNW-field effect transistors (FET) applications.

The AFM lithography process produced SiNW-FET through LAO. This technique allows oxide to grow on the substrate and function as the anode. Anodic oxidation initiates at a specific threshold voltage. A biased AFM tip operates under humid conditions to oxidize the substrate surface locally during the LAO process. The tip creates a voltage field across the small gap between itself and the substrate. The negative bias of the tip dissociates the water menisci that form a bridge in this gap. As a result, the oxidation reaction that produces silicon dioxide on the silicon surface occurs between the silicon substrate (anode), AFM tip (cathode), and water (electrolyte). The oxidation occurs only in a limited region at the cantilever tip, which allows for control over the silicon dioxide pattern.

This paper presents the fabrication of a SiNW-FET array using AFM lithography in contact mode. The fabrication process utilized the optimized parameters of writing speed, applied voltage, and relative humidity. The SLO process was applied to the fabricated SiNWs to further reduce their dimensions. The device architecture adopts a back-gate configuration, where the silicon handle layer of the SOI substrate, separated from the nanowire channel by a 200 nm buried oxide (BOX) layer, can be capacitively coupled to an external gate electrode during operation. This design ensures that, while the present work focuses on baseline two-terminal performance, the fabricated devices remain fully compatible with future gated measurements and biosensing functionalization. In this study, the effects of oxidation temperature and the number of SLO cycles were systematically investigated to understand their influence on nanowire morphology and electrical performance. The AFM was used to characterize the physical properties, while a semiconductor parameter analyser (SPA) was employed for electrical measurements.

Experimental procedure

In this study, a p-type silicon-on-insulator (SOI) substrate with a (100) crystallographic orientation, supplied by SOITEC, was utilized. The structure of the SOI wafer comprised three distinct layers: a 100 nm top silicon layer, a 200 nm BOX layer, and a bottom silicon handle layer measuring 625 µm in thickness. The overall fabrication procedure was categorized into four main stages: substrate cleaning, AFM-based local anodic oxidation, wet etching, and the self-limiting oxidation process. Initially, the SOI wafer was cut into approximately 1 cm × 1 cm sections and subjected to a cleaning process using the standard RCA protocol to remove organic residues and trace metallic impurities from the surface. Following this, SiNWs were patterned using AFM lithography through the LAO method, operated in contact mode. The oxide structures were generated using a vector scanning function in the NanoNavi SPM Control Software (Version 5.02A1) integrated with the scanning probe microscope (SPM) system (SPI3800N/4000: SII Nanotechnology Inc.). A Cr/Pt-coated conductive AFM tip, characterized by a resonant frequency of 13 kHz and a force constant of 0.2 N/m, was employed for the patterning process. During fabrication, nanostructured array was written on the SOI substrate with an applied bias of 9 V and a scanning speed of 0.3 µm/s. The entire procedure was conducted under controlled ambient conditions, maintaining relative humidity between 55 and 65%, and a room temperature ranging from 24 to 26 °C.

The next step involved the selective etching of the silicon layer using a chemical solution consisting of 25 wt% tetramethylammonium hydroxide (TMAH), enhanced with 10 vol% isopropyl alcohol (IPA) and 0.25 vol% Triton X-100. This mixture, referred to as TMAH + Triton X-100, was preheated to 70 °C and continuously stirred at 600 rpm to ensure uniformity. The etching was guided by the oxide mask patterns created during the previous step, enabling precise structuring of the silicon layer. Samples were immersed in the heated solution for 30 s, during which the exposed silicon (not protected by the oxide) was etched away, leaving behind only the silicon regions shielded by the oxide layer. The underlying BOX in the SOI substrate acted as an effective etch stop, preventing over-etching during the process. Following silicon etching, the residual oxide mask was removed by immersing the sample in a 2% hydrofluoric acid (HF) solution for 5 s at room temperature. This step ensured the complete exposure of the silicon nanowire structures for subsequent processing.

To enable further dimensional reduction of the fabricated sub-micron SiNW-FET array, the SLO treatment was applied. This scaling step was essential for refining the lateral dimensions of the nanowires to achieved significant dimensional reduction. The SLO process was conducted at a high temperature of 1000 °C, with a soaking duration of 7 h and an oxygen gas flow rate maintained at 100 cc/min. A total of three SLO cycles were carried out to achieve the desired dimensional reduction. In this study, the oxygen flow rate and oxidation duration were fixed to allow a systematic investigation of oxidation temperature and cycle number effects. Further optimization of these parameters is ongoing and will be reported in future publications, to ensure a more comprehensive understanding without diverting from the current study’s focus on thermal effects. These complementary data will be presented in a separate publication to allow for a more detailed treatment of process optimization without diverging from the main objective of this work. An overview of the complete SiNW-FET fabrication sequence is depicted in Fig. 1.

For electrical characterization of the fabricated SiNW-FET array, current–voltage (I–V) measurements were conducted using a KEITHLEY 4200A-SCS semiconductor parameter analyser (SPA) integrated with a precision probe station. A pair of 0.5 µm radius gold-coated probes was used to make contact with the source and drain electrodes. All measurements were carried out at room temperature under ambient conditions. The SPA system was connected to a control computer, allowing real-time configuration of test parameters and acquisition of I–V data. The drain-source voltage (Vds) was swept from 0 to 1 V, while the gate-source voltage (Vgs) was held constant at 0.1 V throughout the test. The resulting I–V characteristics were used to assess the baseline electrical behaviour and performance of the fabricated SiNW-FET device. During measurements, the device was placed on a gold-coated probe station stage, which served as a back-gate electrode. The silicon handle layer of the SOI substrate, separated from the top SiNWs layer by a 200 nm BOX, enabled capacitive coupling through the BOX. This setup permitted the application of gate bias via the gold stage, forming a back-gate field-effect configuration suitable for preliminary transistor characterization.

Results and discussions

Fabrication of SiNW-FET array via AFM-LAO technique

A silicon dioxide structure composed of a five-wire array was formed using the AFM-LAO method. This array of SiNWs was aligned and connected between two neighbouring contact pads, functioning as the source and drain. Etching of the patterned structures was carried out using a 25 wt% TMAH solution, supplemented with 10 vol% isopropyl alcohol (IPA) and 0.25 vol% Triton X-100, at a temperature of 70 °C for 30 s. The incorporation of IPA and Triton X-100 into the etchant was found to significantly enhance the surface quality of the SOI wafer during the silicon removal process20,21,22. Notably, the combination of TMAH, IPA, and Triton X-100 yielded the lowest observed surface roughness, with an RMS value of 0.2068 nm as measured by AFM, confirming a significant improvement in the surface quality of the etched SOI wafer. This RMS value was previously reported in our earlier work23, and is referenced here to support the effectiveness of the etching solution. Achieving such a low surface roughness is critical for the structural and electrical integrity of SiNWs, as surface irregularities can act as scattering centres, introduce charge traps, and degrade carrier mobility24. Moreover, smoother surfaces ensure better reproducibility and consistency in subsequent functionalization steps, which is particularly important for future integration into surface-sensitive electronic devices. The importance of low surface roughness has been previously reported in this context and, therefore, will not be addressed in detail here12.

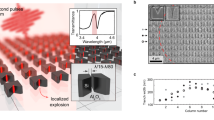

The surface morphology of fabricated SiNW-FET device was characterized using FESEM and AFM contact mode topography, and the results are shown in Fig. 2. Fig. 2a shows the SiNWs pattern before the etching process, while Fig. 2b shows the nanowires after etching with the TMAH-based solution. It can be observed that the lateral dimensions of the nanowires increase after the etching step, which may be attributed to slight isotropic etching beyond the mask boundary, despite the presence of IPA and Triton X-100, which are known to improve anisotropy. This dimensional change is further confirmed in the AFM profile image as shown in Fig. 2f, where the cross-sectional of the lateral dimensions of SiNWs after etching is visibly broader than the initial patterned lines. One drawback of the AFM-LAO technique is that it generates SiNWs with a broad lateral dimension’s variation, ranging from approximately 300–400 nm. Therefore, a scale-down process is an effective way to overcome the variation of lateral dimensions issue in the AFM-LAO technique. The SLO process was further applied to reduce the lateral dimensions of the SiNW array.

Morphological and structural characterization of the fabricated SiNW-FET array: (a) FESEM image of SiNW-FET structure patterned via AFM-LAO before etching, (b) FESEM image after etching, (c) magnified FESEM image of nanowires prior to SLO treatment, (d) corresponding image after three SLO cycles at 1000 °C, indicating dimensional reduction, (e) AFM 3D surface profile of the SiNWs post-SLO showing low surface roughness (Ra = 0.227 nm), (f) AFM top-view and cross-sectional profile of the SiNW array, and (g) schematic diagram of trapezoidal cross-section used for SVR calculation.

Scale-down process of SiNW-FET array via SLO

To improve the dimensional uniformity and scale down the lateral dimensions of SiNW-FET produced via AFM-LAO, the SLO process was introduced as a post-fabrication treatment. This section presents a two-part investigation: first, on the effect of oxidation temperature, and second, on the impact of repeated oxidation cycles.

Influence of oxidation temperature on nanowire reduction

Although it is theoretically possible to fabricate SiNWs at the desired final dimensions using direct lithographic methods, practical limitations in AFM-LAO restrict the minimum achievable lateral dimension due to tip size, meniscus stability, and process variability. Additionally, the subsequent TMAH-based anisotropic etching step often results in lateral undercutting of the oxide mask, leading to unintended broadening of the SiNWs. This effect compromises the final nanowire resolution and uniformity, particularly at sub-500 nm scales. Therefore, a post-fabrication dimensional refinement step is necessary. The SLO technique offers a controlled, uniform, and reproducible method to reduce the lateral dimensions of the nanowires while simultaneously smoothing their sidewalls. This approach not only compensates for the inherent resolution limitations of AFM-LAO but also corrects dimension deviations introduced during etching. As a result, SLO enhances device performance by improving the SVR of the SiNW-FET array.

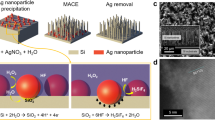

To investigate the effect of oxidation temperature on dimensional reduction, SLO process were carried out at 850 °C, 900 °C, 950 °C, and 1000 °C for 7 h each, under a fixed oxygen flow of 100 cc/min. A maximum oxidation temperature of 1000 °C was selected to avoid potential substrate degradation, stress-induced defects, and thermal incompatibility with standard CMOS processes25,26,27,28. Higher temperatures may compromise device integrity and yield marginal benefits in oxide growth kinetics, thus were not pursued in this study. During this process, the SiNWs were initially oxidized in an oxygen-rich environment. The thermally grown oxide layer was then selectively etched using HF, resulting in a noticeable reduction in lateral dimensions of the nanowire. The transformation during the SLO treatment is illustrated in Fig. 3c, where approximately 54% of the total oxide volume formed externally to the original silicon surface and 46% was consumed from within the nanowire itself29. All oxide layers were subsequently removed during the HF etching stage.

Elemental and chemical characterization of SiNWs before and after the SLO process. (a) EDX spectrum before SLO, (b) EDX spectrum after SLO (c) Schematic illustrating oxidation during SLO, where 46% of the original silicon is consumed and 54% forms oxide, (d) XPS survey spectrum confirming the presence of Si, O, and C elements, (e) High-resolution XPS of Si 2p region and (f) High-resolution XPS of O 1s showing chemical states present on SiNWs post-SLO processing.

To quantify the reduction in lateral dimensions, before-and-after measurements were obtained from FESEM images and analysed using the ImageJ software (Version 1.54f, National Institutes of Health, https://imagej.net/ij/). The oxidized nanowire samples were immersed in HF, which etched the silicon dioxide at a rate of 3 nm/s. Precise control of the HF exposure time was essential to prevent over-etching, which could damage the buried oxide layer and compromise electrical isolation between the device electrodes and the underlying SOI substrate. Additionally, the BOX layer was not exposed during the HF etching step, as it remained protected beneath the top silicon layer throughout the process. The etch was limited to surface-grown oxide from SLO, ensuring the structural and electrical integrity of the BOX layer was preserved. Elemental characterization was performed using energy-dispersive X-ray spectroscopy (EDX) before and after the SLO treatment, as shown in Fig. 3a and b, respectively. The pre-SLO EDX spectra in Fig. 3a showed oxygen and silicon atomic percentages of 40.87% and 59.13%, respectively. After the SLO process, Fig. 3b displayed increased oxygen content, with O and Si atomic percentages of 59.48% and 40.52%, respectively, confirming successful oxidation of the SiNWs array.

To further confirm the oxide formation and analyse the chemical bonding states, X-ray photoelectron spectroscopy (XPS) analysis was carried out. The wide-scan XPS spectrum in Fig. 3d showed high-resolution peaks corresponding to O 1s, C 1s, and Si 2p at binding energies of 532.33 eV, 284.23 eV, and 103.33 eV, respectively. According to the quantification data in Table 1, the oxygen atomic percentage was 65.82%, while silicon was measured at 32.23%. A minor amount of carbon was also detected, likely due to environmental contamination. In Fig. 3e, the Si 2p peak was deconvoluted into three components, with the dominant peak at 103.69 eV corresponding to SiO2, confirming oxide growth during the SLO process. The O 1s peak, shown in Fig. 3f, was resolved into four components. The peak at 532.88 eV aligned with SiO2 as seen in the Si 2p spectrum. Minor peaks at 530.56 eV and 534.71 eV were attributed to C–O and C=O bonds, likely by-products of surface contamination. Additionally, the presence of hydroxyl (OH) groups suggested slight moisture adsorption during or after processing30.

Using a writing speed of 0.3 µm/s and an applied voltage of 9 V, oxide patterns were generated via the AFM-LAO method. The average lateral dimensions of these oxide features were recorded. Subsequent silicon etching was carried out using a ternary solution composed of TMAH, Triton X-100, and IPA, and the resulting lateral dimensions of silicon were measured post-etching. After etching, it was observed that the lateral dimensions of silicon wire were larger than the original oxide pattern dimensions. This was due to the formation of a trapezoidal profile in the etched wires. The top width matched the oxide mask, while the base expanded due to anisotropic etching behaviour, which is influenced by the crystalline structure of silicon. This indicates that the vertical etching rate was greater than the lateral etch rate beneath the oxide coverage.

Following the SLO treatment, the average of lateral dimensions for oxide growth on the SiNWs structures was measured, and the oxide growth percentage was calculated accordingly. Once the oxidation step was complete, the oxide was removed using HF, and the final dimensions of the SiNWs structures were recorded. The thickness reduction of the silicon layer at each temperature point was also determined. Table 2 describe on oxide growth percentage and silicon reduction percentage varied with temperature during the SLO process. Both metrics showed a direct correlation with increased oxidation temperature. At 850 °C, oxide growth reached 34.35%, corresponding to a 15.4% reduction in silicon. At 900 °C, oxide formation increased to 58.3%, with a 26.2% silicon reduction. At 950 °C, oxide growth climbed to 70.3%, and lateral dimensions of silicon decreased by 33.7%. The highest tested temperature, 1000 °C, resulted in 78.3% oxide growth and a 36.5% decrease in silicon lateral dimensions, confirming enhanced scale-down efficiency at elevated temperatures.

The enhanced efficiency of dimensional reduction at 1000 °C can be attributed to the increased oxidation kinetics at elevated temperatures. Higher temperatures accelerate the diffusion of oxygen molecules through the growing oxide layer and increase the reaction rate at the Si/SiO2 interface. According to the Deal–Grove model, thermal oxidation involves a linear-parabolic growth mechanism, where the parabolic rate constant and linear rate constant are both temperature-dependent31,32. At higher temperatures, the parabolic growth dominates due to faster oxygen diffusion, resulting in thicker and more uniform oxide layers over shorter timescales. This promotes consistent dimensional thinning across the nanowire structure while minimizing process variability. Additionally, the elevated temperature helps reduce interface defects and promotes smoother oxide–silicon transitions, further contributing to the overall structural refinement of the SiNWs. Based on these results, 1000 °C was identified as the optimal temperature for oxide growth and silicon thinning. To further investigate dimensional reduction, additional SLO cycles were performed at this temperature.

Effect of multiple SLO cycles on nanowire morphology and roughness

Following identification of 1000 °C as the optimal oxidation temperature, the number of SLO cycles was varied to investigate their cumulative impact on nanowire geometry and surface characteristics. An oxidation temperature of 1000 °C was maintained with a soaking duration of 7 h and an oxygen gas flow rate of 100 cc/min. The changes in oxide layer thickness and their impact on the final SiNW-FET structure were examined after each oxidation cycle. A maximum of three SLO cycles were applied to the SiNW-FET device. As indicated in Fig. 2, the structural transformation of the SiNW-FET array is evident when comparing images (c) before and (d) after completing three SLO cycles. Additionally, the surface roughness of the nanowires post-scale-down was assessed using AFM Nanonavi software, with results shown in Fig. 2e. The lateral dimension of the SiNWs decreased from 412 to 220 nm, corresponding to a 46.6% reduction in lateral dimensions. In terms of vertical dimension, the silicon height dropped from an initial 118–37 nm after processing, signifying a 68.6% reduction in thickness. These results confirm that repeated SLO cycles at elevated temperatures effectively refine the nanowire geometry, producing narrower and thinner structures suitable for advanced nanoelectronics device fabrication.

Consequently, performing only one SLO cycle was insufficient to achieve the minimum lateral dimensions of the SiNWs, even with an oxidation duration extended beyond 10 h. This limitation is attributed to the oxide layer reaching a saturation point, eventually approaching a plateau, as previously observed by Wright et al.33. As a consequence of the dimensional scaling process, the SVR of the nanowires increased considerably. This parameter is crucial in device performance, as it reflects the extent of available surface relative to the internal volume, which is especially important for surface-sensitive applications. The SVR was estimated based on the final nanowire geometry using a Pythagorean19 approach. Specifically, for nanowires with a trapezoidal cross-section, the SVR was calculated using the expression: surface-to-volume ratio = (W1 + 2 h)/\(\frac{H}{2}\)(W1 + W2). Where W₁ and W₂ represent the top and bottom widths of the trapezoidal nanowire cross-section, h denotes the sidewall height, and H is the total vertical height of the nanowire as shows in Fig. 2g. The calculated SVR values before and after three SLO cycles were 0.01246 nm−1 and 0.03329 nm−1, respectively. This indicates a clear increase in the SVR of the SiNWs after the SLO process. A high SVR is essential in SiNW-FET, as it enhances sensitivity, electrostatic control, device performance, and energy efficiency. This property is particularly critical in modern transistor design at the nanoscale, where surface effects dominate electrical behaviour.

Electrical characterization of SiNW-FET array

The electrical characterization of the fabricated SiNW-FET array focused on evaluating the current–voltage (I–V) performance and resistance behaviour of SiNW-FET array before and after the SLO processes depict in Fig. 4a. The I–V measurements were conducted by sweeping the Vds from 0 to 1 V under ambient conditions at room temperature. Prior to the SLO process, the device exhibited a drain current (Ids) of 0.133 nA at Vds = 1 V, indicating a linear response typical of ohmic behaviour. Following the SLO process, which reduced the nanowire’s lateral dimensions from 412 to 220 nm, the Ids decreased to 0.108 nA at the same bias voltage. This decrease in current reflects an increase in channel resistance, consistent with the narrowing of the nanowire’s cross-sectional area. In addition to dimensional scaling, the increase in surface roughness following repeated high-temperature oxidation cycles may have introduced enhanced charge carrier scattering along the nanowire surface, thereby contributing further to the observed reduction in current. It is important to clarify that this reduction in current does not indicate performance degradation. Rather, it confirms the effectiveness of the SLO technique in achieving precise dimensional scaling, which improves the SVR, a desirable characteristic for nanoscale transistor operation and sensing applications. The observed electrical behaviour is in agreement with classical scaling principles, where reduced channel width results in higher resistance and lower current at fixed bias.

As presented in Fig. 4b, the resistance values were calculated from the linear regions of the I–V curves using the relation R = V/I. Before the SLO treatment, the SiNW-FET array had a resistance of 7.37 × 109 Ω. After the SLO process, the resistance increased to 9.05 × 109 Ω, corresponding with the physical reduction in lateral dimensions of nanowire. This observation aligns with the theoretical model in which resistance (R) is inversely proportional to the nanowire’s cross-sectional area (A), described by R = ρℓ/A. These findings support the intended role of SLO as a dimensional refinement step that contributes to the tunability and predictability of electrical characteristics in SiNW-based device.

Conclusion

SiNW-FET array was successfully fabricated on a p-type SOI substrate using AFM-LAO lithography and subsequently refined through the SLO process to achieve precise dimensional control. This post-fabrication approach enabled significant reductions in both lateral and vertical dimensions of the SiNWs structures. Among the process variables explored, oxidation temperature and the number of SLO cycles emerged as critical parameters affecting the nanowire morphology and electrical characteristics. It should be noted that the present study fixed the oxygen flow rate and oxidation duration to allow systematic assessment of temperature and cycle effects. Further optimization of these parameters is ongoing and will be presented in subsequent publications. Electrical characterization before and after SLO treatment showed a clear increase in channel resistance and a corresponding decrease in drain current, consistent with the expected impact of reduced cross-sectional area. The linearity of the I–V response confirmed ohmic behaviour, while the dimensional scaling achieved via SLO demonstrated excellent correlation with theoretical models of nanoscale transport. These results validate the SLO technique as an effective method for improving device uniformity and tailoring SiNW-FET performance. It is worth noting that the SLO process involves a high thermal budget, requiring extended exposure to elevated temperatures. This may pose challenges for integration with thermally sensitive substrates or device architectures. Future studies should therefore explore alternative oxidation methods, such as low-temperature or localized heating strategies, to expand the versatility and compatibility of the fabrication process.

Data availability

Data is provided within the manuscript files.

References

Ajayan, J. et al. Nanosheet field effect transistors-A next generation device to keep Moore’s law alive: An intensive study. Microelectron. J. 114, 105141. https://doi.org/10.1016/j.mejo.2021.105141 (2021).

Huang, C. Y., et al. 3-D self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued Moore’s law scaling. In 2020 IEEE International Electron Devices Meeting (IEDM) (2020). https://doi.org/10.1109/iedm13553.2020.9372066.

Xue, Z. et al. Engineering in-plane silicon nanowire springs for highly stretchable electronics. J. Semicond. 39(1), 011001. https://doi.org/10.1088/1674-4926/39/1/011001 (2018).

Shin, M., Jeong, W. J. & Lee, J. Density functional theory based simulations of silicon nanowire field effect transistors. J. Appl. Phys. 119(15), 154505. https://doi.org/10.1063/1.4946754 (2016).

Elfstrom, N. et al. Surface charge sensitivity of silicon nanowires: Size dependence. Nano Lett. 7(9), 2608–2612. https://doi.org/10.1021/nl0709017 (2007).

Adam, T. & Hashim, U. Highly sensitive silicon nanowire biosensor with novel liquid gate control for detection of specific single-stranded DNA molecules. Biosens. Bioelectron. 67, 656–661. https://doi.org/10.1016/j.bios.2014.10.005 (2015).

Yusoh, S. N., Yaacob, K. A. & Alias, N. N. Trapezoidal SiNWs array fabricated by AFM-LAO for dengue virus DNA oligomer detection. Mater. Res. Express 6(11), 115005. https://doi.org/10.1088/2053-1591/ab3571 (2019).

Nuzaihan, M. N. M. et al. Electrical detection of dengue virus (DENV) DNA oligomer using silicon nanowire biosensor with novel molecular gate control. Biosens. Bioelectron. 83, 106–114. https://doi.org/10.1016/j.bios.2016.04.033 (2016).

Li, J. et al. Monitoring of dynamic processes during detection of cardiac biomarkers using silicon nanowire field-effect transistors. Adv. Mater. Interfaces 7(15), 1–11. https://doi.org/10.1002/admi.202000508 (2020).

Zhang, J. et al. Silicon nanowire FET biosensor and its application in acute myocardial infarction. Nanotechnology 35(11), 112001. https://doi.org/10.1088/1361-6528/ad1438 (2024).

Gongalsky, M. B. et al. Double etched porous silicon nanowire arrays for impedance sensing of influenza viruses. Results Mater. 6, 100084. https://doi.org/10.1016/j.rinma.2020.100084 (2020).

Wasfi, A. et al. COVID-19 detection via silicon nanowire field-effect transistor: setup and modeling of its function. Nanomaterials (Basel) 12(15), 2638. https://doi.org/10.3390/nano12152638 (2022).

Mukherjee, S. et al. A fabrication method for realizing vertically aligned silicon nanowires featuring precise dimension control. Sensors 24(22), 7144. https://doi.org/10.3390/s24227144 (2024).

Pennelli, G. Top down fabrication of long silicon nanowire devices by means of lateral oxidation. Microelectron. Eng. 86(11), 2139–2143. https://doi.org/10.1016/j.mee.2009.02.032 (2009).

Ryu, Y. K., Chiesa, M. & Garcia, R. Electrical characteristics of silicon nanowire transistors fabricated by scanning probe and electron beam lithographies. Nanotechnology 24(31), 315205. https://doi.org/10.1088/0957-4484/24/31/315205 (2013).

Aidil, S. A., et al. Fabrication and characterization of poly-Si nanowire with thin film of Ni/Au contact pad using conventional photolithography. In 2019 IEEE International Conference on Sensors and Nanotechnology, SENSORS and NANO 2019 (2019). https://doi.org/10.1109/SENSORSNANO44414.2019.8940057.

Lee, K. N. et al. Fabrication of silicon nanowire for biosensor applications. Proc. IEEE Sens. https://doi.org/10.1109/ICSENS.2007.355860 (2006).

Reguer, A. & Dallaporta, H. Growth study of silicon nanowires by electron microscopies. Mater. Sci. Semicond. Process. 12(1–2), 44–51. https://doi.org/10.1016/j.mssp.2009.07.015 (2009).

Yusoh, S. N. Development of Dengue Biosensor on Silicon Wire Arrays Using Local Anodic Oxidation by Atomic Force Microscope, in School of Materials and Mineral Resources Engineering 178 (Universiti Sains Malaysia, 2018).

Rola, K. P. et al. Silicon 45° micromirrors fabricated by etching in alkaline solutions with organic additives. Microsyst. Technol. 20(2), 221–226. https://doi.org/10.1007/s00542-013-1859-z (2014).

Zhang, L. et al. Effects of etching conditions on surface morphology of periodic inverted trapezoidal patterned Si(100) substrate. Optoelectron. Lett. 13(1), 45–49. https://doi.org/10.1007/s11801-017-6242-3 (2017).

Yao, M. et al. Silicon anisotropic etching in triton-mixed and isopropyl alcohol-mixed tetramethyl ammonium hydroxide solution. Micro Nano Lett. 10(9), 469–471. https://doi.org/10.1049/mnl.2015.0104 (2015).

Alias, N. N., Yaacob, K. A. & Yew, C. K. Effect of etchant on SOI wafer surface roughness for APTES silanization. Mater. Today Proc. 17, 700–706. https://doi.org/10.1016/j.matpr.2019.06.353 (2019).

Cui, Y. et al. Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species. Science 293(5533), 1289–1292. https://doi.org/10.1126/science.1062711 (2001).

Niess, J., et al. Highly Reliable Rapid Thermal Selective Gate Re-oxidation Process of Advanced Metal Gate Stacks with Tungsten Electrode (2007). https://doi.org/10.1109/RTP.2007.4383844.

Jedlinski, J. Local and microstructure-related effects affecting the high temperature oxidation of alumina formers: A brief survey. Mater. High Temp. 22(3–4), 485–495. https://doi.org/10.1179/mht.2005.059 (2005).

Yoo, J. H. et al. Relaxation of misfit strain in silicon-germanium (Si1−xGex) films during dry oxidation. J. Vac. Sci. Technol. 28(6), 1298–1303. https://doi.org/10.1116/1.3516014 (2010).

Werner, P. et al. Gold-enhanced oxidation of silicon nanowires. Int. J. Mater. Res. 98(11), 1066–1070. https://doi.org/10.3139/146.101564 (2007).

Bonifas, A. P., McCreery, R. L. & Harris, K. D. Thermal oxidation as a simple method to increase resolution in nanoimprint lithography. Microelectron. Eng. 88(11), 3256–3260. https://doi.org/10.1016/j.mee.2011.08.006 (2011).

Post, P. et al. Characterization and applications of nanoparticles modified in-flight with silica or silica-organic coatings. Nanomaterials (Basel) 8(7), 530. https://doi.org/10.3390/nano8070530 (2018).

Saad, A. M. et al. Revealing two components of oxidant flux for thermal oxidation of silicon contrary to several models. J. Mater. Sci. 52(1), 437–445. https://doi.org/10.1007/s10853-016-0343-4 (2017).

Xu, Z., Rosso, K. M. & Bruemmer, S. M. A generalized mathematical framework for thermal oxidation kinetics. J. Chem. Phys. 135(2), 024108. https://doi.org/10.1063/1.3607984 (2011).

Wright, J. T. et al. Thermal oxidation of silicon in a residual oxygen atmosphere—The RESOX process—For self-limiting growth of thin silicon dioxide films. Semicond. Sci. Technol. 31(10), 105007. https://doi.org/10.1088/0268-1242/31/10/105007 (2016).

Acknowledgements

This work was performed under the support of the Ministry of Education Malaysia through a Fundamental Research Grant Scheme under Grant Number FRGS/1/2018/TK05/USM/02/5. Part of this work was also supported by Research University Grant, Grant Number GUP-2024-003.

Author information

Authors and Affiliations

Contributions

Nurain Najihah Alias: Writing—original draft, methodology, formal analysis, conceptualization. Muhammad Aniq Shazni Mohammad Haniff: Supervision, validation, writing—review and editing, funding acquisition. Khatijah Aisha Yaacob: Writing—review and editing, conceptualization, supervision, funding acquisition.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Alias, N.N., Mohammad Haniff, M.A.S. & Yaacob, K.A. Fabrication and dimensional scaling of SiNW-FET array via AFM-LAO lithography and self-limiting oxidation. Sci Rep 15, 32902 (2025). https://doi.org/10.1038/s41598-025-18100-z

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-18100-z