Abstract

A split-gate double-channel asymmetric SiC trench MOSFET (SGDC-ATMOS) is proposed in this work. Besides a P+ shielded region covering the bottom of the trench, a charge balance effect caused by the split gate further reduces the maximum gate oxide electric field (Emox) around the trench, which effectively improves the reliability of the SGDC structure. Additionally, the excellent capacitance characteristics is achieved by varying the length of the P+ shielded region on the right side of the trench. The SGDC structure ensures better current conduction capability by adopting a double conduction channel. Furthermore, the SGDC structure also introduces a current spreading layer to alleviate the junction field-effect transistor (JFET) effect. Simulations demonstrate that, compared with the conventional asymmetric trench MOSFET (C-ATMOS), the SGDC structure shows a 31.5% reduction in the Emox, a 98.4% reduction in the gate-drain capacitance, and a 5% reduction in specific on-resistance, which demonstrates superior gate oxide reliability and dynamic characteristics, making it better suited for the high-performance and low power-loss applications.

Similar content being viewed by others

Introduction

Silicon carbide (SiC) materials offer several advantages over Silicon, including larger bandgap, higher critical breakdown electric field, higher electron saturation velocity and better thermal conductivity. These properties make it an excellent choice for the high-voltage power electronic devices with broad application prospects in the high-voltage, high-temperature, high-power and radiation-resistant scenarios1,2. Compared to traditional planar MOSFET, the SiC trench MOSFET demonstrates higher cell density, faster switching speed, and lower conduction loss, which can enhances the power density and operating efficiency3,4,5. However, the gate of SiC trench MOSFET is situated within the device structure, resulting in significant electric field concentration at the corner and bottom of the trench. The maximum gate oxide electric field (Emox) is higher than the critical breakdown electric field of Silicon dioxide (SiO2), thus causing early damage to the gate oxide6,7,8. Moreover, due to the low SiC/SiO2 interface barrier height and high interface defect density, SiC trench MOSFET exhibits lower channel mobility and higher specific on-resistance (Ron, sp)7,8.

There have been notable improvements that aimed at above challenges for the SiC trench MOSFET. The trench MOSFET which reduces the Ron, sp by forming an accumulation channel and two current paths were proposed9,10. Although the Ron, sp is important to the performances of the device, the reliability of the gate oxide should also be considered seriously. Therefore, the conventional asymmetric trench MOSFET (C-ATMOS) is presented11. The C-ATMOS adopts a half cell structure to ensure a low Ron, sp, and the slope injected P+ shielded region is used to improve the reliability of the gate oxide of the device simultaneously. However, the C-ATMOS has only one conduction channel, which limits its current conduction capacity. Consequently, significant researches should focus on improving the gate oxide reliability and maximizing the current conduction capability for SiC trench MOSFET.

In this work, a split-gate double-channel asymmetric trench MOSFET (SGDC-ATMOS) is proposed. The simulation study of the SGDC-ATMOS model employs the Silvaco TCAD software. By optimizing the doping concentration (NCSL) of the current spreading layer (CSL) and the length (h) of the P+ shielded region along the right side of the trench. Compared to the C-ATMOS, a lower Ron, sp and the Emox is achieved for the SGDC-ATMOS. Moreover, the contact area between the gate and drain is modified by varying the values of h, resulting in a reduction of the gate-drain capacitance (Cgd) and gate-drain charge (Qgd).

Device structure and design principle

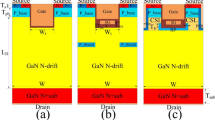

Cross-sectional diagrams of (a) C-ATMOS and (b) SGDC-ATMOS.

Figure 1 illustrates the cross-sectional diagrams of the C-ATMOS and the SGDC-ATMOS. The primary distinction between the two trench MOSFET is the configuration of the P+ shielded region. Compared with C-ATMOS, the SGCD structure uses a novel design of P+ shielded region for extending and covering the bottom of the trench, which more effectively protects the gate oxide. Furthermore, the introduction of a split gate In the SGDC structure results in a deeper trench depth, which contributes to the formation of a double conduction channel. More notably, due to the charge balance effect, the split gate forms a depletion layer around the trench, thus reducing the electric field strength around the gate oxide12,13. Finally, the CSL region between trenches shown in Fig. 1b weakens the the junction field-effect transistor (JFET) effect that arises from the complete wrapping of the trench bottom by the P+ shielded region14.

Based on the the state-of-the-art fabrication technology, the trench width (WT), the trench depth (TD), the cell pitch (Wcell) and the channel length are set with the values of 1.2 μm, 2.4 μm, 2.6 μm and 0.4 μm, respectively, and the channel mobility is rated at 40 cm²/V·s15,16. The thickness of gate sidewall oxide (TOX) and the split gate sidewall oxide (TOXSG) are 50 nm and 150 nm, respectively. For consistency, the drift layer thickness (Tdrift) and the drift layer doping concentration for both devices are maintained at 10 μm and 8 × 10¹⁵ cm⁻³, respectively. The research employs the Silvaco TCAD software to simulate and analyze the impacts of the variations of NCSL and h on the device performances of both MOSFET.

Device simulation and results discussion

The Ron, sp is a critical parameter of power devices in the conducting state, as it affects the conduction losses and efficiency, and the JFET effect has a great influence on the Ron, sp of MOSFET. As shown in Fig. 2a, with the NCSL of 1 × 1016 cm− 3, no current flow is observed in the SGDC structure, which means that it is necessary to optimize the NCSL to improve the conductivity. In Fig. 2b–f, with the increase of NCSL, the reduction of the depletion layer width on both sides of the JFET region in the SGDC structure enables current path expansion, thereby lowering the Ron, sp. Therefore, the JFET effect of the SGDC structure is weakened by optimizing the doping concentration for the CSL region, which improves the conductivity of the SGDC structure effectively.

Simulated current distributions of SGDC-ATMOS with varying NCSL values.

Although a higher NCSL can enhances the current conduction capability of the device, it simultaneously reduces the depletion layer width beside both sides of the JFET region, which also adversely impacts the gate oxide reliability. The Emox must be maintained below 3 MV/cm to ensure the long-term reliability of gate oxide17,18. Figure 3 shows the simulated electric field and equipotential line distribution of the SGDC-ATMOS. The results reveal that the highest electric field occurs along the corner of the trench. With the increase of NCSL, the increasing of Emox from 1.46 MV/cm to 3.65 MV/cm results from the reduction in the depletion layer thickness beside both sides of the JFET region. Based on the equipotential line distribution, it is evident that the electric potential in the JFET region raise with the increase of NCSL, thereby diminishing the protective capability of the P+ shielded region for the gate oxide.

Simulated electric field and equipotential line distributions of SGDC-ATMOS with different NCSL values.

According to the above analysis, it is necessary to select a appropriate NCSL to ensure that the SGDC structure has excellent conductivity and gate oxide reliability. As shown in Fig. 4a, the breakdown voltage (BV) of the device is inversely proportional to NCSL. The Ron, sp, Emox and BV for the SGDC-ATMOS at various NCSL are shown in Fig. 4b. With the increase of NCSL, the data shows a significant initial decrease in Ron, sp, before a slowing trend is observed when NCSL=4 × 1016 cm− 3. The trends of Emox changes is opposite. Therefore, in order to achieve a BV level of 1200 V and optimize the trade-off between the Ron, sp and Emox, the optimal NCSL parameter in this work is set to 4 × 1016 cm− 3.

Simulated (a) leakage current and (b) BV, Emox, and Ron, sp of SGDC-ATMOS with varying NCSL values.

In addition to doping concentration, the structural design of P+ shielded region also plays a crucial role on improving the performance of the MOSFET. The depletion region on the right side of the trench will be changed by adjusting the parameter h values, thereby affecting the static performances of the SGDC structure. As shown in Fig. 5a–c, the devices with h = 1.0 μm and 1.4 μm exhibit two current conduction paths, while the left current conduction path is blocked in the device with h = 1.8 μm, leaving only right conduction path, which contradicts the design guidelines proposed in this study. Moreover, it is clear that the gate oxide electric field of structures with h = 1.4 μm and 1.8 μm is lower than that of the device with h = 1.0 μm.

Simulated (a–c) current and (d–f) electric field distributions of SGDC-ATMOS under varying h conditions.

As shown in Fig. 6a, the h parameter has little effect on the BV of the SGDC structure due to the BV is only related to the P+ shield region at the bottom of the trench. The Ron, sp raises with the increasing of h values, which is attributed to the increased length of the P+ shielded region along the right side of the trench provides a new depletion layer that blocks the current conduction. The Emox decreases with the increase of h value and reaches a minimum h = 1.4 μm, and then gradually reaches saturation. As shown in Fig. 6b, the Emox of the C-ATMOS is 2.32 MV/cm, The Emox of SGDC structure with h = 1.4 μm is 1.59 MV/cm, which is 31.5% lower than that of C-ATMOS, showing a better gate oxide reliability.

(a) Simulated Ron, sp, Emox, and BV of SGDC-ATMOS for various h values. (b) Simulated electric field distributions of SGDC-ATMOS with h = 1.4 μm and C-ATMOS.

Furthermore, the dynamic characteristics is especially important to the SiC trench MOSFET. The typical dynamic characteristics primarily include the switching time, the switching losses, and reverse recovery, all of which affect the efficiency of power devices. The Cgd is a key parameter that influences the dynamic characteristics of MOSFET, as it affects the switching speed and losses.

Schematic diagram of capacitance distribution within the SGDC-ATMOS.

The capacitance distribution of the SGDC structure is shown in Fig. 7. The split gate partially shields the contact area between the gate and the drain, resulting in the Cgd of this structure being primarily composed of the gate, the side oxide layer, the drift region, and the drain. The Cgd1 and Cgd2 are connected in parallel and then connected in series with Cgd3. Similarly, Cgd1, Cgd4 and Cgd3 are also connected in parallel first and then in series. For simplifying the calculations, it is assumed that the depletion layer widths D1 and D2 are equal to D. The relationship between the these capacitances can be described as follow equations:

where εs is the dielectric constant of SiC, εOX is the dielectric constant of oxide layer. The value of Cgd can be achieved by substituting Eqs. (1), (2), and (3) into Eq. (4) which reveals that the Cgd is negatively correlated with h (i.e., a larger h is more helpful for reducing Cgd).

(a) The Cgd-Vds and (b) Qg-Vgs curves for C-ATMOS and SGDC-ATMOS with varying h values.

This work further confirms the correctness of the above theoretical analysis by simulation method. As shown in Fig. 8a, the Cgd of the C-ATMOS and the SGDC-ATMOS changes with varying h values. At a high gate-drain voltages, the Cgd of the C-ATMOS is higher than that of the SGDC structure due to greater exposure area between the gate to the drain. Meanwhile, the Cgd of the SGDC structure decreases with the increase of h, which is due to the reduction of contact area between the gate sidewall and drain. Therefore, it can be confirmed that the structural parameter h is directly proportional to the Cgd of the SGDC-ATMOS.

The Qgd which is proportional to Cgd also has a significant influence on the dynamic characteristics of MOSFET. The test circuit shown in Fig. 8b assesses the performances of the both devices, using a 800 VDC and an ideal free-wheeling diode. The Qgd is obtained by superimposing the Vds waveform onto the Qg characteristic19. As shown in Fig. 8b, the Miller plateau of the SGDC structure is lower than that of the C-ATMOS, which indicates that the SGDC structure has lower switching losses and improved frequency characteristics.

Simulating short-circuit current for C-ATMOS and SGDC-ATMOS with varying h values.

Furthermore, the short-circuit reliability is crucial for power devices, which not only affects the stability of the MOSFET but also relates to the economic efficiency of the entire power system. The short-circuit test shown in Fig. 9 displays the simulated waveforms of short-circuit current (ISC) of the SGDC-ATMOS and the C-ATMOS. Under a 800 VDC and a short-circuit pulse width of 6 µs, with the changing of h from 0.2 μm to 1.8 μm, the ISC of the SGDC-ATMOS decreases from 4532 A/cm2 to 2353 A/cm2, which reflects that this structure exhibits greater short-circuit capability. The ISC of the C-ATMOS is 2548 A/cm2, slightly exceeding that of the SGDC-ATMOS with 1.6 μm of h. It is noted that selecting appropriate h value can improving the short circuit reliability of the SGDC structure.

Table 1 summarizes the comparisons between the key characteristics of the C-ATMOS and the SGDC-ATMOS. With the increase of h, the Baliga’s Figure of Merit (BFOM) decreases and the Emox increases for the SGDC structure, which means that the static performance of the device is inversely proportional to the h, while the Cgd corresponding to dynamic performance decreases. Considering the balance between the static and dynamic performances of the SiC MOSFET, the Figure of Merit of Qgd×Ron, sp is introduced to indicate the comprehensive performance. As shown in Table 1, under the premise of ensuring the short-circuit reliability, the value of h the SGDC is set to 1.4 μm. Therefore, Compared to the C-ATMOS, the SGDC structure with optimized design exhibits significant improvement, which including a 13.1% increase in BFOM, a 31.5% reduction in Emox, a 98.4% reduction in Cgd, and a 5% reduction in Ron, sp. These significant optimization demonstrates that the SGDC-ATMOS achieves excellent gate oxide reliability and dynamic characteristics.

Conclusion

In this work, a split-gate double-channel SiC asymmetric trench MOSFET with enhanced performances is proposed. Combined with the P+ shielded region covering the bottom of the trench, the split gate reduces the maximum gate oxide electric field by the charge balance effect. Additionally, a introducing of CSL effectively alleviate the JFET effect. The simulation results show that, compared with C-ATMOS, the SGDC structure can achieve significant improvement, which have a improvement of 31.5%, 98.4% and 5% in Cgd, Emox and Ron, sp, respectively. These findings confirm that the SGDC-ATMOS exhibits better reliability and dynamic characteristics, which is very promising for high-performance and high-frequency applications.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Kimoto, T. & Watanabe, H. Defect engineering in SiC technology for high-voltage power devices. Appl. Phys. Express. 13(12), 120101. https://doi.org/10.35848/1882-0786/abc787 (2020).

Elasser, A. & Chow, T. P. Silicon carbide benefits and advantages for power electronics circuits and systems. In Proc. IEEE, Vol. 90, no. 6, 969–986 https://doi.org/10.1109/JPROC.2002.1021562 (2002).

Dhar, S. et al. Nitrogen and hydrogen induced trap passivation at the SiO2/4H-SiC interface. In Materials Science Forum, Vol. 527–529, 949–954 (Trans Tech Publications Ltd., 2006).

Chung, G. Y. et al. Improved inversion channel mobility for 4H-SiC mosfets following high temperature anneals in nitric oxide. IEEE Electron. Device Lett. 22(4), 176–178. https://doi.org/10.1109/55.915604 (2001).

Tachiki, K., Mikami, K., Ito, K., Kaneko, M. & Kimoto, T. Mobility enhancement in heavily doped 4H-SiC (0001),(112̄0), and (11̄00) mosfets via an oxidation-minimizing process. Appl. Phys. Express. 15(7), 071001. https://doi.org/10.35848/1882-0786/ac7197 (2022).

Cooper, J. A., Melloch, M. R., Singh, R., Agarwal, A. & Palmour, J. W. Status and prospects for SiC power mosfets. IEEE Trans. Electron. Devices. 49(4), 658–664. https://doi.org/10.1109/16.992876 (2002).

Singh, R. & Hefner, A. R. Reliability of SiC MOS devices. Solid-State Electron. 48, 10–11. https://doi.org/10.1016/j.sse.2004.05.005 (2004).

Sui, Y., Tsuji, T. & Cooper, J. A. On-state characteristics of SiC power umosfets on 115-µm drift layers. IEEE Electron. Device Lett. 26(4), 255–257. https://doi.org/10.1109/led.2005.845495 (2005).

Tan, J., Cooper, J. A. & Melloch, M. R. High-voltage accumulation-layer umosfet’s in 4H-SiC. IEEE Electron. Device Lett. 19(12), 487–489. https://doi.org/10.1109/55.735755 (1998).

Nakamura, T. et al. High performance SiC trench devices with ultra-low ron. In 2011 Int. Electron Devices Meet., Washington, DC, USA, 26 – 5, (IEEE, 2011).

Peters, D. et al. Performance and ruggedness of 1200V SiC-Trench-MOSFET, in 2017 29th Int. Sympos. Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 239–242. (2017).

Deng, S., Hossain, Z. & Taniguchi, T. Detailed study on dynamic characteristics of a high-performance SGT-MOSFET with under-the-trench floating P-pillar. IEEE Trans. Electron. Devices. 64(3), 735–740. https://doi.org/10.1109/TED.2017.2658568 (2017).

Wu, L. et al. Improving dynamic performance for split-gate trench power mosfets using variable vertical doping profile. Micro Nanostruct. 172, 207446. https://doi.org/10.1016/j.micrna.2022.207446 (2022).

Wang, B. et al. A novel SiC trench MOSFET with self-aligned N-type ion implantation technique. 14(12), 2212 https://doi.org/10.3390/mi14122212 (2023).

Nanen, Y., Kato, M., Suda, J. & Kimoto, T. Effects of nitridation on 4H-SiC mosfets fabricated on various crystal faces. IEEE Trans. Electron. Devices. 60(3), 1260–1262. https://doi.org/10.1109/TED.2012.2236333 (2013).

Nakazawa, S., Okuda, T., Suda, J., Nakamura, T. & Kimoto, T. Interface properties of 4H-SiC ($11\bar {2} 0$) and ($1\bar {1} 00$) MOS structures annealed in NO. IEEE Trans. Electron. Devices. 62(2), 309–315. https://doi.org/10.1109/TED.2014.2352117 (2014).

Zhu, S. et al. Reliability comparison of commercial planar and trench 4H-SiC Power MOSFETs. In IEEE Int. Reliability Physics Symposium (IRPS), , Monterey, CA, USA, 2023 1–5 (IEEE, 2023).

Matocha, K., Dunne, G., Soloviev, S. & Beaupre, R. Time-dependent dielectric breakdown of 4H-SiC MOS capacitors and DMOSFETs. IEEE Trans. Electron. Devices. 55(8), 1830–1834. https://doi.org/10.1109/TED.2008.926595 (2008).

Basler, T., Heer, D., Peters, D. & Schorner, R. Practical aspects andbody diode robustness of a 1200 V SiC trench MOSFET. In Proc. PCIM, Vol. 18, no. 455, 313–315 (2018).

Acknowledgements

This work was supported in part by the Innovation Technology Platform Project jointly built by Yangzhou City and Yangzhou University No. YZ2020268, in part by the Opening Foundation of Innovation Technology Platform Project jointly built by Yangzhou City and Yangzhou University No. YZ202026802, in part by the Project of Cooperation between Yangzhou City and Yangzhou University No. YZ2022186, in part by the Jiangsu Province Industry-University-Research Cooperation Project No. BY2021500, and in part by the Opening Foundation of Jiangsu Provincial Key Laboratory of Photonic and Electronic Materials Sciences and Technology No. 202108.

Author information

Authors and Affiliations

Contributions

F.X. conceived and designed the device structure, performed simulation studies, processed simulation data, drafted the manuscript, supervised the overall research and acted as the corresponding author responsible for manuscript communication and submission. Y.D., F.L. and F.X. conducted literature research, and organized references. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Xu, F., Dong, Y., Li, F. et al. A split gate double-channel asymmetric SiC trench MOSFET for improved gate oxide reliability and dynamic characteristics. Sci Rep 15, 43990 (2025). https://doi.org/10.1038/s41598-025-27655-w

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-27655-w