Abstract

Two-dimensional (2D) semiconductors hold a great promise for next-generation electronics. Yet, achieving a clean and intact transfer of 2D films on device-compatible substrates remains a critical challenge. Here, we report an approach that uses selenium (Se) as the intermediate layer to facilitate the transfer of wafer-scale molybdenum disulfide (MoS2) monolayers on target substrates with high surface/interface cleanness and structural integrity. Our method enables nearly 100% film intactness of the transferred 2D semiconductors which are free from residues or contaminants. Characterizations reveal that the Se-assisted dry-transfer yields MoS2 film with superior quality compared to conventional transfer techniques. The fabricated field-effect transistors (FETs) and logic circuits based on these transferred films demonstrate remarkable electrical performance, including on/off current ratios up to 2.7×1010 and electron mobility of 71.3 cm2·V-1·s-1 for individual FETs. Our results underscore the feasibility of this dry-transfer technology for fabricating high-performance 2D electronics that are fully compatible with standard semiconductor processes, paving the way for integrating 2D materials into advanced electronic applications.

Similar content being viewed by others

Introduction

Two-dimensional (2D) semiconductors have attracted significant attentions as promising ultrathin channel materials for advanced electronics, such as next-generation integrated circuits (ICs), flexible electronics, sensors, and optoelectronics, owing to their atomic thickness and optical/electrical properties1,2,3,4,5. While high-quality, wafer-scale 2D semiconductor films have been successfully achieved via chemical vapor deposition (CVD) technique6,7,8,9,10, their practical integration into devices remains constrained by the requirement of specific growth substrates (e.g., sapphire) due to the limitation of lattice matching and thermodynamic factors, posing severe challenges for scale batch manufacturing of 2D electronic devices11,12,13. To address this issue, a large-area transfer of 2D semiconductor films from their growth substrates to target substrates is essential in device fabrication process14,15,16, while maintaining high integrity of the transferred films and avoiding surface/interface contaminations to the best degree as we could is pivotal to achieve optimal device performances.

In large-scale transfer approaches for 2D materials previously developed, either being wet or dry, a certain of transfer medium are usually employed for carrying these 2D materials transferred from their growth substrates to the target substrates. Yet, some technique bottlenecks remain and hinder the acquisition of high-quality wafer scale 2D films by using existing transfer strategies. For instance, in wet transfer approaches, the delamination of a 2D material from its growth substrate and the removal of the transfer medium (e.g., polymethyl methacrylate, label as PMMA) on the target substrate are usually performed by wet chemical process, which is prone to cause structural damages, incomplete transfer, or surface/interface contaminations17,18. In contrast, dry-transfer approaches have shown significant improvements in achieving much cleaner surfaces/interfaces by employing the mechanical peeling 2D materials off their growth substrates and releasing them onto the target substrates19,20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35. However, in order to create a stronger adhesive interface between a 2D material and the transfer medium to facilitate the mechanical peeling-off, polymers such as polycarbonate (PPC), thermal release tape (TRT), and UV-tape have been used21,22,23,24,25,26,27,28,29,30, along with metals like Au, Ag, and Ni, acting as the intermediate adhesive layers31,32,33,34,35. Consequently, the removal of these polymer and metals on surfaces of 2D materials are usually still assisted by chemical process, and the surface residues are still a concern as the residual contaminations are the main source of the electronic performance degradation.

In this work, we demonstrate a completely dry transfer strategy for wafer-scale 2D semiconductor of monolayer molybdenum disulfide (MoS2) film epitaxially grown on sapphire. A low melting point metal of Se is utilized as the adhesive intermediate layer which can be finally removed by a physical process, i.e., thermal evaporation, leaving the surface of monolayer MoS2 ultra-clean. Field-effect transistors (FETs) and logic circuits are fabricated based on the transferred wafer-scale monolayer MoS2 and corresponding electrical characterizations reveal favorable electrical performances. The as-fabricated FETs exhibit an optimal on/off current ratios (Ion/Ioff ratios) of 2.7 × 1010 and relatively high charge mobility of 71.3 cm2·V−1·s−1, highlighting the promise of this Se-transfer method for advanced 2D electronics with fabrication process compatible with existing semiconductor fabrication processing lines.

Results

Se-mediated dry-transfer process

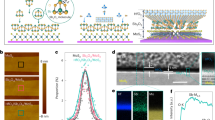

Figure 1a illustrates the schematic of Se-mediated transfer process for wafer-scale MoS2. Starting from a 2-in. wafer-scale monolayer MoS2 epitaxially grown on sapphire, ~500 nm-thick uniform Se is deposited on the surface of monolayer MoS2 film. Detailed characterizations, including photographs, optical microscopy, and atomic force microscopy (AFM) images of the MoS2 surface before and after Se deposition are shown in Supplementary Fig. 1a–f, demonstrating the favorable surface uniformity. A PPC layer is then coated on the Se/MoS2 stack to serve as a support layer during transfer, enabling the mechanical peeling of the entire PPC/Se/MoS2 stack from the sapphire substrate with hydrosol tape assistance, as shown in Fig. 1b. Notably, the Se intermediate layer acts as a gentle yet robust adhesive layer can form a strong interfacial interaction with monolayer MoS2, making it a robust adhesion medium to facilitate the mechanical peeling-off of the MoS2 monolayers from their growth substrates. The interface between Se and MoS2 could be accessed from the cross-section HRTEM images as shown in Supplementary Fig. 2 e and f. Additionally, Se is easily evaporated at low temperatures in vacuum due to its low melting point. The PPC/Se/MoS2 stack is subsequently transferred onto the target substrate, followed by the removal of the hydrosol tape in deionized water (Fig. 1c). Lastly, reactive ion etching (RIE) is employed to remove the PPC residues, while the Se sacrificial layer is thermally evaporated off at 280 oC for 5 h in N2 atmosphere from the surface of monolayer MoS2. Note that the melting point of Se is ~ 221 oC, which falls within the evaporation range of PPC36,37, and see Methods for more experimental details.

a Schematic diagram of the transfer process. PPC polycarbonate, RIE reactive ion etching. b Photographs of a 2-in. wafer-scale Se/MoS2 film on hydrosol tape (left) peeled from sapphire substrate (right). Photographs of the as-transferred 2-in. scale MoS2 film before (c) and (d) after the removal of PPC/Se layer. Optical (e) and AFM (f) image of a Se-mediated transfer MoS2 film on the target substrate. AFM: atomic force microscope, RMS: root-mean-square roughness Optical (g) and AFM (h) image of a PMMA-transferred 2-in. MoS2 film for comparison. PMMA: polymethyl methacrylate.

Figure 1d shows a typical sample of 2-in. monolayer MoS2 transferred on Si/SiO2 substrate with pre-deposited 20-nm thick Al2O3 dielectric layer, highlighting the scalability and integrity of the Se-mediated transfer method. Optical images in Fig. 1e and Supplementary Fig. 3 confirm a crack- and wrinkle-free surface over a large scale. Zoom-in AFM images (Fig. 1f, Supplementary Fig. 4a-i) further confirm the surface flatness, cleanness, and uniformity of the transferred MoS2, with a low root-mean-square (RMS) roughness of ~0.19 nm. In similar control samples of monolayer MoS2 on the same target substrate fabricated via a conventional PMMA assisted wet-transfer process (Supplementary Fig. 5a, b, corresponding to images before and after removal of PMMA), folds, cracks, wrinkles, and PMMA residues are usually seen. Figure 1g, h show the optical and AFM images, correspondingly. And the measured RMS roughness is much higher, i.e., ~0.65 nm.

Compared to the wet-transfer method, the present Se-mediated dry-transfer method not only avoids the introduction of contaminants from the wet process but also mitigates mechanical stress during the transfer process, reducing the risk of crack formation and maintaining the structural uniformity of the MoS2 monolayer. The preservation of the film quality and cleanliness could thus play a pivotal role in advancing large-scale 2D semiconductor devices, providing a reliable way toward scalable, high-quality device manufacturing. To further validate the advantages of Se-mediated transfer strategy, we also used PPC as a direct adhesive layer for transferring wafer scale MoS2 film but failed (supplementary Fig. 6). These results suggest that the binding force between sapphire and MoS2 is significantly stronger than that between MoS2 and PPC, making the PPC transfer method unfeasible for transferring large-scale 2D materials grown on sapphire substrates. Additionally, the feasibility of PMMA/Se/MoS2 configuration for transfer MoS2 film was further confirmed. We can see that PMMA/Se layer can be effectively removed by combined RIE and thermal annealing process (Supplementary Fig. 7b). As seen from the optical and AFM images in Supplementary Fig. 7c, d, the transferred MoS2 film exhibits comparable surface cleanliness with a surface roughness approximately 0.196 nm. The results demonstrate the broad applicability of this Se-mediated transfer technique, extending its utility beyond PPC alone.

We attribute the transfer of wafer-scale 2D MoS2 from the growth substrate to several key aspects: (1) The binding force between Se and MoS2 is significantly greater than that between MoS2 and sapphire; (2) The thick Se layer plays a key role for large-area transfer, ensuring the highly integrity of the MoS2 film during the transfer process. (3) Hydrosol adhesive tape and roller pressing techniques are used to remove air bubbles, ensuring full contact between layers during the transfer process, thereby increasing the success rate of the transfer.

Characterizations of the as-transferred MoS2 wafer

To confirm the complete removal of Se after thermal evaporation, Raman spectra of raw monolayer MoS2 film, Se/MoS2 film, and Se transferred MoS2 film are compared. As shown in Fig. 2a, the typical two Raman peaks at 382 and 402 cm−1 in raw monolayer MoS2 film can be assigned to the E2g and A1g vibration modes, respectively. A slight blue shift of A1g mode (404 cm−1) of Se/MoS2 sample is caused by the deposition of Se layer, inducing interface charge transfer at the interface of MoS2 and Se layer. Note that Raman characteristic peaks of the Se film locate at 142 and 233 cm-1. For Se-mediated transferred MoS2 film, the Se-related Raman peaks vanished and only characteristic peaks of MoS2 existed at 382 and 402 cm−1, indicating complete removal of Se layer after thermal evaporation. The fact of no Se residues is further supported by X-ray photoelectron spectroscopy (XPS), as shown in Fig. 2b, which shows no detectable binding energy signals from the Se 3 d orbitals post-annealing, thereby confirming the effectiveness of the transfer process in producing a clean MoS2 film.

a Raman spectra. b X-ray photoelectron spectra (XPS). Inset: the locally magnified XPS of Se 3d orbitals before annealing treatment. Raman mapping of A1g peak intensity (c) and peak distance (∆ν) between E2g and A1g vibration modes (d). e High resolution transmission electron microscope (HRTEM) image. White triangle: the typical orientation of MoS2 domains. f Selected area electron diffraction (SAED) pattern.

The integrity and spatial uniformity of the as-transferred 2-in. monolayer MoS2 wafer is also accessed via Raman mapping of A1g intensities and the peak distance (∆ν) between E2g and A1g across the entire wafer with an adjacent probing interval of 2 mm (Fig. 2c, d, respectively). Note that the ∆ν is typically ~20 cm−1 for monolayer MoS2. For more peak position mapping of the A1g and specific Raman spectra at different positions, please refer to Supplementary Fig. 8a, b. It is worth noting that the peak shifts are attributed to strain release or interface effects introduced during the transfer process, evidencing from the fact that Raman mapping of a pristine and the MoS2 film (after removal of Se layer) shows no obvious difference, as shown in Supplementary Fig. 9e, f. These Raman mapping results confirm the high spatial uniformity across the entire wafer, which is crucial for large-scale integration of 2D semiconductor devices for many practical applications.

The atomic structure of the monolayer MoS2 transferred via this Se-mediated transfer process is characterized by the atomic-resolution transmission electron microscopy (TEM, Fig. 2e). Nearly perfect lattice structure with no visible Se residues is further confirmed. The selected area electron diffraction (SAED) pattern in Fig. 2f shows a well-defined, undistorted diffraction pattern in the reciprocal space, indicating that the MoS2 retains its single-crystalline nature after Se-mediated transfer. In addition, energy-dispersive X-ray spectroscopy (EDS) detects no signal corresponding to Se (Supplementary Fig. 10), which is consistent with the above characterization results. These characterizations collectively demonstrate that the Se-mediated transfer strategy enables not only a clean transfer process but also the preservation of the crystallographic integrity of monolayer MoS2.

FETs based on Se-mediated transferred MoS2 films

To assess the electrical quality of as-transferred monolayer MoS2 films, we fabricate MoS2 FETs on SiO2/Si substrates (Fig. 3a, b) through a gate-first technology (see Methods). 20-nm Al2O3 dielectric layer is involved in these back-gated FETs and the contact metal is gold (Au). Figure 3c shows the schematic device structure, along with the scanning electron microscopy (SEM) image of an individual FET. The corresponding cross-sectional TEM image and elemental mapping via EDS, depicted in Supplementary Fig. 11, confirms the accurate distribution of Mo and S within the FET channel. Typical output and transfer characteristics of a device with channel length/width of 15/3 µm are shown in Fig. 3d, e, respectively. This device exhibits an Ion/Ioff ratios of ~109 and a threshold voltage (Vth) near 0 V, reflecting the highly intrinsic nature of the monolayer MoS2 channel. Besides, Fig. 3f shows a relatively low hysteresis only about 0.08 V in typical Se-mediated transferred FET, which may be benefited from the clean surface for Se transferred 2D MoS2 channel materials (inset of Fig. 3f). In comparison, the data from PMMA-mediated transfer method are shown in Supplementary Fig. 12a. Note that both negligible hysteresis and Vth shift are critical for device uniformity at a large scale. The device characterization results underscore the cleanness and integrity of the Se-transfer method, which effectively mitigates charge trapping at the interface or surface.

Photograph (a) and optical image (b) of an as-fabricated 2-in. monolayer MoS2 FET array. c Device structure and SEM image of an as-fabricated MoS2 FET. SEM: scanning electron microscope Output (d) and (e) transfer curves of a typical MoS2 FET. f Transfer curves of a FET upon double-sweeping of Vg, showing small hysteresis. Vg: the back-gate voltage. g The transfer characteristics curves from 200 Se-transferred MoS2 FETs. Inset: the transfer characteristics curves of PMMA- transferred MoS2 FETs for comparison. Statistical distribution of Ion (h) and Ion/Ioff ratios (i) with both Se-transferred samples and PMMA-transferred samples involved. Ion: on-current value, Ion/Ioff ratios: on/off current ratios.

Electrical performances of 200 randomly selected FETs fabricated from the Se-transfer process are also presented to further validate the scalability and uniformity of them. The transfer curves of these devices are shown in Fig. 3g, in which the electron mobility (μ) and Ion/Ioff ratios can reach 71.3 cm2·V−1·s−1 and 2.7 × 1010, respectively. The statistical distribution of on-current value (Ion) and Ion/Ioff ratios are presented in Fig. 3h, i. Similar FETs fabricated from PMMA-transfer process are also included as control samples. These devices exhibit inferior performance, with a more negative Vth offset (inset of Fig. 3g) caused by the presence of doping effect due to surface residues. In comparison, the small distribution of Vth for Se-transferred MoS2 FETs (Supplementary Fig. 12b) indicates that the electrical properties of MoS2 films are well preserved. As seen from in Fig. 3i, the Se-transferred FETs exhibit an average Ion/Ioff ratios of 2.6 × 109, which is significantly higher than that of PMMA-transferred FETs, e.g., ~8.3 × 107. The reduced performance of PMMA-transferred MoS2 device is attributed to the contamination and damage introduced during the wet-transfer process. Besides, the contact resistance (Rc) of Se-MoS2 FETs and PMMA-MoS2 FETs were measured by transmission line method (TLM) (Supplementary Fig. 13a). At Vg = 10 V and Vds = 1 V, the extracted Rc and sheet resistance (R□) for Se-MoS2 FETs are about 0.35 kΩ·μm and 0.92 kΩ, respectively (Supplementary Fig. 13b), significantly lower than those of PMMA-MoS2 FETs (2.52 kΩ·μm and 1.52 kΩ). The reduction in Rc suggests that the Se-mediated transfer method yields a cleaner contact interface. These results confirm the advantage of the Se-mediated dry-transfer technique in fabricating high-performance 2D FETs.

Large-scale logic circuits

In order to investigate the logic applications of these Se-transferred MoS2 films, we further fabricated logical units (Fig. 4a), including AND, NAND, NOR, etc. As shown in Fig. 4b, the AND, NAND and NOR logic gates are operated with two input pulses signals of 5 V (VA and VB), all demonstrating accurate Boolean output functionality that is consistent with the corresponding truth tables in Fig. 4c. Moreover, as-fabricated inverters (refer to the inset of Fig. 4d and Supplementary Fig. 14a) present typical voltage transfer characteristics (VTC) with Vdd varying from 1 to 5 V. Obviously, when Vin below the midpoint voltage (VM), Vout reaches a high voltage equal to Vdd, and conversely, Vout approaches 0 V. Supplementary Fig. 14b further illustrates time-domain VTC curves at Vdd = 5 V. These results are consistent with the corresponding logical truth tables (inset of Fig. 4d), indicating that the inverter exhibits the inverting logic function as expected. The voltage gain (G) and static power consumption (P) of an inverter are critical parameters for evaluating its electrical performance. Figure 4e illustrates the variation of G with Vin, with a relatively high volage gain of ~178.8 V/V observed at Vdd = 5 V. The static power consumption of the inverter, shown in Fig. 4e, exhibits low values of ~ 4.5 nW at Vdd = 1 V. In contract, VM of a typical PMMA-transferred MoS2 inverter, as depicted in Supplementary Fig. 15a, exhibits a significant negative offset, and its voltage gain, approximately 113 V/V at Vdd = 1 V, along with its comparatively lower G and gradually increasing static power consumption (inset of Supplementary Fig. 15a, b), which are obviously inferior to those of the Se-transferred MoS2 inverter.

a Optical images of AND, NAND, NOR gates, and ROs. Scale bar, 100 μm. b Output characteristics of an AND, NAND, NOR gate as a function of input voltage pulses at Vdd = 5 V. c The corresponding logic truth tables. d VTC for a MoS2 inverter. VTC: Voltage transfer characteristics, Vin: input voltage, Vout: output voltage. e The static voltage gains and power consumption of a MoS2 inverter at various Vdd. f Normalized output signals of 3-, 5-, and 11-stage 2D MoS2 ROs measured at Vdd = 10 V. g The output frequency varies with Vdd from 1 V to 10 V. Inset: the corresponding delay time per stage (τ). h Comprehensive comparison of the Se-mediated 2D transfer strategy with parts of previous reported work. μ: the electron mobility, Compatibility: the potential of 2D films transfer method for large-scale integration based on standard semiconductor processes.

Large-scale ring oscillators (ROs) consisting of 3-, 5-, and 11-stages are also fabricated, using the Se-transferred monolayer MoS2. The 11-stage ring oscillator, for instance, comprises 11 cascading inverters to generate frequency oscillations (Supplementary Fig. 16a, b), along with an additional inverter serving as an output buffer. As shown in Fig. 4f, the oscillation frequencies of ROs depend on the number of stages, exhibiting distinct values for the 3-, 5-, and 11-stage configurations. Figure 4g presents the typical frequency output as a function of increasing Vdd, revealing an expected trend of decreasing oscillation frequency with increasing stage number (N). The oscillation frequencies reach to 1136 kHz, 711 kHz and 276 kHz for the 3-, 5-, and 11-stage ROs, respectively; and the corresponding delay time per stage (τ) of 0.14 µs, 0.14 µs and 0.16 µs, respectively, calculated by the formula of τ = 1/2Nƒ, where ƒ is the oscillation frequency. The nearly identical delay times across these MoS2 ROs with varying stage numbers suggest well uniformity of the Se-transferred MoS2 film over large areas. As a comparison, similar ROs are also fabricated from the PMMA-transferred MoS2. As shown in Supplementary Fig. 16c, the highest oscillation frequencies achieved were 660.1 kHz, 390.6 kHz and 152.0 kHz for 3-, 5-, and 11-stage MoS2 ROs, respectively, with corresponding delay time per stage is about 0.25 µs, 0.25 µs and 0.29 µs. These values of τ are significantly larger than those observed for the Se-transferred ROs. The results highlight the superior performance and potential of Se-assisted dry-transferred MoS2 films for scalable advanced electronics. Compared with some previously reported about 2D film transfer strategies21,25,27,28,32, as displayed in Fig. 4h, our Se-mediated dry-transfer route exhibits comprehensive advantages for achieve intact transfer of wafer scale 2D semiconductor MoS2 film that retains desired cleanliness and superior electrical quality, being more compatible with standard semiconductor processes for batch fabricate 2D semiconductor ICs in future.

Discussion

A Se-mediated dry-transfer route for large-scale 2D semiconductors is developed, yielding near-perfect film integrity without residues and contaminants. The transfer process employs thermal evaporation to remove the Se intermediate layer and is compatible with the existing semiconductor fabrication process. Electrical characterizations of 2D MoS2 FETs and logic circuits reveal intrinsic performances. This dry transfer approach effectively minimizes the formation of wrinkles and contaminations, providing a reliable solution for the large-scale production of high-performance 2D semiconductor devices.

Methods

Growth of wafer scaled MoS2 monolayer film

Monolayer MoS2 film is epitaxially grown on sapphire by a self-built three-temperature zone CVD system38. The growth process is carried out by using S (Alfa, 99.9%, 8 g) and MoO3 (Alfa, 99.999%, 30 mg) powders as reaction sources, which are placed in the temperature zone I and II, respectively. 2-in. sapphire (c-plane) wafers are used as epitaxial substrates and placed in the temperature zone III. During the growth, the temperatures are 130 °C (zone I), 530 °C (zone II), and 930 °C (zone III) for the S, MoO3 sources and sapphire substrate, respectively. The reactive S and MoO3 vapors were respectively carried by Ar gas (100 sccm) and Ar (200 sccm)/O2 (6 sccm) mixed gas, and the system pressure was maintained at ~1 Torr. The total growth process lasts usually about 50 mins.

Deposition of Se layer on MoS2 film

Se films were deposited in a home-made tube furnace. High-purity Se powder (99.999%, 29 g) (the evaporation source) was placed in upstream zone (Zone-I, 270 °C) of the tube furnace, while a 2-in. MoS2 wafer (the substrate) was positioned downstream (Zone-II, RT). The deposition duration is ~40 min, with the chamber pressure is maintained at ~1 Torr. The thickness of the Se layer used in the transfer process is typically around 500 nm. The photographs of as-prepared wafer scale MoS2 film and that after deposition of Se film are shown in Supplementary Fig. 2, respectively.

Se-mediated transfer process

The high uniformity of Se film is firstly deposited onto MoS2 wafer. Then, a 5 wt% PPC solution is spin-coated as a buffer layer on the Se/MoS2/sapphire substrate at 6000 rpm for 60 s and baked at 50 °C to evaporate the solvent. The PPC/Se/MoS2 stack is mechanically peeled off from the sapphire substrate by using hydrosol adhesive tape and transferred onto a target 3-in. substrate with a 20 nm Al2O3 dielectric layer. In the plying-up process of hydrosol adhesive tape to the surface of the PPC/Se/MoS2 stack, it is important to ensure that no bubbles are trapped between the hydrosol adhesive tape and PPC/Se/MoS2 stack. Before removing the hydrosol tape by soaking in deionized water, necessary pressure is required to ensure a close contact between the hydrosol tape/PPC/Se/MoS2 stack and the target substrate with the assistance from an idler wheel. This step minimizes the risk of water infiltration at the edges. After removing the hydrosol tape, the sample should be carefully fished out and air-dried instead of using a nitrogen gun or other tool, which helps prevent wrinkles or breakage for transferred MoS2 film. Subsequently, the PPC layer is stripped by RIE. Notably, this process does not affect the chemical properties of underlying Se layer or MoS2 due to the Se layer is thick enough, as shown the cross-section of TEM image in Supplementary Fig. 2c. Finally, the Se sacrificial layer is fully removed by a thermal evaporation at 280 oC for 5 h in N2 atmosphere. For comparison, MoS2 films are also transferred using the PMMA-assisted method. The 2-in. wafer of 2D MoS2 monolayer on sapphire is first etched in KOH solution, then transferred to a 3-in. substrate with PMMA as a support layer. The PMMA is then removed by acetone.

Device fabrication

The gate electrodes are firstly patterned on SiO2/Si substrates using UV lithography (MA6, Karl Süss), e-beam evaporation of Ti/Au/Ti (3/8/3 nm), and lifting-off process. Next, a 20-nm Al2O3 dielectric layer is grown on the pre-fabricated metal gates using atomic layer deposition at 300 °C. To establish a cascade connection between the lower- and upper-level metal electrodes, rectangular windows are patterned in the Al2O3 layer at designated locations by UV lithography, followed by etching with RIE. The 2D MoS2 film is then transferred onto the metal gates using the Se-assisted transfer method. Subsequently, an Au/Ti/Au (5/3/35 nm) metal layer is deposited by electron beam evaporation for contact electrodes. Finally, the MoS2 channels are defined by UV lithography and RIE (Plasma Lab 80 Plus, Oxford Instruments).

Material and device performance

The as-transferred 2D MoS2 film is characterized using AFM (Asylum Research Cypher S) and aberration-corrected TEM (Spectra 300). Raman spectra are obtained with a confocal Raman imaging system (Horiba/LabRam HR-Evolution). XPS (Thermo Fisher ESCALAB XI+) is employed to determine the valence states and elemental composition. Electrical performance measurements are conducted using a probe station (Janis ST-500-1-4CX) equipped with a semiconductor analyzer (Agilent B1500A) and an oscilloscope (Agilent DSOX3054A).

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

References

Kim, K. S. et al. The future of two-dimensional semiconductors beyond Moore’s law. Nat. Nanotechnol. 19, 895–906 (2024).

Yin, L. et al. Two-dimensional semiconductors and transistors for future integrated circuits. ACS Nano 18, 7739–7768 (2024).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Dodda, A. et al. Active pixel sensor matrix based on monolayer MoS2 phototransistor array. Nat. Mater. 21, 1379–1387 (2022).

Zhu, Y. et al. Non-volatile 2D MoS2/black phosphorus heterojunction photodiodes in the near- to mid-infrared region. Nat. Commun. 15, 6015 (2024).

Li, L. et al. Epitaxy of wafer-scale single-crystal MoS2 monolayer via buffer layer control. Nat. Commun 15, 1825 (2024).

Yu, H. et al. Eight In. Wafer-scale epitaxial monolayer MoS2. Adv. Mater. 36, 2402855 (2024).

Xue, G. et al. Modularized batch production of 12-inch transition metal dichalcogenides by local element supply. Sci. Bull. 68, 1514–1521 (2023).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Hu, J. et al. Chemical vapor deposition syntheses of wafer-scale 2D transition metal dichalcogenide films toward next-generation integrated circuits related applications. Adv. Funct. Mater. 33, 2303520 (2023).

Liu, C. et al. Understanding epitaxial growth of two-dimensional materials and their homostructures. Nat. Nanotechnol. 19, 907–918 (2024).

Xu, X. et al. Growth of 2D materials at the wafer scale. Adv. Mater. 34, 2108258 (2022).

Zhao, T. et al. Substrate engineering for wafer-scale two-dimensional material growth: strategies, mechanisms, and perspectives. Chem. Soc. Rev. 52, 1650–1671 (2023).

Watson, A. J., Lu, W., Guimarães, M. H. D. & Stöhr, M. Transfer of large-scale two-dimensional semiconductors: challenges and developments. 2D Mater. 8, 032001 (2021).

Sheng, C. et al. Two-dimensional semiconductors: from device processing to circuit Integration. Adv. Funct. Mater. 33, 2304778 (2023).

Ning, H. et al. From lab to fab: path forward for 2D material electronics. Sci. Chin. Inform. Sci. 66, 160411–160411 (2023).

Lin, Y. C. et al. Graphene annealing: how clean can it be? Nano Lett. 12, 414–419 (2012).

Pham, P. V. et al. Transfer of 2D films: from imperfection to perfection. Acs Nano 18, 14841–14876 (2024).

Schranghamer, T. F., Sharma, M., Singh, R. & Das, S. Review and comparison of layer transfer methods for two-dimensional materials for emerging applications. Chem. Soc. Rev. 50, 11032–11054 (2021).

Liu, H., Zhao, J. & Ly, T. H. Clean transfer of two-dimensional materials: a comprehensive review. ACS Nano 18, 11573–11597 (2024).

Liao, M. et al. Precise control of the interlayer twist angle in large scale MoS2 homostructures. Nat. Commun. 11, 2153 (2020).

Kang, K. et al. Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures. Nature 550, 229–233 (2017).

Zhao, Y. et al. Large-area transfer of two-dimensional materials free of cracks, contamination and wrinkles via controllable conformal contact. Nat. Commun. 13, 4409 (2022).

Gao, X. et al. Integrated wafer-scale ultra-flat graphene by gradient surface energy modulation. Nat. Commun. 13, 5410 (2022).

Shen, Y. C. et al. Design of versatile top-down transfer by thermal release tape/poly(methyl methacrylate) (TRT/PMMA) bi-Supporting layers toward all-transfer transition metal dichalcogenide material based transistor arrays. Small Sci. 4, 2300144 (2024).

Hong, N. et al. Roll-to-roll dry transfer of large-scale graphene. Adv. Mater. 34, 2106615 (2022).

Quellmalz, A. et al. Large-area integration of two-dimensional materials and their heterostructures by wafer bonding. Nat. Commun. 12, 917 (2021).

Nakatani, M. et al. Ready-to-transfer two-dimensional materials using tunable adhesive force tapes. Nat. Electron. 7, 119–130 (2024).

Wang, Z. et al. Cyclododecane-based high-intactness and clean transfer method for fabricating suspended two-dimensional materials. Nat. Commun. 15, 6957 (2024).

Satterthwaite, P. F. et al. Van der Waals device integration beyond the limits of van der Waals forces using adhesive matrix transfer. Nat. Electron. 7, 17–28 (2024).

Wang, W. et al. Clean assembly of van der Waals heterostructures using silicon nitride membranes. Nat. Electron. 6, 981–990 (2023).

Ding, S. et al. Ag-assisted dry exfoliation of large-scale and continuous 2D monolayers. ACS Nano 18, 1195–1203 (2024).

Zhang, J. et al. Clean transfer of large graphene single crystals for high-intactness suspended membranes and liquid cells. Adv. Mater. 29, 1700639 (2017).

Shim, J. et al. Controlled crack propagation for atomic precision handling of wafer-scale two-dimensional materials. Science 362, 665–670 (2018).

Kim, H. et al. High-throughput manufacturing of epitaxial membranes from a single wafer by 2D materials-based layer transfer process. Nat. Nanotechnol. 18, 464–470 (2023).

Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Kong, L. et al. Wafer-scale and universal van der Waals metal semiconductor contact. Nat. Commun. 14, 1014 (2023).

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS Nano 11, 12001–12007 (2017).

Acknowledgements

This project was supported by the National Key Research and Development Program (Grant No. 2021YFA1202904 (G.Z.)), the National Science Foundation of China (NSFC, Grant Nos. 62405205 (X.Z.), 62488201 (G.Z.), and 62204166 (N.L.)), the Guangdong Major Project of Basic and Applied Basic Research (Grant No. 2021B0301030002 (G.Z.)), the China National Postdoctoral Program for Innovative Talents (Grant No. BX20230251 (X.Z.)).

Author information

Authors and Affiliations

Contributions

G.Z. and N.L. co-supervised this work. X.Z. performed the device fabrications and performance characterizations with the help from T.L., J.Z., and J.L. L. Z., H.Y., S.W., H.D., L.H. and Y.Z. performed the growth of 2-in. wafer scaled monolayer MoS2 film and Se film. X.Z., N.L., P. C. and H.Y. analyzed data. X.Z., N.L. and G.Z. wrote the manuscript. All authors commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Quanyang Tao, Hualing Zeng, and the other, anonymous, reviewer for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Zhang, X., Zhou, L., Wang, S. et al. Se-mediated dry transfer of wafer-scale 2D semiconductors for advanced electronics. Nat Commun 16, 4468 (2025). https://doi.org/10.1038/s41467-025-59803-1

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-59803-1

This article is cited by

-

11-bit two-dimensional floating-gate memories

Nature Communications (2025)

-

Electrostatic-based transfer keeps 2D materials ultra-clean

Nature (2025)