Abstract

Signal transmission across cryogenic and room-temperature environments remains a significant bottleneck in superconducting quantum computing and classical circuit integration. Furthermore, interactions among cryogenic devices often require room-temperature interfacing, driving substantial demand for data read/write interfaces, which in turn increases interconnect complexity and constrains scalability. In situ fabrication of cryogenic, high-performance logic circuits and devices presents a promising solution to address this “wiring bottleneck”. Here, we demonstrated interfacial two-dimensional electron gas devices with reversible interface states that can be directly modulated at operating temperatures while achieving an unprecedented ultrahigh on/off ratio. Remarkably, these devices can be patterned using a “light pencil” and erased with a pulsed electric field, enabling resist free, in situ direct writing and electrical erasure of the interface state.

Similar content being viewed by others

Introduction

Cryogenic circuits and devices are essential to advancing understanding of superconducting mechanisms1,2, spintronics3,4, and the development of scalable superconducting quantum computers5,6. However, their interconnections and control typically depend on room-temperature interfaces, which introduce unavoidable challenges such as noise and thermal conduction7,8,9. As the number of cryogenic devices continues to grow, the “wiring bottleneck” has emerged as a critical barrier to scalability8,10,11. Addressing this limitation requires innovative strategies, with one of the most promising being the in situ, repeatable fabrication of high-performance cryogenic logic circuits and devices, including field-effect transistors (FETs)12,13. In parallel, field-induced metal-insulator transitions (MIT) offer an intriguing route for the in situ realization of such devices. However, existing approaches for reversible MIT, such as those using conductive atomic force probes1,14 based on the “water cycle” mechanism15, electric field induced hydrogenation16, and hydrogen ion liquid gating technique17, are largely confined to room temperature. The complexity and scalability challenges associated with these techniques further limit their applicability in large-scale device fabrication. While X-ray irradiation has been shown to induce MIT under cryogenic conditions, reversing the transition necessitates thermal annealing18, which not only risks damaging other delicate cryogenic chips but also incurs prohibitive costs, further limiting its practical applicability. Consequently, there is a pressing need to develop a simpler, more cost-effective approach for the repeatable and in situ fabrication of cryogenic logic circuits and devices.

Our study aims to develop a low-cost method for reconfigurable, in situ direct-writing of low-power logic circuits and devices at the interface under cryogenic conditions, without photoresist. Over the past two decades, the correlated two-dimensional electron gas (C-2DEG) generated at the interface between two insulating oxides19, LaAlO3 (LAO) and SrTiO3 (STO), has garnered widespread attention. This interface exhibits plentiful physical phenomena, including superconductivity20,21, magnetism22,23, Rashba spin-orbit coupling24, and quantum oscillations25,26,27. Furthermore, the C-2DEG interface can be well controlled through various means, such as optical28, electric29, and magnetic fields30, and possesses excellent chemical stability31, interference resistance, and high mobility19, making it an ideal platform for developing oxide functional devices14,32,33. The metallic nature of this interface eliminates high Schottky barriers, facilitating near-perfect ohmic contact between the channel and electrodes. Additionally, the single crystal STO substrate boasts an extremely high relative dielectric constant (κ ~ 20,000)1,34, remaining above 3000 even in an electric field of 5 kV/cm35,36. Numerous studies have demonstrated that a high quality single crystal STO film can be integrated on a single-crystal silicon surface37,38, positioning it as one of the ideal candidates for the next generation of cryogenic, low-power oxide functional devices integrated on silicon39. However, the excessively high interface carrier concentration poses challenges in controlling the electric field over the C-2DEG, because C-2DEG interfaces beyond the critical thickness are very conductive and, under normal circumstances, cannot be non-volatilely transformed into an insulating state. Therefore, discovering a non-volatile method to deplete interface carriers is essential for high performance cryogenic devices.

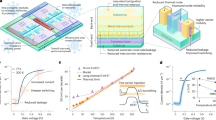

In this study, we present a heterostructure of LaFeO3 (LFO) delta-doped at LAO/STO interfaces to reduce the carrier concentration of the C-2DEG (see Fig. 1a). Using two straightforward examples, we demonstrate in situ construction of two types of cryogenic devices. The first one is a cryogenic FET with ohmic contacts controlled by a back-gate, where the C-2DEG channel is primarily concentrated at the interface to the substrate side, with the thickness as thin as 1 nm or even a mono layer40. This cryogenic FET exhibits a high carrier mobility of up to 2300 cm2V−1s−1, an ultra-low off-state current (Ioff) around 10⁻12 A, a remarkably low supply voltage (VDS) of 5 mV enabled by barrier-free contacts, a high on/off current ratio (Ion/Ioff) approaching 10⁹, and excellent electrical durability and performance, on par with the most advanced cryogenic FETs reported to date41. The second one is a laser direct-writing technology where a laser can produce localized conductive pathways. Furthermore, these pathways are reversible and can be erased using a pulsed back-gate voltage, allowing the conductive pattern to be redefined. This approach, leveraging a “light pencil” for writing and an “electric field eraser” for resetting, provides a versatile and repeatable method for in situ fabricating reversible cryogenic circuits and devices.

a A schematic of optical-electric C-2DEG field-effect transistor. b Two-wire method and Van der Pauw method were employed to measure the resistance-temperature curves of the C-2DEG interface, respectively. c Pulsed back-gate voltages ranging from 100 to 210 V with a pulse width of 1 ms were applied to achieve different resistance states of the C-2DEG interface under VDS = 0.5 V. d The ID-VDS curve of normal-off interface exhibits an onset voltage of approximately 2.6 V. The illustration indicates that the interface experiences breakdown at a VDS of around 40 V.

Results

Back-gate induced metal-insulator transition: fabrication of normally-off channels

The resistance-temperature (R-T) curve serves a clear method for assessing the conductive behavior of the C-2DEG interface. As shown in Fig. 1b, measurements were performed using the two-wire method and the Van der Pauw method respectively. Since the Van der Pauw method can eliminate the contribution of contact resistance42, the measured resistance is solely contributed by the C-2DEG interface. The R-T curve confirms that the C-2DEG interface exhibits metallic behavior. Its carrier concentration extracted from the Hall effect is approximately 1.93 × 1013 cm−2, and the calculated mobility exceeds 2300 cm2V-1s-1 at 2 K. In contrast, the resistance measured from the two-wire method is a sum of the interface C-2DEG and contact resistances. Interestingly, the R-T curve from the two-wire method exhibits similar behavior to that from the Van der Pauw method. This fact indicates a typical metallic ohmic contact between the metal electrodes and C-2DEG surface. Simultaneously, the Current-Voltage (I-V) characteristics of both methods at 2 K are linear and exhibit no threshold voltage (see Fig. S1), indicating the successful achievement of a barrier-free metal-channel contact.

According to our previous work43, this system undergoes a non-volatile transition from normal-on to normal-off state (i.e., MIT) at 2 K after applying a pulsed back-gate voltage of 210 V. With a VDS = 0.5 V, Fig. 1c shows the variations in interface resistance resulting from the non-volatile MIT induced by 1 ms pulses VBG of 100 V, 150 V, 175 V, and 210 V, respectively. For the case of VBG = 210 V, the resistance exceeds the measurement limit of 1010 Ohms, so the Ion/Ioff ratio will be greater than 108, indicating that the channel is cut off at this point. To prove that the switching can be faster, we developed a homemade pulse generator to apply 50 μs pulses of gate voltage and observed comparable switching behavior, as shown in Fig. S2a. To further estimate the gate response time, we adopt the conventional RC charging–discharging framework. Within this model, the characteristic timescale for a full cycle is approximately given by 2 × 5 ReffC, where Reff is the effective series resistance. For our cryogenic FET, this model implies a theoretical temporal resolution of 2 × 5 ReffC, which is directly determined by the gate capacitance and thus depends on gate area and dielectric thickness. With our current gate design (area: 25 mm2, thickness: 0.5 mm), resolution can be expressed as 10Reff εS/d, yielding a value of ~4 μs under our current device geometry. If the gate dimensions are scaled down to match those used in advanced CMOS technologies (a gate area of 150 nm2 and a thickness of 12 nm) the theoretical time resolution could be reduced to ~1 ps. This straightforward method for modulating the MIT at the C-2DEG interface via a back-gate in cryogenic conditions presents a promising avenue for the advancement of cryogenic electronics. Furthermore, Fig. 1d shows the I-V characteristics when the channel is completely cut off (VBG = 0). Drain-source breakdown voltages (VDSS, according to ID ≥ 10−10 A) is approximately 2.6 V, followed by a linear ohmic region (2.6–7 V). As VDS increases further, the channel undergoes avalanche breakdown at VDS ≥ 40 V. This value is significantly higher than the VDSS, indicating that the channel demonstrates exceptional stability.

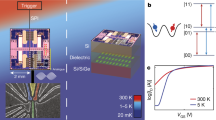

Parallel-plate capacitor series model

Our prior research proposed a plausible model to elucidate the non-volatile MIT43. At lower temperatures, the majority of gases solidify and deposit as a layer on the surface of the thin film. Under these conditions, the environmental pressure is minimal, and a strong electric field, induced by a 210 V back-gate voltage, penetrates the sparse gaseous medium, facilitating the generation of electrons. In the presence of this electric field, electrons adhere to the solidified gas layer (referred to as the gas ice layer) on the thin film surface. This system can be approximated as two parallel-plate capacitors arranged in series (see Fig. 2). In this configuration, the upper parallel-plate capacitor consists of the charged gas ice layer and the C-2DEG interface, with the epitaxial thin films as thin as 6 nm acting as the dielectric layer. The lower parallel-plate capacitor comprises the C-2DEG interface and the bottom electrode, with the STO substrate serving as the dielectric medium. Upon removal of the back-gate voltage, the C-2DEG interface induces positive charges corresponding to the number of electrons in the gas ice layer, depleting the interface carriers.

a, b The C-2DEG interface is conductive in the pristine state. c, d When VBG is applied, the C-2DEG interface induces more carriers. At the same time, the strong electric field ionizes the gas molecules under low gas pressure, and the charges are attracted to the surface of the gas ice layer by the electric field. e, f When the VBG is turned off, charges are absorbed in the insulating gas ice layer, but the bottom electrode is no longer charged. Therefore, positive charges are induced at the C-2DEG interface to neutralize the carriers, and the interface becomes an insulating state. g, h When VBG is applied again, carriers are induced at the C-2DEG interface and the interface is switched to conductive state.

To further substantiate the validity of this model, Fig. 1c demonstrates that varying the back-gate voltage results in distinct resistance states at the interface. Using the previously determined dielectric constant of the single-crystal STO substrate43, we calculated the charge density in the gas ice layer under different back-gate voltages. Assuming that the carrier mobility at the C-2DEG interface remains constant before and after charging the gas ice layer, we computed theoretical resistance values (see Table S1). Notably, these theoretical resistance values exhibit excellent agreement with the experimentally measured values, further corroborating the accuracy of the series-connected parallel-plate capacitor model. Furthermore, reapplying the back-gate voltage again results in the bottom electrode acquiring positive charges, which in turn induces electrons at the C-2DEG interface. Leveraging this principle, we can construct a single cryogenic FET cell based on the described mechanism.

Cryogenic FET with ultra-high on/off ratio

Figure 3b presents a comparative analysis of transfer characteristics (ID-VBG) under various VDS at 2 K. Remarkably, the channel can be efficiently driven with a minimal VDS of 0.5 mV, which is two orders of magnitude smaller than traditional 2D FETs44,45,46, while boasting an Ion/Ioff ratio beyond 105. Therefore, it can be foreseen that such a small VDS can reduce power consumption by approximately four orders of magnitude. As VDS gradually increases from 1 mV to 1 V, the channel maintains a low Ioff (~ 10-12 A), with occasional discontinuities attributed to exceeding the electronic measurement range. With the rise in VDS, the VBG-on significantly decreases from 70.5 V to 55.5 V, and for VDS ≥ 500 mV, the Ion/Ioff ratio is close to 109. Cyclic characteristics reveal that the leakage current after channel closure is less than 1 nA, and the VBG-off is less than the VBG-on but greater than 0, signifying that channel closure does not necessitate applying a negative VBG.

a Conceptual diagram of constructing cryogenic FET array. b The ID-VBG cyclic curve spanning a supply voltage range from 1 mV to 1000 mV. The VBG-on and VBG-off decrease significantly as VBG increases. c Comparison of ID-VBG curves of samples with substrate thicknesses of 0.2 mm and 0.5 mm respectively. VBG-on was significantly reduced from 70.5 V to 17 V due to the reduction of STO gate thickness under VDS = 50 mV. d Different VBG (from 30 V to 210 V) inject carriers to produce different conductive states under VDS = 0.5 V. e ID-VDS characteristics of C-2DEG interface under different VBG (from 5 V to 210 V). f Ion/Ioff ratio as a function with different VDS (from 0.5 mV to 500 mV). g VBG-on as a function with different VDS (from 0.5 mV to 500 mV). h Ion/Ioff ratio versus VDS in C-2DEG FET compared to other FETs with typical semiconductor channel materials. The orange dashed line represents the expected fit as reported in the ref. 41.

However, the application of VBG exceeding 50 V presents a challenge in application. Consequently, we addressed this challenge by mechanically thinning the STO substrate thickness from 0.5 mm to 0.2 mm (see Fig. S4). Furthermore, Fig. 3c compares the transmission characteristics of the FET at 2 K with STO thicknesses of 0.5 mm and 0.2 mm. Notably, at a VDS of 50 mV, the turn-on voltage significantly decreases from 70.5 V to 17 V, while the Ion/Ioff ratio remains relatively unchanged, indicating potential for practical application scenarios. However, to ensure that the power supply voltage can effectively drive the subsequent gate stage, it is necessary to reduce the thickness of the STO gate layer to approximately 14 nm in order to achieve millivolt-level operation. This dimensional scaling could be realized through water-assisted transfer of freestanding membranes or by growing high-quality ultrathin STO films via molecular beam epitaxy47,48. Such an approach would lower VBG–on to around 4.7 mV and is expected to result in a steeper inverse subthreshold slope.

To intuitively assess the response speed and stability of resistance switching, a wider VBG pulse was applied to the sample with an STO thickness of 0.2 mm, using a VDS of 0.5 V (see Fig. 3d). At this juncture, a VBG of only 30 V can lead to an Ion/Ioff ratio exceeding 107, and the response time of the MIT is lower than 1 ms. Here, 1 ms is our digital measurement lower limit. As VBG gradually increases, the Ion/Ioff ratio also significantly increases. The metallic-state resistance exhibits a slow relaxation after maintaining a high VBG for ~1 min, due to the reduced κ value of the STO substrate under strong electric fields. In fact, this change is too weak to affect the normal operation of the FET, and 1 min far exceeds practical device operation times. Moreover, our FET works very well without breakdown under a continuous VBG of 210 V for 5 min, further confirming the stability of the C-2DEG interface.

Furthermore, Fig. 3e depicts the typical output curve of the FET with an STO thickness of 0.2 mm when temperatures as low as 2 K. A linear ohmic I-V relationship is observed at VBG = 20 V, and when VBG < 20 V, the I-V characteristics of channel closure, similar to Fig. 1d, are exhibited in Fig. S6. As VBG gradually increases, the saturation leakage current rises, and the variable resistance region gradually narrows, exhibiting typical N-type channel enhancement FET output characteristics. In addition, A negative resistance effect is observed at very high VDS (above 7.5 V). At such high electric fields, the probability of carrier collisions increases significantly, and carriers may also be captured by local traps, leading to a decrease in IDS. However, when VBG exceeds 150 V, the carrier concentration induced by the back-gate surpasses the initial concentration, resulting in a transition to an N-depletion-type FET49. Consequently, FET achieved from VBG = 210 V exhibits a larger saturation leakage current and a wider variable resistance region.

Temperature stability stands as a critical parameter for evaluating device performance. Despite our field-effect transistor can be operated with a drain–source voltage as low as 0.5 mV, as previously demonstrated, prolonged continuous operation will induce non-negligible Joule heating. To underscore the influence of temperature on the turn-on voltage, we conducted temperature-dependent tests on the sample with STO substrate thicknesses of 0.5 mm within the 2–50 K range. Figure 3f, g (Extracted from Fig. S3) delineates the relationship between Ion/Ioff ratio, VBG-on, and temperature under different VDS drives. Visually discernible from the Fig. S3 is the fact that the reduction in Ion/Ioff ratio primarily stems from the increase in off-state current as the temperature rises. However, at the ultra-low VDS of 0.5 mV, the Ion/Ioff ratio remains almost unchanged and maintains a high level of 105 when the temperature rises to 30 K. This indicates that even if Joule heating causes the FET temperature to rise by 30 K, its performance is scarcely affected. Subsequently, with warming to 50 K, all Ion/Ioff ratios decrease to approximately 100. Nevertheless, the VBG-on is notably affected by temperature, dropping to around 20 V at 10 K and further diminishing to 0.

Figure 3h compares our FET alongside and some typical 2D semiconductor channel materials including α-In2Se350, Graphene51, MoS2–hBN41, hBN–graphene–hBN52, Cr2Ge2Te653 and GaAsSb54. This analysis focuses on Ion/Ioff ratio and supply voltage at cryogenic environment. Evidently, the supply voltage exerts a significant impact on the Ion/Ioff ratio, exhibiting a decrease as the supply voltage diminishes. Our FET, crafted through a simpler fabrication method, attains an Ion/Ioff ratio comparable to the most promising cryogenic FETs reported to date, particularly at lower temperatures. Remarkably, at the lowest VDS ~ 0.5 mV, the Ion/Ioff ratio reaches an impressive 105, a value surpassing the performance of most FETs operating at higher supply voltages. Consequently, the C-2DEG interface can be acknowledged as the one of the most energy-efficient cryogenic 2D channel available.

Based on the schematic diagram in Fig. 2, we observe that, owing to the insulating state of the gas ice layer, the upper layer, resembling a parallel-plate capacitor, will not discharge as long as the adsorbed charge reaches saturation and the temperature remains constant. Consequently, the energy required for writing and reading one bit in a C-2DEG FET logic unit is respectively determined by the energy consumed for charging the lower parallel plate capacitor by the external gate voltage, denoted as EPPC, and the Joule heating, denoted as EOMH, generated by driving the internal C-2DEG and the contact resistance of the metal state55:

Here, \({\varepsilon }_{r}\) represents the relative dielectric constant,\(\,{\varepsilon }_{0}\) is the vacuum permittivity, \({E}_{{BG}}\) is the back gate electric field strength, S is the area of the STO gate, d is the thickness of the STO gate, t is the pulse width, and \({R}_{{OHM}}\) is the sum of the C-2DEG interface resistance and contact resistance.

However, it is worth noting that the interface resistance of the C-2DEG,denoted as \({R}_{{{{\rm{C}}}}-2{{{\rm{DEG}}}}}={{{{\rm{\rho }}}}}_{S}\frac{W}{L}\), where \({\rho }_{S}\) is surface resistivity, W represents the channel width and L denotes the channel length. Thus, its numerical value solely depends on the ratio of channel width to length, independent on the actual channel area. Consequently, if the channel is proportionally scaled down to the nanometer level, its RC-2DEG remains unchanged, implying constant reading power consumption EOHM. Presently, we have achieved a VDS of ~0.5 mV, and the energy required for reading 1-bit of computation will be below 10-18 J for a pulse width t of 1 ns, which is six orders of magnitude lower than traditional 2D FETs (~pJ/bit)52.

It is evident that the EPPC is directly proportional to the volume of the STO gate. However, with the present large gate dimensions, the EPPC reaches a significant value of 10−11 J/bit, and other performance parameters, such as the inverse subthreshold slope, of the FET are not directly comparable to those of advanced nanoscale-gate FETs56. Future efforts could employ self-supporting techniques to reduce gate thickness to the micrometer scale and apply patterning to minimize gate area (see Fig. 2a), potentially lowering the EPPC well below the EOHM. Furthermore, as shown in Fig. S7, the gate leakage current for the 0.2 mm-thick gate remains negligible near the VBG-on, with a typical value around 10−11 A. This fact indicates that the power dissipation associated with gate leakage is negligible. Nevertheless, an alternative ultra-low-power method for channel activation is still needed given the current size of gate layer.

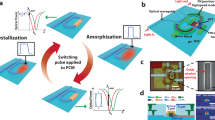

Optical pencil & electric eraser: reversible in situ laser direct-writing

Previous discussions revealed that carrier depletion in the C-2DEG interface arises from charge accumulation within the gas ice layer. Developing a low-power approach to remove this charge could locally restore the conductivity of channels. Photonic devices, known for their ultra-low power requirements, represent a promising solution. To evaluate this potential, we constructed a tunable light source covering wavelengths from 200 to 1100 nm using a xenon lamp coupled with a monochromator, directing the output into cryogenic environments via an optical fiber.

A typical Hall bar pattern was defined over a 1 × 1 mm2 region on the sample surface using a mask (Fig. 4a). As shown in Fig. 4b, an initial pulsed back-gate voltage of 210 V was applied in darkness, inducing the MIT. Subsequently, the Hall bar region was exposed to infrared light (wavelength λ of 900 nm) and ultraviolet light (λ of 300 nm), both of which triggered a transition from the insulating to the metallic state. Following exposure, the interfacial resistance stabilized in the metallic state, affirming the non-volatile nature of the transition. In the metallic state, the Hall resistance (Rxy) exhibited a linear dependence on the external magnetic field (μ0H, see Fig. 4c), with a carrier concentration of nH = 2.23 × 1013 cm−2 extracted via the Hall effect. This value is in close agreement with the carrier concentration nV = 1.93 × 1013 cm−2, previously measured by the van der Pauw method over a 5 × 5 mm2 region. Additional pulsed back-gate voltage induced the further non-volatile MIT, demonstrating that conductive pathways written via light pencil can be effectively erased by a pulsed electric field.

a Schematic of light exposure on the sample surface with a hall bar patterned mask. The left side is shielded, and the right side forms a Hall bar pattern. b Modulation of the C-2DEG interface state. A 210 V back-gate pulse (1 ms) induces an insulating state, which transitions to a persistent conductive state after exposure to infrared (900 nm, 1.2 s) or ultraviolet light (300 nm, 1.2 s). c Hall resistance as a function of the external magnetic field measured in darkness following Hall bar pattern exposure. d Resistance of the insulating C-2DEG interface as a function of wavelength. Red and blue curves represent measurements for decreasing (1100–200 nm) and increasing (200–1100 nm) wavelengths, respectively. e Light flux (blue) and thermocouple temperature (red) versus wavelength (290–1100 nm). Temperature closely tracks light flux, suggesting thermal effects. f Source-drain current response in shielded and exposed regions. Ultraviolet light causes a localized non-volatile transition in the exposed region, while infrared light induces a gradual conductive transition in shielded areas due to thermal effects. g Conceptual illustration of ultraviolet laser direct-writing for creating conductive pathways. Schematic representations of serial (h) and parallel (i) logic circuit switching between cryogenic devices using “optical pencil” and “electric eraser” technology.

Given that both infrared and ultraviolet light produced comparable modulation of the interfacial resistance within the exposed region, we explored the wavelength dependence of this phenomenon. Figure 4d presents the interfacial resistance response across the infrared, visible, and ultraviolet spectral ranges. A sharp decline in interfacial resistance was observed near 1000 nm, indicating a complete recovery of metallic conductivity. A kink around 360 nm correspondes to the bandgap of the STO substrate (~3.4 eV)19. Notably, cyclic testing revealed that upon returning to a wavelength of 1100 nm, the interfacial resistance did not revert to the insulating state, further substantiating the non-volatile nature of the transition.

The potential contribution of thermal effects associated with laser exposure warranted further investigation. To assess this, temperature variations induced by the laser were measured using a thermocouple (see Fig. 4e). The thermocouple response closely followed the light flux distribution, showing a pronounced increase near 1000 nm, which coincided with the steep decline in interfacial resistance. This finding suggests that thermal effects, arising from laser exposure, promoted evaporation of the gas ice layer, thereby restoring the interfacial metallic state.

In contrast, the ultraviolet light of 300 nm, characterized by a significantly lower light flux, elicited no discernible thermocouple response, indicating a non-thermal mechanism. To verify this, two additional electrodes were introduced in the shaded region adjacent to the Hall bar (see Fig. 4a), enabling a comparative study of electrical transport properties in both shaded and exposed regions. Following the application of a back-gate voltage pulse, both regions exhibited the non-volatile MIT. Under ultraviolet light exposure (λ of 300 nm), only the patterned region transitioned to the metallic state, while the shaded region remained insulating (see Fig. 4f). This localized response confirmed the non-thermal nature of the ultraviolet-induced transition. The metallic state in the exposed region persisted post-exposure, and the transition was reversible through the application of a pulse back-gate voltage, demonstrating repeatability.

Under infrared light (λ of 900 nm), both the patterned and shaded regions transitioned to the metallic state. However, the shaded region required approximately 40 s to fully recover its metallic state, indicative of a thermally driven process. Prolonged infrared exposure caused thermal diffusion, leading to evaporation of the charged gas ice layer in the surrounding areas and gradual restoration of conductivity. These findings highlight that low-flux ultraviolet light enables localized, non-volatile insulator-to-metal transitions with ultra-low switching power, whereas infrared light induces broader, thermally driven transitions. These findings enable laser-based direct-writing of conductive pathways (see Fig. 4g) and erasure via back-gate control, facilitating parallel (see Fig. 4h) and serial (see Fig. 4i) switching of cryogenic devices. As illustrated in Fig. S9, localized erasure can also be achieved by tailoring the geometry of the back-gate electrode. Therefore, this approach offers a scalable platform for in situ, large-scale fabrication of integrated circuits and devices in cryogenic environments, particularly when extended beyond gas ice layer techniques in future studies.

In summary, we demonstrated two in situ fabrication approaches for cryogenic devices based on the C-2DEG interface. First, by using a fully metallic C-2DEG interface as the channel, we successfully eliminated the Schottky barrier at metal-semiconductor contacts, significantly reducing VDS and enabling a FET with low contact resistance and a high Ion/Ioff ratio in cryogenic environments. Additionally, we confirmed that reducing the thickness of the single-crystal STO dielectric layer can significantly lower VBG-on. This finding suggests that, in the future, techniques such as water-assisted transfer of freestanding membranes may allow for downsizing gate dimensions, potentially enabling large-scale, ultra-low-power silicon-integrated FET arrays.

However, with the current gate dimensions, the power consumption required for channel activation remains non-negligible. To address this, we developed an alternative method of channel activation based on low-flux ultraviolet laser excitation, enabling localized activation without affecting the interface states in adjacent regions. This approach introduces a cryogenic, in situ, reversible direct-writing technique. By controlling the laser scanning paths and shapes, this method could facilitate the in situ laser direct-writing fabrication of devices and logic circuits in cryogenic environments in the future.

Methods

Sample growth

LaAlO3/LaFeO3/SrTiO3 samples are epitaxially grown on a (001)-oriented TiO2-terminated SrTiO3 substrate using pulsed laser deposition (PLD, KrF, λ = 248 nm) at 700 °C. The fluence ranges from 1 to 1.5 J/cm2, and deposition frequency is 2 Hz, and the oxygen pressure is maintained between 2 × 10−5 to 1 × 10−4 mbar. 5-u.c. of LFO followed by 10-u.c. of LAO thin films were grown sequentially. The growth was monitored by Reflection High-Energy Electron Diffraction (RHEED). The as grown samples were gradually cooled down to room temperature at a rate of 30 °C/min while maintaining constant oxygen pressure. Ti adhesive layers and Au electrodes were deposited using magnetron sputtering.

Transport measurement

The top electrode penetrates the LAO and LFO films by a wire bonder, creating a connection to the two-dimensional electron gas interface. The sample size constructed in this work was 5 × 5 × 0.5 mm and 5 × 5 × 0.2 mm. Cryogenic environments were obtained through a PPMS setup (Quantum Design DynaCool system). Wires and optical fiber with a diameter of 600 μm were integrated using a home-made multifunction probe. The self-constructed wavelength continuously variable light source system comprises a xenon lamp source (PF300-T8 300 W) and a monochromator (CEAULIGHT CEL-IS151), and current and pulse voltage were read and output by the Keithley digital source meter group (6517A, 2613B, 2450 & 2400). The Hall bar channels defined by the employed shadow mask have a width of approximately 50 μm.

Data availability

The data that support the findings of this study are available from the corresponding author upon request. Source data are provided with this paper.

References

Cheng, G. et al. Electron pairing without superconductivity. Nature 521, 196–199 (2015).

Youssefi, A. et al. A cryogenic electro-optic interconnect for superconducting devices. Nat. Electron. 4, 326–332 (2021).

Alam, S., Hossain, M. S., Srinivasa, S. R. & Aziz, A. Cryogenic memory technologies. Nat. Electron. 6, 185–198 (2023).

Hoffmann, A. & Bader, S. D. Opportunities at the frontiers of spintronics. Phys. Rev. Appl. 4, 047001 (2015).

Stassi, R., Cirio, M. & Nori, F. Scalable quantum computer with superconducting circuits in the ultrastrong coupling regime. npj Quantum Inf. 6, 67 (2020).

Li, L. et al. Heterogeneous integration of spin–photon interfaces with a CMOS platform. Nature 630, 70–76 (2024).

Krinner, S. et al. Engineering cryogenic setups for 100-qubit scale superconducting circuit systems. EPJ Quantum Technol. 6, 2 (2019).

Vandersypen, L. M. K. et al. Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent. npj Quantum Inf. 3, 34 (2017).

Reilly, D. J. Engineering the quantum-classical interface of solid-state qubits. npj Quantum Inf. 1, 15011 (2015).

Pauka, S. J. et al. A cryogenic CMOS chip for generating control signals for multiple qubits. Nat. Electron. 4, 64–70 (2021).

Geck, L., Kruth, A., Bluhm, H., Waasen, S. V. & Heinen, S. Control electronics for semiconductor spin qubits. Quantum Sci. Technol. 5, 015004 (2020).

Genssler, P. R. et al. Cryogenic embedded system to support quantum computing: from 5-nm FinFET to full processor. IEEE Trans. Quantum Eng. 4, 1–11 (2023).

Veldhorst, M., Eenink, H. G. J., Yang, C. H. & Dzurak, A. S. Silicon CMOS architecture for a spin-based quantum computer. Nat. Commun. 8, 1766 (2017).

Cen, C., Thiel, S., Mannhart, J. & Levy, J. Oxide nanoelectronics on demand. Science 323, 1026–1030 (2009).

Bi, F. et al. Water-cycle” mechanism for writing and erasing nanostructures at the LaAlO3/SrTiO3 interface. Appl. Phys. Lett. 97, 173110 (2010).

Li, L. et al. Manipulating the insulator–metal transition through tip-induced hydrogenation. Nat. Mater. 21, 1246–1251 (2022).

Yi, D. et al. Emergent electric field control of phase transformation in oxide superlattices. Nat. Commun. 11, 902 (2020).

Kiryukhin, V. et al. An X-ray-induced insulator–metal transition in a magnetoresistive manganite. Nature 386, 813–815 (1997).

Ohtomo, A. & Hwang, H. Y. A high-mobility electron gas at the LaAlO3/SrTiO3 heterointerface. Nature 427, 423–426 (2004).

Caviglia, A. D. et al. Electric field control of the LaAlO3/SrTiO3 interface ground state. Nature 456, 624–627 (2008).

Reyren, N. et al. Superconducting interfaces between insulating oxides. Science 317, 1196–1199 (2007).

Brinkman, A. et al. Magnetic effects at the interface between non-magnetic oxides. Nat. Mater. 6, 493–496 (2007).

Liu, Y. et al. Tuning Dirac states by strain in the topological insulator Bi2Se3. Nat. Phys. 10, 294–299 (2014).

Ben Shalom, M., Sachs, M., Rakhmilevitch, D., Palevski, A. & Dagan, Y. Tuning spin-orbit coupling and superconductivity at the SrTiO3/LaAlO3 interface: a magnetotransport study. Phys. Rev. Lett. 104, 126802 (2010).

Caviglia, A. D. et al. Two-dimensional quantum oscillations of the conductance at LaAlO3/SrTiO3 interfaces. Phys. Rev. Lett. 105, 236802 (2010).

McCollam, A. et al. Quantum oscillations and subband properties of the two-dimensional electron gas at the LaAlO3/SrTiO3 interface. APL Mater. 2, 022102 (2014).

Rubi, K. et al. Aperiodic quantum oscillations in the two-dimensional electron gas at the LaAlO3/SrTiO3 interface. npj Quantum Mater. 5, 9 (2020).

Cheng, L. et al. Optical manipulation of Rashba spin–orbit coupling at SrTiO3-based oxide interfaces. Nano Lett. 17, 6534–6539 (2017).

Christensen, D. V. et al. Stimulating oxide heterostructures: a review on controlling SrTiO3-based heterointerfaces with external stimuli. Adv. Mater. Interfaces 6, 1900772 (2019).

Park, D. S. et al. The emergence of magnetic ordering at complex oxide interfaces tuned by defects. Nat. Commun. 11, 3650 (2020).

Albina, J. M., Mrovec, M., Meyer, B. & Elsässer, C. Structure, stability, and electronic properties of SrTiO3∕LaAlO3 and SrTiO3∕SrRuO3 interfaces. Phys. Rev. B 76, 165103 (2007).

Cheng, G. et al. Sketched oxide single-electron transistor. Nat. Nanotechnol. 6, 343–347 (2011).

Sheridan, E. et al. Gate-tunable optical nonlinearities and extinction in graphene/LaAlO3/SrTiO3 nanostructures. Nano Lett. 20, 6966–6973 (2020).

Müller, K. A. & Burkard, H. SrTiO3: An intrinsic quantum paraelectric below 4 K. Phys. Rev. B 19, 3593–3602 (1979).

Vendik, O. G., Hollmann, E. K., Kozyrev, A. B. & Prudan, A. M. Ferroelectric tuning of planar and bulk microwave devices. J. Supercond. 12, 325–338 (1999).

Tagantsev, A. K., Sherman, V. O., Astafiev, K. F., Venkatesh, J. & Setter, N. Ferroelectric materials for microwave tunable applications. J. Electroceram. 11, 5–66 (2003).

Park, J. W. et al. Creation of a two-dimensional electron gas at an oxide interface on silicon. Nat. Commun. 1, 94 (2010).

Chen, B. et al. Integration of single oriented oxide superlattices on silicon using various template techniques. ACS Appl. Mater. Interfaces 12, 42925–42932 (2020).

Spreitzer, M. et al. Epitaxial ferroelectric oxides on silicon with perspectives for future device applications. APL Mater. 9, 040701 (2021).

Altfeder, I. et al. Scanning tunneling microscopy of an interfacial two-dimensional electron gas in oxide heterostructures. Phys. Rev. B 93, 115437 (2016).

Mondal, A. et al. Low Ohmic contact resistance and high on/off ratio in transition metal dichalcogenides field-effect transistors via residue-free transfer. Nat. Nanotechnol. 19, 34–43 (2024).

Koon, D. W. & Knickerbocker, C. J. What do you measure when you measure resistivity? Rev. Sci. Instrum. 63, 207–210 (1992).

Hong, Y. et al. A broad-spectrum gas sensor based on correlated two-dimensional electron gas. Nat. Commun. 14, 8496 (2023).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Singh, N. K. & Sahoo, M. Comparative investigation of different doping techniques in TMD tunnel FET for subdeca nanometer technology nodes. J. Electron. Mater. 52, 5327–5336 (2023).

Yang, Z. et al. Epitaxial SrTiO3 films with dielectric constants exceeding 25,000. Proc. Natl. Acad. Sci. USA 119, e2202189119 (2022).

Ji, D. et al. Freestanding crystalline oxide perovskites down to the monolayer limit. Nature 570, 87–90 (2019).

Gimenez, S. P. & Galembeck, E. H. S. in Differentiated Layout Styles for MOSFETs: Electrical Behavior in Harsh Environments (eds Salvador Pinillos Gimenez & Egon Henrique Salerno Galembeck) 41–63 (Springer International Publishing, 2023).

Wan, S., Peng, Q., Wu, Z. & Zhou, Y. Nonvolatile ferroelectric memory with lateral β/α/β In2Se3 heterojunctions. ACS Appl. Mater. Interfaces 14, 25693–25700 (2022).

Xia, F., Farmer, D. B., Lin, Y. -m & Avouris, P. Graphene field-effect transistors with high on/off current ratio and large transport band gap at room temperature. Nano Lett. 10, 715–718 (2010).

Lee, J.-H. et al. Semiconductor-less vertical transistor with ION/IOFF of 106. Nat. Commun. 12, 1000 (2021).

Xing, W. et al. Electric field effect in multilayer Cr2Ge2Te6: a ferromagnetic 2D material. 2D Mater. 4, 024009 (2017).

Convertino, C. et al. A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon. Nat. Electron. 4, 162–170 (2021).

Manipatruni, S. et al. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 565, 35–42 (2019).

Icking, E. et al. Ultrasteep slope cryogenic FETs based on bilayer graphene. Nano Lett. 24, 11454–11461 (2024).

Acknowledgements

This work was partially carried out at the USTC Center for Micro and Nanoscale Research and Fabrication. This work was supported by the CAS Project for Young Scientists in Basic Research (YSBR-100 (Z.L.)), the National Key R&D Program of China (No. 2022YFA1403000 (Z.L.)) and the National Natural Science Foundation of China (Nos. 52272095 (Z.L.) and 11974325 (Z.L.)).

Author information

Authors and Affiliations

Contributions

Z.L. directed the project, supervised sample growth and reviewed the manuscript. Y.H. and L. Wang contributed equally to this work. Y.H. did most of the design and fabrication of the devices, performed the experiments and wrote the manuscript. L. Wang did the mask experiment and contributed to manuscript writing. T.L., L. Wei, S.H., J.L., W.X., L.L., and M.H. contributed to measurements and data analysis. Z.S. contributed to manuscript writing. K.C., Y.G., G.R. and G.K. reviewed the manuscript. All the authors discussed the results and commented on the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Louis Hutin and Yangbo Zhou for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Source data

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Hong, Y., Wang, L., Shen, Z. et al. Cryogenic in situ fabrication of reversible direct write logic circuits and devices. Nat Commun 16, 8606 (2025). https://doi.org/10.1038/s41467-025-63647-0

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-63647-0