Abstract

Efficient data transfer between memory and photonic components is crucial for a wide range of applications. However, this necessity brings forth energy-efficient data movement challenges associated with the memory wall, underscoring the demand for a fast and low-energy electro-optic photonic memory solution. Here, we demonstrate a class of energy-efficient electro-optic devices, namely Pockels photonic memory, that combines low-field switchable ferroelectrics with lithium niobate’s Pockel’s effect. Among such devices, this article will describe in detail the integrated embodiment of a ferroelectric field-effect transistor with lithium niobate on insulator micro ring resonator. We achieve switchable and non-volatile multiple optical memory states (6 states per transistor) with ultra-low energy cost (femto Joule/state), while achieving robust 10 year data retention and read-write endurance exceeding 107 cycles. Furthermore, we demonstrate the possibility of linear memory state stacking. The Pockels photonic memory enables the scaling of reconfigurable photonic systems into the femto Joule/state energy efficiencies.

Similar content being viewed by others

Introduction

With the rapid convergence of Artificial Intelligence (AI), Internet-of-Things, and Broad-band High-Speed Communications, our demand for data-intensive compute, transport, and storage continues to accelerate, reaching 120 zettabytes in 20231. To deal with the growing data and AI model complexity, upcoming AI chips run in excess of 1000 W/chip2. To press against this energy runaway, disruptive ideas of photonic computing3 are on-going attempts to significantly enhance the energy efficiency of the data compute, transport, and storage cycles of electronic architectures. Photonic computing offers advantages, as photons lose less energy in waveguides compared to electrons in wires and its operations require no charging and discharging of interconnect capacitances. However, due to lack of intrinsic memory that stores photons, there is still a need to integrate 3D-stacked high-speed DRAMs (E.g. high-bandwidth memories (HBMs)) to enable photonic compute systems3,4,5,6. This invariably leads to significant energy dissipation in transporting data between photonic and electronic subsystems, called the memory wall. To address this photonic compute-storage locality issue, efforts are underway to enable photonic in-memory computing. The electro-optic photonic memory device is key and fundamental. This would involve the incorporation of memory capability in photonic devices, where electrically encoded memory states can modulate optical properties (e.g. optical transmission). This allows photons engaged in computation to read stored information as they pass through the electro-optic photonic memory, eliminating energy dissipation during data transfer.

There are several promising approaches reported to date. They are based on modulating pass-through photonic signal through attenuation of signal amplitudes or employing electromechanical control. Several groups have successfully shown the use of chalcogenide-based phase change material (PCM), which relies on switchable absorption under amorphous and crystalline phases to modulate propagated light5,7,8. Despite the PCM memory’s proven non-volatility and endurance, it suffers from limitations for gradual reset due to its abrupt “melt-quench” phase change9. In addition to its reliance on joule heating, PCM would thus require higher write energies, more cumbersome signal processing and higher latencies to dynamically adjust analog weights (I.e. gradual long-term depression of synaptic weights) of neuromorphic neural networks, compared to ferroelectric’s stable remanent polarization switching that is capable of fast gradual set and reset10. Similarly, memristor-based memories11 with their filament-based memory elements are also current-driven and thus suffer more readily from ohmic losses, write endurance, and read disturbances as compared to the field-switched ferroelectrics. Moreover, with the use of low-thermal-budget HZO ferroelectrics and IGZO transistors, our process is not only completely CMOS compatible but capable of co-integration with copper interconnects of advanced CMOS chip12, enabling the possibility of Electro-Optic 3D-Integrated Circuits (3D-ICs). For Micro-Electromechanical Systems (MEMS)-based optical memory approaches, they offer the ability to mechanically manipulate nanoscale structures to adjust the drop-through power ratio through light-coupling13. While this approach has garnered significant attention, it suffers from intricate storage and retrieval strategies due to its high sensitivity to environmental conditions.

Promising ferroelectric-based photonic devices (E.g. silicon nitride waveguides14, silicon/barium titanate micro-ring resonator15, silicon nitride Mach–Zehnder interferometer16) have also been reported. However, the energy efficiency of these devices fall short of expectations, due to their need to switch substantial volume of waveguide material (100’s nm thick), which requires significant energy, and weak linear optical effect, plasma-dispersion effect17, on the waveguide and low intrinsic carrier density of waveguide material. Moreover, in anticipation of co-integration of electrical and photonic interconnects in a densely-scaled 3D-ICs and electro-optic interposers (Supplementary Fig. 1), there may be higher susceptibility of electronic cross talk and state disturbances with free-carrier-based electro-optic modulation18.

Here, we overcome these limitations by introducing a class of devices based on the integration of multi-state field-effect electronic memory devices with lithium niobate (LN) optical modulators (Supplementary Fig. 2). The approach leverages low-field switchable ferroelectric electronic memories to couple with the electro-optic properties of LN through the Pockels effect. We utilize silicon CMOS compatible low-thermal budget material (E.g. Zr-doped HfO2 (HZO), Indium Gallium Zinc Oxide (IGZO)) to enable the technology to be compatible with future 3-D monolithic heterogeneous integration on silicon chips and their metal interconnect layers, opening possibilities for dense compute-in-memory optoelectronics.

We have demonstrated both a ferroelectric memory capacitor (FeCAP) and ferroelectric memory transistor (FeFET) version of such devices. We capitalize on the non-linear ferroelectric dipole interactions between HZO and the LN as well as the Pockels effect to augment the birefringence of the micro ring resonator (MRR). These devices become programmable high-quality factor (Q-factor) wavelength selectors. We have previously discussed the details of the HZO memory FeCAP devices19, here we will mostly focus on the description of our FeFET-based Pockels photonic memory (Fig. 1). With the use of a three-terminal FeFET, we are able to read out the ferroelectric memory states through the transistor’s source and drain terminals, while leaving the gate electric field modulating the LN undisturbed. Our FeFET Pockels photonic memory demonstrates ultra-low energy cost of 65.1 fJ/state (100× lower than reported non-volatile photonic memories), the capability of non-volatile switching with over 4-bit states, an anticipated retention period of 10 years, and read-write endurance exceeding a million cycles (107 cycles).

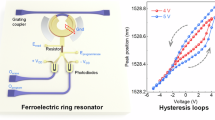

a Schematic illustration of the FeFET Pockels photonic memory realized by integration of FeFET with LNOI MRR. b Ferroelectric polarization switching by electrical signal, causes the optical resonance shift. For instance, to encode the information “0.8,” the dipole polarization in HZO is switched, resulting in an optical resonance shift in the transmission spectrum. In practical applications using a monochromatic laser at wavelength λ, 80% (“0.8”) of the input light would transmit through the MRR. c SEM micrograph in false color of a FeFET Pockels photonic memory. The white represents the straight waveguide and MRR. Source and drain electrodes are depicted in yellow, while top gate (ITO) is depicted in blue. The channel is a ITOx-IGZO bilayer, which are depicted by dark blue. The yellow-red gradient-shaded structure represents HZO ferroelectric layer. d MRR transmission spectra in response to the ferroelectric HZO states. The non-volatile (NV) resonance shifts due to Pockels effect are induced by the stable remnant HZO ferroelectric dipoles.

Results

Device and material structures

In the FeCAP implementation, we had implemented a thin conductive bottom indium tin oxide (ITO) electrode to partially screen and balance the electric field interaction between ferroelectric material and lithium niobate on insulator (LNOI) MRR19 (Supplementary Fig. 3a). Albeit being more complex, the FeFET implementation enables greater tunability through field-effect carrier modulation (electron depletion to strong accumulation), offering stronger and wider Pockels modulation of the MRR. The comparison of FeCAP versus FeFET implementations of Pockels photonic memory is provided in supplementary information. As illustrated in Fig. 1a, a top-gate FeFET fabricated on a LNOI MRR comprises of a metal-ferroelectric HZO gate stack on a heterojunction-engineered Indium-Gallium-Zinc-Oxide (IGZO) oxide semiconductor channel12. The choice of oxide semiconductor FeFET, in contrast to silicon, is motivated by the ultra-low leakage current of the material, low refractive index (nIGZO=1.720 vs. nSi = 3.521), and that the device can be processed under low-thermal budget (Tmax <400oC). This leads to low process and optical interference of the LNOI MRR, as well as process thermal compatibility with CMOS interconnect metallization22,23. The HZO gate stack and transistor channel are engineered for high-reliability and non-volatile memory operation, based on a defect self-compensation effect, with an oxygen-rich semiconducting ITO (ITOx), that passivates the intrinsic IGZO channel interface/bulk defects24. The entire FeFET stack with a bulk conductive ITO top gate electrode is fabricated to minimize light out-coupling optical loss from the waveguide due to their lower refractive index (nIGZO=1.7, nHZO = 1.925, nITO = 1.5), relative to LN (n2 = 2.2) in the C-band infrared region (wavelength range:1530-1565 nm).

The wavelength-dependent resonances of the MRR respond to polarization switching of the HZO (Fig. 1b, d) a phenomenon achieved by biasing the top gate while keeping the source-drain electrodes (Fig. 1a) grounded to 0 Volts. The memory states of the device can also be independently interrogated by the transistor electrical current via the IGZO channel. Figure 1c presents the top-view scanning electron microscope (SEM) image of the FeFET Pockels photonic memory. A window in the SiO2 cladding layer is opened where the FeFET channel directly contacts the LN MRR.

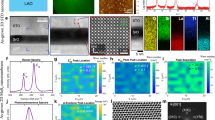

As illustrated in the high-resolution transmission electron microscope (HR-TEM) image (Supplementary Fig. 4), the HZO ferroelectricity is commonly associated with a polar orthorhombic phase (o-phase). The o-phase was found to produce the strongest ferroelectricity in polycrystalline HZO26. Each ferroelectric domain’s polarization aligns along the longitudinal (z) direction of the waveguide. This is accomplished by ensuring the alignment of the electric field through the HZO is z-directed. This alignment is critical, given that z-cut LN demonstrates the strongest Pockels effect at the z-axis (r33 = 32 pm/V) with the highest power efficiency27. Moreover, the interaction between HZO and LN occurs across the body of the ultra-thin IGZO transistor body (8 nm).

Arising from the growth and formation of the films28, the spontaneous ferroelectric polarization (\({{P}_{LN}}^{ \rightharpoonup }\)) in LN has been reported due to the absence of inversion symmetry of the lattice, causing the separation of the positive (Nb+) and negative charges (LiO3-)29. Given that LN exhibits ferroelectricity too, dipole interactions between the HZO and LN are expected. The dipole charge density has been reported to be approximately 70μC/cm2, which is 4.4 times of typical HZO polarizations. Moreover, to support the optical modes, the LN layer of the MRR has to be significantly thicker (TLN = 0.6 μm) than the transistor and the HZO layers as well. Thus, the LN polarization is expected to significantly influence the field-effect operation of the device. Such interactions manifest as electrostatic charge and electric field balance between the dipoles in the HZO and LN, as well as the gate-modulated charges in the transistor. This effect strongly determines how the device operates, program, and erase. We will detail this in the subsequent explanation of the device operation.

Device operations

The polarization of the HZO can be switched by a top electrode (ITO gate) pulse (VG) generating an electric field (Er) exceeding the HZO coercive field (±|Eo | ). The applied field aligns the ferroelectric dipole moment with respect to the field polarity. This resultant ferroelectric dipole translates into a turn-on voltage shift of the transistor channel (threshold voltage Vt). This leads to an accumulation (high conductivity) or depletion (low conductivity) of channel electrons at zero gate voltage, depending on the ferroelectric dipole strength and polarity (Supplementary Fig. 5a). When the applied field falls below the HZO coercive field, the ferroelectric dipoles will remain stable in their previously switched state. The level of electron accumulation in the transistor body, in response to the remnant polarization of the HZO dipoles, determines the amount of electrostatic screening of the HZO dipole charges by these carriers. Consequently, these electrons screen the magnitude of electric field (E-field) penetration into the LN MRR under transistor body; analogous to an “E-Field Filter” (Fig. 2). The resultant E-field exiting from the transistor body will then modulate the refractive index of LN according to the Pockels effect27, leading to a phase shift in the MRR by altering its optical path length difference (OPD). This can be expressed as \({OPD}=2\pi r{n}_{{eff}}=m\lambda\), where r is the radius of the ring resonator, neff is the effective index of refraction of the waveguide material, λ is the resonant wavelength and m is the mode number of the ring resonator30. This corresponds to the resonance shifts as shown in Fig. 1d.

a–c The cross-section illustration of the FeFET Pockels photonic memory during RESET and WRITE operations. The current flowing through the IGZO channel enables non-destructive electrical readout. d–f Band diagrams along the vertical stack of the device in volatile, reset and NV optical states, respectively. The white regions represent the energy gap. In NV optical states, due to the aligned direction of HZO polarization with z-cut lithium niobate spontaneous polarization, the HZO exhibits robust retention of polarization. Since the hole carrier concentration (1014 cm−3)56 and hole mobility (0.01 cm2/Vs)12 are low in the IGZO channel, the device exhibits a sub-pA off-state leakage current. Furthermore, the absence of screening carriers in the channel enables the penetration of the electric field of HZO into LN. The volatile optical state exists only during the RESET operation. After the RESET operation, the spontaneous polarization of lithium niobate tends to reverse the dipoles in HZO, resulting in a blueshift from the volatile optical state to the reset optical state. (E-field electric field, \({{P}_{0}}^{ \rightharpoonup }\): HZO polarization, \({{P}_{s}}^{ \rightharpoonup }\) LN spontaneous polarization, VDS source-drain voltage, VG gate voltage, Er electric field generated by gate voltage, Eo HZO coercive field).

The memory operation of the device involves two key steps (RESET and WRITE) and three device memory states (volatile, reset, and non-volatile state). Prior to performing the WRITE operation to enable the non-volatile memory states, a RESET operation is performed by first applying a positive gate voltage VG bias to produce an electric field exceeding the ferroelectric coercive field of the HZO. This aligns the HZO dipoles in opposition to the LN dipole polarization. The field also induces an accumulation of electrons in the IGZO channel (Fig. 2a, d). The electron accumulation in the transistor not only screens the applied field due to VG, but it also screens the HZO dipoles from the LN dipole fields. The electric field at the LN interface remains directed down-wards (I.e. ELN > 0) and the resultant MRR resonance is at λtemp (Fig. 1d). This memory state is temporary and volatile.

Upon removal of positive VG bias, the electron accumulation in the transistor would diminish, weakening its screening effect. As such, the HZO would depolarize partially (around 1/6 polarization remaining as shown in Supplementary Fig. 6a) due to the competing field from the strong LN dipoles (4.4x polarization of HZO)28, settling the device from volatile optical state into the non-volatile reset optical state (Fig. 2b, e). The electric field at the LN interface switches direction and now directs top-wards (ELN < 0) (Supplementary Fig. 7), this leads to the MRR resonance to move to λ0, according to the Pockels effect (Fig. 1d). This optical state is initial non-volatile state.

The WRITE step involves applying a negative WRITE bias on the gate of FeFET that generates electric field surpassing the coercive field of HZO, polarizing the HZO dipoles. The degree of HZO polarization can be adjusted by controlling the WRITE pulse energy (= \({pulse\; number}\times {\int }_{0}^{{pul}{se\; width}}{pulse\; amplitude}\times {channel\; current}(t)\times {dt}\), where t represents time), thereby achieving the desired ferroelectric domain strengths. The remanent polarizations at V = 0 determine these domain strengths that remain unchanged after the removal of the WRITE pulse (Supplementary Fig. 5b), ensuring the HZO ferroelectric states remain non-volatile and stable (Supplementary Fig. 6b) until a RESET operation is performed. Upon removal of the WRITE pulses, the electric field at the LN interface (ELN) continues to be negative and the magnitude will be determined by the strength of the HZO polarizations (Fig. 2c, f; Supplementary Fig. 8a). This then translates to a blue shift of the MRR resonance with respect to λo. All subsequent nth non-volatile (NV) HZO ferroelectric states produce MRR resonance λn < λo (Fig. 1d). This arises from the field-effect Pockels response of LN to the remnant HZO dipole fields that are directed top-wards (ELN < 0, Supplementary Fig. 8b). The HZO ferroelectric states, and consequently the memorized electro-optic resonances, can also be assessed by measuring the threshold voltage shifts or channel conductivity of the FeFET; allowing for an electronic and photonic bimodal read out. Given that the net HZO polarization aligns with the spontaneous polarization of LN, the HZO polarization is well stabilized, which is important to achieve good state retention times and memory non-volatility. The effective refractive index modulation induced by the HZO dipole field is 1.367 × 10⁻⁹/µm, and the corresponding refractive index change profile (Δn) is provided in Supplementary Fig. 9, assuming the MRR width is fully covered by HZO, only the length is considered, and the ferroelectric material is fully polarized.

Electro-optic memory characterization

To characterize the multi-state performance of the device, the initiated memory state was set to state 0, followed by sequential identical pulses (10 μs, -6 V). As such, six distinct optical states, represented by resonance shifts, can be achieved by applying distinct number of pulses (Fig. 3a). The resonance is determined by fitting the transmission spectra to a Lorentzian distribution31. Compared to the monochromatic method32, this approach provides a more objective assessment, as it is less influenced by MRR parameters such as extinction ratio (ER), quality factor, and the linewidth of the monochromatic source. Statistical distribution of each state was mapped out through 50 repeated measurements. Additionally, these six distinct, stable, and repeatable resonance states exhibit a linear relationship with the number of pulses applied. Additional measurement results using shorter pulses (1 μs, -6 V) are provided in Supplementary Fig. 10. Another critical electro-optic photonic memory parameter is the temporal stability and retention of ferroelectric polarization. To investigate this aspect, we set and monitored three separate states with different writing pulses, as shown in Fig. 3b. Over a period of ~28 h, the optical states remained unchanged, which can be projected to an expected state lifetime of 10 years according to a retention model based on stretched exponential function33. The robust retention can be attributed to the low depolarization-to-coercive field ratio and the low gate leakage in HZO-based FeFETs34.

a Resonance shift as a function of the number of consecutive pulses, each with a width of 10 μs and an amplitude of −6V. The box plots illustrate the variation of each state under a 50 time pulse configuration operation. Ensuring repeatability and non-overlapping resonance states, a total of six distinguishable optical states were identified. b Time dependence of three optical states observed over a period of 105 s after one-time write. The specific pulse configurations applied during this period are represented in the figure. With the observed stability, the expected retention period for these optical states exceeds 10 years33. c The endurance performance of two optical states under specific pulse configurations as indicated. We show the ferroelectric cycling endurance against material fatigue stable over 106 cycles, and a mild shift in the resonance window extending to 107 cycles. The slight reduction in the resonance shift over 106 cycles may be attributed to minor ferroelectric fatigue effects in HZO. d The dependence of the available optical state number on pulse width, frequency, and the number of pulses during operation. The inset provides insight into the variation in operational states when a single pulse is applied. e Pulse sequence and results for measuring the optical and electrical responses after erase and write operations. Specifically, the erase pulse is characterized by 10 μs and 3 V, while the write pulse features 10 μs and −6 V. Continuous measurement of the optical response is conducted using a high-speed photodetector, with signals during pulse operations removed due to the disturbance caused by the grounded channel. The electrical readout pulse is applied with 1 μs and 0.1 V on the drain electrode, with the source electrode grounded. The readout signal is represented by the source-drain current.

It is also well known that ferroelectric materials are susceptible to polarization fatigue in practical applications35. Therefore, we conducted a WRITE/RESET cycling endurance test on our FeFET Pockels photonic memory, and the results are illustrated in Fig. 3c. The WRITE operation employed a negative pulse with varying pulse widths (w), while the RESET operation was accomplished using a long positive pulse. Remarkably, over 107 repeated WRITE/RESET cycles were successfully demonstrated at room temperature with minimal degradation after 105 cycles. Achieving a substantial number of WRITE/RESET cycles exceeding 107 times holds great promise for the reliability of electro-optic photonic memory15.

The HZO polarization modulation is dependent on the total pulse energy (pulse energy ∝ pulse width × amplitude2 × pulse number). To achieve maximum stable intermediate memory states, it is necessary to control the pulse width and pulse frequency (or pulse number) to attain stable remnant HZO polarizations. Too few pulses or too short of a pulse duration may not deliver enough energy to modulate the dipoles. On the other hand, too much switching energy per pulse with long pulse width and/or high pulse frequency leads to excessive change of the polarizations, and a loss of step-wise memory resolution. Hence, there is an optimum choice for pulse width and pulse frequency (Fig. 3d inset). In our case, to achieve 6 stable memory states, we found the optimum programming pulse width to be 10μs at -6 V amplitude. Hence the total WRITE energy per state is estimated to be 65.1 fJ/state. The switching energy per state (Eswitch) and dissipated energy per state (Edissipated) are computed using the following equation14,36,37,38

where n is the pulse number, w is the pulse width, CFE is the gate capacitance, Cmeasure is the parasitic capacitance from measurement setup, Cparasitic is the parasitic capacitance of the device, IGS is the gate leakage current, IDS is the source-drain current, and VDS represents the applied drain voltage while the source is grounded. The equivalent circuit diagram is provided in Supplementary Fig. 11. During the WRITE and RESET operations, both the source and drain are grounded, resulting in IDS ≈ IGS and VDS = 0 V in our calculations. Here, the applied \({V}_{G}\) is -6 V, w is 10 μs, CFE is measured to be 0.25 pF, shunt Cparasitic is measured to be 4.85 pF, series Cmeasure is measured to be 0.7 pF, and IGS is measured to be approximately 5 pA (Supplementary Fig. 12). Consequently, Eswitch is calculated to be 64.8 fJ and Edissipated is estimated by (1) × (10 μs) × (−6 V) × (−5 pA) = 0.3 fJ. Thus, the total WRITE energy per state is 65.1 fJ. The low energy consumption during the WRITE operation, compared to conventional FeFETs, is attributed to the device’s operation in the depletion region, where IGS remains at ~pA level, when a negative VG is applied. In comparison, conventional FeFETs typically operate in the accumulation region, where IGS can reach ~nA level or higher. This lower gate leakage current and higher channel resistance in the depletion region significantly reduces the energy required for WRITE operations. Further details and discussions can be found in the supplementary information. Figure 3d depicts the pulse width versus pulse number optimization to produce the number of stable intermediate states. This will be an important system design consideration when memory data rate, energy dissipation, and parasitic effects are accounted in the context of high-speed computation and communication.

For the time-series memory response, we use a monochromatic light source. The discussion regarding accuracy of result translation from resonance finding method into monochromatic method is provided into the supplementary information. The specific wavelength was chosen to be the minimum of the first derivative of the transmission spectrum, with respect to wavelength, at 1550.972 nm (Supplementary Fig. 13). We expect the transmission shift at this wavelength to be maximized. Figure 3e demonstrates that each optical state can be independently read out, bimodally, through optical power and the FeFET source-drain current. The optical state was initialized with a 10μs pulse at 3 V amplitude. Following the WRITE of the FeFET with a 10μs pulse at -6 V amplitude, the memory state transitioned from state 0 to state 1, as measured by a high-speed photodetector. Moreover, a 1μs pulse at 0.1 V was applied to the source-drain pair, generating a readout current to display the corresponding memory state. During the WRITE or RESET of the FeFET, the source-drain pair is grounded, and subsequently, the readout of the high-speed photodetector is not accurate due to the screening effect of the ground on the HZO electric field. Thus, when the VG bias is applied (Fig. 3e, VG versus time), the corresponding photodetector signal is eliminated (Fig. 3e, power versus time).

Memory state, device stacking, and benchmarking

Due to the linearity of the ferroelectric states with respect to the E-field and the maximum resonance shift according to the coverage area of HZO on MRR (Fig. 4a), it is possible to stack the ferroelectric memory states to increase the Pockels photonic memory capacity. This can be achieved by stacking multiple FeFETs across a single MRR. The MRR would function as an E-field aggregator of FeFET ferroelectric states. Figure 4b describes an example of how the Pockels photonic memory can be independently controlled by three FeFETs sharing a single MRR. Each FeFET has a separate source electrode and top gate electrode but shares the same drain electrode. In this case, the total number of addressable photonic memory states expands to 16 (Fig. 4c). This improvement is attributed to the reduced optical state variation due to the smaller number of HZO grains per FeFET34, even when the coverage area remains the same.

a Maximum resonance shift as function of coverage, where coverage is defined by the angle of covering of the MRR divided by 360°. The coverage cannot reach 100% due to the protective coupling region of the MRR, which should not be covered by other materials. b SEM micrograph in false color of a FeFET Pockels photonic memory controlled by three independent FeFETs, i.e. FeFET-1, FeFET-2, and FeFET-3. The white represents the straight waveguide and MRR. Source and drain electrodes are presented by yellow, while top gates are presented by blue. The channel has two layers, including ITOx and IGZO, which are presented by light blue. The gradient yellow and red represents HZO ferroelectric layer. There is an uncolored fourth FeFET outside the open SiO₂ window, which does not have an effect. (S: source, G: gate, D: drain) (c) Change of optical states modulated by three independent FeFETs on a shared MRR where separate pulses with increasing amplitude are applied. The resonance shift is attributed to the combined effect of the three FeFETs, with each optical state being set by a negative WRITE pulse following a positive RESET pulse. Following a pre-operation of ‘initialization’, the multi-state linear operation, coordinated by three FeFETs, is achieved with a high R2 equal to 0.98323. (λ: wavelength) (d) Histogram showing the reproducibility of reaching each state when starting from ready state for linear operation. 13 distinct states are observed. Different colors correspond to various optical states induced by different FeFETs. e FeFET Pockels photonic memory (red) benchmarked against reported non-volatile photonic memories (orange)7,11,14,15,16,39,40,41,42,43,44,45, in terms of capacity, power consumption, and endurance. The size of each dot represents the capacity.

Despite the largely linear modulation of the memory state with respect to the applied pulses, there are major steps in the resonance shifts due to the initializations into the first non-volatile state (E.g. λ1 in FeFET-1) from the reset state (E.g. λ0 in FeFET-1) for each of the stacked FeFETs, as seen in the upper trace of Fig. 4c. This is due to a major corresponding polarization change of HZO from its polarization in reset state (VG = 0 V) to its polarization at Vg = -2V, which is the minimum voltage (Er > |Eo | ) required to induce ferroelectricity in HZO (Supplementary Fig. 5b). These nonlinear resonance steps can be removed by a ferroelectric state initialization where the FeFETs are individually initialized into their first non-volatile states, as shown in the lower trace of Fig. 4c. To showcase the adaptability of this multi-FeFET Pockels photonic memory, we randomly changed its optical states 40 times for each state, resulting in the resonance histogram presented in Fig. 4d. The histogram demonstrates good reproducibility of different states. The state numbers correspond to those in Fig. 4c after initialization. Between each randomly chosen state, the device is reinitialized to a ready state for linear operations before the next state is set using the same procedure described above. These results affirm the feasibility of accurately and distinctly setting multiple non-volatile states with the multi-FeFET Pockels photonic memory.

Benchmarking the FeFET Pockels photonic memory applied to a hybrid optoelectronic chip (Fig. 4e) involves evaluating three key aspects: capability, power consumption, and endurance. Capability represents the number of stable and differentiable optical states that can be utilized; power consumption measures the energy consumed for switching of one optical state; and endurance represents the ability to sustain repeated operations while maintaining consistent performance. Our device demonstrates a high storage capacity of 4 bits and ultra-low power consumption of 65.1 fJ/state, which is over two orders of magnitude lower than most of existing non-volatile photonic memories7,11,14,15,16,39,40,41,42,43,44,45. This remarkable advancement is driven by the nonlinear Pockels effect, leveraging the strong interaction between LN and HZO, as detailed in the section Device Operations. Additionally, our device exhibits good endurance for both optical and electrical readout, surpassing 10⁷ cycles, due to the good stability of the HZO material46. The capability could be further enhanced by increasing HZO coverage and FeFET density per device, taking into account variations in device performance. To some extent, using a more advanced monochromatic source with a narrower linewidth would also improve the capacity.

A benchmark table is presented in Table 1, with additional detailed benchmarks available in Supplementary Table 2. The relatively low operation speed (~μs) is primarily due to the resistive-capacitive (R-C) switching delay from measurement setup47, large channel width-to-length ratio, and large channel resistance in the depletion region. These factors can be optimized to improve the operation speed to reach sub-nanosecond operation speed48. And the power consumption could be further reduced by increasing o-phase domain density, increasing the Q-factor of MRR and scaling down the entire device (supplementary information), with a potential reduction to sub-fJ/state level. Additionally, while the footprint is approximately 7 × 10⁴ μm² per cell, the active area is only 290 μm², as much of the area within the MRR remains unused. The footprint can be significantly reduced by minimizing the radius of MRR, which can be achieved through lowering propagation loss and increasing the Q-factor. Notably, the electrical readout current does not flow through the HZO, preventing any disturbance to the stored state, which is a significant advantage over other methods, like PCM.

Discussion

By comparing the energy efficiencies between volatile thermo-optic, volatile electro-optic, and non-volatile ferroelectric (this work) modulations, the advantages of non-volatile ferroelectric modulation become evident when maintaining the tuned state. In the thermo-optic case, the heater’s resistive loss accumulates over the modulation duration. In contrast, electro-optic modulators would essentially suffer no resistive loss except for the energy cost of DC drift compensation49. Ferroelectric modulation with 10 year non-volatile state retention (Fig. 3b) would allow for zero energy expense over time. Supplementary Fig. 14 highlights the 100× and 100,000× energy saving for ferroelectric modulation compared to electro-optic and thermos-optic modulation, respectively.

In high-performance and low-energy photonic systems, combining non-volatile memory and high-speed modulation functions is crucial. As demonstrated in our previous work on FeCAP Pockels photonic memory19, integrating both functions into a single compact device is feasible. This integration is also applicable to our FeFET Pockels photonic memory, which can operate in a low-energy non-volatile mode and high-speed volatile mode. Compared to thermo-optic modulation, which suffers from the heater’s large R-C latency, electro-optic modulation has lower R-C switching delay. Moreover, with non-volatile memory features, our device can further reduce R-C latency by pre-setting (program) the device to a baseline resonance λo and perform high-speed modulation for minor tunings about λo (I.e. λtuning = λo +/- Δλ). This would require only incremental changes in switching R-C; further minimizing delay. Thus, the operation speed of our device can be expected to exceed 100 GHz, similar to regular LNOI electro-optic modulators, due to the minimized parasitic effects achieved through the interaction between HZO and LN.

In conclusion, we have described a class of low-voltage hybrid ferroelectric electro-optic modulators by combining ferroelectric switching devices with LN. We show that the combination of an HZO-IGZO FeFET capable of non-volatile multi-state memory can be integrated intimately with LN MRR to produce a Pockels photonic memory. Through the detailed E-field balance between the ferroelectric dipoles in HZO and LN, we implemented a E-field switch that modulates MRR photonic modes through the Pockels effect at femto-Joule/state energy efficiency with expected state retention of 10 years and READ/WRITE endurance exceeding 107 cycles. We show that 6 distinct non-volatile linear memory states are possible per FeFET. To increase the memory capacity dramatically per modulator, we demonstrated the possibility of memory state stacking by stacking transistors on MRR. We showed that up to 16 states can be achieved with three FeFETs integrated on a single MRR. Notably, this Pockels photonic memory offers a 100 × reduction in switching energy compared to state-of-the-art non-volatile photonic memories. Compared to thermo-optic and electro-optic modulators, which suffer from resistive loss and DC drift compensation, respectively, the Pockels photonic memory would be 100× more energy efficient in state maintaining. In addition, it introduces a “program-and-tune” approach to modulation, which allow for incremental switching of parasitic R-C; leading to significant latency reduction. The multi-mode and multi-input capability of our device enables the scaling of reconfigurable photonics and photonic in-memory computing systems into the femto Joule/state energy efficiencies, at reduced device counts/footprint.

Methods

Material optimization

The strength of Pockels effect modulation on the waveguide is limited by the electric-field-effect action through the ferroelectric dielectric on the MRR. As such, it is necessary to maximize the ferroelectricity of the HZO by atomic layer deposition (ALD) process optimization while being sensitive to the LNOI MRR to minimize impact to the LNOI’s birefringence. Increasing the ALD deposition temperature with Ozone as the oxygen source leads to a reduction in the average grain size of the HZO film50, ultimately facilitating an enhancement in ferroelectric polarization (Supplementary Fig. 15a). The orthorhombic HZO phase (Orth.) is easily stabilized in smaller grain regions (Supplementary Fig. 15b). Considering both polarization and leakage current density (Supplementary Fig. 15c), the grown temperature at 280 °C was chosen as the optimal condition. While reducing film thickness leads to a stronger in-plane tensile stress, subsequently strengthening the ferroelectric orthorhombic phase (Supplementary Fig. 16b). Nevertheless, polarization-voltage (PV) loops show decline of ferroelectric polarization in thinner HZO film (Supplementary Fig. 16a), due to rapid increase of leakage current (Supplementary Fig. 16c). Overall, the optimal conditions of HZO growth used for our device is 280 °C temperature for 8 nm thick film.

Device fabrication

The device is fabricated on a thin-film z-cut LNOI wafer (NanoLN) with a film thickness of 600 nm and an oxide insulator thickness of 1.5 μm. The waveguide is defined using electron-beam lithography (EBL) with hydrogen silsesquioxane (HSQ) resist. Subsequently, Ar⁺-based reactive ion etching (RIE) is employed to partially etch the patterns, achieving an etch depth of approximately 320 nm. The removal of HSQ and redeposition residues is carried out using a Piranha solution (H2O2: H2O: NH4OH = 2: 1: 2). To reduce the optical propagation loss, a silicon dioxide (SiO2) cladding layer is deposited onto the device through plasma-enhanced chemical vapor deposition (PECVD) with a thickness of 1 μm. Photolithography and buffered oxide etch (BOE) wet etching are used to remove the SiO2 cladding layer in the regions where the FeFET and MRR are located.

The sample undergoes deposition of IGZO and oxygen-rich ITO (ITOx) dual-channel layers using a magnetron sputter, each with a thickness of 5 nm and 3 nm, respectively. Subsequently, these layers are patterned using photolithography and hydrochloric acid (HCl) wet etching. Palladium (Pd) is deposited on the lithography-defined region using an electron beam evaporator, and a lift-off process is employed to obtain the source and drain electrodes. Following this, ALD is utilized to deposit an 8 nm HZO thin film on top of the ITOx channel. A layer of W is deposited on top of the sample to serve as the ferroelectric induction layer, and a rapid thermal process (RTP) is then conducted in a 380 °C and nitrogen (N2) environment to induce ferroelectricity of HZO. Afterward, the W is removed using a W etchant (Sigma-Aldrich) before growing the conductive ITO layer. The conductive ITO layer is patterned through photolithography and etched using chlorine (Cl2)-based Reactive Ion Etching (RIE), defining it as the top gate electrode.

Finally, the sample is prepared for light edge coupling using dicer and focused ion beam (FIB) polishing to obtain a smooth input port with low insertion loss (1.5 dB/facet) as shown in Supplementary Fig. 17a. The SEM image of well-etched MRR coupling region is provided in Data Supplementary Fig. 17b as well. The energy dispersive X-ray (EDX) spectra are collected by Talos Transmission Electron Microscope (TEM) system as shown in Supplementary Fig. 18. They demonstrate the uniformity of the materials and the orderliness of the stacking.

Optical and electrical measurements

The schematic of the measurement setup used to characterize the optical performance of the device is illustrated in Supplementary Fig. 19. A tunable laser source (TLS) light source (Agilent 81940 A) controlled by lightwave measurement system (Agilent 8164B) is used for the measurement, with the sweeping spectral range from 1550.5 nm to 1551.5 nm, the optical power of 25.12 mW, the sweeping speed at 5 nm/min, and the sweeping step at 1 pm. The full-width at half-maximum (FWHM) of each wavelength in the tunable laser is 0.071 nm (Supplementary Fig. 20). The light is coupled into a single mode optical fiber, and a linear polarizer and a polarization controller (PC) are used to select the transverse magnetic (TM) polarization of the optical mode in the optical fiber. The optical mode is then edge-coupled into the device using a three-dimensional fiber alignment system and a near-infrared (NIR) camera. The output of the device is then collected by another optical fiber and then an optical spectrum analyzer (OSA, Agilent 86412B) or a power sensor (Agilent 81636B) controlled by lightwave measurement system for analysis. The transmission spectra are generated by LabVIEW 2023 software. The electrical signals are provided by semiconductor parameter analyzer (Keysight B1500) which is connected to fast waveform generator/fast measurement (WGFMU, Keysight B1531A) units as shown in Supplementary Fig. 15b-c. Then the WGFMUs are connected to the top gate of FeFET for applying the gate voltage VG, to the source for measuring the source current Is while applying 0 V, and to the drain for measuring the drain current ID while applying a constant voltage of 100 mV.

Optical loss and MRR optimizations

To achieve high-performance FeFET Pockels photonic memory, it is imperative to optimize both waveguide propagation loss and MRR performance. Initially, an LN rib waveguide was designed and optimized using Lumerical MODE software to support a single mode with low propagation loss, either transverse electric (TE) mode (Supplementary Fig. 21a) or TM mode (Supplementary Fig. 21b). The choice of a rib waveguide, instead a strip waveguide, is because of the need to minimize propagation loss caused by the etched waveguide sidewall, given the challenges associated with dry etching of lithium niobate. The width of the partially etched waveguide is 0.8 μm, except for the edge coupler. The edge coupler underwent optimization using Lumerical FDTD software, and the electric field distribution is depicted in Supplementary Fig. 21c. Notably, the blue line in Supplementary Fig. 22a illustrates a peak at 3 μm, indicating the highest coupling efficiency. Consequently, an edge coupler with a maximum width of 3 μm was implemented in our device.

Following the measurement of waveguide loss for varying waveguide lengths, we determined propagation losses of 0.72 dB/mm and 0.58 dB/mm for TE and TM modes, respectively (Supplementary Fig. 22b). These values are comparable with reported results51. In Supplementary Fig. 22a, the coupling efficiency is depicted against the circular MRR gap width. However, due to fabrication limitations, the gap width for our MRR is 0.4 μm. The MRR radius is designed to be 150 µm to enlarge the interaction area between HZO and LN.

Thermal stability of HZO

To assess the feasibility of integrating a heater as a modulator with our FeFET Pockels photonic memory, we conducted a thermal stability test on an 8 nm-thin film of HZO. The ferroelectricity of the HZO film was measured using a ferroelectric tester (Radiant Multiferroic II) at various environmental temperatures ranging from 20 °C to 90 °C. As illustrated in Supplementary Fig. 23, the results indicate that less than 15% of polarization is lost when the temperature is below 90 °C. In practical terms, this implies that the proposed variation in differentiable states remains acceptable, even if it exceeds a 15% loss in polarization.

Comparison with FeCAP Pockels photonic memory

In our previous paper19, FeCAP Pockels photonic memory was introduced, consisting of a HZO ferroelectric capacitor and a LNOI MRR, as depicted in Supplementary Fig. 3a. The capacitor comprises an HZO ferroelectric layer sandwiched between two ITO electrodes. Besides aforementioned worse modulation efficiency than FeFET Pockels photonic memory, another challenge specific to FeCAP Pockels photonic memory, not encountered by FeFET Pockels photonic memory, is the indium segregation in the oxygen-rich ITO thin bottom electrode (Supplementary Fig. 3b). This phenomenon contributes to the propagation loss of the waveguide.

Ferroelectric memory simulation framework and methods

We employed the Sentaurus TCAD tool52 to investigate the ferroelectric memory characteristics in LN/ITOx-IGZO/HZO/ITO heterostructures. These structures were analysed within the Sentaurus S-Device environment using customized models specifically designed to describe the properties of ferroelectric materials, HZO and LN, which are not included in the standard material library of the simulation software. By “library,” we mean a parametric file (*.par) that details a material’s characteristics, such as permittivity, bandgap, work function, and polarization properties. Custom libraries for HZO and LN were created and integrated into the default library. These files are processed by the TCAD tools, ensuring that the physical and electrical properties of each material involved in the analysis are accurately considered. For HZO, the polarization properties were derived from experimental measurements, while for LN, the polarization properties were extracted from reported literature.

The dynamics of ferroelectricity is described by the Preisach-based ferroelectric model implemented in Sentaurus TCAD. In the Preisach-model the discrete square-shaped hysterons are summed up and averaged over the parameter distribution (e.g. internal bias fields and coercive fields) and polarization versus the electric field are described by hyperbolic tangent functions. In the static Preisach model, the saturated hysteresis loop Psat-EFE is described by the following equations.

Where Ps is the saturation polarization, Pr is the remnant polarization, s is the steepness parameter of the PFE-EFE hysteresis loop, EFE is the electric field in the ferroelectrics, Poffset adjusts for the offset of the hysteresis loop’s center along the polarization axis. The coercive fields, Ec+ for the forward sweep and Ec- for the backward sweep account for the asymmetry of the hysteresis loop center along the electric field axis. Further details of the implementation and model derivation can be found in references53,54,55. Where the plus (+) sign indicates the branch of the polarization for the positive field ramp, and the minus (-) sign indicates the branch for the negative field ramp.

In the simulator, ferroelectric polarization properties are primarily described by three quantities: the remanent polarization (Pr), the saturation polarization (Psat), and the coercive field (Ec). To emulate spontaneous polarization in LN, we first simulate the ferroelectric properties of the LN/ITOx-IGZO/HZO/ITO structure with the ferroelectric model turned off for HZO, where HZO acts as a normal dielectric. When the voltage across the LN exceeds its coercive field, LN becomes polarized. To achieve negative spontaneous polarization in LN, a voltage of -10V is applied at the gate (near HZO) and then ramped back to 0 V to retain the negative polarization in LN. This structure, with spontaneous negative polarization in LN, will serve as the initial condition for subsequent steps. While the transport properties are still captured by the drift-diffusion solver, the LN/ITOx-IGZO/HZO/ITO structure is investigated by self-consistently solving the 2-D Poisson’s equation, carrier continuity equations, and the Preisach-based ferroelectric model.

Data availability

The main data that support the findings of this study are available in this article and its Supplementary Information. Additional data are available from the corresponding author upon request.

References

Thirunavukarasu, A. J. et al. Large language models in medicine. Nat. Med. 29, 1930–1940 (2023).

Liu, M. & Wong, H.-S. P. How We’ll Reach a 1 Trillion Transistor GPU. https://spectrum.ieee.org/trillion-transistor-gpu (2024).

Shen, Y. et al. Deep learning with coherent nanophotonic circuits. Nat. Photonics 11, 441–446 (2017).

Ashtiani, F., Geers, A. J. & Aflatouni, F. An on-chip photonic deep neural network for image classification. Nature 606, 501–506 (2022).

Feldmann, J. et al. Parallel convolutional processing using an integrated photonic tensor core. Nature 589, 52–58 (2021).

Xu, X. et al. 11 TOPS photonic convolutional accelerator for optical neural networks. Nature 589, 44–51 (2021).

Ríos, C. et al. Integrated all-photonic non-volatile multi-level memory. Nat. Photonics 9, 725–732 (2015).

Wei, M. et al. Electrically programmable phase-change photonic memory for optical neural networks with nanoseconds in situ training capability. Adv. Photonics 5, 046004 (2023).

Stern, K. et al. Sub-nanosecond pulses enable partial reset for analog phase change memory. IEEE Electron Device Lett. 42, 1291–1294 (2021).

Tsai, S.-H. et al. Stress-memorized HZO for high-performance ferroelectric field-effect memtransistor. ACS Appl. Electron. Mater. 4, 1642–1650 (2022).

Tossoun, B. et al. High-speed and energy-efficient non-volatile silicon photonic memory based on heterogeneously integrated memresonator. Nat. Commun. 15, 551 (2024).

Chen, C.-K. et al. High-performance top-gated and double-gated oxide–semiconductor ferroelectric field-effect transistor enabled by channel defect self-compensation effect. IEEE Trans. Electron Devices 70, 2098–2105 (2023).

Errando-Herranz, C. et al. MEMS for photonic integrated circuits. IEEE J. Sel. Top. Quant. Electron. 26, 1–16 (2020).

Yao, D. et al. Energy-efficient non-volatile ferroelectric based electrostatic doping multilevel optical readout memory. Opt. Express 30, 13572 (2022).

Geler-Kremer, J. et al. A ferroelectric multilevel non-volatile photonic phase shifter. Nat. Photonics 16, 491–497 (2022).

Taki, K. et al. Nonvolatile optical phase shift in ferroelectric hafnium zirconium oxide. Nat. Commun. 15, 3549 (2024).

Treyz, G. V., May, P. G. & Halbout, J.-M. Silicon Mach–Zehnder waveguide interferometers based on the plasma dispersion effect. Appl. Phys. Lett. 59, 771–773 (1991).

Garcia, V. et al. Giant tunnel electroresistance for non-destructive readout of ferroelectric states. Nature 460, 81–84 (2009).

Xu, Z. et al. First demonstration of HZO-LNOI integrated ferroelectric electro-optic modulator and memory to enable reconfigurable photonic systems. In 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Yan, H. et al. Influence of InGaZnO films with different ratios on refractive index sensing characteristics of LPFG. Coatings 10, 978 (2020).

Dong, P. et al. Novel integration technique for silicon/III-V hybrid laser. Opt. Express 22, 26854 (2014).

Fox, R. et al. High performance k = 2.5 ULK backend solution using an improved TFHM architecture, extendible to the 45nm technology node. In IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest. 81–84 (IEEE, 2005).

Thean, A. et al. Low-thermal-budget BEOL-compatible beyond-silicon transistor technologies for future monolithic-3d compute and memory applications. In 2022 International Electron Devices Meeting (IEDM) 12.2.1-12.2.4 (IEEE, 2022).

Chen, C.-K. et al. First demonstration of ultra-low d it top-gated ferroelectric oxide-semiconductor memtransistor with record performance by channel defect self-compensation effect for beol-compatible non-volatile logic switch. In 2022 International Electron Devices Meeting (IEDM) 6.1.1-6.1.4 (IEEE, 2022).

Polyanskiy, M. N. Refractiveindex.info database of optical constants. Sci. Data 11, 94 (2024).

Hong, D. H. et al. Characteristics of Hf0.5Zr0.5O2 thin films prepared by direct and remote plasma atomic layer deposition for application to ferroelectric memory. Nanomaterials 13, 900 (2023).

Roussey, M. et al. Electro-optic effect exaltation on lithium niobate photonic crystals due to slow photons. Appl. Phys. Lett. 89, 241110 (2006).

Sanna, S. & Schmidt, W. G. Lithium niobate X -cut, Y -cut, and Z -cut surfaces from ab initio theory. Phys. Rev. B 81, 214116 (2010).

Fedotova, A. et al. Lithium niobate meta-optics. ACS Photonics 9, 3745–3763 (2022).

Bogaerts, W. et al. Silicon microring resonators. Laser Photonics Rev. 6, 47–73 (2012).

Sinclair, M. et al. 1.4 million Q factor Si3 N4 micro-ring resonator at 780 nm wavelength for chip-scale atomic systems. Opt. Express 28, 4010 (2020).

Han, S., Chen, W., Hu, H., Cheng, Z. & Liu, T. Characterization method of a mid-infrared graphene-on-silicon microring with a monochromatic laser. J. Opt. Soc. Am. B 37, 1683 (2020).

Hong, J. W. et al. Nanoscale investigation of domain retention in preferentially oriented PbZr0.53Ti0.47O3 thin films on Pt and on LaNiO3. Appl. Phys. Lett. 75, 3183–3185 (1999).

Zagni, N., Puglisi, F. M., Pavan, P. & Alam, M. A. Reliability of HfO2 -based ferroelectric FETs: a critical review of current and future challenges. Proc. IEEE 111, 158–184 (2023).

Genenko, Y. A., Glaum, J., Hoffmann, M. J. & Albe, K. Mechanisms of aging and fatigue in ferroelectrics. Mater. Sci. Eng. B 192, 52–82 (2015).

Halter, M. et al. Back-end, CMOS-compatible ferroelectric field-effect transistor for synaptic weights. ACS Appl. Mater. Interfaces 12, 17725–17732 (2020).

Jin, D.-G. et al. Improvement of polarization switching in ferroelectric transistor by interface trap reduction for brain-inspired artificial synapses. Mater. Today Nano 22, 100320 (2023).

Zhou, J., Liu, N., Zhu, L., Shi, Y. & Wan, Q. Energy-efficient artificial synapses based on flexible IGZO electric-double-layer transistors. IEEE Electron Device Lett. 36, 198–200 (2015).

Song, J.-F. et al. Integrated photonics with programmable non-volatile memory. Sci. Rep. 6, 22616 (2016).

Lu, Y. et al. Mixed-mode operation of hybrid phase-change nanophotonic circuits. Nano Lett. 17, 150–155 (2017).

Farmakidis, N. et al. Plasmonic nanogap enhanced phase-change devices with dual electrical-optical functionality. Sci. Adv. 5, eaaw2687 (2019).

Li, X. et al. Fast and reliable storage using a 5 bit, nonvolatile photonic memory cell. Optica 6, 1 (2019).

Wu, C. et al. Programmable phase-change metasurfaces on waveguides for multimode photonic convolutional neural network. Nat. Commun. 12, 96 (2021).

Liu, Z. et al. Intelligent all-fiber device: storage and logic computing. Photonics Res. 10, 357 (2022).

Meng, J. et al. Electrical programmable multilevel nonvolatile photonic random-access memory. Light Sci. Appl. 12, 189 (2023).

Chae, K., Hwang, J., Chagarov, E., Kummel, A. & Cho, K. Stability of ferroelectric and antiferroelectric hafnium–zirconium oxide thin films. J. Appl. Phys. 128, 054101 (2020).

Si, M. et al. Ultrafast measurements of polarization switching dynamics on ferroelectric and anti-ferroelectric hafnium zirconium oxide. Appl. Phys. Lett. 115, 072107 (2019).

Kondratyuk, E. & Chouprik, A. Polarization switching ginetics in thin ferroelectric HZO films. Nanomaterials 12, 4126 (2022).

Sosunov, A., Ponomarev, R., Zhuravlev, A., Mushinsky, S. & Kuneva, M. reduction in DC-drift in LiNbO3-based electro-optical modulator. Photonics 8, 571 (2021).

Choi, Y. et al. Impact of chamber/annealing temperature on the endurance characteristic of Zr:HfO2 ferroelectric capacitor. Sensors 22, 4087 (2022).

Zhu, D. et al. Integrated photonics on thin-film lithium niobate. Adv. Opt. Photonics 13, 242 (2021).

Chowdhury, J., Das, J. K., Sarkar, A. & Mohapatra, K. TCAD simulation of emerging nanoscale devices. In Nanoelectronics: Physics, Materials and Devices (eds. Sarkar, A., Sarkar, K. C., Benfdila, A.) 409–455 (Elsevier, 2023).

Dragosits, K., Hagenbeck, R. & Selberherr, S. Transient Simulation of Ferroelectric Hysteresis. https://www.iue.tuwien.ac.at/pdf/ib_2000/CP2000_Dragosits_3.pdf (2000).

Pešić, M., Slesazeck, S., Schenk, T., Schroeder, U. & Mikolajick, T. Impact of charge trapping on the ferroelectric switching behavior of doped HfO 2. Phys. Status Solidi A 213, 270–273 (2016).

Pešić, M. et al. Physical mechanisms behind the field‐cycling behavior of HfO 2 ‐based ferroelectric capacitors. Adv. Funct. Mater. 26, 4601–4612 (2016).

Bae, M., Kim, Y., Kim, S., Kim, D. M. & Kim, D. H. Extraction of subgap donor states in a-IGZO TFTs by generation–recombination current spectroscopy. IEEE Electron Device Lett 32, 1248–1250 (2011).

Acknowledgements

This work is supported by the Ministry of Education, Singapore, under its Academic Research Fund (AcRF) Tier 2 (MOE‐T2EP50123‐0011) as well as NRF’s Medium Sized Centre: Singapore Hybrid-Integrated Next-Generation μ-Electronics (SHINE) Centre funding program.

Author information

Authors and Affiliations

Contributions

Z. X., C.-K. C. and A. V.-Y. T. conceived the research, designed the experiments, analysed the data and wrote the paper. Z. X., C.-K. C. and H.-L. Lin led the device fabrication and electro-optic characterization. M.S. conducted TCAD simulation. E.Z., J.Y.-M. L., S.V. and A.D. contributed towards discussion and data interpretation. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Carlos A. Rios Ocampo, and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Xu, Z., Chen, CK., Lin, HL. et al. Ferroelectric-based Pockels photonic memory. Nat Commun 16, 8329 (2025). https://doi.org/10.1038/s41467-025-63850-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-025-63850-z