Abstract

Enhancing the drive current of oxide semiconductor transistors is crucial for enabling high-resolution displays with thin bezels and improving memory write and access speeds. High-mobility channel materials boost drive current but typically require stricter process control and reliability, presenting mass-production challenges compared to stable materials like InGaZnO. Therefore, increasing drive current without changing the channel material is a desirable goal to pursue. One approach is to enhance gate capacitance using high-κ gate dielectrics. In this study, we systematically investigate the impact of high-κ gate dielectrics on the performance of InGaZnO transistors, focusing on three different gate insulators: SiO2, HfO2, and ZrO2. Experimental results show that as the dielectric constant increases from 3.9 (SiO2) to 17 (HfO2) and 30 (ZrO2), the drive current is enhanced by factors of 2.8 and 7, respectively–less than the expected enhancement from κ alone. Device simulations reveal that contact resistance, channel capacitance, and interface trap density all influence the drive current. Notably, interface traps emerge as the primary limiting factor, particularly in HfO2, significantly degrading the transconductance. Utilizing the single-pulse charge pumping method, we quantify interface trap densities and demonstrate that reducing interface traps is essential in fully leveraging high-κ gate dielectrics to enhance drive current.

Similar content being viewed by others

Introduction

Oxide semiconductor transistors are used in thin-film transistor (TFT) circuits of display panels, back-end-of-the-line switches, and embedded memory devices1,2,3. High drive current of TFTs enable high pixel density, display resolution, and thinner frame thicknesses owing to the smaller device footprint in pixel and gate driver circuits. Also, fast memory write and read times are made possible by high drive current of oxide semiconductor access transistors in 2T0C or 1T1C DRAM cells4. Despite low-temperature poly-silicon (LTPS) TFTs having high mobility exceeding 70 cm2/V·s5,6,7, oxide semiconductoros having extremely-low off-state current have wide promise for back-end integration in low-power applications. Currently, amorphous InGaZnO (IGZO) are heterogeneously fabricated with LTPS on the same substrate in displays of mobile and wearable electronic devices8,9,10. However, high integration and circuit complexity, as well as increased fabrication cost due to additional photolithography steps and dual optimization of two types of TFTs raises demand for a universal channel material. Therefore, drive current improvement of oxide semiconductor TFTs is actively being pursued. Drive current (I ∝ qnv) can be enhanced by either higher electron transport (v) or more channel charge (n) at the same bias conditions. Obtaining high electron mobility (high v) by using different cation composition channel materials has been extensively studied, particularly increasing indium for higher mobility and carrier concentration, such as InZnO or In2O311,12. Due to the increased carrier density in the channel, devices tend to become depletion mode and require carrier suppression primarily by oxygen treatments for Vth > 0 operation. Thus, reliability degradation mechanisms become more complex due to indium complexes and peroxy linkages caused by simultaneous increase of indium and oxygen content in the channel13. Hence, alternative methods of obtaining high drive current are preferred, such as channel length reduction14, interface treatment, and point defect minimization for improved transport15.

In this study, we focus on increasing n with a higher gate oxide capacitance \((C_{{ox}} = ~\kappa \epsilon _{0} A~/~t_{{ox}} )\) to increase the drain current (ID) of IGZO transistors maintaining the same device footprint, rather than increased transport characteristics. To do this, the gate area (A = W × L) can be increased, the gate insulator (GI) thickness (tox) can be reduced, or a higher dielectric constant (κ) GI material can be implemented. Increasing current by increased channel width (W) is not a preferred direction due to increased device footprint and larger circuit area, so we will exclude increasing gate area as an option. First, we performed technology computer-aided design (TCAD) device simulations16. We set a nominal tox = 100 nm and κ = 6. Then, Cox was increased by 5 times by either: reducing tox to 20 nm or increasing κ to 30. Increasing the GI dielectric constant or decreasing the GI thickness both resulted in a 4.6 times increase of ID and when applying both simultaneously resulted in a 21.3 times ID increase. Although Cox increased by 5 times, Cg increases less due to the gate-to-channel capacitance (Cs) in series with Cox. Since tox reduction is limited due to gate leakage or large-area film uniformity constraints, we will focus on increasing κ. Contact resistance and interface traps also affect the drive current but to a lesser effect which will be discussed in a later section.

Results

High-κ gate insulators in IGZO devices: enhanced drive current with HfO2 and ZrO2

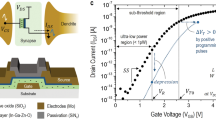

Figure 1a shows the band gap and dielectric constant of various dielectric materials. Empirically, higher κ dielectrics have smaller band gaps, which would lead to high gate leakage current when applied as the GI of a transistor. Among the materials with a band gap larger than 5 eV17, HfO2 and ZrO2 have the highest dielectric constant. Metal-insulator-metal (MIM) capacitors and TFTs were fabricated using HfO2 and ZrO2 as the gate dielectric materials (see Methods for process details). Figure 1b and c show the measured dielectric constant and current density of the MIM capacitor. Inverted staggered structure IGZO TFTs with SiO2, HfO2, ZrO2 GI are individually fabricated, as shown in Fig. 1d (see Methods for process and structure details).

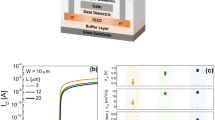

To obtain the current ratios of the high-κ GI devices against the SiO2 GI device, currents are compared at the same gate overdrive voltage (VOV = VGS – Vth) to compensate for different Vth values across different devices for fair comparison. Vth is extracted using the constant current method20,21, where Vth is defined as the VGS where ID reaches a specified current value (ICC) of 10 nA. Figure 2a shows the ID–VOV characteristics of IGZO devices with different GI materials. Table 1 lists the measured device parameters. ID values at VOV = 2 V and VDS = 2 V are shown. Note that the subthreshold swing (SS) varies between devices, which implies that the choice of ICC affects VOV differently among the devices. Hence, for completeness, current ratios at several ICC values are evaluated. Figure 2b and c show the current enhancement ratio of HfO2 and ZrO2 GI devices with respect to the SiO2 GI device, plotted against VOV. We note that the current ratios become larger when Vth is extracted at a lower ICC, because more of the subthreshold regime is included, thereby exaggerating the apparent current enhancement for high- κ GI devices with steeper SS. The ID, high−κ / ID, SiO2 ratio, averaged over a Vov range of 1–2 V, is 3.1 for HfO₂ and 7.3 for ZrO₂ at ICC = 10 nA, and increases to 3.7 for HfO2 and 11.8 for ZrO2 at ICC = 10 pA. Since \(SS = \frac{{kT}}{q} \times \ln \left( {10} \right) \times ~\left( {1 + ~C_{s} /C_{{ox}} } \right)\), higher κ gate dielectrics will have a steeper SS due to high Cox. Hence, selecting a low ICC value penalizes devices with high SS, as the wider subthreshold region is included in VOV. In other words, lower ICC values result in larger ID at equal VOV for higher κ GI devices. Having acknowledged the κ-dependent SS effect, we use ICC = 10 nA for Vth determination for subsequent analysis to exclude the influence of the subthreshold region.

(a) Bandgap and dielectric constant values of various dielectric materials18,19. (b) Dielectric constant, and (c) current density (measured at 2.5 MV/cm) of fabricated MIM capacitors with HfO2, ZrO2 as the insulator (both 20-nm-thick) and 50-nm-thick Mo as the electrodes. The lower measured dielectric constant from its typical amorphous-phase value is attributed to partial crystallization during post-deposition annealing22. (d) Bottom gate structure of IGZO TFT with SiO2 (PECVD), HfO2 (ALD), and ZrO2 (ALD) GI. All GI layers have the same thickness of 20 nm. Channel length and width are 20 μm and 40 μm, respectively. Molecular structures of the precursors for HfO2 and ZrO2 are shown.

Figure 2d shows the simulated and experimental current increase ratios against the κ enhancement factor relative to SiO2 (3.9). The device structure used in simulations was matched with the experimental device, including the extrinsic overlap regions between the gate and S/D electrodes to accurately account for the parasitic capacitance. Simulation parameters regarding material properties and sub-gap density of states profile are listed in Supplementary Table S1. Further, simulation results are obtained by changing only the κ of the GI material with all other parameters kept the same. As a result, when the dielectric constant increased by a factor of 4.3 and 7.6, the measured ID increased by a factor of 2.8 and 7.0, respectively. The measured current increase ratio of ZrO2 GI devices matched the simulated value, but that of the HfO2 GI devices is noticeably lower than the simulated value of 4.

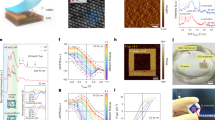

To investigate this discrepancy in current increase ratio of the HfO2 device over the SiO2 device between simulation and measurement, factors affecting the drive current including contact resistance, series capacitance, and interface traps were analysed using TCAD simulations. For the contact resistance to account for the current ratio suppression of 3.9 to 2.8, the contact resistance must be increased by 1,000–1,300 times. For series capacitance to account for the ID ratio reduction it must be increased by 5.83 times. In both cases, there is no reason for a contact resistance or series capacitance increase only for the HfO2 device since the Al/IGZO contacts and IGZO channel formation process conditions were the same for all the devices. Finally, the interface trap density was varied (see Supplementary Information for details). Figure 3a shows the degradation of the transconductance (gm) as the acceptor interface state density increases. Further, gm degradation leads to ID degradation as shown in Fig. 3b–d for various GI devices.

(a) ID–Vov curves of IGZO TFTs with SiO2, HfO2, and ZrO2 GI. Current ratios of (b) HfO2 and (c) ZrO2 GI devices relative to the SiO2 GI device at various ICC. (d) Current ratio at VOV = 2 V as a function of κ enhancement factor referenced to SiO2 (κ = 3.9). Data based on experiments (symbols) and ideal TCAD simulations (solid line) are shown, while the 1:1 relation is denoted by a dotted line for reference. Ideal simulation conditions do not account for Dit which result in a pronounced discrepancy with experiments at 17 / 3.9 = 4.36 (HfO2 case, κ = 17).

(a) Simulated ID–VGS characteristics (log scale) and transconductance characteristics at different interface trap densities (Dit), for the case of HfO2 GI device. Simulated ID–VGS characteristics at different Dit levels for (b) SiO2, (c) HfO2, (d) ZrO2 GI devices. Experimental ID–VGS data are included for comparison. Simulations suggest that Dit larger than 3 × 1012 cm− 2 is required to agree with experimental data for the HfO2 GI device. All characteristics are taken at VDS = 2 V.

Single-pulse charge-pumping method for interface trap extraction

To experimentally confirm the amount of interface traps among different GI devices, interface traps at the IGZO/GI boundary are extracted using single-pulse charge pumping (SPCP)23,24. SPCP is a measurement method that extracts charge traps at the IGZO/GI interface and the GI bulk in the vicinity of the interface. SPCP enables more direct and robust quantification of interface traps in amorphous oxide semiconductors compared to conventional C–V-based methods, which are often susceptible to noise or require large gate-area devices. Supplementary Fig. S1a shows the SPCP measurement setup, where a voltage pulse (Vp) is applied to the gate of the device under test, and current (Ip) is sensed at the tied-S/D node. During the rising and falling edges of Vp, displacement current flows as the gate capacitor is charged and discharged, respectively. Ideally, for a linear Vp ramp the current will be constant during rise and fall times following

and

since displacement current for charging and discharging a capacitor should ideally be symmetrical. The current direction is defined as positive when electrons accumulate the IGZO channel interface during the rising edge and negative when electrons are flowing out the S/D node during the falling edge, as in Supplementary Fig. S1b. However, when trapping occurs in the gate stack, the two current components will differ. Supplementary Fig. S1c overlaps Ip(t) during the rising edge and the flipped |Ip(t)| during the falling edge, and the larger area of the rising edge clearly indicates that accumulated electrons were partially captured and couldn’t escape at the falling edge. In other words, the areal density of trapped charge (Nit) can be extracted using:

where T is the period of one full Vp cycle, q is the elementary electron charge, W is the channel width, and L is the gate length.

Figure 4a–c show the applied Vp and measured Ip(t) as a result of the SPCP method. Since the threshold voltage is different for each device, the base voltage (VL) of Vp was set to be the VGS where ID = 1 pA. Also, since high-κ GI materials have higher Cg, the pulse amplitude and rising/falling times were adjusted to keep the displacement current component (Eq. 1) constant. The applied voltage pulses were set to have the same C × dV/dt across different devices, taking into account the Vth and dielectric constant of the GI materials. Figure 4d–f show the trapped charge density obtained from the transient current integrated over the duration of a pulse cycle according to Eq. 3. The extracted Nit for SiO2, HfO2, ZrO2 GI are 1.42 × 1012, 3.30 × 1012, 4.96 × 1010 cm− 2, respectively. This is consistent with the simulation results shown in Fig. 3. The ZrO2 GI device achieved a current enhancement factor expected from κ enhancement relative to SiO2 due to its low Nit, agreeing with simulations. However, the high Nit of HfO2 devices degrades the drain current, preventing the current enhancement factor from reaching its expected κ-proportional increase, as shown by simulations in Fig. 3c.

TCAD simulation to investigate the impact of interface traps on device performance

Figure 5a shows the simulated current ratios using the interface trap density extracted by SPCP as input parameters (green symbols and line). Simulations including the high Dit of the HfO2 GI device now reflect the experimental results. To further investigate the effect of interface traps on the device performance, we analyse the simulated device. Figure 5b–d shows the 1D cut lines in the x and y directions (defined in the inset of Fig. 5b). Electron concentration, electron velocity, and E-field were compared at different interface trap densities. Both the electron velocity and the E-field at the interface decrease as the interface trap increases. As the Fermi level passes through the energy range of interface trap states, the rate of surface potential (\(\:{\psi\:}_{s}\)) change in response to the gate voltage slows as electrons are filling the interface states, which can be modeled as an interface trap capacitance (Cit)21. Since Cg is a series connection of Cox and Cs + Cit (see Supplementary Fig. S2), the increase in interface traps requires filling, which in turn lowers \(\:{\psi\:}_{s}\) at a given gate voltage. Hence, the field across Cox is reduced, carrier velocity is lowered, and reaching an equal amount of carrier concentration would require a higher gate voltage. Hence, degradation in transconductance occurs. This contrasts with the influence of oxide charge, where ID degradation is caused by a parallel shift in Vth25. Figure 3a supports the effect of interface traps, as it is evident that there is no Vth shift with Dit change, and the transconductance is reduced due to higher Dit.

(a) Current ratio at VOV = 2 V as a function of κ enhancement factor from experiments (red triangle symbols), TCAD simulations with Dit = 0 (blue solid line), and simulations with Dit values extracted from SPCP used as input parameters (green inverse triangle symbols). (b), (c), and (d) display the 1D profiles of electron concentration, electron velocity, and electric field (E-field), respectively, for various interface trap densities. The inset of (b) shows the device structure with cut lines in the x and y directions.

Discussion

Increased current is required for the application of oxide TFTs in display and integration with CMOS, which we achieve by increasing gate capacitance by implementing gate insulators with a higher dielectric constant. However, the observed current increase was lower than the theoretically expected κ-proportional increase rate. This is confirmed by SPCP analysis and TCAD simulations, where HfO2 with higher Nit resulted in less ID enhancement. The main causes behind this include Cit lowering Cg and transconductance degradation via interface traps. We have demonstrated that drive current can be enhanced by implementing high-κ GI materials, as expected; however, we emphasize that optimization of interface properties is crucial to fully realize the benefits of high-κ dielectrics.

Methods

We fabricated metal/insulator/metal (MIM) capacitors with 50-nm Mo electrodes and 20 nm of HfO2 and ZrO2 insulator layers, respectively. The dielectric films were formed by atomic layer deposition (ALD) at a deposition temperature of 320℃. The carrier gas is Ar (99.99%), and precursors are Hf[Cp(NMe2)3] and Zr[Cp(NMe2)3] for HfO2 and ZrO2, respectively, and ozone is used as the reactant. HfO2 and ZrO2 shows a dielectric constant of 15 ~ 17 and 22 ~ 23, respectively, after rapid thermal annealing at 500℃ for 10 s. The current densities of the MIM capacitors are less than 10− 7 for HfO2, and 10− 5 A/cm2 for ZrO2 at 2.5 MV/cm. For reference, this translates to a gate current less than 10− 13 A and 10− 11 A for tox = 20 nm HfO2 and ZrO2 GI films, respectively, of a W / L = 40 μm / 20 μm transistor device at 5 V.

For the fabrication of IGZO TFTs, first, a Mo metal gate of 50 nm is deposited by sputtering on a glass substrate and patterned by wet etch. For GI formation, SiO2 is deposited by plasma enhanced chemical deposition (PECVD), while HfO2 and ZrO2 are deposited by ALD. Power, working pressure and stage temperature of PECVD are 50 W, 1000 mtorr and 350℃, respectively. Self-limited reaction process of ALD makes good uniformity and step coverage of the GI films. Thickness of all three GI materials are 20 nm measured by ellipsometry. Gate via contact holes are etched by reactive ion etching (RIE) with 2 sccm of Ar and CF4 gas each and rf power of 150 W. A 30-nm-thick IGZO is deposited by rf sputter with working pressure of 8 mtorr, power of 50 W, and Ar flow of 50 sccm. All devices have a channel width of 40 μm and a channel length of 20 μm. Source and drain (S/D) electrodes are formed by 50-nm-thick Al deposited by a thermal evaporator.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Morosawa, N. et al. High-mobility self-aligned top-gate oxide TFT for high-resolution AM-OLED. J. Soc. Inf. Disp. 21, 467. (2014).

Son, Y., Frost, B., Zhao, Y. & Peterson, R. L. Monolithic integration of high-voltage thin-film electronics on low-voltage integrated circuits using a solution process. Nat. Electron. 21, 467. https://doi.org/10.1038/s41928-019-0316-0 (2014).

Belmonte, A. et al. Capacitor-less, long-retention(> 400s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. In IEEE Int. Electron. Devices Meeting (IEDM) 609. https://doi.org/10.1109/IEDM13553.2020.9371900 (2022).

Hu, Q. et al. Optimized IGZO fets for capacitorless DRAM with retention of 10 Ks at RT and 7 Ks at 85 ℃ at zero Vhold with Sub-10 Ns speed and 3-bit operation. In 2022 IEEE Int. Electron. Devices Meeting (IEDM) 619. https://doi.org/10.1109/IEDM45625.2022.10019435

Ibaraki, N. Low temperature Poly-Si TFT technology. SID Symp. Dig. Tech. Pap. 30 (180). https://doi.org/10.1889/1.1833987 (1999).

Kim, S. J. et al. A novel five-photomask low-temperature polycrystalline silicon CMOS structure for AMLCD application. IEEE Trans. Electron. Devices. 57, 9 2324. https://doi.org/10.1109/TED.2010.2053868 (2010).

Kim, M. et al. (ed, J.) World-best performance LTPS TFTs with robust bending properties on AMOLED displays. SID Symp. Dig. Tech. Pap. 437 194. https://doi.org/10.1889/1.3621268 (2011).

Chang, T. K., Lin, C. W. & Chan, S. LTPO TFT technology for amoleds. SID Symp. Dig. Tech. Pap. 50 (545). https://doi.org/10.1002/sdtp.12978 (2019).

Chung, U. J. et al. Manufacturing technology of LTPO TFT. SID Symp. Dig. Tech. Pap. 51 192. https://doi.org/10.1002/sdtp.13835 (2004).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488. https://doi.org/10.1038/nature03090 (2004).

De Wit, J. H. W., Unen, G. V. & Lahey M. Electron concentration and mobility in In2O3. J. Phys. Chem. Solid. 38, 819. https://doi.org/10.1016/0022-3697(77)90117-2 (1977).

Illiberi, A. et al. Atmospheric plasma-enhanced spatial-ALD of InZnO for high mobility thin film transistors. J. Vac Sci. Technol. A. 36, 04F401. https://doi.org/10.1116/1.5008464 (2018).

Lee, S., Song, Y., Park, H., Paine, A. & Zaslavsky & Channel scaling and field-effect mobility extraction in amorphous InZnO thin film transistors. Solid State Electron. 135, 94. https://doi.org/10.1016/j.sse.2017.06.033 (2017).

Liu, W. S., Hsu, C. H., Jiang, Y., Lai, Y. C. & Kuo, H. C. Improving device characteristics of dual-gate IGZO Thin-Film transistors with Ar–O2 mixed plasma treatment and rapid thermal annealing. Membranes 135, 94. https://doi.org/10.3390/membranes12010049 (2017).

Jang, J. T. et al. Cation composition-dependent device performance and positive bias instability of self-aligned oxide semiconductor Thin-Film transistors: including oxygen and hydrogen effect. ACS Appl. Mater. Interfaces. 14, 1389. https://doi.org/10.1021/acsami.1c18890 (2022).

Atlas User’s Manual: Version 5.26. 1.R (Silvaco Inc., 2018).

Cerdeira, A., Estrada, M., Marsal, L. F., Pallares, J. & Iniguez, B. On the series resistance in staggered amorphous thin film transistors. Microelectron. Reliab. 63, 325. https://doi.org/10.1016/j.microrel.2016.05.005 (1984).

Barquinha, P., Martins, R., Pereira, L. & Fortunato, E. Transparent Oxide Electronics: From Materials To Devices (Wiley, 2012).

Robertson, J. Band offsets of Wide-Band-Gap oxides and implications for future electronic devices. J Vac Sci. Technol N. 18, 1785. https://doi.org/10.1116/1.591472 (2000).

Booth, R. V., White, M. H., Wong, H. S. & Krutsick, T. J. The effect of channel implants on MOS transistor characterization. IEEE Trans. Electron. Device. 34, 2501. https://doi.org/10.1109/T-ED.1987.23341 (1987).

Taur, Y. & Ning, T. H. Fundamentals of Modern VLSI Devices (Cambridge University Press, 1998).

Chen, T. J. & Kuo, C. L. First principles study of the structural, electronic, and dielectric properties of amorphous HfO2. J. Appl. Phys. 110, 064105. https://doi.org/10.1063/1.3636362 (2011).

Nguyen, M. C. et al. Application of Single-Pulse Charge-Pumping method on evaluation of indium gallium zinc oxide Thin-Film transistors. IEEE Trans. Electron. Devices. 65, 3786. (2018).

Groeseneken, G., Maes, H. E., Beltran, N. & Keersmaecker, R. F. D. A reliable approach to charge-pumping measurements in MOS transistors. IEEE Trans. Electron. Devices. 31, 42. https://doi.org/10.1109/T-ED.1984.21472 (1984).

Huang, X. Y. et al. Effect of interface traps and oxide charge on drain current degradation in tunneling Field-Effect transistors. IEEE Electron. Device Lett. 31, 779. https://doi.org/10.1109/LED.2010.2050456 (2010).

Acknowledgements

This work was supported by LG Display; the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (MSIT) of the Korea Government under Grants 2022M3F3A2A01072215 and 2022M3F3A2A01073562. The EDA tool was supported by the IC Design Education Center (IDEC).

Author information

Authors and Affiliations

Contributions

S.O., J.H.B., J.N., K.-S.P. proposed the work. J.P., H.K., S.M.Y. performed the experiments. J.P. and K.K. contributed to pulse measurements. S.O. and J.A. supervised the research. K.-S.P. and S.Y.Y. provided resources. J.P. and S.O. wrote the original draft. All authors reviewed and approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Below is the link to the electronic supplementary material.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Park, J., Kim, HB., Yu, S.M. et al. Enhancing InGaZnO transistor current through high-κ dielectrics and interface trap extraction using single-pulse charge pumping. Sci Rep 15, 23113 (2025). https://doi.org/10.1038/s41598-025-07995-3

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-07995-3

Keywords

This article is cited by

-

LTPO-based pixel circuit with highly uniform luminance and low flicker for variable refresh rate in AMOLED displays

Scientific Reports (2025)

-

Role of various oxygen vacancy suppressors on the electrical performance of amorphous Zn-Sn-O thin film transistors

Journal of Materials Science: Materials in Electronics (2025)