Abstract

The performance of any elliptic curve cryptography hardware accelerator significantly relies on the efficiency of the underlying point multiplication (PM) architecture. This article presents a hardware implementation of field-programmable gate array (FPGA) based modular arithmetic, group operation, and point multiplication unit on the twisted Edwards curve (Edwards25519) over the 256-bit prime field. An original hardware architecture of a unified point operation module in projective coordinates that executes point addition and point doubling within a single module has been developed, taking only 646 clock cycles and ensuring a better security level than conventional approaches. The proposed point multiplication module consumes 1.4 ms time, operating at a maximal clock frequency of 117.8 MHz utilising 164,730 clock cycles having 183.38 kbps throughput on the Xilinx Virtex-5 FPGA platform for 256-bit length of key. The comparative assessment of latency and throughput across various related recent works indicates the effectiveness of our proposed PM architecture. Finally, this high throughput and low latency PM architecture will be a good candidate for rapid data encryption in high-speed wireless communication networks.

Similar content being viewed by others

Introduction

The emergence of the modern Internet of things (IoT) infrastructure is a manifestation of the prediction made by Moore’s Law (more computation capability due to aggressive technology scaling) and Edholm’s Law (more data communication due to modern wireless standards). Nowadays, billions of devices of various cyber-physical systems like smart cities, healthcare, and intelligent transportation are connected through the IoT network. Consequently, the IoT ecosystem has fostered a widespread network of wireless sensor nodes (WSNs) within its application layer, as shown in Fig. 1. Many IoT devices utilises cloud-based data storage solutions due to limited resources, allowing users to access and share data from anywhere over the Internet. However, this approach raises significant security concerns as attackers can manipulate data through unregistered devices deployed within the IoT ecosystem. Therefore, the futuristic IoT ecosystem demands a secure data transmission network to avert unauthorised access and protect sensitive data1,2,3. Asymmetric cryptography or public-key cryptography (PKC) based security protocols can be a viable solution to deal with the privacy aspects of such networks as it avoids key distribution compared to conventional symmetric cryptography4. There are several popular methods of PKCs, such as RSA5, ECC6,7 as well as Edward curve cryptography (EdCC)8. However, ECC has emerged as an intriguing replacement for traditional RSA encryption, owing to its superior strength-per-bit in achieving equivalent levels of security. Hence, ECC can be deployed in the limited-resource IoT environment to achieve fast computation while upholding the intended level of security.

Privacy Aspects of the growing IoT environment.

Side Channel Attacks (SCA) exploit information leaked during the physical implementation of cryptographic algorithms. These attacks target the hardware rather than the cryptographic algorithm itself, making them a significant concern for cryptographic implementations. Power analysis attacks are a type of SCA that involves measuring the power consumption of a cryptographic device during its operation. Simple Power Analysis (SPA) and Differential Power Analysis (DPA) are the two main types of power analysis attacks. SPA examines the power consumption patterns of a device to extract cryptographic keys and other sensitive information. SPA relies on identifying distinct power consumption patterns that correspond to specific operations within the cryptographic algorithm. DPA is a more sophisticated attack that involves statistical analysis of power consumption data collected from multiple cryptographic operations. By analysing the differences in power consumption, attackers can reveal secret information, such as cryptographic keys. Various techniques have been proposed to protect cryptographic hardware implementations against SPA and DPA attacks. For example, the paper by Joye and Tymen9 discusses countermeasures for ECC against power analysis attacks. Additionally, the study by Sasdrich and Güneysu10 presents hardware implementations of ECC with protection against SPA and DPA. Unlike Post-Quantum Cryptography10, which is designed to be secure against attacks from both quantum and classical computers, existing cryptographic systems are susceptible to side-channel attacks. While ECC is widely used and integrated into various cryptographic protocols such as Transport Layer Security, it is important to acknowledge that ECC is not resistant to attacks from quantum computers. Post-Quantum Cryptography aims to develop cryptographic algorithms that are secure against quantum adversaries. Nevertheless, ECC remains a well-established and diffused cryptosystem in current applications, and its efficiency and security are critical for many existing infrastructures.

Edward curves, a special species of the family of elliptic curves, have recently attracted significant research focus because of their high side-channel attack resilience, fast group operation and unified addition formulas. The primary operation of the Edward Curve Crypto Processor (EdCCP) is the Edward curve scalar multiplication (EdCSM) or Edward curve point multiplication (EdCPM), which is expressed as S = k.P; while k is a scalar number, P denotes a particular point on the Edward curve—the resultant point S is found by multiplying an Edward curve point P with a scalar value k. The efficient design of the point multiplication unit is mandatory for developing a high-performance EdCCP, where the performance of the particular point or group operation unit and the modular arithmetic unit determines the efficacy of the point multiplication unit. Thus, optimising the designs of these three units establishes a framework for achieving high efficiency in EdCCP9,10,11,12. The overall approach of the elliptic curve cryptography (ECC) hardware accelerator design is delineated in Fig. 2. The urge to produce a high-performance ECC accelerator has alluded many researchers to design a high-performance point multiplication unit. Owing to the flexible design environment offered by the FPGA platforms, many FPGA-based hardware architectures for ECC point multiplication on both Galois prime field GF(p) as well as Galois binary field GF(2n) have been proposed by many researchers13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36. Some of these research were intended to save hardware resources required for small-device applications, while others were intended to minimise the computational time for efficient data encryption in different field sizes. However, a 256-bit architecture over the prime field is preferred most for direct comparison as it is suitable for modern cryptographic security applications. Our proposed EdCPM architecture can be implemented for other standard NIST prime curves.

Hierarchy of the ECC hardware accelerator.

In Hossain et al.19 put forward a hardware implementation of the elliptic curve scalar multiplication (ECSM) over a prime field, providing a novel modular multiplication unit using the Montgomery method. In Marzouqi et al.20 also designed Karatsuba–Ofman modular multiplication unit and Radix-4 Binary GCD Modular Division unit to achieve efficient ECSM operation over NIST curve P256. In the same year, i.e. Amiet et al.21 also developed a flexible ECSM architecture using an Iterative digit-digit Montgomery algorithm-based modular multiplication unit. The design reported by Salman et al.22 presents a scalable ECSM unit with mechanisms to prevent side-channel attacks employing Montgomery ladder as well as exponent randomisation to withstand DPA along with SPA. In fact, a cost-effective dual-field ECC processor utilising a word-based Montgomery modular multiplication algorithm was put forward by Lai and Huang23. In the period of 2019–2020, Islam et al.24,25 designed a high-throughput point multiplication module on the twisted Edward curve (Edwards25519) over a 256-bit prime field. In Yeh et al.26 produced an ECSM unit using a unique technique utilising signed binary representation (SBR) with the M-ary method for reducing the area as well as the energy usage while eschewing SPA. In Lee et al. developed a large field-size ECC processor utilising a novel Montgomery point multiplication (PM) algorithm for minimising the resource consumption while maximising the signal flow27. Using the Montgomery ladder approach, Hao et al. devised a lightweight ECSM architecture favouring the random Weierstrass curves over a prime field29. In Rashid et al. presented an area-optimised ECC processor for large field-size deploying Lopez-Dahab projective point arithmetic operations30. The article by Zhao et al.31 published in 2021 introduced an ECC processor on the binary field, providing an efficient modular inversion unit using the Itoh–Tsujii inversion algorithm. Between 2021 and 2022, Awaludin et al.32,35 demonstrated a fast ECSM module using the schoolbook long and Karatsuba multiplication technique for Generic Weierstrass Curves over a prime field. In Kieu-Do-Nguyen et al.33 described an area-efficient multi-functional ECC processor with a modular inversion unit incorporating the Binary Euclidean algorithm. In Kudithi and Sakthivel34 implemented an optimised hardware ECC architecture in affine coordinates. In Hu et al.36 suggested a low-hardware architecture for ECC processors, over GF(p) to be applied in embedded applications, that shows resiliency against SPA attacks.

The primary aim of our design is to achieve an architecture that demonstrates both low latency and high throughput and can be efficiently integrated with current high-speed wireless communication protocols. The major contributions of the research reported in this article, in each unit, are highlighted below:

-

A novel EdCPM module on a twisted curve (Edwards25519) has been proposed to accomplish fast computation and high security.

-

The EdCPM unit is designed in Jacobian coordinate instead of Affine coordinate to eliminate computationally intensive modular inversion operation.

-

An efficient hardware architecture for twisted Edward curve point operation has been designed for minimising arithmetic operations by utilising the parallelisation technique.

-

The point operation unit is capable of performing both point doubling (PD) as well as addition (PA) operations within a single operation using a unified point addition formula; thereby offering better resilience against side-channel attacks.

-

Multiplication and modular reduction operation are carried out separately utilizing fast reduction modulo as well as Booth radix-4 algorithms to minimise latency and hardware resources.

The subsequent sections of this article are organised along these lines: "Mathematical background" section briefly discusses group operations and field arithmetic on the twisted Edward Curve with relevant equations and algorithms. "Hardware architecture" section outlines proposed hardware architecture for the EdCC accelerator over Edwards25519. Then, "Implementation results" section highlights the implementation results as well as the comparative performance analysis of our EdPM architecture with other existing designs. Lastly, "Conclusions" section summarises and concludes this work.

Mathematical background

This section presents the mathematical concepts and algorithms associated with the modular arithmetic unit, group operation unit as well as point multiplication unit.

Finite field arithmetic

The arithmetic of Finite Fields, alias Galois Fields [GF(p)], is a mathematical abstraction of number systems wherein the set of elements in the field (F) is finite. The fundamental operations involved in field arithmetic are Addition and Multiplication. In finite field arithmetic, subtraction operation can be expressed as addition, where \(\left({\varvec{a}}, {\varvec{b}}\right)\in {\varvec{F}}\) and \({\varvec{a}}-{\varvec{b}}={\varvec{a}}+(-{\varvec{b}})\). Here,\(\left(-{\varvec{b}}\right)\in {\varvec{F}}\) such that \({\varvec{b}}+\left(-{\varvec{b}}\right)=0\). Likewise, inversion/division can be performed in the form of multiplication. However, the inversion unit can be excluded from the Jacobian coordinate system. The finite field’s order (q) denotes the elements’ number present in any field. As a rule, a finite field is classified as a prime field if its order q could be expressed as a prime power (\({\varvec{q}}={{\varvec{p}}}^{{\varvec{m}}}\)), where \({\varvec{m}}=1\) and p denotes a prime value7.

Modular addition as well as subtraction over GF(p) are fundamental cryptosystem operations. Equations (1) and (2) hold the mathematical notation of modular addition and subtraction respectively.

Here, x along with y are the numbers provided, p denotes the prime number and Z signifies the output. The output of the modular addition is derived through the summation of x as well as y (\({\varvec{x}}+{\varvec{y}}\)), followed by the deduction of p from (\({\varvec{x}}+{\varvec{y}}\)) as long as the resultant (Z) is not less than p. On the other hand, in modular subtraction, if \(({\varvec{x}}\ge {\varvec{y}})\), it could be promptly calculated by simple subtraction or using 2’s complement, whereas if (\({\varvec{x}}<{\varvec{y}}\)), then y is subtracted from (\({\varvec{x}}+{\varvec{p}}\)). However, modular reduction operation is less significant during modular addition and subtraction because the inputs x and y lie from 0 to p − 1, whereby Z must be \(\le 2{\varvec{p}}\). This paper proposes a combined modular addition and subtraction unit instead of two distinct modules for EdCCP18.

Modular multiplication is one of the most crucial design units to devise a high-performance cryptosystem, as implementing the modular multiplication over GF(p) requires much area and time compared with other modular arithmetic operations. Generally, the modular multiplication operation can be mathematically expressed by Eq. (3), where M and R are the provided numbers, p denotes the prime number and Z is the output. This research establishes two modules for modular multiplication: one of them for the regular multiplication operation while the other is for the modular reduction operation18.

Twisted Edward curve

The mathematical expression of a twisted Edward curve over the field k (\(k\ne 2\)) is expressed as follows:

Here, \(a,d\in GF(p)\backslash \{\text{0,1}\}\). In fact, if \({\varvec{a}}=1\), it is known as the untwisted Edwards curve. The specifications of the Edwards25519 over GF(p) are: \({\varvec{a}}=-1\), \(d=-121665/121666\) and \({\varvec{p}}={2}^{255}-19\)11,12. Selecting the twisted Edward curve over conventional elliptic curves presents several advantages. Firstly, the twisted Edward curve follows a unified addition law which supports point addition as well as doubling while preserving the identity. Moreover, the Twisted Edward curve saves computational time by offering fewer arithmetic operations than the standard curve24.

Projective homogeneous coordinate system

The curve \({e}_{a,d}\) can be represented within a projective homogeneous coordinate system, where a triplet (\(X, Y, Z\)) denotes every point (\(x, y\)). This triplet falls in with the affine point (\(x=Z/X, y=Z/Y\)), where \(Z\ne 0\). Thus, the allied projective twisted Edwards curve can be expressed as:

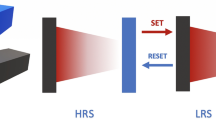

Several coordinate systems exist, e.g. the projective or Jacobian, affine, Chudnovsky and Lopez-Dahab projective coordinates, for point representation. However, for our research we chose Jacobian coordinates amongst the other popular ones for several reasons. First of all, Jacobian coordinates eliminate the inversion operation which is considered to be the most expensive division, reducing computations on the Edward curve. Secondly, it is possible to present the same affine point (x,y) by Z’s various values; hence, such points can be encoded using random values of Z that will offer an extra layer of security against side-channel attacks28.

Group law for twisted Edward curve

In twisted Edwards curve, (\(0, 1\)) signifies the zero or neutral element while the inverse of any point (\(x, y\)) is (\(-x, y\)). Let, both \(\left({X}_{1}:{Y}_{1}:{Z}_{1}\right)\) as well as \(({X}_{2}:{Y}_{2}:{Z}_{2})\) are to be the paired points on the projective twisted Edward curve while \(({X}_{3}:{Y}_{3}:{Z}_{3})\) is the sum of those points10. Then, \(({X}_{3}:{Y}_{3}:{Z}_{3})\) can be represented as:

Point multiplication

Computationally intensive point multiplication (PM) is considered to be the most significant function of an EdCC accelerator. Generally, the fundamental process of PM could be characterised as \(S=k.P\); while the P denotes a base point within the Edward curve, the k represents a confidential scalar (i.e. the secret/private key) where the S signifies another point within the curve that serves as the public key. Point multiplication can be executed by carrying out an array of point additions and doublings, adopting k’s binary bit sequence. The double-and-add method is considered the most forthright approach to execute PM, as outlined in Algorithm 6, wherein point doublings are executed in each cycle. In contrast, point additions are only carried out if \({{\varvec{k}}}_{{\varvec{i}}}=1\)19,24.

Algorithms

The algorithms used for various mathematical operations, including modular addition, modular reduction, multiplication, subtraction, unified point operation as well as point multiplication, are mentioned below.

Addition in GF(p)7

Subtraction in GF(p)7

Booth Radix-4 Multiplication12

Unified Twisted Edward Curve Point Operation15

Double and Add Algorithm for Point Multiplication15

Hardware architecture

High-performance EdCCP requires efficient designing of modular arithmetic, group operation and point multiplication units. This research proposes five hardware architectures for modeling an EdCCP, which will be elaborated on in this section.

Modular arithmetic unit

Combined modular addition-subtraction

The architecture shown in Fig. 3 starts functioning based on the selected operation (addition or subtraction) that must be carried out. Initially, out of two distinct predetermined values, one will be saved in registers depending on the operation selected. Then, an adder will perform the addition operation and hold the value. This value will be sent to the comparator, which will convert that value into a suitable range based on the selected operation. Finally, the outcome will be a 256-bit value for modular addition or subtraction.

The proposed hardware architecture for combined modular addition as well as subtraction.

Booth radix-4 multiplication unit

The diagram shown in Fig. 4 represents the Booth radix-4 multiplication, which operates following Algorithm 3. Following the reset operation, appropriate values will be stored in prod-reg, state-reg, Q-reg as well as result-reg. Subsequently, the values contained within the result-next, prod-next and state-next shall be modified. The multiplier as well as multiplicand values are be transferred to the prod-reg register as well as mcand-reg, respectively, at the time of the IDLE state. Then, an 8X1 multiplexer determines the proper computation depending on the result-next register’s three least significant bits (LSBs); this process will continue throughout the BUSY state. When the final value is reached by counter, a 512-bit value is generated as the multiplication output using 128 Clock Cycles.

The proposed hardware architecture for booth radix-4 multiplication.

Modular reduction unit

The proposed hardware architecture presented in Fig. 5 executes modular reduction operation and has been developed using the fast reduction modulo algorithm (refer to Algorithm 4). At the onset of the operation, nine values shall be generated utilising the fast reduction modulo algorithm. After that, all values will undergo processing through left-shifters, not gates and adders to satisfy the necessary addition operation. The outcome of this operation will then be combined with six different pre-defined values. Subsequently, the multiplexers will select the appropriate bits based on the values produced by the adder. Finally, the 256-bit result is achieved from 512-bit input using only one clock cycle.

The proposed hardware architecture for modular reduction.

Modular multiplication unit

Figure 6 illustrates the overall methodology underlying our proposed modular multiplication technique. The modular multiplication unit receives two inputs: a 256-bit multiplier as well as a 256-bit multiplicand. Initially, the two 256-bit inputs are processed through a Booth Radix-4 multiplication unit, resulting in a 512-bit output. Finally, the outcome of the multiplication module, which yields a 512-bit output, undergoes modular reduction architecture to attain a 256-bit output. The complete process of modular multiplication necessitates 129 clock cycles, comprising 128 cycles for multiplication and an additional cycle for modular reduction.

The proffered modular multiplication architecture’s block diagram.

Group/point operation unit

Elliptic curve group operations comprise modular adders, subtractors, multipliers and squares, distributed across multiple levels to execute point multiplication operations. The group operation module is designed in projective coordinates according to the Unified Point Operation algorithm, as mentioned in Algorithm 5. Figure 7 depicts this unit’s hardware design, which has six successive levels that cost thirteen modular multipliers, one modular square operator, two modular additions operators and two modular subtraction operators denoted as (13 M + 1S + 4A). The six distinct levels are shown here to visualise the parallelisation that takes place in the overall operation. In order to reduce arithmetic operations and latency, the proposed group operation architecture is optimised using parallelisation techniques across various levels. In this design, modular multiplication and squaring necessitate m/2 + 1 clock cycles, while modular addition as well as subtraction require a single clock cycle to complete the operation. Here, m denotes the total count of bits involved per operation. In addition, computational complexity of a level is determined by squaring as well as multiplication operations. Levels having squaring and multiplication require m/2 + 1 clock cycles, while levels without squaring or multiplication require only one cycle to proceed to the following level. Thus, the total clock cycles (CCs) needed for the group operation unit is (5 m/2 + 6) CCs. Thus, for 256-bit, the latency (i.e. CCs) for group operation is 646 CCs.

Proposed hardware architecture for unified point operation.

Point multiplication unit

Figure 8 depicts the proposed EdCPM over the prime field using efficient group operations in Jacobian coordinate. The double and add algorithm is utilised for completion of the proposed point multiplication scheme, as outlined in Algorithm 6. The unified point operation module performs both PD and PA in Jacobian coordinates. The input of PA and the output of PD are compared using the comparative unit. The output of EdCPM is defined as k.P, while k (key) denotes a private key, P denotes a point within the twisted Edward curve. In EdCPM architecture, the input of PD is P (Px, Py, Pz) and the output is Q (Q2x, Q2y, Q2z). The input of PA is P (Px, Py, Pz) + Q (Q2x, Q2y, Q2z) and the output is (Q2px, Q2py, Q2pz). The output of the bit patterns of the input key depends upon the MUX2 output. The total clock cycles required for EdCPM is computed by: CCEdCPM = (m − 1) (CCEdUPO) = (m − 1) (5 m/2 + 6) = (5m2/2 + 7 m/2 − 6). For 256-bit EdCPM, CCEdUPO = 164,730 clock cycles.

Proposed point multiplication hardware architecture.

Implementation results

This section analyses and reports the post-synthesis performance of the preferred modular arithmetic architectures, a point operation unit and a point multiplication unit over GF(p). The proffered EdCC accelerator has been materialised utilising Xilinx ISE 14.5 Design Suite, which was synthesised on the Virtex-5 (xc5vl50t-2ff1136) FPGA platform. The simulations were performed utilising Modelsim and Isim, while the outcomes were verified employing the Maple software. On the Virtex-5 FPGA, the maximum frequency of the proposed modular arithmetic, point operation and point multiplication modules is 117.809 MHz.

Various multiplication architectures have been designed which is depicted in Table 1, among them Booth radix-4 shows the best hardware performance. After that, the best multiplication hardware (Booth radix-4) is selected for modular multiplication with the help of our designed modular reduction module. Based on the implementation results in Table 1, Booth Radix-4 multiplication with the fast reduction modulo is by far the most efficient hardware implementation approach both in terms of optimized area and time having 1290(4%) slices, 4915(17%) LUTs, 584(10%) FFs and 2.04 µs delay. All hardware architectures have been implemented on Virtex-5 FPGA.

A comparative analysis with other relevant works has been presented, in this section, to demonstrate the efficacy of the proposed research. This work employs a unified design approach for modular addition and subtraction instead of discrete execution of these operations to minimise hardware resources. The combined modular addition and subtraction unit operates within a single clock cycle. Thus, this architecture requires only 0.575 ns and 4% of the available slice LUTs for a 256-bit prime field. The proposed modular multiplication architecture is developed by merging the Booth Radix-4 multiplication algorithm as well as the fast reduction modulo algorithm. This modular multiplication approach utilises 1290 slices (constituting 4% of the total), 4915 LUTs (17%), and 584 FFs (10%) and incurs a delay of 2.04 µs. The total count of clock cycles necessary for conducting the multiplication can be determined as (128 + 1) due to the utilisation of the Booth Radix-4 multiplication algorithm, which simultaneously processes two (2) bits and the modular reduction operation, which necessitates one clock cycle. Consequently, the time required for executing the modular multiplication operation calculated to be (15.832 ns × 129), which equals to 2.04 microsecond in Virtex-5 FPGA over GF (256). Furthermore, our proposed architecture for the point operation module on the twisted Edward curve is based on the unified point operation algorithm. The implementation results reveal that it only takes 3102 slices (10% of the available slices) for a prime field of 256-bit in Virtex-5 FPGA. The average time of the point operation unit is (646 X 8.48 ns) = 5.48 µs at 117.809 MHz frequency, where the rate of throughput of this unit is (256/5.48 µs) = 46.72 Mbps. The Edward Curve point multiplication (EdPM) module is designed using the high-performance modular arithmetic and point operation unit that utilises the Double and Add algorithm for optimal efficiency. The EdPM unit exhibits a latency of 164,730 clock cycles, while it requires 1.4 ms to execute single-point multiplication for any 256-bit key with a throughput of 183.38 kbps. Table 2 summarises the implementation outcomes of the proffered EdCCP for a 256-bit prime field.

Table 3 presents performance comparisons of our proposed point multiplication (PM) unit and other avant-garde point multiplication designs over GF(p). Hossain et al., 2016 proposed a PM architecture, adopting a Double and Add algorithm that takes 5.26 ms with a corresponding throughput of 48.67 Kbps for executing a point multiplication operation over the prime curve p-25619. The proposed accelerator exhibits better speed and throughput compared to the one proposed in19. Marzouqi et al.20 put forward an ECC processor architecture based on RSD that consumes 397,300 CCs to perform a point multiplication, almost 2.5 times greater than our proposed design. Amiet et al.21 designed a PM architecture using Virtex-7 FPGA platform that completes a point multiplication in 1.49 ms; however, the CCs requirement of this design is higher (335,360). Salman et al.22 engineered a PM scheme with countermeasures to side-channel attacks where the throughput rate is 34.57 Kbps. Our design offers better latency and side-channel attack resilience due to utilising a unified point operation algorithm than the design recommended in22. The dual field PM architecture reported by Lai and Huang23 necessitates 2.66 ms time which is higher than our design. Our proposed PM architecture shows better design performance with respect to latency compared with that of the other reported designs24,28,29,33,34. The processor documented in research by Hu et al.36 is reconfigurable in terms of various field orders as well as immune to the side-channel attacks. In addition, computational costs of the design in36 for point multiplication are 610 k clock cycles, whereas our proposed design exhibits lower computational costs of 164.7 k clock cycles for point multiplication. Its ECPM performance requires 29.84 ms, almost 20 times higher than our design. Therefore, our proposed EdCC hardware accelerator will advance the rapid data encryption process especially in high-speed wireless communication networks. The implementations in37,38 used Intel Agilex, which uses superior technology compared to our Virtex-5. Hence, these implementations can achieve higher clock speeds, lower latency and further acceleration through specialised DSP units. Therefore, our proposed implementation is to yield better results on the Intel Agilex FPGA platform. Besides, Choi et al. proposed an ECC processor with variable partial product bit38. Their FPGA implementation resource usage depends on the selection of partial product bit-width. Both40,41 presented unconventional architectures, based on residue number system and double-point multiplier respectively, both of which achieved a very high throughput but cost more FPGA resources. In42, the authors proposed a low-resource using ECC, which traded off substantial throughput. A pipelined approach was proposed in43, where the authors achieved high performance on their Atrix-7 FPGA with field size of 251. However, the resource usage was significantly higher compared to the other works.

In terms of latency, our point multiplication module requires only 164,730 clock cycles to perform a single-point multiplication, which is significantly lower than many existing designs (e.g.,19,20,21,22,23,24,28,29,33,34,36). As for throughput, our design achieves a throughput of 183.38 kbps, which is higher than most of the compared works (e.g.,19,20,22,23,24,28,29,33,34,36). Considering the area efficiency, our modular multiplication unit uses only 1290 slices (4% of the total available slices) on the Xilinx Virtex-5 FPGA platform, which is highly efficient compared to other designs.

The clock cycles and computation time of our design are quite competitive, ensuring that our design is more efficient for modern high-speed wireless communication standards. Although our designs are implemented in an earlier FPGA technology (Virtex-5), which has higher power consumption and fewer input/output blocks (IoBs), it achieves better outcomes than the other relevant designs.

Conclusions

Within the scope of this research, a high-speed point multiplication architecture for the EdCC hardware accelerator has been developed using the Edwards25519 curve in a projective coordinate system. An efficient modular multiplier is implemented by adopting Booth Radix-4 Multiplication and Fast modular reduction, which necessitates 129 CCs to multiply two 256-bit integers. A new hardware structure for a group operation unit using a unified point operation algorithm is proposed that requires 646 CCs to execute a single operation. The point multiplication module utilises a double and add always algorithm for faster computation. The designs have been employed on Xilinx Virtex-5 FPGA platform, on a 256-bit prime field. It has been observed that our proposed accelerator completes a point multiplication operation in 164,730 clock cycles, while the processing time is 1.4 ms having a throughput of 183.38 kbps. Our proposed design offers better efficiency in both latency and throughput without compromising security. The comprehensive performance analyses infer that this EdCC will definitely be a viable option for fast and secured data encryption.

Data availability

All data generated or analysed during this study are included in this published article.

References

Ramadan, R. & Yadav, K. A novel hybrid intrusion detection system (IDS) for the detection of internet of things (IoT) network attacks. Ann. Emerg. Technol. Comput. (AETiC) 4(5), 61–74. https://doi.org/10.33166/AETiC.2020.05.004 (2020).

Farooq, H., Rehman, H., Javed, A., Shoukat, M. & Dudley, S. A Review on smart IoT based farming. Ann. Emerg. Technol. Comput. 4(3), 61–74. https://doi.org/10.33166/AETiC.2020.03.003 (2020).

Zaman, K. S. et al. Minimum signed digit approximation for faster and more efficient convolutional neural network computation on embedded devices. Eng. Sci. Technol. Int. J. 36, 101153. https://doi.org/10.1016/j.jestch.2022.101153 (2022).

Ullah, S. et al. Elliptic curve cryptography applications, challenges, recent advances, and future trends: A comprehensive survey. Comput. Sci. Rev. 47, 100530. https://doi.org/10.1016/j.cosrev.2022.100530 (2023).

Rivest, R. L., Shamir, A. & Adleman, L. A method for obtaining digital signatures and public-key cryptosystems. Commun. ACM 21, 120–126. https://doi.org/10.1145/359340.359342 (1978).

Miller, V. S. Use of elliptic curves in cryptography. Lect. Notes Comput. Sci. 218, 417–426. https://doi.org/10.1007/3-540-39799-x_31 (1986).

Koblitz, N. Elliptic curve cryptosystems. Math. Comput. 48, 203–209. https://doi.org/10.1090/S0025-5718-1987-0866109 (1987).

Bernstein, J., Birkner, P., Lange, T. & Peters, C. ECM using Edwards curves. Math. Comput. 82, 1139–1179. https://doi.org/10.1090/s0025-5718-2012-02633-0 (2012).

Fan, J., Guo, X., De Mulder, E., Schaumont, P., Preneel, B. & Verbauwhede I. State-of-the-art of secure ECC implementations: a survey on known side-channel attacks and countermeasures. In 2010 IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), Anaheim, CA, USA, 76–87, (2010). https://doi.org/10.1109/HST.2010.5513110

Zulberti, L. et al. A script-based cycle-true verification framework to speed-up hardware and software co-design: Performance evaluation on ECC accelerator use-case. Electronics 11, 3704. https://doi.org/10.3390/electronics11223704 (2022).

Bernstein, J. & Lange, T. Faster addition and doubling on elliptic curves. Adv. Cryptol. ASIACRYPT 4833, 29–50. https://doi.org/10.1007/978-3-540-76900-2_3 (2007).

Brier, É. & Joye, M. Weierstraß elliptic curves and side-channel attacks. Public Key Cryptography 2274, 335–345. https://doi.org/10.1007/3-540-45664-3_24 (2002).

Hisil, H., Wong, K.-H., Carter, G. & Dawson, E. Twisted Edwards curves revisited. Adv. Cryptol. ASIACRYPT 5350(2008), 326–343. https://doi.org/10.1007/978-3-540-89255-7_20 (2008).

Barnard, E. M. Tutorial of twisted Edwards curves in elliptic curve cryptography, (2015). http://koclab.cs.ucsb.edu/teaching/ecc/project/2015Projects/Barnard-Paper.pdf

Liu, Z., Liu, D. & Zou, X. An efficient and flexible hardware implementation of the dual-field elliptic curve cryptographic processor. IEEE Trans. Industr. Electron. 64, 2353–2362. https://doi.org/10.1109/TIE.2016.2625241 (2017).

Baldwin, B., Moloney, R., Byrne, A., McGuire, G. & Marnane, W. P. A hardware analysis of twisted edwards curves for an elliptic curve cryptosystem. Lect. Notes Comput. Sci. 5453, 355–361. https://doi.org/10.1007/978-3-642-00641-8_41 (2009).

Hossain, M. R. & Hossain, M. S. Efficient FPGA Implementation of Modular Arithmetic for Elliptic Curve Cryptography. In 2019 International Conference on Electrical, Computer and Communication Engineering (ECCE), (2019). https://doi.org/10.1109/ecace.2019.8679419.

Hossain, M. R., Hossain, M. S., Kong, Y. Efficient FPGA Implementation of Unified Point Operation for Twisted Edward Curve Cryptography. In 2019 International Conference on Computer, Communication, Chemical, Materials and Electronic Engineering (IC4ME2), (2019). https://doi.org/10.1109/ic4me247184.2019.9036635.

Hossain, M. S., Kong, Y., Saeedi, E. & Vayalil, N. C. High-performance elliptic curve cryptography processor over NIST prime fields. IET Comput. Digital Tech. 11, 33–42. https://doi.org/10.1049/iet-cdt.2016.0033 (2016).

Marzouqi, M. A., Salah, K., Schinianakis, D. & Stouraitis, T. A high-speed FPGA implementation of an RSD-based ECC processor. IEEE Trans. Very Large Scale Integr VLSI Syst. 24, 151–164. https://doi.org/10.1109/tvlsi.2015.2391274.D (2016).

Amiet, D., Curiger, A. & Zbinden, P. Flexible FPGA-based architectures for curve point multiplication over GF(p). In 2016 Euromicro Conference on Digital System Design (DSD), (2016). https://doi.org/10.1109/dsd.2016.70.

Salman, A., Ferozpuri, A., Homsirikamol, E., Yalla, P., Kaps, J.-P. & Gaj, K. A scalable ECC processor implementation for high-speed and lightweight with side-channel countermeasures. 2017 International Conference on ReConFigurable Computing and FPGAs (ReConFig), (2017). https://doi.org/10.1109/reconfig.2017.8279769.

Lai, J. Y. & Huang C. T. Elixir: High-throughput cost-effective dual-field processors and the design framework for elliptic curve cryptography. In IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 16, 1567–1580, (2008). https://doi.org/10.1109/tvlsi.2008.2001239.

Islam, M. M., Hossain, M. S., Hasan, M. K., Shahjalal, M. & Jang, Y. M. FPGA implementation of high-speed area-efficient processor for elliptic curve point multiplication over prime field. IEEE Access 7, 178811–178826. https://doi.org/10.1109/access.2019.2958491 (2019).

Islam, M. M., Hossain, M. S., Hasan, M. K., Shahjalal, M. & Jang, Y. M. Design and implementation of high-performance ECC processor with unified point addition on twisted Edwards curve. Sensors 20, 5148. https://doi.org/10.3390/s20185148 (2020).

Yeh, L.-Y., Chen, P.-J., Pai, C.-C. & Liu, T.-T. An energy-efficient dual-field elliptic curve cryptography processor for internet of things applications. IEEE Trans. Circuits Syst. II Exp. Briefs 67, 1614–1618. https://doi.org/10.1109/tcsii.2020.3012448 (2020).

Lee, C.-Y., Zeghid, M., Sghaier, A., Ahmed, H. Y. & Xie, J. Efficient hardware implementation of large field-size elliptic curve cryptographic processor. IEEE Access 10, 7926–7936. https://doi.org/10.1109/access.2022.3141104 (2022).

Wang, J. et al. Dynamic Scalable elliptic curve cryptographic scheme and its application to in-vehicle security. IEEE Int. Things J. 6, 5892–5901. https://doi.org/10.1109/jiot.2018.2869872 (2019).

Hao, Y. Lightweight architecture for elliptic curve scalar multiplication over prime field. Electronics 11, 2234. https://doi.org/10.3390/electronics11142234 (2022).

Rashid, M. et al. Large field-size elliptic curve processor for area-constrained applications. Appl. Sci. 13, 1240. https://doi.org/10.3390/app13031240 (2023).

Zhao, X. et al. FPGA implementation of high-efficiency ECC point multiplication circuit. Electronics 10, 1252. https://doi.org/10.3390/electronics10111252 (2021).

Awaludin, M., Larasati, H. T. & Kim, H. High-speed and unified ECC processor for generic weierstrass curves over GF(p) on FPGA. Sensors 21, 1451. https://doi.org/10.3390/s21041451 (2021).

Kieu-Do-Nguyen, B., Pham-Quoc, C., Tran, N.-T., Pham, C.-K. & Hoang, T.-T. Low-cost area-efficient FPGA-based multi-functional ECDSA/EdDSA. Cryptography 6, 25. https://doi.org/10.3390/cryptography6020025 (2022).

Kudithi, T. & Sakthivel, R. High-performance ECC processor architecture design for IoT security applications. J. Supercomput. 75, 447–474. https://doi.org/10.1007/s11227-018-02740-2 (2019).

Awaludin, M., Park, J., Wardhani, R. W. & Kim, H. A high-performance ECC processor over Curve448 based on a novel variant of the Karatsuba formula for asymmetric digit multiplier. IEEE Access 10, 67470–67481. https://doi.org/10.1109/access.2022.3184786 (2022).

Hu, X., Zheng, X., Zhang, S., Cai, S. & Xiong, X. A low hardware consumption elliptic curve cryptographic architecture over GF(p) in embedded application. Electronics 7, 104. https://doi.org/10.3390/electronics7070104 (2018).

Wu, G., He, Q., Jiang, J., Zhang, Z., Long, X. & Zhao, Y. A High-Performance hardware architecture for ecc point multiplication over Curve25519. In IEEE 30th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), (2022). https://doi.org/10.1109/FCCM53951.2022.9786192.

Wu, G. et al. E-booster: A field-programmable gate array-based accelerator for secure tree boosting using additively homomorphic encryption. IEEE Micro 43, 88–96. https://doi.org/10.1109/MM.2023.3293845 (2023).

Choi, P., Lee, M.-K., Kim, J.-H. & Kim, D. K. Low-complexity elliptic curve cryptography processor based on configurable partial modular reduction over NIST prime fields. IEEE Trans Circuits Syst. II Exp. Briefs 65, 1703–1707. https://doi.org/10.1109/TCSII.2017.2756680 (2018).

Asif, S., Hossain, M. S., Kong, Y. & Abdul, W. A fully RNS based ECC processor. Integration 61, 138–149. https://doi.org/10.1016/j.vlsi.2017.11.010 (2018).

Mosanaei-Boorani, H. & Bayat-Sarmadi, S. A digital signature architecture suitable for V2V applications. IEEE Trans Circuits Syst. I Regul. Pap. 71, 731–739. https://doi.org/10.1109/TCSI.2023.3337121 (2024).

Kudithi, T. & Sakthivel, R. An efficient hardware implementation of the elliptic curve cryptographic processor over prime field. Int. J. Circuit Theory Appl. 48, 1256–1273. https://doi.org/10.1002/cta.2759 (2020).

Anandakumar, N. N. et al. Field Programmable gate array based elliptic curve Menezes-Qu-Vanstone key agreement protocol realization using physical unclonable function and true random number generator primitives. IET Circuits Dev. Syst. 16, 382–398. https://doi.org/10.1049/cds2.12111 (2022).

Acknowledgements

This research was supported by the Xiamen University Malaysia through XMUMRF/2020-C6/IECE/0016 and XMUMRF/2021-C8/IECE/0025 grants as well as the Independent University Bangladesh (IUB) through VCRF-SETS:24-021.

Author information

Authors and Affiliations

Contributions

M.R.H. wrote the main manuscript text, M.S.R. prepared all the figures, M.A.S.B., T.J.Y. and M.H.M. supervised the project, W.E.F. and C.C.K analysed the data, K.H.Z., M.A.S.B. and M.H.M. addressed the review comments. All authors reviewed the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Hossain, M.R., Rahman, M.S., Zaman, K.S. et al. Low latency FPGA implementation of twisted Edward curve cryptography hardware accelerator over prime field. Sci Rep 15, 15097 (2025). https://doi.org/10.1038/s41598-025-99100-x

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-99100-x