Abstract

The conventional full power converter (FPC) for battery energy storage applications is limited by bulky components and suboptimal efficiency. In response, a series-connected step-up/down partial power converter (SUDPPC) with high power density is proposed in this paper. It consists of an LLC resonant converter operating at a fixed switching frequency cascaded with a full-bridge converter capable of providing bipolar output. By connecting the SUDPPC in series with the load, the voltage stress on the series side and the current stress on the parallel side are markedly reduced. The four-quadrant function provides support for further optimization of the rated power level. Universal series interconnection schemes are elaborated, and design guidelines are formulated based on power distribution characteristics. Furthermore, the topology is evaluated in terms of nonactive power and component stress factor (CSF), and benchmarked against a four-switch buck/boost FPC and a phase-shifted full-bridge step-up partial power converter (SUPPC). Finally, a 1.1 kW prototype is developed to experimentally validate the theoretical analysis, demonstrating that only 14.3% of the total active power is processed under full-load conditions, with a peak efficiency of 98.15%.

Similar content being viewed by others

Introduction

In emerging battery energy storage applications, the bidirectional dc-dc converter serves as a critical interface between the battery and the dc bus, with its performance exerting a significant impact on overall system efficiency1,2. Depending on voltage levels, noise sensitivity, and current requirements, both isolated topologies using high-frequency transformers and non-isolated configurations3,4 may be adopted. However, conventional parallel schemes are based on full power processing, in which the voltage and current stresses of components are governed by steady-state power, resulting in elevated conduction losses5.

In contrast, partial power processing (PPP) has been recognized as a promising approach for achieving compact and efficient regulation6. Its primary goal is to reduce component ratings, physical dimensions, and power losses7. Rather than refining converter topologies, soft-switching techniques, or control strategies, PPP systems are characterized by a direct infeed path that transfers the majority of power6,8,9. As shown in Fig. 1, only a small fraction of the total power is processed by the series-connected partial power converter (PPC), while the remainder is delivered to the load without conversion loss10,11,12. Consequently, regulation is accomplished using low-rated components, leading to notable enhancements in power density and conversion efficiency13,14,15. This unique connectivity makes the PPC particularly suitable for applications such as traction powertrains, photovoltaic (PV) systems, battery energy storage, and data-center power delivery.

However, the effectiveness of converter series operation in fulfilling PPP has been questioned in previous studies. In certain implementations, the PPC reduces only the active power flow while neglecting the reactive component, which may lead to decreased overall system efficiency16,17. This inefficiency stems from the interaction between active and nonactive power, which jointly influence component losses. Moreover, even when PPP is successfully realized, optimal performance requires careful consideration of trade-offs among connectivity configurations, topology choices, and parameter design.

Most of the works carried out in PPC-based are focused on either step-up (SUPPC) or step-down (SDPPC) operation. If the series port (SP) voltage is designed as bipolar, i.e., the conversion system is managed by SUDPPC, the power processing level can be further reduced. In18, a SUDPPC intended for offshore wind farm applications is implemented using a dual active bridge converter combined with an unfolder circuit, which only inverts the SP voltage polarity without providing active regulation. Consequently, the transition near zero-voltage becomes challenging, though it remains essential in specific operational scenarios. In10, four-quadrant switches are configured on the secondary side of a phase-shifted full-bridge (PSFB) converter, where the negative output voltage is achieved by forcing the inductor current to flow back into the input source. However, this method is characterized by a complex dynamic model, making it relatively challenging to control and analyze. Similar concepts are also discussed in19,20,21,22. Another SUDPPC topology with mode switching achieved via additional switches is conducted in23, where control must be temporarily interrupted to avoid overshoot as the bias voltage approaches zero. It should be noted that none of the above studies systematically evaluated the effectiveness of PPP.

To present the relevant content, a SUDPPC topology consisting of an LLC resonant converter and a full-bridge (FB) converter is developed in this paper. The LLC operates in a high-efficiency resonant state and provides galvanic isolation, while the FB converter achieves system regulation by managing the SP voltage or current. The topology is evaluated in terms of nonactive power and the component stress factor (CSF), and a detailed comparative analysis is conducted with a unipolar SUPPC employing PSFB and a four-switch buck-boost (FSBB) full power converter (FPC). The results indicate that the SUDPPC yields the lowest total circulating energy and the highest component utilization. In addition, the universal connection schemes and corresponding selection guidelines for PPC are presented. Finally, the modeling and control design of the proposed SUDPPC are presented, followed by hardware verification and conclusions.

Interface configurations and performance metrics for PPC

To support configuration selection tailored to specific requirements, universal interface schemes and associated power distribution characteristics are examined. Besides, key performance metrics for evaluating different topologies are introduced.

Classification of interface configurations

The PPC functions as a power shunt, with one port connected in series between the battery and the dc bus, while the other port is connected in parallel to either side. As depicted in Fig. 2, PPCs are primarily categorized into step-up and step-down types, with the series path and corresponding power flow direction indicated by red lines and arrows. Without loss of generality, the battery pack is assumed to be in a charging state.

In Fig. 2, the PPC connected in parallel with the dc bus is categorized as type A, otherwise it is designated as type B. Here Vdc and Idc represent the dc bus voltage and current, while Vb and Ib denote the battery voltage and current, respectively. It is obvious that the operating conditions of PPC are strongly influenced by the interface configuration. The SU-A configuration can be derived by changing the SP voltage polarity of the SD-A, which is accompanied by a reversal of the converter power flow direction. Therefore, when the SP voltage exhibits bipolar characteristics, SU-A and SD-A (as well as SU-B and SD-B) possess identical power handling capabilities, and bidirectional switching devices are required.

It should be emphasized that a shared reference ground is inherently formed between the input source and the load in a series-connected PPC. Nevertheless, utilizing an isolation transformer is strongly recommended to mitigate short-circuit risks. As mentioned in10, Rakoski Zientarski et al. demonstrated that only isolated converters with non-unity transformer turns ratio can fully realize PPP. In fact, minimizing the stress on the switching device is essential for ensuring proper PPP operation. Significant reduction in conduction losses can only be achieved by simultaneously avoiding rated voltage and current, a challenge effectively addressed by the series configuration of isolation topologies.

Active power processing

Based on the analysis conducted in this study, the PPC characteristics are investigated using the SD-A as a representative case. The SP shares the same current as the battery, and its blocking voltage is denoted as ΔV (ΔV =|Vdc-Vb|). Therefore, the power relationship of the SD-A can be described as

where Pout is the output active power, and Pd is the active power delivered by the direct infeed path. Pp refers to the active power processed by the PPC, which may be unidirectional or bidirectional. V2 represents the voltage of SP.

The allocation mechanism for power transfer can be defined by Eq. (2).

where the power processing factor (PPF) and PPF* indicate the fractions of active power processed by the PPC and the direct infeed path, respectively. When PPF equals zero, energy is transmitted solely through the direct infeed path, achieving an ideal efficiency of 100%. As the PPF increases and gradually becomes greater than unity, the system rated or higher active power is processed by the converter, contradicting the principle of PPP.

Here, Vdc is normalized to unity, and ΔV is conceived as a dimensionless parameter that varies with the battery voltage. Following similar calculations, the PPF and PPF* considering the bipolar SP voltage of the PPCs are summarized in Table 1. It is clear that a smaller ΔV facilitates a lower converter power level. When the directly fed power exceeds the system rating (i.e., PPF* > 1), the surplus is pushed back to the input through the converter, thereby increasing the processed power. For instance, with a positive SP voltage, the SU-B exhibits a higher PPF compared to SU-A. Hence, PPCs should be selected according to specific criteria to ensure operation within an optimal voltage range.

This study is conducted using a 48 V dc bus within a low-voltage power system, commonly utilized in residential energy storage systems, communication infrastructure, and data centers. To achieve optimal voltage matching, a 50 Ah lithium-ion battery from LG Chem is employed, as shown in Fig. 3(a), with a voltage range of 40–56 V. Constant current (CC) control is implemented to ensure stability and predictability in energy transfer between the battery and the dc bus. To mitigate performance degradation, the battery is operated above a 10% state of charge (SOC), as generally recommended. The power distribution characteristics of SU-A/SD-A and SU-B/SD-B under bipolar SP voltage conditions are illustrated in Figs. 3(b) and (c). Only 14.3% of the total active power is handled by SU-A/SD-A at full load, compared to 16.7% by SU-B/SD-B., indicating that SU-A/SD-A offers a more size and stress efficient component design. Additionally, in the SU-B/SD-B configuration, the battery current is split between the input and output branches of the PPC, complicating the implementation of CC control.

Performance evaluation metrics

The switching actions of semiconductor devices induce internal energy circulation without delivering power to the load, introducing the concept of nonactive power10. In PPC, achieving high efficiency presupposes that the nonactive power is also partially processed, since it represents the circulating energy that affects the component size and losses. As discussed in16, PPC implemented with a buck-boost converter exhibits nearly identical circuit pattern and efficiency performance as a conventional boost converter, even though its PPF is below unity. Moreover, a similar behavior is observed in a series-connected flyback converter23, where the coupled inductors transfer more nonactive power than the isolation transformer. These systems are fundamentally constrained from achieving PPP due to excessive nonactive power circulation, substantially degrading converter efficiency.

For inductors and capacitors, the nonactive powers NL and NC can be calculated based on the energy absorbed and released during the switching period Ts17.

where \(\alpha {T_s}\) is the moment of transition between energy absorption and release. Note that for the passive component responsible for filtering, Eq. (3) can be simplified to Eq. (4) using the small ripple approximation.

where \({\bar {i}_L}\) and \(\Delta {i_L}\) represent the average current and current ripple of the inductor, and \({\bar {v}_c}\) and \(\Delta {v_c}\) represent the average voltage and voltage ripple of the capacitor. The total nonactive power managed by the PPC is expressed as the sum of the aforementioned components. Full compliance with the PPP principle is achieved only when both active and nonactive power in the conversion system are partially processed under identical operating conditions.

Besides, as a key complementary metric for evaluating converter performance24,25,26,27, the CSF provides a dimensionless result by calculating the apparent power of each component.

where V* and I* are determined depending on the component properties, as shown in Table 2.

Based on the values presented in Table 2, the voltage and current stresses of the components are related by the CSF, which indirectly serves as an auxiliary metric for comparing conduction losses across different topologies. Therefore, weight factors can be assigned according to the component on-resistance to adapt to different scenarios, and they are set to 1 in this paper.

Configuration selection guidelines

Indeed, reducing the maximum power rating of the PPC should be prioritized in configuration selection, as it dictates component specifications28. In most practical scenarios, system input or output parameters are typically fixed, such as a stable dc bus voltage in battery charging systems29 or a regulated output voltage in onboard electronics. Additionally, the load may exhibit CC30 or constant-power31,32 characteristics. Based on the analysis presented in Table 1, selection guidelines for PPCs are systematically derived and illustrated in Fig. 4, with key conclusions summarized below.

-

i.

Unipolar PPC: For systems operating with a positive SP voltage, SU-A is preferred for step-up applications, whereas SD-B is more suitable for step-down conversion. In contrast, under a negative SP voltage, SD-A and SU-B are optimally employed for step-up and step-down operations, respectively. A review of previous studies reveals that SU-B has been utilized in certain unidirectional step-up systems with positive SP voltage33, while a similar misconception is observed in step-down converters implemented with SD-A31,34. Although these PPCs enable substantial reductions in processed power, they remain limited by issues related to power backflow.

-

ii.

Bipolar PPC with constant power loads: When the input voltage is fixed, configurations based on the SU-B/SD-B scheme are more suitable, as they yield the lowest peak PPF across the output voltage range [see Fig. 3(c)]. Conversely, SU-A/SD-A enables reduced converter ratings when the output voltage is held constant. In summary, the port with variable voltage should be preferentially selected for parallel connection.

-

iii.

Bipolar PPC with CC loads: When the voltage difference is symmetrically distributed between the positive and negative directions, SU-A/SD-A performs superiorly in handling input/output voltage variations. In cases of asymmetric voltage distribution, a comparative analysis supported by detailed calculations is required.

It is worth noting that the guidelines in Fig. 4 are applicable across different power and voltage levels, and the optimal PPC configuration can therefore be selected according to the operating conditions. For instance, in a dc-dc converter with a given rated power and fixed input voltage, SU-B and SD-B are generally preferred when the input and output voltage ranges overlap, independent of the specific voltage and power levels.

Despite its broad application prospects, the PPC topology exhibits pronounced audio susceptibility to input variations due to its direct feed path, which allows disturbances to be directly coupled to the output. As a result, advanced control schemes with strong disturbance-rejection capability are desirable for PPCs. Moreover, the series operation of PPC results in a narrow voltage regulation range, making it unsuitable for high-ratio applications. On the other hand, implementing the SUDPPC with a bipolar port requires additional power switches, which introduces a trade-off between operating efficiency and hardware cost.

Analysis of the proposed SUDPPC

In view of the preceding analysis, the SD-A configuration is adopted as the optimal power level implementation for the SUDPPC, with its operating principles, parameter tuning, and control design discussed in this section.

Operating principle

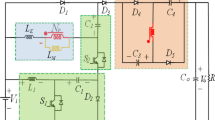

Figure 5 illustrates the proposed SUDPPC topology and its four-quadrant operation, where the front-stage is equipped with an LLC converter operating in open-loop resonant point to provide current isolation and soft-switching capabilities. The output voltage (i.e., SP voltage) V2 of the subsequent FB converter is determined by the equivalent duty cycle d, i.e., V2 = Vdc⋅d/n. The value of d ranges from − 1 to 1, and n is the turns ratio of the transformer. Current control is achieved using a current-loop scheme with a high-bandwidth proportional-integral (PI) controller, Gic(s).

From the series relationship in Fig. 5, the input to output voltage gain G can be expressed as:

Taking battery charging as an example, the key waveforms of the SUDPPC operating in step-up/down mode are shown in Fig. 6, where the red shaded area indicates the switches performing synchronous rectification (SR) in the FB converter. ILf, ILr, and ILm represent the currents flowing through the filter inductor Lf, the resonant inductor Lr, and the magnetizing inductor Lm, respectively. Vds and Ids correspond to the voltage and current of power switch.

As indicated by the rectified current, the SUDPPC transfers power from the parallel side to the series side in step-up mode, whereas the power flow reverses in step-down mode. The sinusoidal resonant current waveform confirms that the LLC converter operates precisely at the resonant point. The FB converter employs unipolar frequency doubling modulation to reduce the effective period of the inductor current, thereby suppressing high frequency ripple. Specifically, MOSFETs S9 and S11 use different modulation waves to generate duty cycles d1 and d2, respectively, with the FB converter’s equivalent duty cycle given by d = d1-d2. The gate signals for the same leg are maintained in a logically complementary state, with an appropriate dead time inserted. Therefore, this topology can easily achieve zero-voltage stable output and four-quadrant operation.

Parameter tuning

The transformer turns ratio n has a significant impact on circulating nonactive power and component utilization, and its maximum permissible value nmax is constrained by the duty ratio.

The duty cycle behavior for different values of n is reported in Fig. 7, where n = 5 is identified as an appropriate choice, providing a 16.7% control margin to account for non-idealities.

To satisfy the soft-switching in the LLC converter, ILm must fully discharge the output capacitors Coss of the primary switches within the dead time td.

Here, fs denotes the LLC converter switching frequency, which is set to 100 kHz in this paper, and td is obtained from the double-pulse test and equals 200 ns. Accordingly, the constraints for Lm is derived.

Further, the resonant capacitor Cr and Lr can be determined by Eq. (9).

where Pmax is the maximum power processed by SUDPPC, and the quality factor Q is taken as 0.57.

The peak values of ILr and the resonant capacitor voltage VCr can be further obtained35:

where Vd is the output voltage of the LLC converter.

For FB converter, the current ripple ΔILf of the Lf is constrained to within 10% to mitigate cumulative degradation effects on the battery pack, as expressed by the following requirements.

The switching frequency fc is chosen as 50 kHz to minimize switching losses. With regard to the filter capacitors C1, Cd, and C2, their values are determined by the 0.5% voltage ripple:

Since the SP sustains a small bias voltage, C2 is designed with a increased capacitance to ensure compliance with voltage ripple constraints. However, due to the high power density of capacitors, this requirement does not adversely affect the system volume. Furthermore, the bipolar characteristic permits the adoption of compact and highly reliable film capacitors for C2.

For the selection of power devices, the blocking voltage of MOSFETs S1-S4 is Vdc, whereas the blocking voltage of S5-S12 is Vdc/n. In addition, the current stress of S1-S4 is the peak value of ILr, the current stress of S9-S12 equals the battery current Ib, and the current stress of S5-S8 can be expressed by:

The root-mean-square (RMS) value of the current required for calculating the losses of the power devices can then be obtained, as given in Eq. (14).

In the PPC structure, the voltage stress on the series side and the current stress on the parallel side can be significantly reduced. By increasing the value of n, the blocking voltage of the series side semiconductor can be further reduced. Considering the above calculation process, the detailed specifications of the proposed SUDPPC are given in Table 3. Regarding the extension of the proposed SUDPPC to different power and voltage levels, a clear design flowchart is presented in Fig. 8. Most importantly, the transformer turns ratio n should be selected as the maximum value that satisfies the entire required voltage-gain range while maintaining sufficient control margin.

Control design

Since the FB converter operates with controlled current, its dynamic model can be derived using the state-space averaging method. As for the front-stage LLC converter, it can be considered an ideal dc transformer. Therefore, the small-signal model of SUDPPC under duty cycle perturbation can be plotted in Fig. 9, where D, V2 and Ib are the associated static values.

By analyzing the duty cycle disturbance \(\hat {d}\) and the voltage and current equations at each node, the transfer function Gid(s) of the controlled plant can be derived.

where Rb represents the battery equivalent impedance, modeled as a resistor for simplicity. In particular, since the driving logic remains unchanged, the small-signal model of the SUDPPC is consistent in both step-up and step-down modes, simplifying the design of a unified controller.

An ac sweep analysis was conducted under the specified charging condition (Vb=56 V, Ib=20 A) using SIMPLIS software, with the results illustrated in Fig. 10(a). The simulated frequency response exhibits strong correlation with the theoretical prediction derived from (15), thereby validating the analytical model.

Based on a loop bandwidth of 10 kHz and a phase margin of 50 degrees, the PI regulator parameters are determined as kp=0.07 and ki=3700, ensuring excellent dynamic response and stability. The open-loop gain L(s) and closed-loop transfer function T(s) are then derived as follows:

Bode plots of L(s) and T(s) for different Rb are shown in Fig. 10(b) and (c), demonstrating that the high-bandwidth PI control offers strong robustness and stability against load variations.

Performance evaluation and comparative analysis of different topologies

To comprehensively assess the advantages of the SUDPPC topology, a comparative analysis is conducted against conventional FPC and unipolar SUPPC topologies based on performance metrics and operational efficiency. The evaluation results are obtained from Eqs. (3) and (5), calculated using SIMPLIS, and SR is implemented with active power devices. A purely resistive load Rb is employed on the battery side to ensure a constant charging rate of 0.4 C. For consistency and validity, all comparison plants are designed with identical bias voltage ranges, ripple constraints, and load conditions, as detailed in Tables 4 and 5.

Evaluation of the FSBB-based FPC

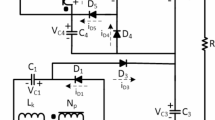

The FSBB converter, with its non-isolation and step-up/down characteristics, serves as a benchmark for verifying the effectiveness of SUDPPC31. Its operating modes are divided into basic buck and boost circuits,

as shown in Fig. 11. Based on the small-ripple approximation in Eq. (4) and the operating principle of the FSBB converter, the expressions for nonactive power and CSF in both buck and boost modes are derived in Table 6. The curves obtained from this analytical model show strong consistency with the simulation results presented in Fig. 12.

Analysis indicates that, in buck mode, the filter inductor Lf and input capacitor C1 contribute a significant and nearly equal amount of nonactive power. This arises from the inherent discontinuities in the voltage across Lf and the current passing through C1, which generate higher harmonic components. By contrast, the output capacitor C2 contributes negligibly owing to its low ripple characteristics. For the boost mode, the duality holds. On the other hand, the measured CSF results are shown in Fig. 12(b), where the semiconductor device is identified as the main contributor. As the bias voltage approaches zero, switch S1 operates with a duty cycle nearing 100%, causing a sharp drop in the total CSF from 1 to 0.

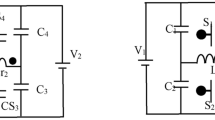

Evaluation of the PSFB-based SUPPC

In the study conducted by Mira et al., the PSFB converter was demonstrated to be more suitable for PPC implementation than the dual active bridge converter, primarily due to its lower cumulative CSF31. As shown in Fig. 13, the PSFB converter is configured using the optimal SU-A scheme, with the dc bus voltage maintained at 40 V to ensure an identical bias voltage swing. A single phase-shift control strategy is utilized to maintain a positive SP voltage, yielding a 320 W SUPPC solution. The transformer is designed with a maximum turns ratio of n = 2.08, under identical control margins as the SUDPPC.

The total nonactive power of the PSFB converter along with its component wise distribution is illustrated in Fig. 14(a). A peak nonactive power of 397 var is observed at Vb≈50 V, which is attributed to the maximum current ripple at 0.5 phase shift ratio. Moreover, as illustrated in Fig. 14(b), the total CSF value sharply drops to zero due to the loss of the blocking voltage across the secondary-side switches during the zero-voltage transition.

Evaluation of the SUDPPC case

Figure 15(a) illustrates the nonactive power characteristics for the analyzed case with a transformer turns ratio of n = 5. It is evident that the nonactive power is predominantly contributed by the rear-stage FB converter. In the LLC converter, the series impedance formed by the resonant capacitor Cr and inductor Lr is effectively nullified, facilitating energy transfer exclusively through the internal electromagnetic field, thereby rendering its contribution to nonactive power negligible. Under zero bias voltage, the LLC converter operates independently of the load, with total nonactive power mainly determined by the dc bus capacitor C1 and the magnetizing inductor Lm. Importantly, given the soft-switching conditions achieved, the nonactive power produced by Lm remains constant across the entire voltage range. The CSF values associated with each element within the SUDPPC are revealed in Fig. 15(b), where increased component utilization is evident during step-up operation. This behavior results from the relatively lower PPF exhibited by the SUDPPC in boost mode. Owing to the capability to accommodate the full voltage range, the switches are subjected to both voltage and current stresses even during zero-voltage transition conditions.

Comparative results analysis

Figure 16 presents the comparison results of the evaluated topologies, where a standard boost converter with 40 V input is additionally tested as a baseline reference for the PSFB-based SUPPC. As clearly depicted, the properly engineered PPC significantly outperforms the FPC under identical operating conditions. Notably, the SUDPPC case presented demonstrates superior overall performance, with a maximum nonactive power of only 224 var, representing a 66.3% reduction compared to the FPC. Meanwhile, a similar behavior is observed in the CSF results, where a value as low as 2.28 under full-load conditions indicates markedly reduced component stress, thereby minimizing long-term degradation and enhancing system reliability.

Based on the operating characteristics of the evaluated topologies, the switching device stresses are summarized in Tables 3, 4 and 5, and corresponding prototype components were selected with appropriate design safety margins. Notably, the SUDPPC substantially reduces current stress at the parallel port and voltage stress on the SP terminal. By integrating detailed thermal models of components into the SIMPLIS simulation environment, terminal efficiency curves across the full output voltage range are illustrated in Fig. 17, capturing both converter-level and system-level efficiencies. The reported values are deemed reasonable for the discussed topologies. Under identical operating conditions, systems designed using the PPP methodology consistently exhibit higher overall efficiency, despite the configured PPC showing lower.

terminal efficiencies at extreme operating points. These low-efficiency points are attributed to extreme voltage conversion ratios, where the converters typically operate with low PPF values, consequently posing minimal impact on the global system efficiency. As demonstrated by Fang et al.35, the battery charging efficiency across the full SOC range can be converted into a time-weighted average, with the corresponding results indicated in the figure captions. Despite incorporating additional components, the SUDPPC delivers superior performance compared to both the FPC and SUPPC during the battery charging process, attaining an average efficiency of 98.63%.

Finally, the loss breakdown of the evaluated topologies is visualized in Fig. 18, encompassing the switching device loss (Pmos), inductor loss (PL), and residual loss (Prest). Here, Prest includes the losses associated with the capacitors and the transformer. Pmos can be further divided into conduction loss Pcon, switching loss Psw, output-capacitance loss Pcoss, and gate-drive loss Pdrive. The corresponding calculation models are summarized in Table 7, where the RMS currents required for evaluating the losses of key components have already been provided in Sect. 3. It is evident that the dominant loss in the SUDPPC is the copper loss of the inductor, as the current flowing through the filter inductor on the series side is approximately the load current. Meanwhile, the reduced voltage stress enables the use of power devices with lower on-resistance. On the parallel side, the current is reduced by the transformer turns ratio. Compared with the conventional FPC, the PPC improves overall efficiency primarily through a significant reduction in Pmos.

Literature review

The design of a PPC revolves around two aspects, namely the connection configuration and the internal dc-dc converter topology. To clearly illustrate the advantages and limitations of the proposed SUDPPC, a comparison with previously reported PPCs is provided in Table 8 in terms of voltage gain, number of power devices, device stress, and control complexity. It can be observed that PPCs are predominantly applied in energy systems where inherent voltage variations exist, and the achievable power level and voltage-stress reduction depend on specific operating conditions. Among existing studies, the SU-A configuration implemented in unidirectional step-up dc-dc converter systems is the most widely adopted. The topologies of PPCs are mainly categorized as dual-active-bridge (DAB) and PSFB structures. In contrast, resonant-converter-based PPCs and PPCs for multi-port systems remain scarcely investigated and represent promising future research directions. It is worth noting that the use of bipolar outputs can further reduce the rated converter power and is gradually becoming mainstream. Although the SUDPPC requires a relatively higher number of power devices, favorable key performance indicators and high overall efficiency can be achieved through appropriate parameter design.

On the other hand, in the design approach presented in14,15,36,37, the polarity reversal of the bipolar SUDPPC leads to unavoidable oscillations in the control signals, and achieving a stable output at zero voltage remains a challenging issue. In contrast, the control logic of the SUDPPC proposed in this paper is considerably simpler, and no extreme duty cycles occur during the dynamic transition between boost and buck modes. Furthermore, zero-voltage output can be achieved by setting the duty cycle of both bridge arms to 0.5, which is obtained by sacrificing the number of power devices in the FB converter.

Experimental validation

A 1.1 kW SUDPPC prototype was built as a device between the 48 V dc bus and the battery pack, with design specifications summarized in Table 3. As illustrated in Fig. 19, the TMS320F28377 digital processor, which supports high-precision pulse-width modulation, was utilized to control the power switches. Besides, a programmable battery simulator was integrated to emulate the dynamic electrical behavior of the battery pack, allowing for controlled and repeatable testing without the need for a physical load.

Figure 20(a) displays the critical experimental waveforms of the analyzed case under the 0.4 C battery charging, which contains the SP voltage V2, resonant current ILr, battery current Ib, and the gate signal VS11 for switch S11 in the FB converter. During step-up operation, characterized by a negative SP voltage, power is transferred from the dc bus to the SP side, while the reverse power flow is observed in step-down case. The duty cycle of VS11 for both operations is approximately 0.9 and 0.1. Similarly, the waveforms during battery discharge are visualized in Fig. 20(b), with voltage/current polarities and power flow directions as described in Fig. 5(b). The sinusoidal characteristics of ILr are achieved by operating the LLC converter near the resonant frequency. At full load, the converter is measured to process 160 W, representing 14.3% of the total system active power.

The experimental results under different reference commands are shown in Fig. 21. During the transition between charging and discharging, the battery current maintains good tracking performance, with a seamless transition completed in approximately 5 ms. Due to the direction of battery current and the effect of internal impedance, a slight fluctuation in the SP voltage amplitude is observed. Furthermore, the transient response induced by dc bus voltage variation is illustrated in Fig. 22, where Vdc changes stepwise between 44 V and 52 V. It is evident that the input voltage Vd of the FB converter and the SP voltage V2 vary simultaneously and stabilize following closed-loop regulation by the PPC.

In addition, the system efficiency and PPC efficiency when the battery is charged at 0.4 C are revealed in Fig. 23(a), which are measured using a Yokogawa WT1800 precision power analyzer. The given SUDPPC is verified to be able to maintain high efficiency over the entire SOC range, reaching a peak efficiency of 98.15% at Vb=48 V. Under this condition, the SP voltage approaches zero, enabling predomi-.

-nant power transfer through the direct infeed path and filter inductor. In particular, higher global system efficiency is observed in the step-up mode due to the reduction in PPF. For battery discharge operations, essentially identical results are obtained.

Furthermore, to more clearly illustrate the loss distribution of the SUDPPC, Fig. 23(b) presents the decomposition of two representative operating points based on theoretical calculations, namely Vb=48 V and Vb=56 V. Because only minor turn-off losses are involved, the Psw of the LLC converter is much smaller than that of the subsequent FB converter. At Vb=48 V, the battery current is transferred solely through the FB converter. During one half-cycle, switches S9 and S11 conduct, while during the other half-cycle, S10 and S12 conduct. Under this operating condition, the upstream LLC converter is completely decoupled from the FB stage, and no power transfer takes place, although soft switching is still maintained. As a result, the Pcon of switches S1 through S8 are eliminated, enabling operation at the peak-efficiency point. Notably, the high-efficiency advantage of the proposed SUDPPC is primarily determined by the series connection scheme and voltage matching, which provide strong robustness against variations in load characteristics and soft-switching boundaries.

Conclusion

This paper described universal interconnection schemes for series-connected PPCs and provided guidelines based on the power distribution characteristics. A SUDPPC topology tailored for battery energy storage systems was analyzed, demonstrating that only 14.3% of the total active power is processed under full-load conditions. Its partial power processing capability was validated through derivation of nonactive power and component stress factor across the full SOC range. Comparative analysis with conventional FPC and series-connected SUPPC topologies revealed superior performance in terms of power loss and component utilization. Experimental validation using a 1.1 kW hardware prototype confirmed the theoretical analysis, with a peak efficiency of 98.15% achieved during bidirectional operation. These results indicate that PPC offers a compact and efficient dc-dc interface solution, particularly well-suited for step-up/down applications.

Data availability

Research data is shared if requested to the corresponding author.

Abbreviations

- V dc :

-

Dc bus voltage

- V b :

-

Battery voltage

- V 2 :

-

SP voltage

- ΔV :

-

Bias voltage

- I dc :

-

Dc bus voltage

- I b :

-

Battery current

- I Lm :

-

Magnetizing current

- I Lf :

-

Filter inductor current

- ΔI Lf :

-

Inductor current ripple

- P p :

-

Processed active power

- P d :

-

Direct infeed active power

- P max :

-

PPC maximum power

- P out :

-

Output active power

- f s :

-

LLC converter resonant frequency

- t d :

-

Dead time

- f c :

-

FB converter switching frequency

- C oss :

-

Output capacitance of the switches

- C r :

-

Resonant capacitor

- L r :

-

Resonant inductor

- L m :

-

Magnetizing inductor

- d :

-

FB converter equivalent duty cycle

- n :

-

Transformer turns ratio

References

Hou, N. et al. A partial power processing structure embedding renewable energy source and energy storage element for islanded DC microgrid. IEEE Trans. Power Electron. 38, 4027–4039 (2023).

Cao, Y. et al. Design and implementation of an 18-kW 500-kHz 98.8% efficiency high-density battery charger with partial power processing. IEEE J. Emerg. Sel. Topics Power Electron. 10, 7963–7975 (2022).

Hashemzadeh, S. M. & Zhu, B. A multi-port high step-up converter integrating coupled inductor and high-frequency transformer with hybrid isolated/non-isolated outputs for renewable energy-based DC micro grids. Energy 335, 138350 (2025).

Hashemzadeh, S. M. & Hosseini, S. H. A coupled inductor-based multiinput high step-up converter for renewable power generation systems. IEEE Trans. Ind. Electron. 72, 4682–4695 (2025).

Anzola, J., Garayalde, E., Urkizu, J., Alacano, A. & Lopez-Erauskin, R. High efficiency converters based on modular partial power processing for fully electric maritime applications. Electronics 12, 2778 (2023).

Zheng, K., Zhang, W., Wu, X., Jing, L. & Zhao, H. Partial-power conversion for increased energy storage capability of li-ion battery energy storage system. IEEE Trans. Ind. Electron. 71, 4742–4752 (2024).

Yadav, N. et al. Performance evaluation of step-up/down partial power converters based on current-fed DC-DC topologies. IEEE Trans. Ind. Appl. 60, 7111–7124 (2024).

Duan, J., Zhang, D. & Gu, R. Partial-power post-regulated LLC resonant DC transformer. IEEE Trans. Ind. Electron. 69, 7909–7919 (2022).

Hassanpour, N., Chub, A., Blinov, A. & Vinnikov, D. Soft-switching bidirectional step-up/down partial power converter with reduced components stress. IEEE Trans. Power Electron. 38, 14166–14177 (2023).

Zientarski, J. R. R., da Silva Martins, M. L., Pinheiro, J. R. & Hey, H. L. Series-connected partial-power converters applied to PV systems: a design approach based on step-up/down voltage regulation range. IEEE Trans. Power Electron. 33, 7622–7633 (2018).

Tian, Y., Li, Y., Cao, B., Wei, F. & Zheng, Y. Systematic topology synthesis and power density visualization of partial power processing architecture. IEEE Trans. Power Electron. 40, 1346–1358 (2025).

Li, C. et al. Revisiting ‘partial power architectures’ from the ‘differential power’ perspective. In 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL) 1–8 https://doi.org/10.1109/COMPEL.2019.8769667 (2019).

Iyer, V. M., Gulur, S., Bhattacharya, S. & Ramabhadran, R. A partial power converter interface for battery energy storage integration with a DC microgrid. In 2019 IEEE Energy Conversion Congress and Exposition (ECCE) 5783–5790 https://doi.org/10.1109/ECCE.2019.8912590 (IEEE, 2019).

dos Santos, N. G. F., Zientarski, J. R. R. & da Silva Martins, M. L. A review of series-connected partial power converters for DC–DC applications. IEEE J. Emerg. Sel. Topics Power Electron. 10, 7825–7838 (2022).

dos Santos, N. G. F., Zientarski, J. R. R. & da Silva Martins, M. L. A two-switch forward partial power converter for step-up/down string PV systems. IEEE Trans. Power Electron. 37, 6247–6252 (2022).

Zientarski, J. R. R., da Silva Martins, M. L., Pinheiro, J. R. & Hey, H. L. Evaluation of power processing in series-connected partial-power converters. IEEE J. Emerg. Sel. Topics Power Electron. 7, 343–352 (2019).

Chen, H., Kim, H., Erickson, R. & Maksimović, D. Electrified automotive powertrain architecture using composite DC–DC converters. IEEE Trans. Power Electron. 32, 98–116 (2017).

Pape, M. & Kazerani, M. An offshore wind farm With DC collection system featuring differential power processing. IEEE Trans. Energy Convers. 35, 222–236 (2020).

Yadav, N. et al. A hybrid modulation approach for step-up/down partial power converter with improved MPPT efficiency around zero partiality. IEEE Trans. Ind. Applicat. 61, 3259–3268 (2025).

Harfman-Todorovic, M. et al. A high efficiency PV micro-inverter with grid support functions. In 2014 IEEE Energy Conversion Congress and Exposition (ECCE) 4244–4250 https://doi.org/10.1109/ECCE.2014.6953979 (IEEE, 2014).

Agamy, M. S. et al. An efficient partial power processing DC/DC converter for distributed PV architectures. IEEE Trans. Power Electron. 29, 674–686 (2014).

Hassanpour, N., Blinov, A., Chub, A., Vinnikov, D. & Abdel-Rahim, O. A Series partial power converter based on dual active bridge converter for residential battery energy storage system. In 2021 IEEE 62nd International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON) 1–6 https://doi.org/10.1109/RTUCON53541.2021.9711725 (IEEE, 2021).

Liu, Y., Hu, Y., Chen, G. & Wen, H. Partial power processing multiport DC–DC converter with radial module connections. IEEE Trans. Power Electron. 37, 13398–13412 (2022).

Liu, C., Zhang, Z. & Andersen, M. A. E. An efficient voltage step-up/down partial power converter (SUD-PPC) using wide bandgap devices. In 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WIPDA ASIA 2021) 264–269 https://doi.org/10.1109/WIPDAASIA51810.2021.9656053. (IEEE, 2021).

Mira, M. C., Zhang, Z. & Michael Andersen, A. E. Analysis and comparison of DC/DC topologies in partial power processing configuration for energy storage systems. In 2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia) 1351–1357 https://doi.org/10.23919/IPEC.2018.8507937. (IEEE, 2018).

Liu, C., Zhang, Z. & Andersen, M. A. E. Analysis and evaluation of 99% efficient step-up/down converter based on partial power processing. IEEE Tran. Ind. Electron. https://doi.org/10.1109/TIE.2022.3198241 (2022).

Kasper, M., Bortis, D. & Kolar, J. W. Classification and Comparative evaluation of PV panel-integrated DC–DC converter concepts. IEEE Trans. Power Electron. 29, 2511–2526 (2014).

Hashemzadeh, S. M., Marzang, V., Pourjafar, S. & Hossein Hosseini, S. An ultra high step-up dual-input single-output DC–DC converter based on coupled inductor. IEEE Trans. Ind. Electron. 69, 11023–11034 (2022).

dos Santos, N. G. F., Zientarski, J. R. R. & da Silva Martins, M. L. A ZCS/ZVS DC–DC partial power converter with reconfigurable H-bridge and variable turns ratio for an integrated on-board charger. IEEE Trans. Power Electron. 39, 13916–13933 (2024).

Iyer, V. M., Gulur, S., Gohil, G. & Bhattacharya, S. An approach towards extreme fast charging station power delivery for electric vehicles with partial power processing. IEEE Trans. Ind. Electron. 67, 8076–8087 (2020).

Mira, M. C., Zhang, Z., Jørgensen, K. L. & Andersen, M. A. Fractional charging converter with high efficiency and low cost for electrochemical energy storage devices. IEEE Trans. Ind. Appl. 55, 7461–7470 (2019).

Hashemzadeh, S. M. & Hosseini, S. H. Design of a high voltage gain converter using coupled inductor with reduced voltage stress for photovoltaic energy based systems. Sci. Rep. 14, 21455 (2024).

Zapata, J. W., Kouro, S., Carrasco, G., Renaudineau, H. & Meynard, T. A. Analysis of partial power DC–DC converters for two-stage photovoltaic systems. IEEE J. Emerg. Sel. Topics Power Electron. 7, 591–603 (2019).

Anzola J, Aizpuru I, Arruti A. Non-isolated partial power converter for electric vehicle fast charging stations. In 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG) 18–22 https://doi.org/10.1109/PEDG48541.2020.9244345 (IEEE, 2020).

Fang, Z., Cai, T., Duan, S. & Chen, C. Optimal design methodology for LLC resonant converter in battery charging applications based on time-weighted average efficiency. IEEE Trans. Power Electron. 30, 5469–5483 (2015).

Köse, H. & Aydemir, M. T. Design and implementation of a 22 kW full-bridge push–pull series partial power converter for stationary battery energy storage system with battery charger. Meas. Control 53, 1454–1464 (2020).

Hassanpour, N., Chub, A., Blinov, A. & Vinnikov, D. Comparison of full power and partial power buck-boost DC-DC converters for residential battery energy storage applications. In 2022 IEEE 16th International Conference on Compatibility, Power Electronics, and Power Engineering (CPE-POWERENG) 1–6 https://doi.org/10.1109/CPE-POWERENG54966.2022.9880862 (IEEE, 2022).

Kurichiparambil, S. D. & Jegathesan, V. Series partial power converter with half bridge LLC series resonant converter for PV application. J. Electr. Eng. 75, 317–324 (2024).

Yadav, N., Hassanpour, N., Chub, A., Blinov, A. & Vinnikov, D. Improved maximum power point tracking algorithm for step-up/down partial power converters operating around zero partiality. IEEE J. Emerg. Sel. Topics Power Electron. 12, 1984–1994 (2024).

Hoffmann, F. et al. A multiport partial power processing converter with energy storage integration for EV stationary charging. IEEE J. Emerg. Sel. Topics Power Electron. 10, 7950–7962 (2022).

Funding

This work is supported by the Shenzhen Science and Technology Plan project (The key technology research and development of MWh level battery energy storage cluster balance control system, KJZD20230923112959001).

Author information

Authors and Affiliations

Contributions

Q. L.: Data curation, Methodology, Software, Writing-original draft. L. J.: Writing-review & editing. W. X.: Writing-review & editing. R. S.: Writing-review & editing. X. W.: Writing-review & editing. J. L.: Writing-review & editing. Y. Z.: Writing-review & editing. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Liu, Q., Jing, L., Xu, W. et al. Performance evaluation of a series-connected step-up/down partial power converter for battery energy storage applications. Sci Rep 16, 5577 (2026). https://doi.org/10.1038/s41598-026-35857-z

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-026-35857-z