Abstract

The integration of high-quality, ultrathin van der Waals (vdW) dielectrics with 2D semiconductors remains a critical bottleneck in the development of reliable, ultra-scaled field-effect transistors (FETs). Here, we report a comprehensive study of MoS2-based FETs employing layered rhombohedral MnAl2S4 as the gate insulator, a previously unexplored vdW dielectric that can be isolated down to the monolayer limit. Devices fabricated in both top-gated (TG) and bottom-gated (BT) configurations exhibit excellent electrical performance, featuring low gate leakage, minimal hysteresis ( < 2 mV) under high electric fields up to 11 MV cm-1 across a wide range of gate voltage sweep rates (0.001–10 Vs-1). We observed a consistent counterclockwise hysteresis and an anomalous bias temperature instability (BTI), possibly caused by the diffusion of Mn interstitials and S vacancies formed inside the MnAl2S4 film during growth. Notably, we show that threshold voltage degradation at high temperatures was observed to be negligible, and hysteresis dynamics and very small BTI are reproducible over a long time, demonstrating the high reliability of our devices. In addition, the vdW interface between MnAl2S4 and MoS2 in our device is of good quality and is expected to provide a small density of insulator defects, a promising gate dielectric for reliable 2D devices.

Similar content being viewed by others

Introduction

Unlike conventional semiconductors like Si, the surface of 2D materials, including MoS2, WSe2, black phosphorus, and graphene, is ideally free of dangling bonds. Thus, a seeding layer, which is required to initiate growth of the dielectric layer, or surface functionalization, is necessary to create nucleation sites before the growth of high-k dielectric layers using atomic layer deposition1,2. Such process steps tend to degrade the 2D/dielectric interface and complicate device processing3. In contrast, traditional oxide gate dielectrics such as SiO2 and Al2O3 require a seeding layer but often exhibit significant charge-trapping sites due to their intrinsic dangling bonds on the surface, degrading the 2D FET device performance4,5. To overcome these limitations, vdW integration of layered crystalline insulators with 2D semiconductors has gained traction as a strategy to form atomically sharp, dangling-bond-free interfaces6,7. Such interfaces help minimize trap densities and leakage currents, enabling aggressive scaling of the gate dielectric thickness, an essential requirement for low-power 2D nanoelectronic8,9,10,11. Hexagonal boron nitride (hBN) is the most widely studied 2D dielectric implemented in 2D FETs12,13, providing ultra-low interface trap densities down to 1010 cm−2 and near-ideal subthreshold swing (SS) down to 62 mV/decade have been achieved14. Furthermore, in general, BN encapsulation (both crystalline and amorphous) has enabled record-high carrier mobility in 2D channels by effectively suppressing interfacial scattering15,16,17. However, due to the low dielectric constant, BN-based FETs exhibited poor electrostatic control of the channel, requiring a larger operation bias than that of high-k insulators18. In addition to the low dielectric constant of BN, the existence of defect states near the band edge of the semiconductor results in higher leakage current density18,19. To address these limitations, several alternative layered insulators, including Bi2SeO520, MoO321, and SrTiO322, have been studied, though their integration into scalable device architectures remains hindered by compatibility challenges with standard CMOS processing. Single-crystal MnAl2S4 is a 2D dielectric with a layered rhombohedral structure23. To date, the research on MnAl2S4 has been limited to the growth of a sizable film24 and the interesting magnetic23,25 and optical properties of the material26. The latest research showed that MnAl2S4 results in vdW interfaces with MoS2, which are expected to show small interface trap density, low SS, and high On/Off ratio at a low bias voltage regime27. MnAl2S4 has a dielectric constant of ~6.1 (higher than that of SiO2 or hBN), and can be readily transferred on a wide range of 2D semiconductors using a practical integration technique that overcomes fabrication challenges of oxide insulators for FET devices, such as structural mismatch28. Notwithstanding these promising attributes, however, the long-term reliability, thermal robustness, and stability of MnAl2S4-based FETs remain largely unexplored, critical factors that must be addressed for future commercial nanoelectronics integration.

Here, we demonstrate the reliability of TG and BG MnAl2S4/MoS2 FETs by evaluating the evolutions in the transfer characteristics, leakage current, and the dynamics of hysteresis, as well as BTI in the temperature range −75 to 150 °C. We show that crystalline MnAl2S4 devices exhibit near-zero counterclockwise hysteresis at and below room temperature, which transitions to a partially clockwise hysteresis at elevated temperatures. Overall, the hysteresis profile is highly reproducible, and the examined BTI is small and often anomalous over a wide temperature range of 0–125 °C. Our results confirm that MnAl2S4 is an exceptionally promising low-hysteresis insulator for reliable ultra-thin 2D nanoelectronics.

Results and discussion

Structural and electrical characterization of MnAl2S4/MoS2 devices

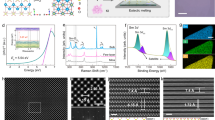

Figure 1a presents a schematic illustration of the TG-FET device incorporating MnAl2S4 as the gate dielectric, while Fig. 1b shows an optical micrograph of the fabricated device. The details of the device fabrication procedure are described in the methods section, and a step-by-step schematic of the process is provided in Supplementary Fig. 1. We determined our MnAl2S4/MoS2 FETs to have channel dimensions of L = 4 μm and W = 12 μm; however, the value of W may vary across different devices due to variations in the lateral dimensions of the exfoliated MoS2 flakes. To identify the layered structure of our device, a 100-nm-thick specimen was prepared using a focused ion beam cut approximately along the yellow rectangle (Fig. 1b). The high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image of a vertically stacked MnAl2S4/MoS2/Ni/Cr heterostructure on SiO2/Si substrates (Fig. 1c) shows a clean and flat MnAl2S4 interface with the underlying MoS2 layer (Fig. 2d). Also, atomic force microscopy (AFM) images further confirmed that the MnAl2S4 films possess a uniform thickness and a smooth surface morphology (Supplementary Fig. 2). The HAADF-STEM, coupled with Energy-dispersive X-ray spectrometry (EDS) elemental maps, confirms the distribution of Mn, Al, S, Mo, S, Ni, and Cr in the heterostructure (Fig. 2e).

a Schematic of the MnAl2S4/MoS2 2D FET. b A top-view optical image of the device taken by an optical microscope. The yellow rectangle indicates the location of the FIB cut, as shown in (c) for the HAADF-STEM, EDS, and TEM analyses. d The HAADF-STEM of the MnAl2S4/MoS2 interface. e The HAADF-STEM of the vertically stacked MnAl2S4/MoS2/Ni/Cr heterostructure on a SiO2/Si substrate from the area labeled in the red rectangle, and the corresponding EDS elemental map shows the distribution of Mn, Al, S, Mo, S, Ni, and Cr.

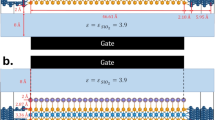

The schematic images of a TG and b BG MnAl2S4 FETs. c, d Show the normalized ID-VD characteristics at different VG. e, f Demonstrate the ID-VG characteristics. g Field-effect mobility over the effective electric field of the TG and BG MnAl2S4 FETs, respectively.

Two device configurations, TG and BG FETs, were fabricated, and their electrical characteristics were measured. The schematics of the MnAl2S4/MoS2 devices are shown in the top panel (Fig. 2a, b). We used highly doped p-type silicon with SiO2 as the substrate to transfer exfoliated MnAl2S4 flakes using PDMS-assisted stamp transfer methods (methods section). Cr/Ni and Ti/Ni metal stacks were employed for the gate, drain, and source terminals in top-gated (TG) and back-gated (BG) devices, respectively. We compare the general behavior of the TG and BG MnAl2S4 FETs, output characteristics (ID − VD), and transfer curves (ID − VG characteristics) measured under vacuum at room temperature (T = 25 °C). For both devices, the output characteristics measured at varying gate voltages exhibit nearly linear and unipolar behavior (Fig. 2c, d). The ION/IOFF ratio at VD = 1 V is around 105 and 107 for TG and BG devices, respectively. The maximum measured on currents of 26 nAμm−1 and 60 nAμm−1 are achieved for TG and BG devices, respectively. At this stage, factors such as high contact resistance are likely limiting device performance. Further improvements in dielectric deposition and contact engineering are expected to enhance current levels. The SS for the best BG devices is ~94 mVdec−1, which is larger compared to the TG devices with SS ~ 87 mVdec−1 at VD = 1 V and 25 °C (Fig. 2e, f). The transfer characteristics measured for both configurations at different VG show promising behavior with good control over the drain current. The device exhibits stable performance, showing nearly identical transfer characteristics in both ambient and vacuum conditions (Supplementary Fig. 3). Critical parameters, including threshold voltage, subthreshold swing, and on/off ratio, remain unchanged. In addition, we compare the field-effect mobility of our devices under top and back-gate operation. The TG devices showed mobilities close to 60, and BG showed 36 cm2 V−1 s−1. This good mobility can be attributed to the stacked MnAl2S4 layer, whose high dielectric constant and clean interface effectively suppress Coulomb scattering, thereby improving carrier transport.

Device-to-device variability

Next, we perform a statistical analysis of the ID-VG characteristics measured for TG and BG devices with comparable channel sizes. The MnAl2S4 layer thickness is determined to be about 32 and 19 nm for the TG and BG devices, respectively. As shown in Fig. 3a, both TG and BG MnAl2S4 FETs show close to identical ID-VG characteristics. However, the BG devices have a slightly larger ION/IOFF ratio, and the threshold voltage is closer to zero (~−0.2 V). The on current is smaller in the TG case, which is possibly due to larger contact resistances caused by the imperfections involved during fabrication and processing. Figure 3b shows the representative contact resistance behavior over gate voltage for both TG and BG devices. Our results show that the BG devices exhibit lower contact resistance at higher gate voltages, which accounts for their relatively higher saturation current. Notably, incorporating a smooth MnAl2S4 dielectric layer between the channel and the SiO2 substrate can enhance the on current by providing a flat, low-trap interface that suppresses charged impurity scattering and interface trap effects in BG devices. Similarly, BG architectures isolated from substrate showed significant charge screening, mitigating SiO2-induced interfacial degradation and enhancing on-state current16. Figure 3c shows the distribution of the drain current over threshold voltage (ID-VTH), where VTH is calculated by extrapolating the linear ID-VG curves to zero obtained from x devices. The main difference between the transfer curve in TG and BG configurations is the shift of VTH towards negative voltages in the TG case. The more negative VTH shift is likely caused by more positive fixed charges in the TG stack, where for thicker insulators the shift becomes larger29,30. In Fig. 3d, we show the leakage current (IG) of all TG (solid lines) and BG (dashed lines) MnAl2S4 FETs with a representative ID. The IG density for both configurations is considerably smaller than the ID and remains below 10−12 A μm−1 at VG = −2V. Figure 3e shows a representative measured ID-VG characteristic in vacuum at fs = 1 Hz, along with the current criterion (IC) used to extract the hysteresis width. The sweeping frequency is fs = 1/tsw, where tsw is the time needed for a single sweep, and the hysteresis width is determined as VH = VTH, down - VTH, up at a constant IC to calculate VTH. Then, we analyze the hysteresis dynamics for both TG and BG FETs over the sweep frequency at 25 °C, as shown in Fig. 3f. Five devices are examined for TG and three for the BG configuration, where TG are shown in blue, and the BG devices in red. The measured hysteresis widths are normalized by the MnAl2S4 insulator’s equivalent oxide thickness (EOT), with EOT = 12 and 20 nm for TG and BG devices, respectively. All of our devices showed a small counterclockwise hysteresis width of around 2 mVnm−1 (TG) and 5 mVnm−1 (BG) at low fs, which increases by almost a factor of 2 at higher fs. Thus, our TG devices showed rather small counterclockwise hysteresis compared to their BG counterparts. We suggest that the diffusion of ions and vacancies inside the MnAl2S4 layer results in the counterclockwise hysteresis in our MnAl2S4/MoS2 FETs. Possibly, Mn interstitials/ions and S vacancies initially formed in the MnAl2S423,31,32 can diffuse under the gate bias field and contribute to the counterclockwise hysteresis. It is worth noting that the MnAl2S4 layer seems to be too thick to make charge-trapping from the gate side a possible mechanism to explain the counterclockwise hysteresis33,34,35. This was qualitatively confirmed by our TCAD simulations for a dummy MoS2 FET, as shown in Supplementary Fig. 4, which only causes a small contribution to the counterclockwise hysteresis in the device. Additionally, the impact of the maximum gate voltage (VG,max) on the hysteresis performance of our device at 25 °C is shown in Fig. 3g. Higher applied VG,max results in a larger hysteresis and the hysteresis width all over the sweep frequency is increased almost three times with VG,max increasing from 0 to 3 V. As VG,max increases, band-bending becomes significant, and more traps inside the dielectric are shifted below the Fermi level, or mobile species are redistributed more effectively by the larger field across the dielectric, resulting in a larger hysteresis width. However, our devices showed relatively larger counterclockwise hysteresis at fast sweep rates, which could be attributed to fast ion diffusion from the MnAl2S4/MoS2 interface to the MnAl2S4/metal gate interface. The hysteresis peak is barely observed in the measurements (Supplementary Fig. 5), possibly due to the very broad distributions of time constants in MnAl2S4. The observed shape of the hysteresis width curve with a maximum and a wide stretch out over many decades in sweep frequency indicates charge trapping as a dominant mechanism36.

a ID-VG characteristics of representative TG and BG MnAl2S4/MoS2 FETs. b Contact resistance as a function of gate voltage for TG and BG devices highlights the relatively lower resistance of BG devices at VG > −0.4 V. c extracted threshold current versus threshold voltage extracted from ID-VG curves. d Small gate leakage current compared to the drain current through the MnAl2S4/MoS2 FETs with a density below 10−2A cm−1 at VG = 1 V. e ID-VG characteristics and IC for hysteresis analysis. The inset shows zoomed counterclockwise (CCW) hysteresis. Hysteresis width over sweeping frequency for f different TG and BG devices, and g at different VG, max at 25 °C.

Temperature-dependent electrical stability

Understanding the impact of temperature is necessary for benchmarking device performance as thermal activation influences charge trapping, impurity behavior, and vacancy diffusion. Thus, we investigated the transfer curve of our MnAl2S4/MoS2 FETs in the temperature range −75 to 150 °C (Fig. 4a, b). Initially, the ID-VG characteristics were measured at 25, 0, −75, 75, 100, and 150 °C, respectively. Subsequently, a final measurement was conducted at 25 °C to assess the reproducibility of the transfer curve following high-temperature exposure. Most importantly, we observe that ID decreases with decreasing temperature, where the saturation current degrades by almost one order for TG and two orders of magnitude for BG devices when going from 150 to −75 °C. This is possibly due to temperature-dependent charge injection over the Schottky barriers at the source and drain. Overall, the initial VTH at 25 °C shifts positively as the temperature decreases to 0 °C and −75 °C, and shifts negatively as the temperature increases above 25 °C. However, the VTH shift for TG devices is pronounced, where VTH is shifted to −2V at 150 °C; however, VTH partially recovers after high-temperature measurements, returning to about −1.7 V. On the other side, VTH is shifted outside the measurement range in BG devices where the FET can no longer be turned off at >75 °C. The ID-VG shift did not recover after high-temperature measurements, and the degradation seems to be permanent. The SS and On/Off ratio over temperature for both the TG and BG devices was degraded over temperature (Supplementary Fig. 6a, b). Next, we determined the IG over temperature for MnAl2S4/MoS2 devices, as shown in Fig. 4c, d. Initially, IG is very small (<1.7 × 10−7 Acm−2) at 25 °C. With the increase in temperature, we observe a more than three orders of magnitude rise in IG for TG and BG devices. Finally, IG increases to ~10−4 μA at 150 °C and VG = −2V, respectively, possibly caused by the creation of new defects at high temperatures and trap-assisted tunneling. However, for both device configurations, IG at 25 °C and 150 °C is very small and does not exceed 10−5 and 10−2 Acm−2, respectively, under an electric field of 8 MVcm−1. Also, we observed a strong VTH shift at high temperatures together with an abrupt increase in the IG, which suggests the creation of new defects in the MnAl2S4 film. As schematically shown in Fig. 4e, the increase of IG can be explained by forming a percolation path through the whole insulator. Following prolonged exposure to 150 °C for several days, the electrical characteristics of the device exhibit only partial recovery upon returning to 25 °C. The evolution of IG over temperature for both the TG and BG devices is summarized in Supplementary Fig. 6c.

Temperature-dependent ID-VG characteristics of a TG and b BG MnAl2S4/MoS2 FETs measured at vacuum and their gate leakage current (c) and (d), respectively. e Schematics of the creation of new defects in MnAl2S4 at high temperatures.

Temperature-dependent hysteresis dynamics and reliability

We next examine the dependence of hysteresis width on measurement frequency across five distinct temperatures, with all measurements conducted under vacuum conditions. Initial measurements were carried out at 25 °C, followed by sequential low- and high-temperature testing. Subsequently, hysteresis was re-evaluated at room temperature following high-temperature measurements at 125 °C to assess the reproducibility of device behavior after thermal exposure. Initially, for the TG device, the hysteresis becomes increasingly counterclockwise at 0 °C and −75 °C, with a pronounced peak observed at high sweep frequencies (Fig. 5a). This trend suggests that rapid diffusion of mobile species, likely originating from within the dielectric, plays a dominant role in the counterclockwise hysteresis behavior under these conditions. As the temperature is increased to 100 °C, the counterclockwise hysteresis is notably suppressed, and at 125 °C, it transitions to an almost entirely clockwise direction. Upon cooling the device back to 25 °C, the hysteresis remains counterclockwise at low and medium sweep frequencies, and reverts to the counterclockwise regime at high frequencies. A similar temperature-dependent hysteresis evolution is observed for BG devices, although in this configuration, the counterclockwise hysteresis exhibits two distinct peaks at both low and high frequencies. Notably, for the BG device, the counterclockwise hysteresis is almost fully restored following high-temperature exposure (Fig. 5b), indicating a high degree of hysteresis reproducibility. As discussed earlier, the mobile ions such as Mn and S inside MnAl2S4 are expected to be the main players in counterclockwise hysteresis at −75, 0, and 25 °C. However, at high temperatures, ion diffusion becomes too fast to be observable, and charge trapping in MnAl2S4 from the channel side dominates, resulting in clockwise hysteresis. Typically, clockwise hysteresis is associated with charge trapping at the semiconductor–dielectric interface or within the dielectric itself. During the forward gate sweep, charges become trapped, causing a shift in the threshold voltage that appears as hysteresis when the gate is swept back. In contrast, counterclockwise hysteresis is often attributed to the movement of mobile ions or adsorption/desorption of ambient molecules, which can dynamically modulate the channel potential depending on the sweep direction. This was qualitatively confirmed by our TCAD simulations for a dummy MoS2 FET, as shown in Supplementary Fig. 7. At the same time, charge trapping by defects in MnAl2S4 situated near the interface with MoS2 makes a small contribution to the BG device and likely comes into play only at very slow sweep rates. In the BG devices, the counterclockwise hysteresis profile remains largely unchanged before and after high-temperature exposure, suggesting stable interface and dielectric behavior. In contrast, TG devices exhibit a pronounced shift toward clockwise hysteresis following high-temperature measurements, indicating a stronger influence of thermally activated charge trapping or species diffusion from the gate side. Heating the device to 125 °C for many hours may reduce the densities of mobile species within the MnAl2S4 layer, thereby reducing the counterclockwise contribution, which otherwise counteracts and masks the clockwise hysteresis caused by charge traps. To understand the effect of ambient conditions on our devices, we analyze the hysteresis dynamics at vacuum and ambient conditions. Our device exhibits a small hysteresis after storage in the ambient for two and five days, as shown in Supplementary Fig. 8. The counterclockwise hysteresis profile remains identical to that in the vacuum without remarkable changes. In general, the smaller the hysteresis, the more reliable the device operation. In this context, we compare the ΔVH of our devices with various 2D FET technologies at different VG sweeping rates and vacuum conditions (Fig. 5c). Our TG MnAl2S4/MoS2 devices exhibit excellent hysteresis stability across a wide range of gate voltage sweep rates, achieving near-zero normalized hysteresis widths around 1 mV nm−1, surpassing many previously reported technologies in terms of hysteresis suppression.

Observed hysteresis in vacuum at varying temperatures for a TG and b BG MnAl2S4/MoS2 FETs. c Comparison of the absolute normalized hysteresis width measured on various 2D-FET technologies at different sweeping rates: 1, ref. 6; 2, ref. 44; 3, ref. 45; 4, ref. 46; 5, ref. 41; 6, this work; 7, ref. 47; 8, ref. 48; 9, ref. 49; 10, ref. 50; 11, ref. 45; 12, ref. 51; 13, ref. 52; 14, ref. 12; 15, ref. 37; 16, ref. 53; 17, ref. 54; 18, ref. 41; 19, this work; 20, ref. 47; 21, ref. 55; 22, ref. 56; 23, ref. 57; 24, ref. 58; 25, ref. 59; 26, ref. 55; 27, ref. 45; 28, ref. 49; 29, ref. 12; 30, ref. 60; 31, ref. 61; 32, ref. 41; 33, ref. 61; 34, this work.

Besides the transfer characteristics’ hysteresis, the threshold voltage’s long-term drift is one of the most critical reliability challenges in Si- and 2D-FETs because of their significant bias and temperature dependence37,38. The assessment of the shift in VTH under constant gate stress bias is called bias temperature instability (BTI). Applying a positive stress bias results in positive BTI (PBTI) and, similarly, negative BTI (NBTI) for a negative stress bias. Here, first we measured transfer characteristics before applying any stress voltages to the devices, as shown by the curve labeled fresh in Fig. 6a. Since the MoS2 is an n-type 2D material, we evaluated the PBTI results of subsequent stress/relaxation cycles for various ts. Then, the devices were subjected to VG,stress of 2 V for varying stress times of ts = 1, 1ks, and 10ks. The BTI measure-stress-measure procedure in our measurement is shown in Supplementary Fig. 9. After the stress period, the VTH shift is extracted using a constant IC. Figure 6a shows the evolution of the ID-VG characteristics under a PBTI stress for TG devices for VG, stress = 2 V. Once the positive stress voltage is applied, VTH shifts to negative voltages, and the shift becomes more pronounced with increasing stress time (Fig. 6b). The measured PBTI shifts are normalized by the EOT of the MnAl2S4 insulator, the same as for hysteresis. The normalized VTH shift is small, and after almost seven hours of relaxation, the device shows sizable over-recovery. Similarly, we measured PBTI for the BG devices, and the ID-VG characteristics of the device are shown in Fig. 6c. The VTH shift is negative, and the shift becomes abrupt at larger ts. The VTH shift for the BG device seems considerably larger than the TG case, where the shift reaches over 80 mV nm−1 (at ts = 10ks). At the same time, the BG device also shows more recovery after a relaxation period (Fig. 6d). Also, we determined the effect of VG,stress on the PBTI behavior at 25 °C under a long stress time, ts = 10ks (Supplementary Fig. 10). As VG,stress increases, the anomalous PBTI (negative PBTI)39,40 becomes more pronounced; however, the shift stayed small even at higher VG,stress = 5 V. Also, we examined the NBTI behavior by applying an increasing negative VG,stress for stress times of ts = 10ks. We observed a positive VTH shift of the ID-VG characteristics for NBTI at VG,stress = −2V (Supplementary Fig. 11). However, the VTH shift moves to the negative region with increasing VG,stress, but remains very small even at larger stress voltages. By comparison of Supplementary Figs. 10, 11, we realize that the PBTI degradation seems to be larger than NBTI, similar to our previous work41. This asymmetry can be attributed to differences in charge trapping dynamics and the nature of defect states within the MnAl2S4 layer and at the MoS2/MnAl2S4 interface. We suggest that the diffusion of mobile species in MnAl2S4, such as Mn interstitials and S vacancies, may also contribute to anomalous PBTI. Note that during the early stages of PBTI recovery in Fig. 6b, d, ΔVTH is negative, but over-recovers after sufficiently long relaxation times. This anomalous PBTI could be caused either by the diffusion of mobile species or by charge trapping from the gate/insulator interface rather than the channel42. Note that if the bandgap of the insulator is small enough and the work function for the gate metal is large, the barrier for charge trapping from the gate side will be facilitated, which can cause anomalous PBTI. However, this remains a speculative hypothesis, as none of our current models or simulations have provided evidence supporting this mechanism. For consistency, reliability measurements were primarily performed on identical TG and BG devices to enable direct comparison, while additional tests (Supplementary Fig. 12) confirm the reproducibility of the observed BTI behavior across multiple devices. Understanding this BTI behavior at different temperatures is key to analyzing the distribution of traps in the device. A series of measurements was performed at 0, 25, 100, and 125 °C, then BTI was re-measured at 25 °C following the measurement at 125 °C. The PBTI behavior of the TG device at different temperatures, 0, 25, 100, and 125 °C, and under ts = 1 s is shown in Fig. 6e. Initially, PBTI shows anomalous behavior by shifting VTH to more negative values, while at longer relaxation times the shifts become positive, i.e., over-recovered, at all temperatures. The anomalous PBTI shift, in particular, at high temperatures, is more pronounced at larger stress times ts = 10ks (Fig. 6f). We observed nearly complete recovery at 0 °C within about eight hours, where the PBTI considerably over-recovers at high temperatures. In particular, BTI-induced threshold voltage shift is not only a major degradation mechanism but also serves as a key metric for evaluating the performance and long-term reliability of FETs, as it can lead to circuit instability and eventual failure in integrated circuits42. Therefore, we provide an overview of the PBTI performance of various 2D FET technologies and compare them with our devices at vacuum conditions (Fig. 6g). Notably, the MnAl2S4/MoS2 devices show very small long-term positive bias temperature instability (PBTI) stability in comparison to other reported 2D-FET technologies. This is evidenced by the exceptionally small threshold voltage shift (PBTI shift) of around 10 and 23 mV nm−1 under stress duration of ts = 1 and 10ks, respectively.

a Evolution of the ID-VG characteristics under PBTI stress measured for TG and b corresponding recovery traces for increasing stress biases, similarly c and d for the BG device. PBTI measured at T = 0, 25, 100, and 125 °C under (e) ts = 1 s and under (f) ts = 10ks were measured for the TG device at stress bias of VG,stress = 2 V. g Comparison of the absolute normalized PBTI measured on various 2D-FET technologies at vacuum: 1, ref. 62; 2, ref. 63; 3, ref. 64; 4, ref. 63; 5, ref. 65; 6, ref. 66; 7, ref. 67; 8, ref. 37; 9, ref. 66; 10, ref. 61. * The SiO2/ReS2 FET devices is passivated with α-MoO3.

Notably, among vdW dielectric candidates, MnAl2S4 offers a particularly well-balanced set of properties. Exfoliated h-BN is valued for its pristine interface and excellent leakage suppression, yet leakage becomes significant below ~2 nm, and its intrinsically low dielectric constant limits meaningful EOT scaling. CVD-grown h-BN, by contrast, exhibits higher leakage currents and maintains an EOT above 5 nm. SrTiO3 provides very high permittivity, but when thinned to the nanometer regime, it shows leakage characteristics comparable to MnAl2S4, and its 2D/dielectric interface in exfoliated samples requires further investigation. CaF2 can achieve smaller EOT values, though its leakage performance deteriorates at ultrathin thicknesses. By combining sufficient dielectric strength, scalable EOT, and robust leakage suppression, MnAl2S4 emerges as a promising dielectric for next-generation 2D FET technologies. A summary of these parameters is provided in Supplementary Table 1.

Eventually, we will overview the transfer curve and gate leakage current of the devices after each measurement step, including frequent BTI tests and exposure to high temperatures (e.g., at 100, 125, and 150 °C). In both device configurations, we observe a negative VTH shift of the transfer curve after the PBTI measurements, compared to the fresh state. This behavior suggests the influence of fixed positive charges located within the MnAl2S4 layer, which modulate the transfer curve response under electrical stress (Supplementary Fig. 13). Next, we measured the transfer curve after baking the device at high temperatures of 100 and 150°C, each for 8 h. There is an additional shift of VTH towards negative voltages and a slight increment in the saturation current in TG devices. However, the VTH shift is remarkably larger for the BG case, where the device was not turned off at the operated gate voltage range, SS drastically degraded, and saturation current increased by an order of magnitude. Finally, we exposed devices to the ambient and measured transfer curves one hour and three days after exposure, respectively. The TG device exhibited gradual recovery during ambient exposure and nearly complete restoration of its initial characteristics after three days under ambient conditions (Supplementary Fig. 13a). In contrast, the BG device showed no observable recovery, even after identical ambient storage. We argue that oxygen molecules might have passivated some S vacancies that have formed in MnAl2S4 during baking under ambient exposure, which might play a role in the TG device transfer curve recovery. In addition, the leakage current of the BG device increased by over two orders of magnitude following thermal baking, but exhibited partial recovery after subsequent exposure to ambient conditions. The SS degradation under PBTI and high-temperature measurements is not reversible (Supplementary Fig. 13b). However, during all of the measurements, the leakage current density remains smaller than 0.5 μAμm−1. We suggest that the enhancement in leakage current is due to the degradation of MnAl2S4 during high temperature and long stress bias, and partial recovery while being exposed to air.

Conclusion

In conclusion, we report the fabrication of MoS2-based 2D FETs employing van der Waals integration with single-crystalline, layered MnAl2S4 as a gate dielectric. An in-depth investigation of device performance, hysteresis dynamics, and BTI was conducted to assess the electrical reliability of this previously unexplored dielectric. The HAADF-STEM revealed a clean and well-ordered interface between MnAl2S4 and MoS2, indicating a high-quality insulator/semiconductor junction. The MnAl2S4/MoS2 FETs exhibited excellent electrical stability across a range of temperatures and demonstrated minimal, normalized counterclockwise hysteresis below 2 mV at or below room temperature. At elevated temperatures, the hysteresis progressively transitioned to a predominantly clockwise direction. This temperature-dependent hysteresis behavior is attributed to distinct charge-trapping mechanisms: counterclockwise hysteresis is likely driven by gate-side trapping and diffusion of mobile species such as Mn interstitials and sulfur vacancies within the MnAl2S4 film, whereas clockwise hysteresis at higher temperatures is dominated by channel-side trapping. Similarly, BTI degradation is very small and anomalous, which we attribute to thermally activated defect diffusion within the dielectric layer. Since both the observed hysteresis and BTI drifts are small, our findings underscore the thermal robustness and reliability of MnAl2S4, establishing it as a compelling candidate among layered crystalline dielectrics for next-generation, ultra-scaled 2D nanoelectronic devices.

Experimental section

Material preparations

The conventional chemical vapor transport (CVT) technique is used to grow MnAl2S4 crystals25. First, the high-purity manganese (99.9%), aluminum (99.9%), and sulfur (99.9%) powders were mixed at a stoichiometric ratio of 1:2:4, and the mixture was sealed in a quartz tube at a vacuum of ~10−4 Torr. The two-zone furnace is used to grow the MnAl2S4 crystal. The growth was conducted by maintaining the cold zone at 880 °C and the hot zone at 980 °C for 7 days. Subsequently, the tube was allowed to cool naturally to room temperature to obtain the MnAl2S4 crystals.

Device fabrication

Layered MnAl2S4 films were mechanically exfoliated from the bulk crystals and transferred onto SiO2/Si substrates by a PDMS stamp transfer approach43. Multi-layered MoS2 flakes were exfoliated and transferred onto a SiO2 substrate using the same approach. For the TG FET devices, the MoS2 channel was transferred through a mechanical exfoliation approach on the SiO2/Si substrate. After identifying the flake location using an optical microscope, the MnAl2S4 layer was aligned and transferred to the MoS2 flake. The drain, source, and gate electrode areas were determined using electron-beam lithography followed by thermal deposition of 10 nm Ti and 50 nm Ni. For BG FETs, first, the drain and source contacts were patterned on the SiO2 substrate, and 10 nm Ti and 50 nm Ni were deposited to fabricate the gate electrode. To fabricate BG FETs, first, the drain and source contacts were patterned on the SiO2 substrate, and a similar procedure to dual-gated devices was carried out to fabricate gate electrodes. The MnAl2S4 layer was transferred on a patterned gate electrode, followed by the transfer of MoS2, and the electrodes were first patterned using the EBL process and deposited using a thermal evaporator. Then, the devices are loaded into a vacuum chamber for characterization. All the measurements were carried out without light illumination.

Material characterization

HAADF-STEM imaging and EDS analysis of the samples were performed using a Cs image corrected TEM Titan from FEI. The Reith-83 instrument performed the AFM surface profile and thickness.

Electrical characterization

ID − VD and ID − VG characteristics at different temperatures were conducted using a Keithley 2636 parameter analyzer in the chamber of a Lakeshore vacuum probe station (~2 × 10−6 torr) in dark conditions. The hysteresis width of the transfer curve was analyzed by performing double sweeps for a wide range of different sweep times. The hysteresis width is obtained from the difference in VTH between the forward and backward ID-VG curves. Subsequent stress/recovery tests measured the BTI behavior. Both ΔVH and BTI values were normalized by EOT.

Data availability

The data that support the findings of this work are available from the corresponding author upon reasonable request. All data requests will be handled by SM.SE., who can be contacted at sattari@iue.tuwien.ac.at.

References

Guo, Y. et al. Van der Waals polarity-engineered 3D integration of 2D complementary logic. Nature, 630, 346–352 (2024).

McDonnell, S. et al. HfO2 on MoS2 by atomic layer deposition: adsorption mechanisms and thickness scalability. ACS Nano 7, 10354–10361 (2013).

Sheng, Y. et al. Gate stack engineering in MoS2 field-effect transistor for reduced channel doping and hysteresis effect. Adv. Electron. Mater. 7, 2000395 (2021).

Lemke, B. P. & Haneman, D. Dangling bonds on silicon. Phys. Rev. B 17, 1893 (1978).

Broqvist, P., Alkauskas, A. & Pasquarello, A. Defect levels of dangling bonds in silicon and germanium through hybrid functionals. Phys. Rev. B 78, 075203 (2008).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Zhang, X. et al. Van der Waals-interface-dominated all-2D electronics. Adv. Mater. 35, 2207966 (2023).

Huang, J. K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Dorow, C. J. et al. Gate length scaling beyond Si: mono-layer 2D channel FETs robust to short channel effects. In 2022 International Electron Devices Meeting (IEDM) 7-5 (IEEE, 2022).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Chen, C. et al. Water-induced bandgap engineering in nanoribbons of hexagonal boron nitride. Adv. Mater. 35, 2303198 (2023).

Vu, Q. A. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 031001 (2018).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Lee, G. H. et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano 9, 7019–7026 (2015).

Sattari-Esfahlan, S. M. et al. Low-temperature direct growth of amorphous boron nitride films for high-performance nanoelectronic device applications. ACS Appl. Mater. Interfaces 15, 7274–7281 (2023).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Lee, G. H. et al. Electron tunneling through atomically flat and ultrathin hexagonal boron nitride. Appl. Phys. Lett., 99, 243114 (2011).

McDougall, N. L., Partridge, J. G., Nicholls, R. J., Russo, S. P. & McCulloch, D. G. Influence of point defects on the near edge structure of hexagonal boron nitride. Phys. Rev. B 96, 144106 (2017).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature 616, 66–72 (2023).

Holler, B. A., Crowley, K., Berger, M. H. & Gao, X. P. 2D semiconductor transistors with van der Waals oxide MoO3 as integrated high-k gate dielectric. Adv. Electron. Mater. 6, 2000635 (2020).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Verchenko, V. Y. et al. Layered van der Waals chalcogenides FeAl2Se4, MnAl2S4, and MnAl2Se4: Atomically thin triangular arrangement of transition-metal atoms. Inorg. Chem. 62, 7557–7565 (2023).

You, S. H., Hong, K. J., Jeong, T. S., Lim, K. Y. & Youn, C. J. Growth and photocurrent characteristics of the photoconductive MnAl2S4 layers grown by hot-wall epitaxy method. J. Cryst. growth 404, 116–121 (2014).

Menard, M. C. et al. High-resolution synchrotron studies and magnetic properties of frustrated antiferromagnets MAl2S4 (M= Mn2+, Fe2+, Co2+). Chem. Mater. 23, 3086–3094 (2011).

Park, T. Y., Jin, M. S., Choe, S. H., Goh, J. M. & Kim, W. T. Optical properties of MnAl2S4 and MnAl2Se4 single crystals. J. Appl. Phys. 86, 3478–3480 (1999).

Xu, F. et al. Few-layered MnAl2S4 dielectrics for high-performance van der Waals stacked transistors. ACS Appl. Mater. Interfaces 14, 25920–25927 (2022).

Liu, Y. et al. Thermal oxidation of WSe2 nanosheets adhered on SiO2/Si substrates. Nano Lett. 15, 4979–4984 (2015).

Mo, F. et al. Low-voltage operating ferroelectric FET with ultrathin IGZO channel for high-density memory application. IEEE J. Electron Devices Soc. 8, 717–723 (2020).

Shih, C. H. & Wang, J. S. Threshold voltage of ultrathin gate-insulator MOSFETs. IEEE Electron Device Lett. 30, 278–281 (2009).

Hong, K. J., Jeong, T. S. & Youn, C. J. Photocurrent spectroscopic study of temperature-dependent photoresponse and valence-band splitting in MnAl2S4 layers. J. Electron. Mater. 43, 3092–3097 (2014).

You, S. H. et al. Investigation of the structural, electrical, and optical properties of MnAl2Se4 layers grown using the hot-wall deposition technique. J. Korean Phys. Soc. 69, 605–611 (2016).

Provias, A. et al. Reliability assessment of double-gated wafer-scale MoS₂ field effect transistors through hysteresis and bias temperature instability analyses. In 2023 International Electron Devices Meeting (IEDM), 1–4 (IEEE, 2023).

Knobloch, T. et al. Modeling the performance and reliability of two-dimensional semiconductor transistors. In 2023 International Electron Devices Meeting (IEDM), 1–4 (IEEE, 2023).

Knobloch, T. et al. A physical model for the hysteresis in MoS2 transistors. IEEE J. Electron Devices Soc. 6, 972–978 (2018).

Devine, R. A. B. et al. O interstitial generation and diffusion in high temperature annealed Si/SiO₂/Si structures. J. Appl. Phys. 79, 2302–2308 (1996).

Illarionov, Y. Y. et al. Long-term stability and reliability of black phosphorus field-effect transistors. ACS Nano 10, 9543 (2016).

Puschkarsky, K., Grasser, T., Aichinger, T., Gustin, W. & Reisinger, H. Review on SiC MOSFETs high-voltage device reliability focusing on threshold voltage instability. IEEE Trans. Electron Devices 66, 4604–4616 (2019).

Contamin, L. et al. Fast measurement of BTI on 28nm fully depleted silicon-on-insulator MOSFETs at cryogenic temperature down to 4K. In 2022 IEEE International Reliability Physics Symposium (IRPS), 7A–3 (IEEE, 2022)

Daus, A. et al. Charge trapping mechanism leading to sub-60-mV/decade-swing FETs. IEEE Trans. Electron Devices 64, 2789–2796 (2017).

Sattari-Esfahlan, S. M. et al. Stability and reliability of van der Waals high-k SrTiO3 field-effect transistors with small hysteresis. ACS Nano 19, 12288–12297 (2025).

Pae, S. et al. Effect of BTI degradation on transistor variability in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 8, 519–525 (2008).

Castellanos-Gomez, A. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Mater. 1, 011002 (2014).

Uchiyama, H., Maruyama, K., Chen, E., Nishimura, T. & Nagashio, K. A monolayer MoS2 FET with an EOT of 1.1 nm achieved by the direct formation of a high-k Er2O3 insulator through thermal evaporation. Small 19, 2207394 (2023).

Aslam, M. A. et al. All van der Waals semiconducting PtSe2 field effect transistors with low contact resistance graphite electrodes. Nano Lett. 24, 6529–6537 (2024).

Zhu, C. Y. et al. Magnesium niobate as a high-k gate dielectric for two-dimensional electronics. Nat. Electron. 7, 1137–1146 (2024).

Debashis, P. et al. Ultra-high-k ferroelectric BaTiO3 perovskite in the gate stack for two-dimensional WSe2 p-type high-performance transistors. Nano Lett. 24, 12353–12360 (2024).

Ye, Z. et al. Mechanism and origin of hysteresis in oxide thin-film transistor and its application on 3-D nonvolatile memory. IEEE Trans. Electron Devices 64, 438–446 (2017).

Jawa, H., Varghese, A. & Lodha, S. Electrically tunable room temperature hysteresis crossover in underlap MoS2 field-effect transistors. ACS Appl. Mater. Interfaces 13, 9186–9194 (2021).

Lan, C. et al. The origin of gate bias stress instability and hysteresis in monolayer WS2 transistors. Nano Res. 13, 3278–3285 (2020).

Late, D. J., Liu, B., Matte, H. S. S. R., Dravid, V. P. & Rao, C. N. R. Hysteresis in single layer MoS2 field effect transistors. ACS Nano 6, 5635–5641 (2012).

Prasad, P., Garg, M. & Chandni, U. Tailoring the transfer characteristics and hysteresis in MoS2 transistors using substrate engineering. Nanoscale 12, 23817–23823 (2020).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron 2, 230–235 (2019).

Zeng, D. et al. Single-crystalline metal-oxide dielectrics for top-gate 2D transistors. Nature 632, 788–794 (2024).

Oliva, N. et al. Hysteresis dynamics in double-gated n-type WSe2 FETs with high-k top gate dielectric. IEEE J. Electron Devices Soc. 7, 1163–1169 (2019).

Guo, J. et al. Capacitorless dynamic random access memory with 2D transistors by one-step transfer of van der Waals dielectrics and electrodes. ACS Nano 19, 2848–2856 (2025).

Illarionov, Y. Y. et al. Energetic mapping of oxide traps in MoS2 field effect transistors. 2D Mater. 4, 025108 (2017).

Cho, A. J. et al. Multi-layer MoS2FET with small hysteresis by using atomic layer deposition Al2O3 as gate insulator. ECS Solid State Lett. 3, Q67 (2014).

Illarionov, Y. Y. et al. Improvedhysteresis and reliability of MoS2 FETs with high-quality CVD growth and Al2O3encapsulation. IEEE Electron Device Lett. 38, 1763–1766 (2017).

Lee, C. et al. Comparison of trapped charges and hysteresis behavior in hBN encapsulated single MoS2 flake based field effect transistors on SiO2 and hBN substrates. Nanotechnology 29, 335202 (2018).

Illarionov, Y. Y. et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistor. 2D Mater. 3, 035004 (2016).

Illarionov, Y. Y. et al. Reliability of scalable MoS2 FETs with 2 nm crystalline CaF2 insulators. 2D Mater. 6, 045004 (2019).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Cho, K. et al. Electric stress-induced threshold voltage instability of multilayer MoS2 field effect transistors. ACS Nano 7, 7751–7758 (2013).

Illarionov, Y. Y. et al. Process implications on the stability and reliability of 300 mm FAB MoS2 field-effect transistors. npj 2D Mater. Appl. 8, 8 (2024).

Chun, J., Lee, J., Cho, H. & Kim, G. T. Bias temperature instability of multilayer ReS2 FET with α-MoO3 passivation. Adv. Mater. Interfaces 9, 2200378 (2022).

Yang, G. et al. Anomalous positive bias stress instability in MoS2 transistors with high-hydrogen-concentration SiO2 gate dielectrics. IEEE Electron Device Lett. 40, 232–235 (2018).

Acknowledgements

The authors acknowledge financial support through the European Research Council under Grant Agreement No. 101055379 (F2GO) and CzechNanoLab Research Infrastructure, supported by MEYS CR (LM2023051). Y.Z. appreciates the National Natural Science Foundation of China (Nos. 62264010, 62474083). Y.Y.I. acknowledges the financial support from National Natural Science Foundation of China (NSFC) grant number W2432040, Guangdong Basic and Applied Basic Research Foundation (grant numbers 2024A1515010179 and 2023ZT10X010) and Shenzhen Science and Technology Program 20231115150611001. Eventually, S.M.S.-E. acknowledges the TU Wien Library for financial support through its Open Access Funding Program.

Author information

Authors and Affiliations

Contributions

S.M.S.E. carried out the experiments, analyzed the experimental data, and wrote the manuscript. Y.I. reviewed the manuscript and provided comments. F.X. fabricated the MoS2 FET devices. A.P. assisted with schematic illustrations. T.K. performed TCAD simulations. S.M., J.M., and O.M. conducted the TEM measurements. Y.Z. guided the device fabrication and reviewed the manuscript. T.G. supervised this work. All authors discussed the results and contributed to the editing of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Materials thanks Jing-Kai Qin and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Sattari-Esfahlan, S.M., Illarionov, Y., Xu, F. et al. Near-zero hysteresis van der Waals MnAl2S4 field-effect transistors with low minimal threshold voltage degradation and high thermal stability. Commun Mater 7, 11 (2026). https://doi.org/10.1038/s43246-025-01020-w

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s43246-025-01020-w