Abstract

As silicon-based computing approaches fundamental physical limits in energy efficiency, speed and density, the search for complementary materials beyond silicon-based technology has intensified. In this Perspective, we examine van der Waals indium selenides — particularly InSe and In2Se3 — as promising candidates for next-generation low-power electronics. Indium selenides exhibit exceptional electron mobility exceeding 1,000 cm2 V–1 s–1, high thermal velocity of >2 × 107 cm s–1, thickness-tunable bandgaps of 0.97–2.5 eV and unique phase-dependent ferroelectric properties, enabling both high-performance logic and non-volatile memory functions within a single material system. This Perspective critically evaluates the materials properties, fabrication challenges and device applications of indium selenides, examining their potential to surpass silicon in ultra-scaled transistors through ballistic transport while simultaneously offering ferroelectric memory capabilities impossible in conventional semiconductors. We analyse breakthroughs in ballistic InSe transistors, tunnel field-effect transistors and In2Se3-based ferroelectric devices for information storage, and identify key research priorities for addressing persistent challenges in scalable synthesis, phase control and oxidation prevention. By bridging fundamental materials science with practical device engineering, we provide a roadmap for translating the exceptional properties of indium selenides into commercially viable, low-power computing technologies that can overcome the limitations of silicon while enabling novel computing architectures.

Key points

-

Indium selenides uniquely combine exceptional electron mobility of > 1,000 cm2 V–1 s–1, high thermal velocity of >2 × 107 cm s–1 and diverse phase-dependent properties that make them superior to other 2D materials for ultra-scaled transistors and memory devices.

-

The polymorphic nature of InSe (β-phase, γ-phase, ε-phase) and In2Se3 (α-phase, β-phase, β‘-phase) enables precise tuning of electronic and ferroelectric properties, offering unprecedented design flexibility for device engineers compared with conventional semiconductors with fixed properties.

-

Ballistic InSe transistors with 10 nm channels have achieved record-high transconductance of ~6 mS and current densities that outperform other 2D materials and approach theoretical limits, validating the potential of indium selenides for post-silicon logic devices.

-

The robust ferroelectricity in In2Se3 and emerging sliding ferroelectricity in InSe enable non-volatile memory functionality integrated with semiconducting properties — a combination unavailable in conventional materials that could fundamentally transform computing architectures.

-

Addressing the challenges of scalable synthesis, phase control and oxidation prevention represents the critical path towards commercial implementation of indium selenide-based technologies for next-generation, low-power computing beyond the silicon-based semiconductor chips.

Similar content being viewed by others

Introduction

The miniaturization of silicon-based microelectronics faces concurrent challenges of limited device scalability and increasing energy consumption in advanced processing nodes, necessitating the exploration of novel materials solutions for future low-power computing hardware. The 2D van der Waals indium selenides — InSe and In2Se3 — have emerged as particularly promising candidates, offering advantages that potentially exceed those of both silicon and other widely studied 2D materials such as transition metal dichalcogenides (TMDs) of molybdenum and tungsten1,2,3,4,5. Their atomically thin form factors yield exceptional electrostatic gate control, mitigating short-channel effects that plague deeply scaled silicon transistors1,4,5. Second, InSe exhibits extraordinarily high electron mobility, with experimental values exceeding 1,000 cm2 V−1 s−1 at room temperature6,7,8, owing to an unusually low effective electron mass of ~0.12 m0). This high mobility supports ballistic transport in nanoscale devices6,9,10. Moreover, the binary indium–selenium system offers a rich phase landscape with diverse structural configurations and electronic properties, allowing for precise engineering of device characteristics through phase and thickness control11,12,13.

Perhaps most significantly, certain phases of both In2Se3 and InSe exhibit robust ferroelectric properties persisting down to the monolayer limit, combining semiconducting behaviour with non-volatile memory functionality in a single material platform14,15,16,17. This integration of logic and memory capabilities within one material system offers an elegant path towards overcoming the energy-intensive data movement between separate logic and memory components in conventional von Neumann architectures15,18,19.

The materials diversity and functional richness of indium selenides have enabled electronic devices specifically designed for logic and memory applications. For logic devices, substantial progress has been demonstrated with InSe ballistic transistors achieving a record-high transconductance value of ~6 mS and current density of 1.2 mA μm–1 at VDD = 0.5 V, making them promising candidates for sub-1 nm node integration6,9. Additionally, InSe-based tunnel field-effect transistors (TFETs) show potential for ultra-low power switching through sub-thermionic subthreshold characteristics20. For memory, In2Se3 ferroelectric semiconductor field-effect transistors (FeSFETs) leverage inherent ferroelectric properties for non-volatile data storage15,18, whereas ferroelectric semiconductor junctions (FSJs) offer innovative approaches to resistance-based memory with high on/off ratios19.

In this Perspective, we critically evaluate advances in indium selenide materials and devices, assessing their potential as cornerstones for beyond-silicon electronics, focusing on low-power computing applications. We analyse the diverse phases and electronic structures, and discuss key challenges in scalable synthesis and device integration. By bridging materials science fundamentals with device engineering considerations, this Perspective aims to provide a comprehensive assessment of the prospects of indium selenides for transforming future microelectronics and nanoelectronics.

Indium selenides across diverse phases

Layered 2D InSe (Fig. 1a, left) and In2Se3 (Fig. 1a, right) have emerged as interesting avenues for materials and device-level exploration due to their superlative electronic and optical properties, relative thermodynamic stability at room temperature and the ability to grow large crystals or thin films that are easily processable11,12,13. The larger indium selenide family of compounds exists in multiple different polymorphs and polytypes, including layered (2D) InSe, In2Se3, In3Se4 (ref. 21) and In4Se3 (ref. 22) (Fig. 1a, centre). This diversity broadens the design landscape but also introduces new processing challenges.

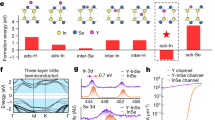

a, Structures of InSe (left) and In2Se3 (right) showing their phase variants and stacking orders, with the binary In–Se phase diagram (centre). b, Thermal velocity as a function of thickness for InSe compared with other semiconducting materials such as 2D transition metal dichalcogenides (TMDs), 3D compound semiconductors and 3D silicon9. c, Thickness-dependent bandgaps of the indium selenides compared with the semiconducting 2D TMDs and bulk silicon6,25,28,41,44. d, Coercive field and remnant polarization of α-In2Se3 compared with other 2D van der Waals ferroelectrics130,141,142,143,144,145,146, such as bilayer graphene (BLG), α-phase SnS (αSnS), CuInP2S6 (CIPS) and rhombohedral-stacked MoS2 (3R-MoS2) (filled symbols) as well as conventional 3D ferroelectrics147,148,149,150 such as scandium-doped AlN (AlScN), poly(vinylidene fluoride) (PVDF), HfxZr1–xO2 (HZO), SrBi2Ta2O9 (SBT), BaTiO3 (BTO) and Pb(Zr,Ti)O3 (PZT) (open symbols). Here, all materials exhibit out-of-plane ferroelectricity, except for α-phase SnS which has in-plane (αSnS (IP)) ferroelectricity.

Polymorphism and electronic structures of InSe

Indium(II) selenide (InSe) is a layered material wherein each layer is four atoms thick with a covalently bonded, honeycomb, in-plane lattice with D3h symmetry. Individual layers are van der Waals bonded in at least three distinct polytypes related by interlayer translations and 180° with respect to the 120° crystal symmetry. InSe has different stacking orders and space groups (Fig. 1a, left and Supplementary Table 1). Density functional theory has been used to calculate the electronic band structures of each InSe phase23,24,25 and, in the cases of β-InSe and γ-InSe, corroborated with angle-resolved photoemission spectroscopy measurements26,27. As constituent layers share the same structure, the in-plane electronic properties of different stacking orders have only subtle differences arising from the orbital overlap between layers. All of these phases have similar bandgaps, as β-InSe exhibits a direct bandgap of 1.2 eV28 about the Γ-point, ε-InSe has an indirect gap of 1.4 eV29 near the Γ-point and γ-InSe is a direct gap semiconductor with a gap around 1.3 eV (refs. 30,31) at the B-point in momentum space (Supplementary Table 1). Their low energy dispersions are similar to each other, with the conduction band (CB) showing a steeper dispersion and a lower effective mass of 0.12 m0, compared with the valence band (VB) whose effective mass is ~0.40 m0. This steep dispersion contributes to high thermal velocity and low effective electron mass, which are crucial parameters for ultra-scaled transistor operation10,32,33. The thermal velocity (vth) of 2D electrons is dependent only on the temperature (\(T\)) and effective electron mass (me) as follows10,32,33:

Calculations of the effective masses of charge carriers in bulk InSe reveal very small effective electron masses of 0.14 m0 and 0.08 m0 for in-plane and out-of-plane conduction, respectively; much smaller than other 2D semiconductors such as MoS2 and WSe2 and comparable with 3D semiconductors such as GaAs and Si (Fig. 1b). Although γ-InSe has received the most attention, all three of the InSe phases are expected to demonstrate high in-plane electron mobility due to their low effective masses and nearly identical low energy dispersions.

In addition to electronic transport, the symmetry of each stacking configuration gives rise to distinct physical functionalities, such as non-linear optical activity and ferroelectricity. For example, the lack of inversion symmetry in the ε-phase and γ-phase allows for non-linear optical effects such as second harmonic generation34 and the piezo-phototronic effect35 compared with β-InSe. Additionally, the non-centrosymmetry allows additional vibrational modes to be Raman active in the γ-polytype and ε-polytype which can couple with other dipolar excitations36.

Beyond these symmetry-enabled effects, structure-driven ferroelectricity in InSe arises from interlayer stacking dynamics. Multilayer van der Waals InSe exhibits ferroelectric polarization through a mechanism known as sliding ferroelectricity, where the stacking sequence of atomic layers dictates the electrical polarization16,37 (Box 1). Specific stacking arrangements induce charge transfer between layers, resulting in an out-of-plane spontaneous polarization. When these atomic layers slide relative to each other, altering their stacking sequence, the associated charge transfer reverses, thereby flipping the spontaneous polarization. This mechanism is fundamentally distinct from classical displacive ferroelectrics and emerges through substitutional doping of yttrium16,37 and layer-number engineering38. This stacking-dependent polarization makes InSe particularly attractive for ferroelectric applications.

Another key aspect of InSe polymorphism is its strong thickness dependence on the band structure, governed by quantum confinement effects, that allows for the tunability of their electronic and optical properties with material thickness. For example, the optical bandgaps of TMDs such as MoS2 and WS2 increase from their bulk values of ~1.5 and ~1.4 eV (indirect) to ~1.9 and ~2.1 eV (direct) in their monolayer limits, respectively39,40. Similarly, the thickness dependence of the bandgaps of γ-InSe and β-InSe have been measured to be ~1.3 eV (direct) in the bulk and to increase to ~2.4 eV (indirect) in the monolayer limit6,28,41 (Fig. 1c and Box 2). We also note that, in the In2Se3 system, α-In2Se3 increases from ~1.3 eV (direct) in bulk to ~1.5 eV (direct) in a monolayer42, and β- In2Se3 rises from ~1.43 eV (direct) in bulk to greater than ~1.58 eV (direct) in the bilayer43. Unlike molybdenum and tungsten dichalcogenides, which experience an abrupt transition from direct to indirect bandgap going from monolayer to bilayer, these phases of InSe and In2Se3 gradually transition over thicknesses of ~10 nm, allowing for a high degree of band structure optimization (Fig. 1c).

The origin of the direct to indirect gap crossover in the InSe phases has been observed experimentally and studied theoretically. Quantum confinement effects cause different VBs to shift in energy at different rates with decreasing thickness25,28,44. As the layer number decreases from bulk, the VB peaks at the Γ-point or B-point get pushed to lower energies, eventually transitioning below the next highest energy VB between 6 and 20 layers25,28. The VB at low thicknesses has a maximum along the Γ–K direction, forming a distorted potential. This transition changes the bandgap from direct momentum at bulk-like thicknesses to indirect momentum at lower thicknesses (Box 2). Due to the reduced dimensionality, many-body effects and long-range forces have a stronger effect on optical and electronic properties. For example, Coulomb interactions and electron–phonon coupling are enhanced in the monolayer limit of InSe, leading to a dramatic increase in excitonic binding energy25 and dark exciton luminescence41. Taken together, the strong dependence of band structures of InSe on layer thickness and stacking order demonstrates how structural and dimensional engineering can be leveraged to tailor its electronic and optical functionalities for emerging device concepts.

Structure and ferroelectricity of In2Se3

Polymorphism in van der Waals In2Se3 is more complicated than in the monoselenide as there are multiple possible structural configurations of each quintuple layer (Se–In–Se–In–Se) in addition to different stacking orders. Thus, the identification and refinement of structural parameters and the resulting electronic properties of these polymorphs remain a central topic of research on phase-dependent phenomena in In2Se3. The three most commonly reported phases of In2Se3 are α-In2Se3, β-In2Se3 and γ-In2Se3. In α-In2Se3, one plane of indium atoms is octahedrally coordinated and the other forms tetrahedra with the selenium atoms (Fig. 1a, right). In β-In2Se3, both planes of indium atoms are octahedrally bonded to selenium atoms. The γ-phase of In2Se3 exhibits a defective wurtzite-like non-layered crystal structure. Because γ-phase In2Se3 does not have the van der Waals characteristic of 2D layered materials, it is not discussed in detail. Additionally, the α-phase and β-phase of In2Se3 can exhibit different stacking orders. α-In2Se3 can form both 2H and 3R layered structures with P63/mc and R3m space groups, respectively, whereas β-In2Se3 can adopt 1T, 2H or 3R lattices with \(P\bar{3}m1\), \(P\bar{3}m1\) and \(R\bar{3}m\) space groups, respectively45 (Supplementary Table 1). In their monolayer form, β-In2Se3 polytypes are centrosymmetric, whereas α-In2Se3 is non-centrosymmetric. This non-centrosymmetry gives rise to inherent electrical polarization even in monolayer α-In2Se3 (refs. 14,46). Together, these diverse stacking configurations and symmetry variations underpin the distinct electronic and ferroelectric behaviours observed in different In2Se3 phases.

Ferroelectricity is a unique property of certain materials, characterized by a spontaneous electric polarization that can be reversed by applying an external electric field. In the α-phase In2Se3, the third-layer selenium atoms deviate from their centrosymmetric positions to reach a more stable potential energy state. Upon an external electric field, these selenium atoms can shift either downward below the upper indium sublayer or upward above the lower indium sublayer, depending on the field direction, thereby enabling out-of-plane ferroelectricity (Fig. 1a, right). According to theoretical symmetry considerations, the threefold rotational symmetry around the out-of-plane axis in monolayer α-In2Se3 cancels any possible in-plane polarization, allowing only out-of-plane ferroelectricity47. Nevertheless, clear in-plane polarization signals in α-In2Se3 through piezo-response force microscopy15,46,48, second harmonic generation49 and opto-electronic transport measurements49 have been experimentally reported. This discrepancy between theory and experiment suggests that the origin of the observed in-plane polarization remains under debate and requires further investigation. In multilayer α-In2Se3, the 2H or 3R stacking configuration can further influence its ferroelectric properties50. The stacking order modulates interlayer interactions and charge redistributions, leading to variations in the motion of ferroelectric domain walls in both in-plane and out-of-plane directions50. Notably, 3R-stacked α-In2Se3 exhibits in-plane movement of out-of-plane ferroelectric domain walls, resulting in a broader electrical hysteresis, known as the memory window, compared with its 2H-stacked counterpart50. The Curie temperature of α-In2Se3 is reported to be ~700 K (ref. 51), which is higher than most of the 2D ferroelectric materials such as ~320 K for van der Waals CuInP2S6 (CIPS), suggesting its robust operation at higher temperatures (see the comparisons in Fig. 1d and Supplementary Table 2).

In the case of β-phase In2Se3, the bulk crystal is centrosymmetric. However, its surface can develop periodic nanostripes that break inversion symmetry, forming a metastable β′-phase (Fig. 1a, right). This β’-phase is similar to the β-phase but with a small displacement of the central selenium atoms52,53. As this displacement breaks the centrosymmetry of the β-phase, the β’-phase exhibits in-plane (anti)ferroelectricity, which persists down to the monolayer limit and is stable up to 200 °C in both bulk and thin exfoliated flakes54,55. Further, due to an unusual competition between ferroelectric and antiferroelectric ordering, the β’-phase often exhibits antiparallel adjacent ferroelectric domains, forming a striped superstructure52,55,56. Depending on the relative size and number of alternating domains, the macroscopic crystal can be observed to be antiferroelectric or ferrielectric, or can be poled to become fully ferroelectric56,57. Angle-resolved photoemission spectroscopy measurements of the β’-phase show an indirect bandgap of 0.97 eV in the bulk with an effective electron mass as small as \({m}_{\text{e}} \sim 0.21\,{m}_{0}\) (ref. 58), whereas the bandgap of monolayer β’-In2Se3 has been found to be 2.5 eV by scanning tunnelling microscope measurements59. This gives the β’-In2Se3 phase a larger range of possible bandgap values and, thus, more tunability than the β-In2Se3 phase.

Moreover, small energy differences and energy barriers between different stacking orders and polymorphs can easily lead to the formation of stacking faults and phase impurity50. In addition, these polymorphs are capable of undergoing phase transitions driven by temperature, defects or synthesis parameters, enabling further engineering of the ferroelectric properties within the material system. For instance, heterophase junctions composed of α-structures and β’-structures facilitate enhanced non-volatile memory performance through band engineering12. Although careful correlation between phase composition and its impact on electronic properties has not yet been demonstrated, proper control and characterization of indium selenide polymorphs and polytypes is expected to be important for producing reliable and reproducible device performance.

Scalable thin-film deposition

Although InSe and In2Se3 exhibit attractive material properties, numerous challenges arise in their preparation. The inherent complexity of the In–Se phase diagram complicates the chemical synthesis of materials with the desired stoichiometry (Fig. 1a). Unlike 2D TMDs such as MoS2 and 3D III–V compound semiconductors such as GaN, GaAs and InP, which each exhibit only one stable polymorph, the binary In–Se system features at least four stable phases at room temperature: InSe, In2Se3, In6Se7 and In4Se3. This complexity hinders precise stoichiometric control during chemical synthesis, compromising the phase purity of the resulting crystal. Moreover, InSe is highly unstable under ambient conditions, particularly in the presence of water molecules and oxygen, leading to oxidation. InSe and In2Se3 spontaneously oxidize rapidly when exposed to air or moisture, following simple reactions60:

This oxidation process results in the formation of amorphous In2Se3 or elemental selenium and converts the crystalline InSe or In2Se3 into stable In2O3. Consequently, it is essential to have a thorough understanding of methods for preparing InSe or In2Se3 with the desired stoichiometry and chemical purity. Furthermore, considering the scalability required for electronic device applications, achieving large-area synthesis of these materials with controlled thickness is equally important.

Mechanical and chemical exfoliations

The preparation of 2D InSe and In2Se3 nanosheets has employed various top-down techniques, including mechanical exfoliation (ME) and chemical exfoliation (CE) from bulk single crystals. ME often uses adhesive tapes to produce high-quality, single-crystalline, few-layer flakes from a mother crystal, suitable for fundamental studies. For example, thickness-dependent quantum confinement affecting the band structure61 and excitonic lasing properties62 has been investigated in mechanically exfoliated InSe crystals. However, ME typically yields small flakes of less than 1,000 μm2 with limited scalability for commercialization.

Another technique, liquid-phase exfoliation, uses solvents and ultrasonic energy to disperse layered materials into nanosheets. This approach can produce larger quantities of exfoliated material, making it more suitable for applications requiring bulk production. However, it can introduce defects or impurities, potentially affecting the material’s intrinsic properties. A liquid-phase exfoliation using KOH achieving thicknesses down to 7 nm for InSe was reported in 2018 (ref. 63). Here, liquid exfoliation enabled the production of few-layered InSe nanosheets with direct bandgaps and large lateral sizes, which are essential for fabricating high-performance photoelectrochemical photodetectors. To prevent oxidation, InSe can be exfoliated using a surfactant-free, deoxygenated, low boiling-point ethanol–water co-solvent system64. This approach enables the preparation of high-quality InSe flakes that exhibit exceptional photoresponsivity of ≈5 × 10⁷ A W⁻¹ in photodetectors.

Another solution-processable method, molecular intercalation, also enables large-scale production of high-quality atom-thick nanosheets with controllable thicknesses15 (Fig. 2a). Electrochemical exfoliation using tetrahexylammonium cations (THA⁺) in tetraethylammonium bromide in N,N-dimethylformamide (DMF) electrolyte provides a scalable approach to generating atom-thick InSe layers with precise structural control with the expression as below15:

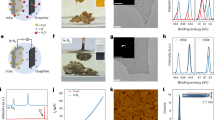

a–d, Representative synthesis methods for indium selenide thin films: chemical exfoliation (CE) (panel a), powder-based chemical vapour deposition (CVD) (panel b), metal–organic chemical vapour deposition (MOCVD) (panel c) and molecular beam epitaxy (MBE)80 (panel d). e,f, Growth temperature dependence of grain or exfoliated crystal size (panel e) and lateral growth rate (panel f), summarized from reports on mechanical exfoliation (ME), CE, CVD74,76,151,152,153,154,155, chemical vapour transport (CVT)75, MBE80 and MOCVD11. ME and CVD data are shown with green and yellow shading. g, Thickness-dependent field-effect mobility of InSe and In₂Se₃ thin films mainly grown by CVD; MOCVD and CE are labelled, and ME samples are shown as open squares with InSe highlighted in green11,74,76,151,152,153,154,155. CMOS BEOL, complementary metal-oxide-semiconductor back-end-of-line; EPC, electronic pressure controller; MFC, mass flow controller; THA⁺, tetrahexylammonium cation. Part d adapted with permission from ref. 80, ACS.

Upon an applied field, THA⁺ intercalates into the mother-crystal bulk InSe and expands the structure gradually through the intercalation. This eventually results in the production of InSe nanosheets, reducing Br– ions on the anode. Importantly, under an external electric field, biaxial tension strain induced by the electrochemical process can cause atomic distortion in β-InSe, breaking its inversion symmetry. This distortion enables the emergence of both in-plane and out-of-plane ferroelectricity in InSe15, indicating that the structural and electrical properties are highly dependent on the method. It should be mentioned that a major breakthrough in improving the scalability and high-quality 2D InSe involved developing an oxygen-free electrochemical molecular intercalation process65. The resultant InSe monolayers exhibited high purity and uniformity across the 4-inch wafer, while proving its high electrical properties with an average electron mobility of ~90–120 cm² V–1 s–1 and on/off ratio of ~107 in fabricated transistors65.

For In2Se3, the exfoliation efficiency reaches higher than 83%, producing sheets up to 30 μm (ref. 66). Furthermore, to date there are no reported cases of In2Se3 exhibiting ferroelectric properties through liquid-phase processes. Therefore, minimizing the risk of degradation during the CE is crucial for future large-scale production. Note that intercalation of alkali metals such as lithium and potassium has not been demonstrated for InSe and In2Se3, probably due to the charge transfer-induced degradation issues.

Altogether, advances in top-down exfoliation techniques, ranging from mechanical and liquid-phase to oxygen-free intercalation, have greatly improved the scalability and quality of 2D InSe, whereas the prevention of chemical degradation remains a key challenge for realizing stable and large-scale production.

Thin-film growth

Compared with ME or CE, thin-film growth of 2D materials offers key advantages for semiconductor industrial applications including thickness and stoichiometry control, enhanced potential for scale-up, gas-phase doping, uniformity across large areas and the ability to tailor material properties by adjusting growth parameters. However, during chemical vapour-based processes, a selenium-rich environment typically favours the formation of In2Se3, whereas an indium-rich condition increases the possibility of producing InSe11. Therefore, to achieve the desired stoichiometric composition, precise control over the fluxes of precursors, especially the chalcogen-to-metal ratio, is essential. Furthermore, the growth temperature and cooling rate also affect the crystalline phases and stacking orders, indicating that multiple growth parameters should be optimized to obtain reliable growth windows.

Metal–organic chemical vapour deposition (MOCVD) emerges as a promising technique for growing phase-pure InSe and In2Se3 thin film11,67, particularly in comparison with powder-based thermal chemical vapour deposition (CVD) (Fig. 2b,c). Metal–organic sources, such as In(CH3)3, have lower melting points than metal or metal oxide sources, such as In or In2O3 (Supplementary Table 3). This lower melting point facilitates improved control of the sources, particularly because MOCVD utilizes a bubbler system equipped with electrical pressure controllers and mass flow controllers, enabling precise regulation of the vapour pressure. It is also worth noting that group III metal precursors, such as indium, In(CH3)3, gallium and Ga(CH3)3, exhibit lower evaporation or sublimation temperatures than transition metal precursors, such as molybdenum and tungsten (Supplementary Table 3). For instance, In(CH3)3 has a melting point of 88 °C and Ga(CH3)3 is in a liquid state at room temperature, whereas tungsten has an exceptionally high melting point of 3,422 °C. Furthermore, the thermal decomposition temperatures of In(CH3)3 and Ga(CH3)3 begin at ~101–150 °C and are lower than those of metal–organic precursors for 2D TMDs at ~250–350 °C for Mo(CO)6 and W(CO)6. This lower temperature requirement for group III precursors thus provides an advantage for silicon back-end-of-line integration at temperatures lower than 450–550 °C (ref. 68).

Compared with InSe and In2Se3, the In–Ga–Se ternary system remains largely unexplored, yet offers opportunities for materials engineering69,70,71,72. Forming In1–xGaxSe alloys could allow for the controlled adjustment of band structures, effective mass and optical properties beyond phase or thickness engineering alone, using growth techniques such as thermal CVD, MOCVD, chemical vapour transport (CVT) and molecular beam epitaxy (MBE) (Fig. 2b–d). Thermal CVD is the most widely adopted method for growth of materials in the In–Ga–Se ternary system due to its easy accessibility, and can grow relatively large grain sizes of ~10–100 µm with moderate growth rates of several nanometres per minute by manipulating solid-state precursors (Fig. 2e,f). However, sublimation of the sources requires high growth temperatures of 700–900 °C (Fig. 2e) and precise control of the metal-to-chalcogen ratio. Hence, powder-based CVD of stoichiometric InSe remains difficult, with only two related reports available as of 2025 (refs. 73,74). CVT, which employs InSe source powder and NH4Cl as a transport agent within a sealed quartz tube, also enables the growth of few-layer InSe or In2Se3 at a growth temperature of ~400–450 °C (ref. 75). High-quality In2Se3 can also be obtained by physical vapour deposition or quasi-equilibrium growth76 using In2Se3 powder at high temperatures of up to ~850 °C (refs. 43,77,78). However, the physical vapour deposition of InSe lacks control over the indium-to-selenium ratio. In addition, both CVT75 and physical vapour deposition43,77,78 typically produce randomly oriented few-layer flakes with smaller grain sizes of less than 20 μm and lack scalability and thickness controllability. In contrast, MOCVD presents a promising approach for scalable and high-quality InSe or In2Se3 production, offering epitaxial mode, wafer-scale growth, moderate growth temperatures of ~400–500 °C and thickness controllability11,67,79. MBE can similarly achieve large-scale, thickness-controlled InSe or In2Se3 by adjusting the growth temperature and source flux ratio80,81 (Fig. 2d), but has limited throughput for producing large-area thin films and high cost because it requires an ultra-high vacuum of 10–10 Torr, which restricts its commercialization when compared with MOCVD (Fig. 2f). However, despite advancements in growth techniques, the electrical performance of synthesized indium selenide films lags behind that of mechanically exfoliated films (Fig. 2g). Specifically, the field-effect mobility of InSe films grown by CVD is typically ~1–10 cm² V–1 s–1, much lower than their mechanically exfoliated counterparts of ~103 cm2 V–1 s–1 for InSe flakes with a thickness of ~5 nm. This reduced electrical mobility in synthetic films is largely attributed to defects such as undesired oxides, vacancies, grain boundaries and phase impurities, which hinder charge carrier transport.

Consequently, there is a pressing need for improved growth methods to minimize defects. One promising approach involves the use of flow-modulation MOCVD to optimize the ripening stage, thereby reducing nucleation densities and promoting lateral growth11,79. Additionally, unidirectionally oriented epitaxial growth, similar to the epitaxial growth of TMD single crystals82, holds potential for producing high-quality thin films. The step-guided epitaxial growth of InSe or In2Se3 on a vicinal-stepped substrate, such as sapphire, with an off-cut angle has yet to be observed. Complementary to these epitaxial approaches, the solid–liquid–solid growth method reported in 2025 represents a highly promising route towards achieving stoichiometric and highly crystalline InSe83. Furthermore, advanced in situ characterization techniques during growth could enable real-time monitoring of phase formation, potentially allowing for automated feedback systems that dynamically adjust growth parameters to maintain stoichiometric control across entire wafers. The integration of machine learning approaches for optimizing the complex growth parameter space holds promise for rapidly identifying conditions that maximize mobility while minimizing defect density.

Achieving high-quality indium selenide thin films requires careful control of the precursor ratios, growth temperature and cooling conditions to ensure the proper stoichiometry and crystal phase purity for optimal film performance. Further progress will depend on improving MOCVD control, epitaxial alignment and data-driven optimization to produce large, defect-free films with high electronic performance.

Defects and oxidation in indium selenides

As predicted by the In–Se–O phase diagram, indium selenides can undergo oxidation to finally form In2O3. When ultrathin InSe is exposed to pure oxygen or air at room temperature, p-type doping and current hysteresis behaviours can arise84,85, making it difficult to achieve the desired high conductivity in transistor applications. Furthermore, the oxidative behaviour of InSe depends on the degree of defects, such as selenium vacancies86, and on the film thickness60. In the case of In2Se3, exposure to oxygen and moisture can induce the formation of an amorphous In2Se3–3xO3x surface layer, a process that is further accelerated under light illumination. Once this oxidation takes place, selenium hemisphere particles can form on the oxidized In2Se3–3xO3x surface87, which might act as a trap centre and undesired doping. Notably, the oxidation characteristics depend on the surface coordination environment: octahedral coordination of atoms in both α-phases and β-phases is less stable than tetrahedral coordination in the α-phase, thereby facilitating the formation of these selenium particles87. The resultant In2Se3–3xO3x layer can self-passivate the surface by limiting oxidation to just a few nanometres in thickness, suggesting that thicker In2Se3 can exhibit reduced oxidation87, thereby preserving the underlying crystal quality and carrier transport properties.

Consequently, optimizing the surface chemistry of indium selenides and developing protective coatings that preserve their electronic properties are imperative. The most widely used method to retard the oxidation of indium selenides involves fabricating encapsulation layers such as HfO2 by atomic layer deposition, which effectively isolates the crystals from moisture and oxygen in the environment and improves its stability9. One can also conduct dry oxidation to form a non-stoichiometric, self-limiting InSe1–xOx oxide layer60. The formation of a dry oxide layer retards further oxidation of the underlying InSe, thereby enabling a high two-probe field-effect mobility of >450 cm2 V–1 s–1 at 300 K for 13 nm-thick InSe in its field-effect transistor (FET)60. For device fabrication, it is essential to use an air-stable fabrication method compatible with photo-beam or electron-beam lithography. In those processes, baking the e-beam resist at 110 °C instead of the usual 180 °C or higher, and then quickly placing it in a high-vacuum environment, helps minimize the formation of free radicals that degrade the InSe contact interface9.

In addition to the native oxides, intrinsic defects such as selenium vacancies in indium selenide structures mediate electronic doping characteristics (Supplementary Table 4). Selenium vacancies generally act as deep-level traps or shallow donors, contributing to n-type behaviour in indium-rich conditions. Conversely, indium vacancies serve as shallow acceptors under selenium-rich environments and can induce p-type conduction in α-In2Se3 or selenium-rich InSe88,89. Several strategies have been experimentally explored to engineer the desired transport characteristics using extrinsic doping (Supplementary Table 4). For example, tin or iodine substitution introduces n-type doping with improved conductivity90,91, whereas yttrium substitution can induce a semi-metallic state in InSe9. These atomic heterogeneities can strongly influence the carrier concentration, recombination dynamics and transport mobility, which are key metrics for logic devices such as future complementary FETs, which are the transistors that enable low-power and high-speed digital circuits by integrating both n-type and p-type channels. Overall, understanding and controlling oxidation and defect chemistry are crucial for realizing stable, high-mobility indium selenide devices suited for electronic and memory applications.

InSe low-power transistors

Transistors are fundamental and critical components in modern electronics, driving the research community and semiconductor industries since their invention in the mid-twentieth century. 2D semiconductors offer an exciting path towards transistor scaling beyond the conventional 5 nm node. Their atomic-scale thickness of a few nanometres greatly improves electrostatic control, which makes them promising for physical sub-10 nm gate lengths. 2D channels have dangling-bond-free surfaces that reduce interface traps and variability, and they can be integrated into 3D device architecture such as vertically stacked nanosheet or nanowire FETs for enhanced drive current and higher device density. Even with its simple planar structure, a metal-oxide semiconductor field-effect transistor (MOSFET) using a 2D semiconductor channel demonstrates the potential to eventually replace conventional silicon channels4,92,93 (Fig. 3a). Nevertheless, major hurdles remain, including finding the most viable channel material options among the versatile 2D semiconductors. InSe stands out as a promising material for logic device fabrication due to its high carrier mobility, low thermal conductivity and ballistic transport.

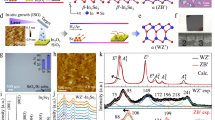

a, Ballistic field-effect transistor (BFET) with an on InSe channel, where contact engineering and a short channel enable ballistic rather than scattering-limited transport9. b, Tunnel field-effect transistor (TFET) employing InSe and p++Si for band-to-band tunnelling20. c–e, Benchmarking plots of transfer curves (c), subthreshold swing (SS) (d) and on-state current density (Ion) versus channel length (LG) (e) for InSe-based field-effect transistors (FETs) — BFET, TFET, metal-oxide semiconductor field-effect transistor (MOSFET) and fin-shaped field-effect transistor (FinFET) — compared with silicon and other conventional semiconductor materials9,20,105,106,107,108. f, Flat-band observation through gate-source tunnelling current (IG) under laser illumination109. g, Ballistic avalanche FET showing impact ionization-driven carrier multiplication in a heterostructuresed of InSe and black phosphorus (BP)111. Ec, conduction-band edge energy; Ev, valence-band edge energy; Ids, drain-source current; Vds, drain-source voltage VG, gate voltage; VTH, threshold voltage.

Beyond conventional thermionic MOSFET operation, 2D semiconductors also enable novel steep-slope device concepts that can reduce the switching power below the limit of traditional FETs by overcoming the ~60 mV decade–1 subthreshold swing (SS) limit at room temperature. Their exceptionally high carrier mobility makes 2D semiconductors particularly appealing for these emerging steep-slope transistors, whereas their van der Waals surfaces and easy integration offer extensive opportunities for band engineering and device design. For example, in TFETs, 2D heterojunctions with type-III band alignment can promote band-to-band carrier tunnelling and facilitate sub-thermionic (less than ~60 mV decade–1) switching, albeit with ongoing challenges in boosting the on-state current (Fig. 3b). These breakthroughs suggest that high-mobility 2D semiconductors, when combined with advanced device physics approaches such as tunnelling and 3D integration, could be key to continuing transistor scaling and enabling ultra-low-power operation in next-generation electronics.

FETs with 2D InSe nanosheet channels

The most attractive feature of InSe for electronic applications is the high electron mobility. Even early-stage, non-optimized InSe transistors exhibit mobilities higher than those achievable with single-crystal TMDs94,95,96. InSe transistor performance is improved by employing smooth polymer substrates7,97,98, passivation by controlled oxidation60,99,100, indium capping8 and encapsulation with hBN6,101,102. Room-temperature field-effect mobilities in these devices can routinely exceed 1,000 cm2 V–1 s–1, competing with state-of-the-art silicon transistors6,7,8.

This high mobility of InSe is attributed to an exceptionally high thermal velocity exceeding 2 × 107 cm s–1 (ref. 9), which surpasses that of all semiconducting TMDs and silicon at equivalent thicknesses9 (Fig. 1b). This high thermal velocity enables electrons to travel through the transistor channel with minimal scattering when the channel length is short enough and ohmic contact exists. As a result, carriers traverse the channel without undergoing substantial scattering with phonons or impurities, preserving their energy and momentum, which is critical for reducing power dissipation and ensuring faster operation (Fig. 3a, right). This is important because, at ultra-short channel lengths, 2D material FETs are typically limited by the thermal velocity of the channel material, which is determined solely by the material’s effective electron mass10,32,33. The superior thermal velocity of InSe is due to its small effective mass of ~0.1 m0. However, the small effective mass can trigger the disadvantage of increasing the probability of source-drain tunnelling in the off-state, known as the leakage current103. Therefore, to realize InSe-based FET devices with a high on-to-off current ratio, it is vital to suppress the leakage current. One strategy is to select the appropriate channel InSe thickness and thereby increase the effective mass and bandgap due to quantum confinement effects, which reduces the probability of tunnelling. Additionally, integrating high-k gate dielectrics or adopting gate-all-around geometries enhances gate control, thereby minimizing tunnelling leakage current through improved electrostatic control of the channel.

By employing contact engineering, encapsulation with high-k dielectrics and scaled channel lengths below 20 nm, ballistic transistors utilizing 2.4 nm-thick InSe have been demonstrated9. The device, with a 10 nm channel length, achieves ohmic contacts through yttrium doping-induced phase transitions in InSe. By minimizing phonon scattering and leveraging its high thermal velocity, the InSe ballistic transistors demonstrate exceptional transfer characteristics, including a SS of ~75 mV decade–1 (Fig. 3a,c,d) and a record-high transconductance of 6 mS (ref. 9) (Fig. 3e), better than other 2D material MOSFETs.

Still, most InSe FETs typically exhibit intrinsic n-type behaviour, primarily attributed to native point defects, such as indium interstitials and selenium vacancies (Supplementary Table 4), as well as Fermi-level pinning at the metal–semiconductor interface (Supplementary Fig. 1 and Supplementary Note 1). To implement the complementary FET architecture, which necessitates possessing both n-type and p-type channels, the fabrication of high-performance p-type 2D InSe FETs is necessary. One effective strategy involves using electrical contact of a high work-function metal, such as platinum, configured in a van der Waals interface, which can mitigate Fermi-level pinning (Supplementary Fig. 1) and enhance hole injection in FETs104.

Tunnel FETs based on InSe/Si heterojunction

TFETs composed of 2D InSe and 3D silicon (Fig. 3b) exhibit sub-60 mV decade–1 operation, an on-state current density of ~0.3 µA µm–1 and an on/off current ratio of ~106 (ref. 20). These remarkable results are attributed to the type-III band alignment formed between InSe and silicon, which establishes an optimal offset in their CB and VB. Moreover, the atomic-scale thickness of InSe not only maximizes gate electrostatic control but also, owing to its van der Waals surface, provides the clean and thin channel essential for TFETs. Consequently, when suitable gate and drain voltages are applied, band-to-band tunnelling is readily induced.

The SS of InSe TFETs20 is comparable with that of black phosphorus (BP)-based TFETs105 and superior to that of 3D InAs-based TFETs106 (Fig. 3d). However, the current density of InSe TFETs, which is less than 1 mA μm–1 (ref. 20), is still lower than that of silicon-based or 2D semiconductor-based MOSFETs9,107,108 (Fig. 3d,e). These characteristics suggest that there is substantial room for improvement in achieving high on-state conductance. Thus, it is necessary to find better material options for semiconductors with a bandgap compatible with InSe, and to implement automated, large-area processes that can optimize characteristics of interfaces at junctions, contacts and dielectrics.

Flat bands of InSe and their detection in FETs

In addition, InSe FETs provide an excellent platform for studying new physical properties of 2D InSe. One notable discovery involves detecting the flat band of InSe through electrical measurements109 (Fig. 3f). The measurement of the flat band can be conducted using a FET with a simple but effective design: InSe is sandwiched between two hBN insulating layers and uses graphene for the source and drain contacts (Fig. 3f, left). By adjusting the gate voltage, one can move the Fermi level (EF) of InSe from the CB, through the bandgap and into the VB region. Hence, the out-of-plane tunnelling current using carriers generated by visible laser light can be measured. When EF reaches the van Hove singularity near the VB (Fig. 3f, right), the density of states increases sharply, causing a distinct spike in tunnelling current. This effect becomes particularly noticeable as the tunnelling mechanism shifts from direct to Fowler–Nordheim tunnelling at the flat band. Compared with traditional measurement techniques such as angle-resolved photoemission spectroscopy, scanning tunnelling microscopy and scanning tunnelling spectroscopy, this electrical detection method is remarkably simple109. Because flat bands typically exhibit large effective masses and strong electron–electron interactions, InSe might display interesting phenomena such as magnetic and superconducting phase transitions. Additionally, the transistor structure enables studying spin polarization and chirality effects in 2D InSe by measuring photo-excited holes tunnelling through the hBN barrier under magnetic fields110.

Ballistic avalanche InSe/BP FETs

By leveraging the ballistic transport characteristics and van der Waals properties of InSe, one can form a high-performance FET based on heterostructures composed of InSe and other 2D or 3D semiconductors (Fig. 3g). Depending on how carriers transport across these semiconductors, such heterostructures can be utilized in devices such as impact ionization transistors or tunnelling transistors.

For instance, by using InSe as an n-type semiconductor and BP as a p-type semiconductor, both electrons and holes can be sufficiently accelerated within the heterostructure to drive impact ionization111 (Fig. 3g). As a result, unlike the conventional impact ionization-driven avalanche phenomenon observed in bulk semiconductors, a ballistic avalanche phenomenon can be observed in vertical InSe/BP heterostructures. Although typical avalanche devices require high voltages in the order of tens of volts or a long impact ionization region, the InSe/BP heterostructure enables avalanche breakdown at voltages below ~1 V. Moreover, the devices exhibit excellent noise performance with a low avalanche threshold below 1 V, and an ultra-steep SS of 0.25 mV decade–1, demonstrating their potential for high-sensitivity avalanche photodetectors and transistors111.

Non-volatile memory device applications

Ferroelectricity in 2D materials has attracted much research interest due to its potential applications in energy-efficient computing platforms when applying the non-volatile properties of the ferroelectric polarizations112. When coupled with the van der Waals nature of 2D materials, in particular, ferroelectricity offers an innovative approach to address the scaling limitations and performance degradation at reduced thicknesses faced by traditional 3D ferroelectrics14,112,113. Moreover, van der Waals layered InSe and In2Se3, even with their atomic-scale thickness and a bandgap of >1.41 eV, exhibit either sliding ferroelectricity or spontaneous ferroelectricity despite not being insulators. Consequently, the existence of ferroelectricity in indium selenides enables the integration of strong polarization responses with functionalities derived from their semiconducting properties, facilitating the development of compact, energy-efficient devices for in-memory, in-sensory computing, neuromorphic systems and optoelectronics14,112,113. Furthermore, the high Curie temperature of In2Se3 makes it especially attractive, as this allows for maintaining stable operation under high temperatures generated by Joule heating. Therefore, InSe and In2Se3 can be applied to FSJs19,50,114 and FeSFETs12,18,115 for future ultra-high-density, low-power memory applications.

In2Se3 ferroelectric semiconductor junctions

Ferroelectric tunnel junctions (FTJs) are next-generation memory devices that utilize electron tunnelling through an ultrathin ferroelectric insulating film, exhibiting non-volatile resistance changes depending on the polarization orientation. A typical FTJ adopts a metal–ferroelectric–metal configuration, in which a nanometre-thick ferroelectric layer serves as the tunnelling barrier and is sandwiched between two metal electrodes, and an oxide or semiconducting interlayer is sometimes inserted between the metal and ferroelectric. In this structure, electrons tunnel quantum mechanically through the ferroelectric barrier, and the reversal of ferroelectric polarization shifts the barrier height and width, thereby altering the tunnelling current in a non-volatile manner. This phenomenon, referred to as tunnelling electroresistance, is quantified by its on/off ratio, which is a key figure of merit for FTJ memory operation.

For the ferroelectric semiconductor In2Se3, rather than an ferroelectric insulator, crossbar two-terminal FSJ devices share the same metal–ferroelectric–metal structure as FTJs (Fig. 4a). However, polarization-dependent charge transport can occur via thermionic emission over a Schottky barrier, rather than tunnelling electroresistance in FTJs (Fig. 4b). This key distinction enables FSJs to achieve high on/off ratios above ~104, improved thermal stability and reduced leakage without requiring ultrathin films in various In2Se3 FSJs19,114,116. Furthermore, due to the semiconducting nature of In2Se3, partial polarization switching confined near the contact interface can occur under localized electric fields117. Compared with typical insulators, the smaller bandgap of In2Se3 facilitates non-volatile modulation of the Schottky barrier height (Фeff) without full switching across the entire film thickness, offering an additional degree of partial ferroelectric control in FSJ. Therefore, FSJs can exhibit potential for multi-state applications in analogue synaptic devices.

a,b, In2Se3-based ferroelectric semiconductor junction (FSJ) device with an interlayer: representative device structure (a) and the FSJ with each effective Schottky barrier height (Фeff) at the on-state and off-state (b). c,d, Ferroelectric semiconductor field-effect transistor (FeSFET) using In2Se3: device structure (c) and band diagram of a FeSFET in polarization up (Pup) and polarization down (Pdown) states (d). CB, conduction band; EF, Fermi level; VB, valence band.

Contributing to van der Waals stacking of different materials, the FSJ structures of metal/interlayer/α-In2Se3/p+Si (ref. 19), metal/hBN/α-In2Se3/graphene (ref. 114) and metal/α-In2Se3/MoS2 (ref. 116) have been proposed. The insertion of an interlayer can provide asymmetry of the band alignment, while modulating Фeff (refs. 19,114,116) and suppressing the thermionic current leakage116. For example, the metal/α-In2Se3/MoS2 (ref. 116) device exhibits both a room-temperature negative differential resistance effect and high electroresistance exceeding 104 simultaneously, providing temperature-independent transport. The ferroelectric van der Waals metal WTe2 has been used as metal electrode for In2Se3 FSJs in WTe2/α-In2Se3/metal (ref. 118). The use of WTe2 allows for the high on/off ratio of 105, with a switching voltage of less than 2 V. In addition, multiple resistance levels have been observed due to the pinning effect of the WTe2/α-In2Se3 interface on the upward polarization of α-In2Se3. This pinning effect permits the polarization of α-In2Se3 to maintain a partially switched polarization state, resulting in an intermediate resistance level.

Despite this potential, however, the on/off ratio of an In2Se3 FSJ19,50,114,116 is limited to ~105, which is relatively low compared with other FTJs. The state-of-the-art bulk ferroelectric-based FTJ composed of oxide heterostructures exhibits an on/off ratio of ~108 (ref. 119), and the van der Waals ferroelectric CIPS-based FTJ achieves ~1010 at room temperature120, both higher than that of an In2Se3 FSJ19,50,114,116 (Table 1). More importantly, there remain significant challenges for the large-area integration of In2Se3 FSJs into crossbar array devices within silicon back-end-of-line compatible fabrication processes and large-scale integration technologies.

InSe and In2Se3 ferroelectric semiconductor FETs

Compared with two-terminal FTJs or FSJs, three-terminal ferroelectric field-effect transistors (FeFETs) offer multiple advantages in terms of operating mechanism and practical utility121. For instance, two-terminal ferroelectric devices typically ascertain the memory state by applying voltage and measuring the resulting current, which can lead to destructive read-out if the polarization is altered or partially lost during measurement122. In contrast, in a three-terminal FeFET architecture, one can measure the channel doping state indirectly by simply adjusting the gate voltage, thus enabling non-destructive read-out121,123. Because the read and write pathways are physically separated, these transistor-based devices provide higher device stability and better data retention. Additionally, the channel conductivity is modulated through the gate, whereas ferroelectric polarization maintains non-volatility, making it more straightforward to combine logic and memory functionality within a single device124. Thus, FeFETs are well suited for next-generation non-volatile memories, neuromorphic computing and logic-in-memory applications, thanks to their fast-switching characteristics, potential for high-density integration and low power consumption. By finely tuning the gate voltage, these devices can realize multilevel channel current control, synaptic weight updates and independent read-out signals.

In the case of InSe and In2Se3, both materials can exhibit ferroelectric behaviour yet have a relatively small bandgap of >1.41 eV compared with bulk ferroelectric insulators (Fig. 1d). This property has attracted attention for potential applications as FeSFETs12,18,110,125 (Fig. 4c). Unlike conventional FeFETs that use a ferroelectric layer as the gate dielectric, InSe and In2Se3 allow the use of a standard gate dielectric while still enabling polarization control in the channel. Because the channel itself is ferroelectric, reorienting the polarization critically alters the channel doping concentration and conductivity (Fig. 4d). Depending on the effective oxide thickness, different portions of the channel’s top or bottom surfaces can be polarized, and the electric field can penetrate to varying depths18. Consequently, the transfer characteristics can exhibit clockwise or counterclockwise hysteresis, forming a memory window, and because this polarization is preserved even when power is removed, these transistors can serve as non-volatile memory that integrates logic and memory in a single device.

In conventional FeFETs employing a bulk ferroelectric gate, incomplete screening of polarization along the channel can degrade memory properties126. In contrast, ferroelectric semiconductor channels, such as InSe and In2Se3, can self-screen the polarization charges with mobile carriers, thereby reducing interface trapping and gate leakage and improving retention18,112. This advantage can be explained in terms of the depolarization field. The depolarization field is an internal electric field opposite to spontaneous polarization that arises when bound charges at the ferroelectric interfaces are only partially compensated127. For a typical FeFET with a metal–ferroelectric–interlayer–semiconductor gate structure, the depolarization field can be severe when a thin, low-k interfacial oxide such as SiO2 in a TiN/HfxZr1–xO2 (HZO)/SiO2/Si stack separates the ferroelectric from the channel; as the magnitude of the depolarization field approaches the coercive field, retention degrades rapidly because the polarization can no longer remain stable against this self-imposed field. FeSFETs based on atomically thin ferroelectric semiconductors can avoid this limitation because the channel itself is ferroelectric. The van der Waals interface supplies nearly ideal charge compensation without dangling bonds, and the FeSFET device stack typically lacks a distinct interfacial oxide, eliminating the voltage drop that would otherwise generate a strong depolarization field. Retention can be further enhanced by combining this intrinsic advantage with extrinsic engineering, such as adopting an ultrathin, high-k gate dielectric to shorten the screening length, and by applying modest electrostatic or chemical doping to the ferroelectric channel, ensuring a sufficient free-carrier density for rapid charge compensation. In short, 2D FeSFETs hold the promise of mitigating the depolarization field-limited retention that has long hindered bulk-oxide FeFETs.

In addition, switching speeds can reach ~40 ns in In2Se3-based FeSFETs115. This fast-switching behaviour could possibly arise from the intrinsic coupling between ferroelectricity and semiconducting nature of α-In2Se3: unlike traditional FeFETs where only polarization-bound charges participate, the ferroelectric semiconductor channel supports both bound and mobile charges18,112,115. The presence of mobile carriers enables the formation of internal electric fields that assist and stabilize the polarization switching, thereby enhancing switching dynamics. In this configuration, the internal field compensates for depolarization and reinforces domain alignment even under moderate gate voltages.

However, the switching timescale is still slower than that of non-2D ferroelectrics operating in the sub-nanosecond regime, such as Pb(Zr,Ti)O3 (PZT)128. Therefore, realizing further acceleration of switching speed in 2D FeSFETs remains an open challenge. This limitation could be particularly attributed to gate capacitance limitations and incomplete polarization caused by relatively thick dielectrics or weak vertical electric fields. As such, continued optimization of gate stack engineering — such as reducing the effective oxide thickness to enhance the vertical electrical field — will be essential for pushing the switching speed.

Furthermore, device-level validation of the interface stability, operating temperature ranges and long-term endurance is also becoming increasingly important, given that current In2Se3 FeSFETs12,18,125 often show endurance of ~104 cycles and retention in the order of 105 s (Table 1). To ensure robust performance, it is essential to optimize selection of metal contacts and gate dielectrics to minimize contact resistance, trap states and device degradation. In this regard, employing 2D ferroelectric metal contacts, similar to work with WTe2/α-In2Se3/metal crossbar devices118, combined with Fermi-level depinned metal contacts (Supplementary Note 1) will enable more stable, low-resistance contact interfaces and enhanced endurance in future FeSFETs.

In addition, the demonstration of endurance over 1011 cycles in FeFETs based on the sliding ferroelectricity of bilayer BN129 indicates that sliding ferroelectricity in InSe can offer enhanced robustness against fatigue. Here, polarization reversal proceeds through an in-plane interlayer shear described as a shear-mediated phase transformation130, which transforms pre-existing, movable ferroelectric domain boundaries rather than repeatedly nucleating and annihilating out-of-plane domains. Because this shear occurs across weak van der Waals gaps, it largely suppresses the creation of dangling bonds, oxygen vacancies and other interface defects that usually accumulate at the junction between the ferroelectric and the semiconductor, resulting in reliability issues and narrowing the memory window in conventional FeFETs131. Therefore, sliding ferroelectrics maintain high endurance through an in-plane sliding mechanism129. Although this intrinsic ‘defect-tolerant’ switching pathway explains the high cycling endurance observed thus far, systematic studies are still needed to correlate native defects, possible interlayer slip pinning and long-term retention, thereby validating the ultimate reliability limits of InSe-based sliding ferroelectric memories.

Ferroelectric devices for in-memory computing

Indium selenide-based ferroelectric memory devices can provide new opportunities for beyond von Neumann computing architectures. These devices enable simultaneous storage and processing of information within the same physical element, thereby overcoming the memory–logic bottleneck in conventional silicon-based semiconductor systems. The non-destructive read-out and low switching energy further enhance their applicability in low-power embedded systems. Furthermore, In2Se3-based FeFETs can perform Boolean operations by utilizing polarization-dependent conductance states, thereby enabling logic-in-memory or compute-in-memory architectures. For example, ferroelectric polarization can modulate channel resistance to represent different logic states, allowing the realization of AND, OR and majority logic gates directly within memory arrays. Such architectures benefit from fine-grained parallelism and reduced interconnect overhead, which are crucial for data-centric workloads such as matrix-vector multiplication and real-time signal processing.

Beyond digital logic, indium selenide memory devices have shown promising characteristics for neuromorphic computing. The analogue tunability of ferroelectric polarization in In2Se3 FeFETs enables gradual conductance modulation, mimicking biological synaptic plasticity132,133,134. Spike-dependent programming and long-term potentiation and depression behaviours make suitable artificial synapses in hardware neural networks132,133,134. Additionally, the comparatively wider bandgap and optical activity of In2Se3, especially with respect to silicon, allow integration with photodetectors to realize retinomorphic systems that process visual stimuli at the sensor level with minimal energy overhead.

Outlook

The development of van der Waals indium selenides for advanced logic and memory applications remains at an exciting early stage compared with established silicon and compound semiconductor technologies. The key engineering hurdle is to tame the material’s complexity while scaling from record-setting material properties and device performance metrics in exfoliated flakes to wafer-level manufacturing. MOCVD can ultimately deliver high-purity InSe and In2Se3 films on wafers >200 mm. Achieving this target will require the strict suppression of oxide impurities, vacancies and other defect-forming mechanisms; robust oxidation-resistant encapsulation that survives back-end temperatures below 450 °C; and contact electrodes that decisively eliminate Fermi-level pinning, allowing both n-type and p-type operation to become feasible.

Once these large-area process challenges are met, architectural attention will shift to exploiting the interesting characteristics of indium selenides. A compelling concept is a monolithically stacked logic-in-memory block135, in which nanometre-scale gate-all-around InSe transistors on the lower tier provide fast logic. In contrast, an upper-tier array of ferroelectric semiconductor transistors or junctions supplies non-volatile storage and analogue multiply-accumulate functionality. Demonstrating such heterogeneous integration at practical densities would show that indium selenide electronics can coexist with, or augment, conventional silicon for system-on-chip platforms.

Still, the most immediate research priority should be improving the endurance of In2Se3 ferroelectric devices beyond their current <104 cycle limitation towards the goal of >1011 cycles, the threshold necessary for reliable non-volatile memory operation. To enhance the cycling endurance and reliability of In2Se3-based memories, efforts should focus on reducing intrinsic defect density, particularly selenium vacancies and indium interstitials, through controlled doping and defect passivation strategies such as oxygen incorporation. As the technology matures, vertically integrating dozens of indium selenides layers — each only a few atoms thick and separated by self-aligned metallic interconnects — will become possible. This monolithic 3D integration promises memory densities while sitting directly atop logic, eliminating the von Neumann bottleneck and the area penalties of through-silicon vias.

Looking further ahead, compositionally tuned 2D InxGaySez alloys could unlock reconfigurable bandgap engineering and other features that push the frontiers of adaptive electronic and neuromorphic systems69,70,71,72. Alloying InSe with GaSe to form In1–xGaxSe compounds would enable continuous tuning of band structures, effective masses and optical properties beyond what is possible with phase and thickness control alone. These ternary alloys could offer optimized combinations of mobility, bandgap and stability tailored for specific applications from high-performance logic to photodetection. Furthermore, the In–Ga–Se system potentially harbours entirely new phases with unique properties at specific compositional ratios, analogous to discoveries in other ternary chalcogenide systems. The development of compositional gradient structures or vertical heterostructures within this material family could yield novel quantum phenomena and device functionalities impossible in binary compounds.

The transformative potential of indium selenides ultimately depends on continued cross-disciplinary collaboration between materials scientists, device physicists, process engineers and system architects. By addressing the full spectrum from fundamental properties to practical implementation challenges, this emerging material platform can fulfil its promise as a cornerstone of next-generation, low-power computing technologies.

References

Song, S., Rahaman, M. & Jariwala, D. Can 2D semiconductors be game-changers for nanoelectronics and photonics? ACS Nano 18, 10955–10978 (2024).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223–227 (2017).

Feng, W., Zheng, W., Cao, W. & Hu, P. Back gated multilayer InSe transistors with enhanced carrier mobilities via the suppression of carrier scattering from a dielectric interface. Adv. Mater. 26, 6587–6593 (2014).

Li, M. et al. High mobilities in layered InSe transistors with indium-encapsulation-induced surface charge doping. Adv. Mater. 30, 1803690 (2018).

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Natori, K. Ballistic metal-oxide-semiconductor field effect transistor. J. Appl. Phys. 76, 4879–4890 (1994).

Song, S. et al. Wafer-scale growth of two-dimensional, phase-pure InSe. Matter 6, 3483–3498 (2023).

Han, W. et al. Phase-controllable large-area two-dimensional In2Se3 and ferroelectric heterophase junction. Nat. Nanotechnol. 18, 55–63 (2023).

Imai, K., Suzuki, K., Haga, T., Hasegawa, Y. & Abe, Y. Phase diagram of In–Se system and crystal growth of indium monoselenide. J. Cryst. Growth 54, 501–506 (1981).

Ding, W. et al. Prediction of intrinsic two-dimensional ferroelectrics in In2Se3 and other III2-VI3 van der Waals materials. Nat. Commun. 8, 14956 (2017).

Hu, H. et al. Out-of-plane and in-plane ferroelectricity of atom-thick two-dimensional InSe. Nanotechnology 32, 385202 (2021).

Sui, F. et al. Sliding ferroelectricity in van der Waals layered γ-InSe semiconductor. Nat. Commun. 14, 36 (2023).

Li, W. et al. Emergence of ferroelectricity in a nonferroelectric monolayer. Nat. Commun. 14, 2757 (2023).

Si, M. et al. A ferroelectric semiconductor field-effect transistor. Nat. Electron. 2, 580–586 (2019).

Si, M. et al. Asymmetric metal/α-In2Se3/Si crossbar ferroelectric semiconductor junction. ACS Nano 15, 5689–5695 (2021).

Miao, J. et al. Heterojunction tunnel triodes based on two-dimensional metal selenide and three-dimensional silicon. Nat. Electron. 5, 744–751 (2022).

Han, G. et al. A new crystal: layer-structured rhombohedral In3Se4. CrystEngComm 16, 393–398 (2014).

Hogg, J. H. C., Sutherland, H. H. & Williams, D. J. The crystal structure of tetraindium triselenide. Acta Crystallogr. B Struct. Crystallogr Cryst. Chem. 29, 1590–1593 (1973).

Debbichi, L., Eriksson, O. & Lebègue, S. Two-dimensional indium selenides compounds: an ab initio study. J. Phys. Chem. Lett. 6, 3098–3103 (2015).

Srour, J., Badawi, M., El Haj Hassan, F. & Postnikov, A. Comparative study of structural and electronic properties of GaSe and InSe polytypes. J. Chem. Phys. 149, 054106 (2018).

Pike, N. A. et al. Understanding the origin and implication of the indirect-to-direct bandgap transition in multilayer InSe. J. Phys. Chem. C. 128, 7957–7967 (2024).

Politano, A. et al. Indium selenide: an insight into electronic band structure and surface excitations. Sci. Rep. 7, 3445 (2017).

Hamer, M. J. et al. Indirect to direct gap crossover in two-dimensional InSe revealed by angle-resolved photoemission spectroscopy. ACS Nano 13, 2136–2142 (2019).

Borodin, B. R. et al. Indirect-to-direct band-gap transition in few-layer β-InSe as probed by photoluminescence spectroscopy. Phys. Rev. Mater. 8, 014001 (2024).

Manjón, F. J. et al. Experimental and theoretical study of band structure of InSe and In1−xGaxSe (x < 0.2) under high pressure: direct to indirect crossovers. Phys. Rev. B 63, 125330 (2001).

Abay, B., Efeoğlu, H. & Yoğurtçu, Y. K. Low-temperature photoluminescence of n-InSe layer semiconductor crystals. Mater. Res. Bull. 33, 1401–1410 (1998).

Gürbulak, B. et al. Structural characterizations and optical properties of InSe and InSe:Ag semiconductors grown by Bridgman/Stockbarger technique. Phys. E: Low-dimensional Syst. Nanostructures 64, 106–111 (2014).

Quhe, R. et al. Sub-10 nm two-dimensional transistors: theory and experiment. Phys. Rep. 938, 1–72 (2021).

Lundstrom, M. Elementary scattering theory of the Si MOSFET. IEEE Electron. Device Lett. 18, 361–363 (1997).

Hao, Q. et al. Phase identification and strong second harmonic generation in pure ε-InSe and its alloys. Nano Lett. 19, 2634–2640 (2019).

Dai, M. et al. Robust piezo-phototronic effect in multilayer γ-InSe for high-performance self-powered flexible photodetectors. ACS Nano 13, 7291–7299 (2019).

Hilse, M. et al. Mixed polytype/polymorph formation in InSe films grown by molecular beam epitaxy on GaAs(111)B. npj 2D Mater. Appl. 9, 19 (2025).

Sui, F. et al. Atomic-level polarization reversal in sliding ferroelectric semiconductors. Nat. Commun. 15, 3799 (2024).

Wang, Y. et al. Sliding ferroelectricity induced ultrafast switchable photovoltaic response in ε-InSe layers. Adv. Mater. 36, 2410696 (2024).

Molas, M. R. et al. The optical response of monolayer, few-layer and bulk tungsten disulfide. Nanoscale 9, 13128–13141 (2017).

Li, X. & Zhu, H. Two-dimensional MoS2: properties, preparation, and applications. J. Materiomics 1, 33–44 (2015).

Paylaga, N. T. et al. Monolayer indium selenide: an indirect bandgap material exhibits efficient brightening of dark excitons. npj 2D Mater. Appl. 8, 12 (2024).

Jacobs-Gedrim, R. B. et al. Extraordinary photoresponse in two-dimensional In2Se3 nanosheets. ACS Nano 8, 514–521 (2014).

Balakrishnan, N. et al. Quantum confinement and photoresponsivity of β-In2Se3 nanosheets grown by physical vapour transport. 2D Mater. 3, 025030 (2016).

Quereda, J. et al. Strong quantum confinement effect in the optical properties of ultrathin α-In2Se3. Adv. Optical Mater. 4, 1939–1943 (2016).

Liu, L. et al. Atomically resolving polymorphs and crystal structures of In2Se3. Chem. Mater. 31, 10143–10149 (2019).

Xue, F. et al. Gate-tunable and multidirection-switchable memristive phenomena in a van der Waals ferroelectric. Adv. Mater. 31, 1901300 (2019).

Bai, L. et al. Intrinsic ferroelectric switching in two-dimensional α-In2Se3. ACS Nano 18, 26103–26114 (2024).

Wang, L. et al. Exploring ferroelectric switching in α-In2Se3 for neuromorphic computing. Adv. Funct. Mater. 30, 2004609 (2020).

Uzhansky, M., Rakshit, A., Kalcheim, Y. & Koren, E. Coupled pyroelectric-photovoltaic effect in 2D ferroelectric α-In2Se3. npj 2D Mater. Appl. 9, 6 (2025).

Wu, Y. et al. Stacking selected polarization switching and phase transition in vdW ferroelectric α-In2Se3 junction devices. Nat. Commun. 15, 10481 (2024).

Xiao, J. et al. Intrinsic two-dimensional ferroelectricity with dipole locking. Phys. Rev. Lett. 120, 227601 (2018).

Zhang, F. et al. Atomic-scale manipulation of polar domain boundaries in monolayer ferroelectric In2Se3. Nat. Commun. 15, 718 (2024).

Huang, J., Ke, C., Qian, Z. & Liu, S. Competing charge transfer and screening effects in two-dimensional ferroelectric capacitors. Nano Lett. 24, 6683–6688 (2024).

Zheng, C. et al. Room temperature in-plane ferroelectricity in van der Waals In2Se3. Sci. Adv. 4, eaar7720 (2018).

Xu, C. et al. Two-dimensional ferroelasticity in van der Waals β’-In2Se3. Nat. Commun. 12, 3665 (2021).

Xu, C. et al. Two-dimensional antiferroelectricity in nanostripe-ordered In2Se3. Phys. Rev. Lett. 125, 047601 (2020).

Wang, L. et al. In-plane ferrielectric order in van der Waals β′-In2Se3. ACS Nano 18, 809–818 (2024).

Collins, J. L. et al. Electronic band structure of in-plane ferroelectric van der Waals β′-In2Se3. ACS Appl. Electron. Mater. 2, 213–219 (2020).

Zhang, F. et al. Atomic-scale observation of reversible thermally driven phase transformation in 2D In2Se3. ACS Nano 13, 8004–8011 (2019).

Ho, P.-H. et al. High-mobility InSe transistors: the role of surface oxides. ACS Nano 11, 7362–7370 (2017).

Mudd, G. W. et al. Tuning the bandgap of exfoliated InSe nanosheets by quantum confinement. Adv. Mater. 25, 5714–5718 (2013).

Li, C. et al. Room-temperature near-infrared excitonic lasing from mechanically exfoliated InSe microflake. ACS Nano 16, 1477–1485 (2022).

Li, Z. et al. High-performance photo-electrochemical photodetector based on liquid-exfoliated few-layered InSe nanosheets with enhanced stability. Adv. Funct. Mater. 28, 1705237 (2018).

Kang, J. et al. Solution-based processing of optoelectronically active indium selenide. Adv. Mater. 30, 1802990 (2018).

He, J. et al. Solution-processed wafer-scale indium selenide semiconductor thin films with high mobilities. Nat. Electron. 8, 244–253 (2025).

Shi, H. et al. Ultrafast electrochemical synthesis of defect-free In2Se3 flakes for large-area optoelectronics. Adv. Mater. 32, 1907244 (2020).

Zhang, X. et al. Epitaxial growth of few-layer β-In2Se3 thin films by metalorganic chemical vapor deposition. J. Cryst. Growth 533, 125471 (2020).

Tang, A. et al. Toward low-temperature solid-source synthesis of monolayer MoS2. ACS Appl. Mater. Interfaces 13, 41866–41874 (2021).

Gouskov, A., Camassel, J. & Gouskov, L. Growth and characterization of III–VI layered crystals like GaSe, GaTe, InSe, GaSe1–xTex and GaxIn1–xSe. Prog. Cryst. Growth Charact. 5, 323–413 (1982).

Yu, M. et al. Synthesis of two-dimensional alloy Ga0.84In0.16Se nanosheets for high-performance photodetector. ACS Appl. Mater. Interfaces 10, 43299–43304 (2018).

Tran, Q. T. et al. Molecular beam epitaxy of mixed dimensional InGaSe/GaSe hybrid heterostructures on C-sapphire. ACS Appl. Electron. Mater. 6, 7448–7455 (2024).

Amiraslanov, I. R. et al. Synthesis and characterization of new indium gallium selenides of the InSe–GaSe system. J. Solid. State Chem. 304, 122569 (2021).

Huang, W., Gan, L., Li, H., Ma, Y. & Zhai, T. Phase-engineered growth of ultrathin InSe flakes by chemical vapor deposition for high-efficiency second harmonic generation. Chemistry 24, 15678–15684 (2018).

Chang, H.-C. et al. Synthesis of large-area InSe monolayers by chemical vapor deposition. Small 14, 1802351 (2018).

Hu, Y. X. et al. Temperature-dependent growth of few layer β-InSe and α-InSe single crystals for optoelectronic device. Semicond. Sci. Tech. 33, eaae629 (2018).

Si, K. et al. Quasi-equilibrium growth of inch-scale single-crystal monolayer alpha-In2Se3 on fluor-phlogopite. Nat. Commun. 15, 7471 (2024).

Rashid, R. et al. Shape-control growth of 2D-In2Se3 with out-of-plane ferroelectricity by chemical vapor deposition. Nanoscale 12, 20189–20201 (2020).